Analog Devices ADP3152 Datasheet

a

5-Bit Programmable Synchronous

Switching Regulator Controller

®

for Pentium

II Processor

ADP3152

FEATURES

5-Bit Digitally Programmable 1.8 V to 3.5 V Output

Voltage

Dual N-Channel Synchronous Driver

Total Output Accuracy 61% (08C to 708C)

High Efficiency

Current-Mode Operation

Short Circuit Protection

Power Good Output

Integrated Overvoltage Protection Crowbar

16-Lead SOIC Package

VRM 8.2 Compatible

APPLICATIONS

Desktop PC Power Supply for:

Pentium II Processor

Pentium Pro Processor

Pentium Processor

AMD–K6 Processor

VRM Modules

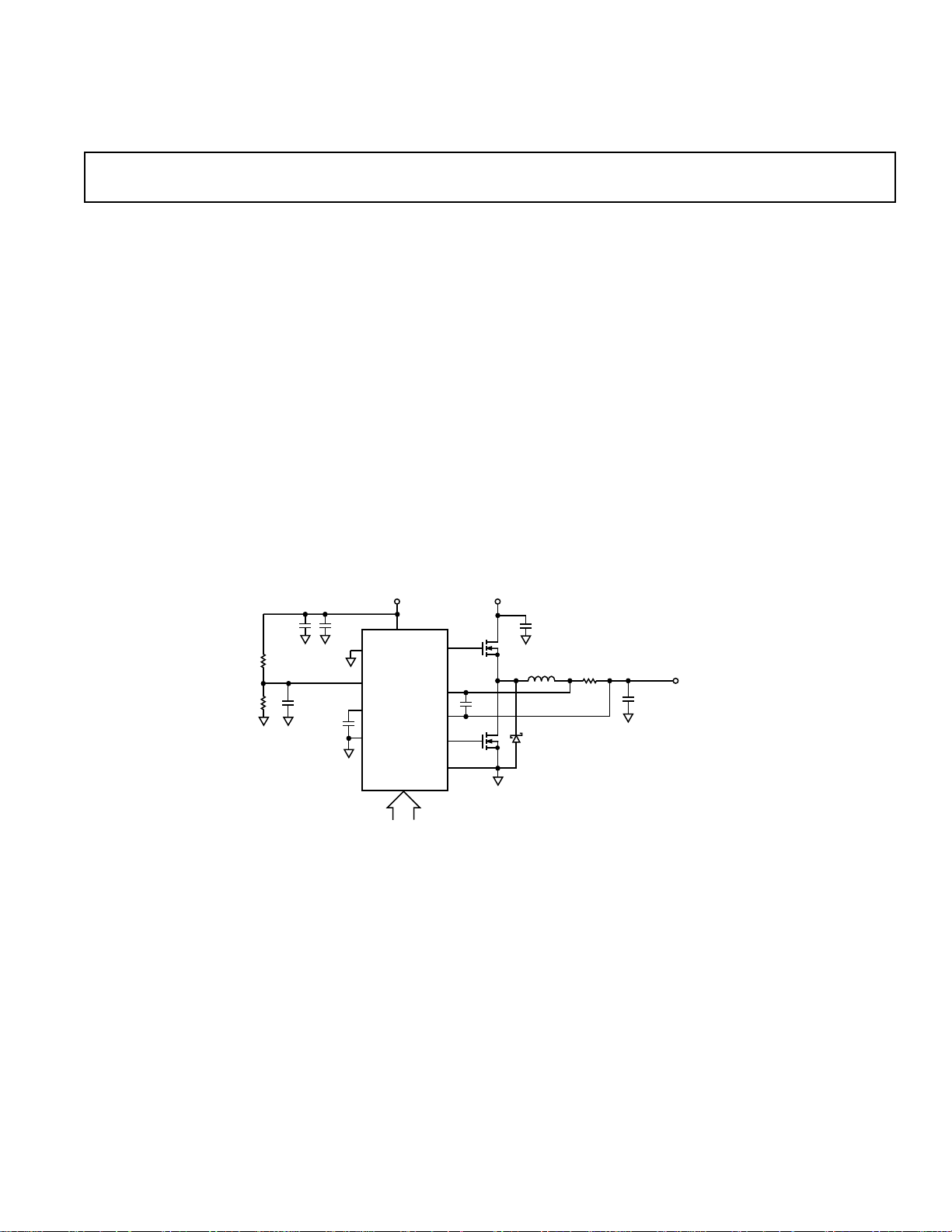

V

CC

+12V

C

COMP

150pF

1mF

SD

ADP3152

CMP

C

T

AGND

VID0–VID4

V

CC

DRIVE1

SENSE+

SENSE–

DRIVE2

PGND

22mF

R1

R2

IRL3103

1nF

IRL3103

GENERAL DESCRIPTION

The ADP3152 is a highly efficient synchronous switching regulator controller optimized for Pentium II Processor applications

where 5 V is stepped down to a digitally controlled output voltage between 1.8 V and 3.5 V. Using a 5-bit DAC to read a

voltage identification (VID) code directly from the processor,

the ADP3152 uses a current mode constant off-time architecture to generate its precise output voltage.

The ADP3152 drives two N-channel MOSFETS in a synchronous rectified buck converter, at a maximum switching frequency of 250 kHz. Using the recommended loop compensation

and guidelines, the ADP3152 provides a dc/dc converter that

meets Intel’s stringent transient specifications with a minimum

number of output capacitors and smallest footprint. Additionally,

the current mode architecture also provides guaranteed short

circuit protection and adjustable current limiting.

V

IN

+5V

+

C

IN

L

R

2.5mH

10BQ015

SENSE

6.7mV

V

O

1.8V–3.5V

+

14A

C

O

5-BIT CODE

Figure 1. Typical Application

Pentium is a registered trademark of Intel Corporation.

All other trademarks are the property of their respective holders.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998

ADP3152–SPECIFICATIONS

(08C ≤ TA ≤ +708C, V

= 12 V, VIN = 5 V, unless otherwise noted)

CC

Parameter Symbol Conditions Min Typ Max Units

OUTPUT ACCURACY

1.8 V Output Voltage V

O

With Respect to Nominal –1.0 1.0 %

2.8 V Output Voltage Output Voltage (Figure 13) –1.0 1.0 %

3.5 V Output Voltage –1.0 1.0 %

OUTPUT VOLTAGE LINE ∆V

O

I

= 10 A (Figure 2)

LOAD

REGULATION VIN = 4.75 V to 5.25 V 0.05 %

OUTPUT VOLTAGE LOAD ∆V

O

REGULATION 200 mA < I

INPUT DC SUPPLY CURRENT

Normal Mode I

1

Q

Shutdown T

(Figure 2)

< 14 A 0.1 %

LOAD

VSD = 0.8 V 3.7 4.5 mA

= +25°C, VID Pins Floating 140 250 µA

A

CURRENT SENSE THRESHOLD

VOLTAGE V8–V

VID PINS THRESHOLD V

, V1–V

16

7

V7 Forced to V

4

– 3% 125 145 165 mV

OUT

Low 0.6 V

High 2.0 V

VID PINS INPUT CURRENT I16, I1–I

VID0–VID4 PULL-UP RESISTANCE R

C

PIN DISCHARGE CURRENT I

T

OFFTIME t

DRIVER OUTPUT TRANSITION t

VID

9

OFF

, t

R

F

TIMES T

POSITIVE POWER GOOD TRIP POINT V

NEGATIVE POWER GOOD TRIP POINT V

POWER GOOD RESPONSE TIME t

CROWBAR TRIP POINT V

PWRGD

PWRGD

PWRGD

CROWBAR

VID

4

= 0 V 110 220 µA

20 30 kΩ

T

= +25°C

A

in Regulation 65 µA

V

OUT

V

= 0 V 2 10 µA

OUT

C

= 150 pF 1.8 2.45 3.2 µs

T

CL = 7000 pF (Pins 13, 14)

= +25°C 120 200 ns

A

Output Coming Into Regulation 5 8 %

Output Coming Into Regulation –8 –5 %

500 µs

% Above Output Voltage 9 15 24 %

ERROR AMPLIFIER

OUTPUT IMPEDANCE RO

ERR

145 kΩ

ERROR AMPLIFIER

TRANSCONDUCTANCE GM

ERR

2.2 mmho

ERROR AMPLIFIER MINIMUM

OUTPUT VOLTAGE V

CMPMIN

V7 Forced to V

+ 3% 0.8 V

OUT

ERROR AMPLIFIER MAXIMUM

OUTPUT VOLTAGE V

CMPMAXV7

ERROR AMPLIFIER BANDWIDTH –3 dB BW

ERR

Forced to V

– 3% 2.4 V

OUT

CMP = Open 500 kHz

SHUTDOWN (SD) PIN

Low Threshold SD

High Threshold SD

Input Current SD

NOTES

1

Dynamic supply current is higher due to the gate charge being delivered to the external MOSFETS.

All limits at temperature extremes are guaranteed via correlation using standard quality control methods.

Specifications are subject to change without notice.

L

H

IB

Part Active 0.6 V

Part in Shutdown 2.0 V

10 µA

–2– REV. 0

ADP3152

WARNING!

ESD SENSITIVE DEVICE

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1–4, 16 VID1–VID4, VD0 Voltage Identification DAC Input Pins. These pins are internally pulled up to V

logic one if left open. Leaving all five DAC inputs open results in placing the ADP3152 into

shutdown.

5 AGND Analog Ground Pin. This pin must be routed separately to the (–) terminal of C

6 SD Shutdown Pin. A logic high will place the ADP3152 in shutdown and disable the output. This

pin is internally pulled down.

7 SENSE– Connects to the internal resistor divider which, along with the VID code, sets the output volt-

age. Pin 7 is also the (–) input for the current comparator.

8 SENSE+ The (+) input for the current comparator. A threshold between Pins 8 and 7 set by the error

9C

T

amplifier in conjunction with R

External Capacitor CT from Pin 9 to ground sets the off time of the device.

, sets the current trip point.

SENSE

10 CMP Error Amplifier Compensation Point. The current comparator threshold increases with the Pin

10 voltage.

11 PWRGD Power Good Pin. An open drain signal to indicate that the output voltage is within a ±5% regu-

lation band.

12 V

CC

Input Voltage Pin.

13 DRIVE2 Gate Drive for the bottom synchronous N-channel MOSFET. The voltage at Pin 13 swings

from ground to V

CC

.

14 DRIVE1 Gate Drive for the top primary N-channel MOSFET. The voltage at Pin 14 swings from ground

to V

.

CC

15 PGND Driver Power Ground. Connects to the source of the bottom N-channel MOSFET and to the

(–) terminal of CIN.

providing a

REG

.

OUT

ABSOLUTE MAXIMUM RATINGS*

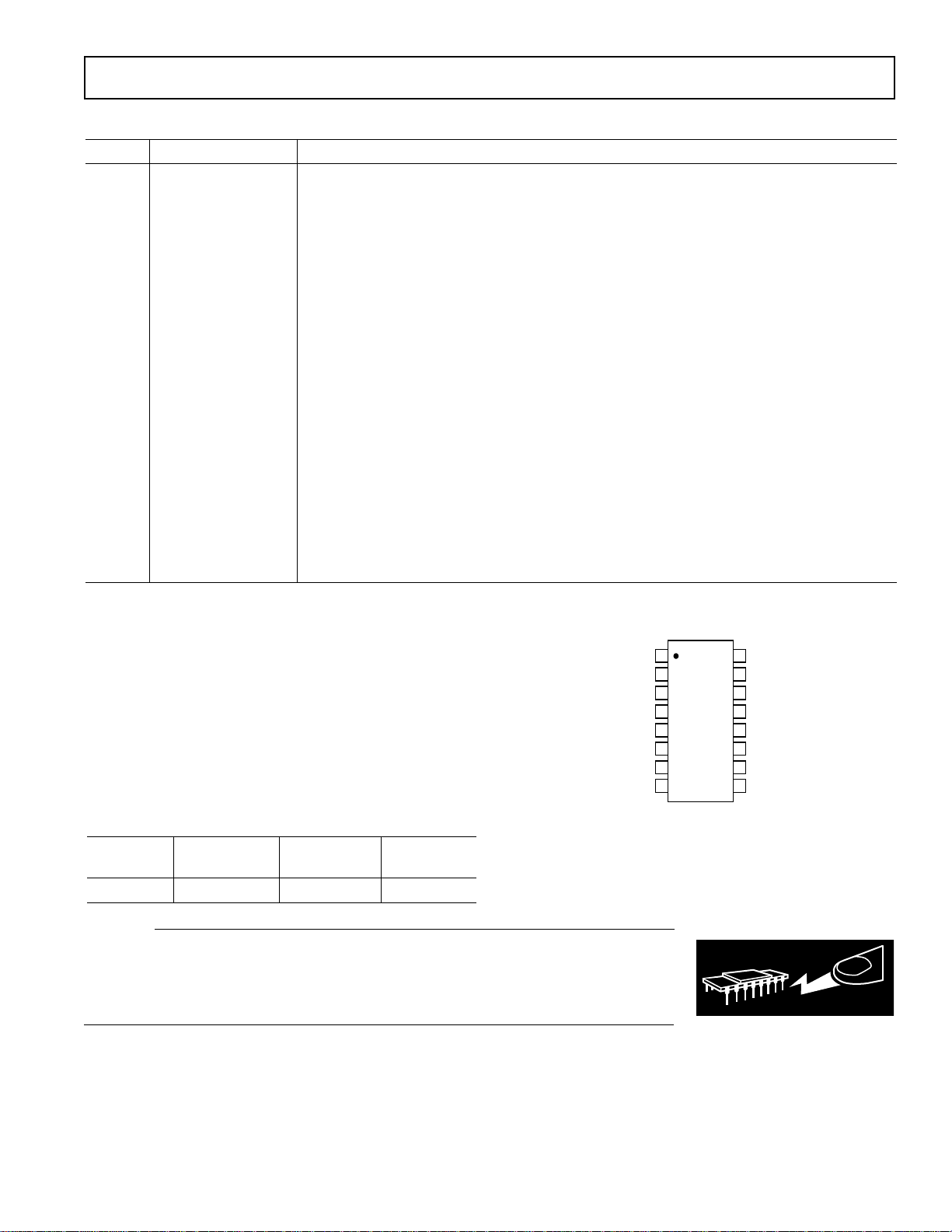

PIN CONFIGURATION

Input Supply Voltage (Pin 12) . . . . . . . . . . . . –0.3 V to +16 V

VID0–VID4, SD, PWRGD, CMP, CT . . . . . . . –0.3 V to V

DRIVE1, DRIVE2, SENSE+, SENSE– . . . . . . –0.3 V to V

Operating Temperature Range . . . . . . . . . . . . . 0°C to +70°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

␣ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110°C/W

θ

JA

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . .+300°C

*This is a stress rating only; operation beyond these limits can cause the device to

be permanently damaged.

CC

CC

VID1

VID2

VID3

VID4

AGND

SD

SENSE–

SENSE+

1

2

3

ADP3152

4

TOP VIEW

5

(Not to Scale)

6

7

8

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

ADP3152AR 0°C to +70°C 16-Lead SOIC R-16A/SO-16

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the ADP3152 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

16

15

14

13

12

11

10

9

VID0

PGND

DRIVE1

DRIVE2

V

CC

PWRGD

CMP

C

T

–3–REV. 0

ADP3152

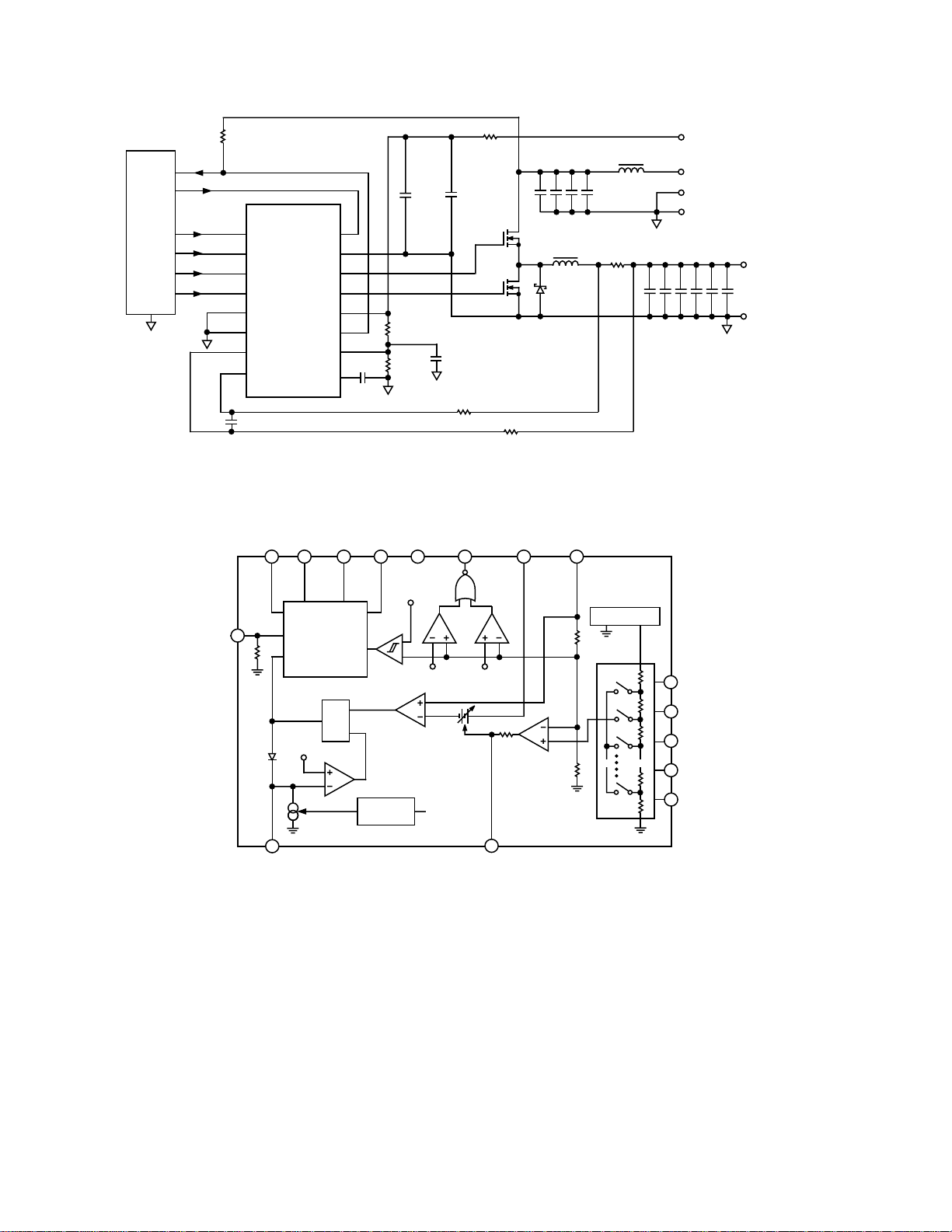

mP

SYSTEM

2nF

C

1mF

COMP

220V

22V

IRL3103

IRL3103

220V

3 32700mF/10V

++++

L1

2.5mH

10BQ015

1mF

R

SENSE

6.7mV

L2

1.7mH

V

+5V RTN

+12V RTN

2700mF 3 6 (10V)

+ + + + +

+

100kV VCC + 12V

+

22mF

ADP3152

1

2

3

4

5

6

7

8

VID1

VID2

VID3

VID4

AGND

SD

SENSE–

SENSE+

VID0

PGND

DRIVE1

DRIVE2

V

PWRGD

CMP

C

16

15

14

13

12

CC

11

10

9

T

C

T

150pF

R1

150kV

R2

39kV

1nF

Figure 2. Typical Application for Pentium II

SENSE–

8

7

ADP3152

REFERENCE

2R

1.20V

16

VID0

1

VID1

2

g

m

V

REF

R

VID2

3

VID3

SD

DRIVE1 DRIVE2 PGND

V

CC

12 14 13 15

NONOVERLAP

6

IN

V

T2

DRIVE

CROWBAR

S

Q

R

CMPT

V

REF

CMPI

AGND

+ 15%

V

REF

PWRGD

+ 5% V

V

T1

SENSE+

115

DELAY

– 5%

REF

IN

+ 5V

V

O

1.8V–3.5V

0-14A

RTN

4

OFF-TIME

CONTROL

9

C

T

SENSE–

10

CMP

DAC

VID4

Figure 3. Functional Block Diagram

–4– REV. 0

Loading...

Loading...