Analog Devices ADP3088ARM Datasheet

PRELIMINARY TECHNICAL DATA

a

1 MHz, 750 mA Buck Regulator

Preliminary Technical Data ADP3088

FEATURES

1 MHz PWM Frequency

Automatic PWM to Power Saving Mode at Light Load

Fully Integrated 1 A Power Switch

3% Output Regulation Accuracy over Temperature,

Line, and Load

100% Duty Cycle Operation

Simple Compensation

Output Voltage: 1.25 V to 10.5 V

Small Inductor and MLC Capacitors

Low Quiescent Current while Pulse Skipping

Thermal Shutdown

Fully Integrated Soft Start

Cycle-by-cycle Current Limit

APPLICATONS

PDAs and Palmtop Computers

Notebook Computers

PCMCIA Cards

Bus Products

Portable Instruments

IN

IN

COMP

GND

GND

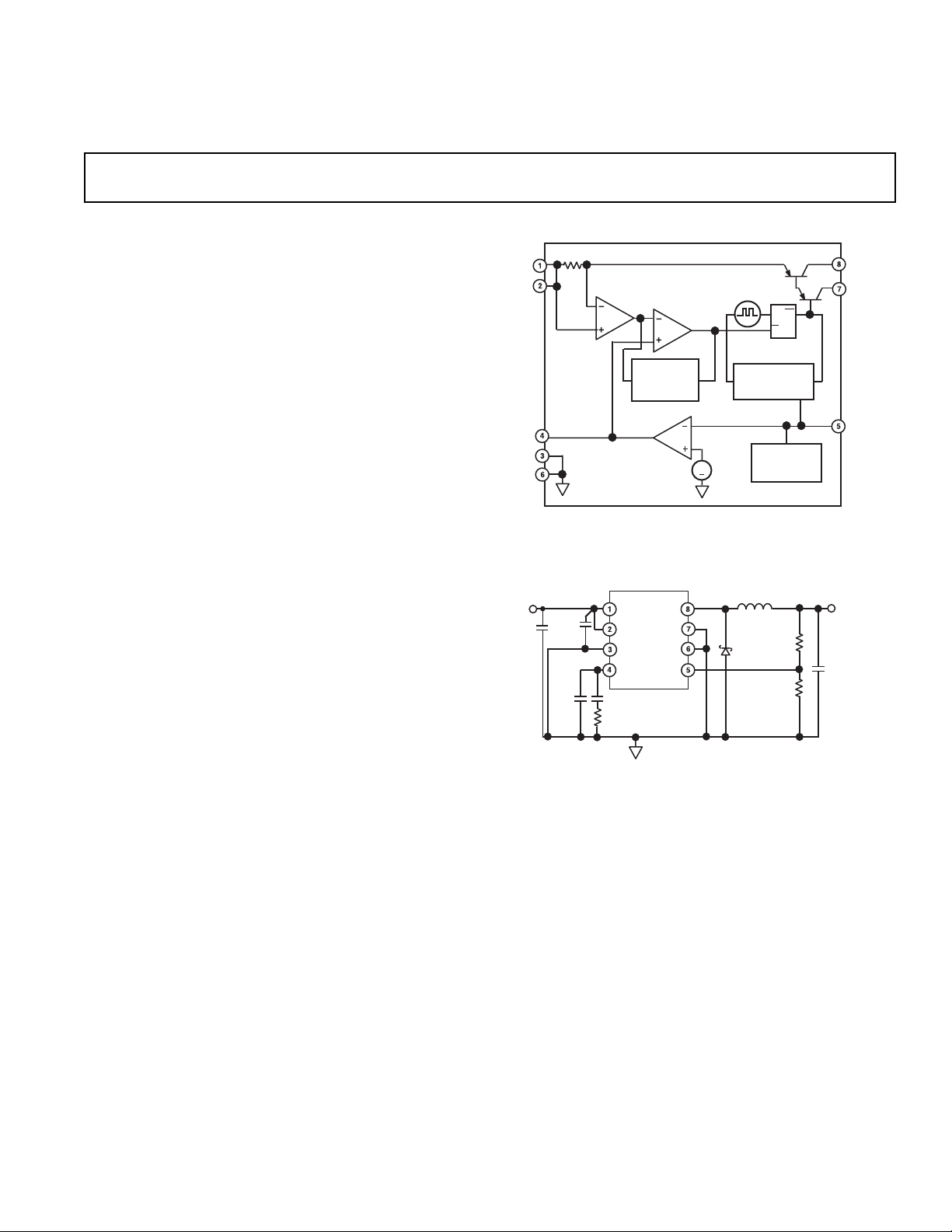

FUNCTIONAL BLOCK DIAGRAM

CURRENT

SENSE

AMP

PWM

COMPARATOR

PROTECTION

LOGIC

(ILIM, OT)

ERROR

AMP

g

m

+

REF

1.245V

1MHz

SQ

R

RUN/STOP

COMPARATORS

SOFT-START

TIMER

SW

DRV

FB

GENERAL DESCRIPTION

The ADP3088 is a high frequency, non-synchronous PWM

step-down DC-DC regulator with an integrated 1A power

switch in a space-saving MSOP8 package. It provides high

efficiency, excellent dynamic response, and is very simple

to use.

The ADP3088’s 1 MHz switching frequency allows for

small, inexpensive external components, and the current

mode control loop is simple to compensate and eases noise

filtering. It operates in PWM current mode under heavy

loads and saves energy at lighter loads by switching automatically into Power Saving mode. Soft start is integrated

completely on chip, as is the cycle-by-cycle current limit.

Capable of operating from 2.5 V to 11 V input, it is ideal for

many applications, including portable, battery power applications, where local point-of-use power regulation is required. Supporting output voltages down to 1.25 V, the

ADP3088 is ideal to generate low voltage rails, providing

the optimal solution in its class for delivering power efficiently, responsively, and simply with minimal printed circuit board area.

The device is specified over the industrial temperature

range of -40 °C to +85°C.

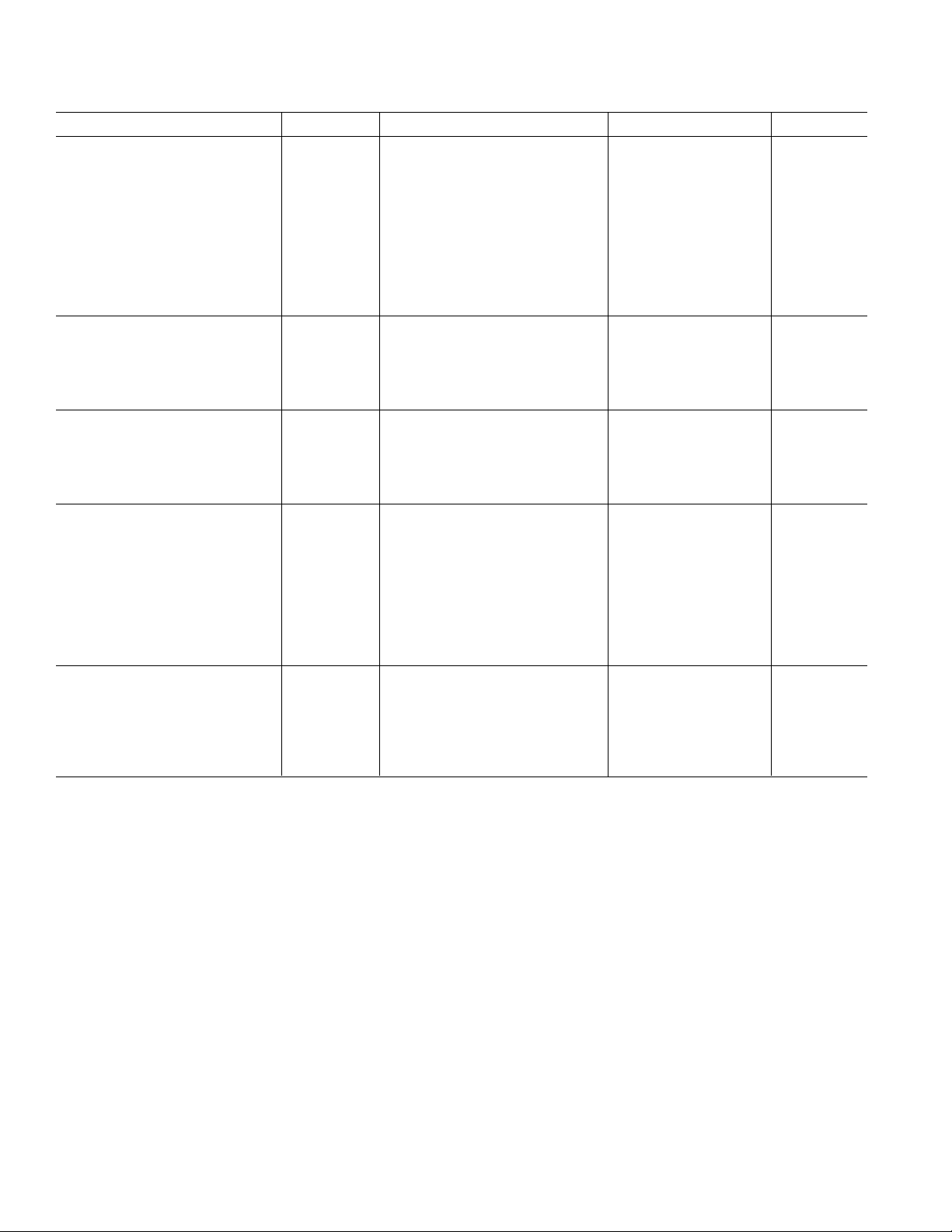

VIN

3.3V

10µF

0.1µF

4.7pF

220pF

20kΩ

ADP3088

IN

IN

GND

COMP

SW

DRV

GND

FB

3.3µH

1N5817

10.0kΩ

22.4kΩ

Figure 1. Typical Application

10µF

VOUT

1.8V

REV. PrK 3/28/02

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor

for any infringements of patents or other rights of third parties which may

result from its use. No license is granted by implication or otherwise under any

patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 Analog Devices, Inc., 2002

PRELIMINARY TECHNICAL DATA

1

ADP3088–SPECIFICATIONS

Parameter Symbol Conditions Min Typ Max Units

SUPPLY

Input Voltage Range V

Quiescent Current Operating I

Quiescent Current Operating I

Shutdown I

Ground Current I

Normal Operation VIN = 11 V, IL = 500 mA, 2.5 3.6 mA

Thermal Shutdown Threshold T

OSCILLATOR

Oscillator Frequency f

Minimum Sleep Duty Cycle D

Maximum Duty Cycle D

Wake up Hysteresis V

OUTPUT SWITCH

Switch On Voltage V

Current Limit Threshold I

Leakage Current VIN = 12 V 0.5 µA

ERROR AMPLIFIER

Reference Voltage Accuracy V

Reference Voltage Line FB = COMP, .02 %/V

Regulation V

Feedback Input Bias Current I

Sink/Source Current I

Short Circuit Current I

Transconductance gm,

MODULATOR

Transconductance gm,

Control Offset Voltage V

Soft Start Time t

Shutdown Threshold Voltage V

Slope Compensation m

NOTES

1 All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC).

2 For higher efficiency operation, tie the DRV pin to the output for IL < 250 mA, and VIN > 3 V.

3 V(IN) - V(SW), includes voltage drop across internal current sensor.

Specifications subject to change without notice.

IN

Q

Q

SD

2

GND

SD

SW

PSM

MAX

HYST

3

IO

LIM

REF

FB

COMP

COMP, SD

EA

MOD

PWM, OS

SS

COMP, SD

SC

(VIN = +3.3 V, TA = -40°C to +85°C, unless otherwise noted)

DRV = GND 2.5 11 V

VIN = 10 V, IL = 500 mA, 6 mA

DRV = GND

No load 150 250 µA

V

= 0 V 15 40

COMP

DRV = 2 V

160 °C

0.75 1 1.25 MHz

IL = 500 mA 14 %

100 %

FB voltage drops below V

REF

20 30 40 mV

IL = 500 mA, FB and DRV = 0.25 0.4 V

GND

1.0 1.2 1.4 A

FB = COMP 1.222 1.245 1.265 V

= 3 V to 12 V

IN

soft start expired -50 1 50 nA

35 60 85 µA

V

= 0 V, activating 20 40 µA

COMP

shutdown

FB = COMP 480 µA/V

V

COMP

to I

L

1 A/V

0.90 V

250 600 µs

340 750 mV

Effectively summed to I

SW

0.7 A/µs

–2– REV. PrK

PRELIMINARY TECHNICAL DATA

PRELIMINARY TECHNICAL DATA

ADP3088

ABSOLUTE MAXIMUM RATINGS*

Input Supply Voltage ............................... –0.3 V to +12 V

Voltage on any pin with respect to GND .. –0.3 V to +12 V

(voltage on any pin may not exceed V

)

IN

Operating Ambient Temperature Range .. –40°C to +85°C

Operating Junction Temperature ......................... +125°C

(4-layer board)........................................... +116°C/W

θ

JA

θ

(2-layer board)........................................... +159°C/W

JA

Storage Temperature Range .................. –65°C to +150°C

Lead Temperature Range (Soldering, 10 sec.) ..... +300°C

Vapor Phase (60 sec) ........................................ +215°C

Infrared (15 sec) ............................................... +220°C

*This is a stress rating only; operation beyond these limits can cause the device

to be permanently damaged. Unless otherwise specified, all voltages are

referenced to GND.

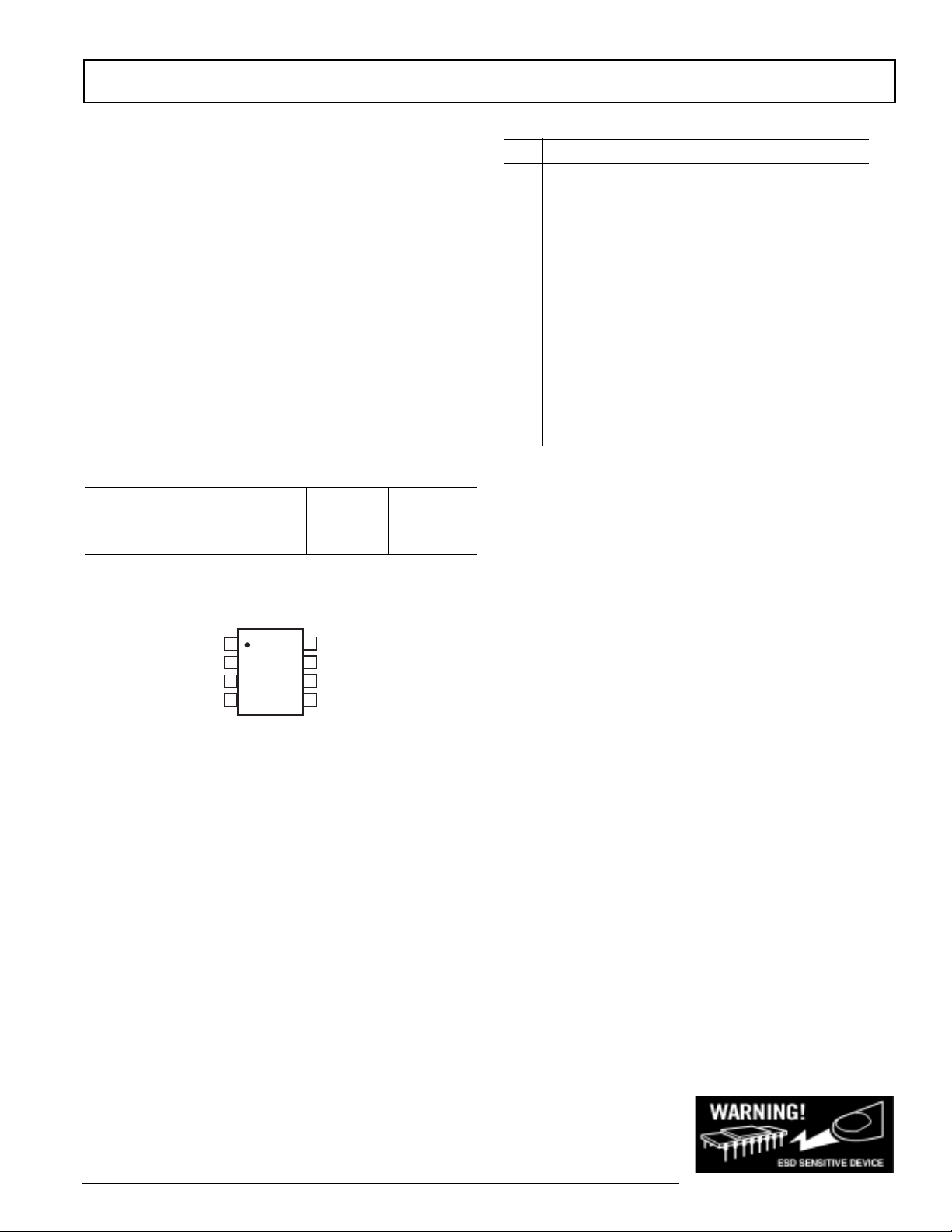

ORDERING GUIDE

Temperature Package Branding

Model Range Option Information

ADP3088ARM -40°C to +85°C MSOP-8 P0A

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1, 2 IN Power Supply Input. Both pins

must be connected.

3,6 GND Ground. Both pins must be con-

nected.

4 COMP Feedback Loop Compensation

and Shutdown Input. An open

drain or collector used to pull

the pin to ground will shutdown

the device.

5 FB Feedback Voltage Sense Input.

This pin senses the voltage via

an external resistor divider.

7 DRV This pin provides a separate

path for drive current to be connected to ground.

8 SW Switching Output.

PIN CONFIGURATION

GND

COMP

1

IN

2

IN

ADP3088

3

4

8

SW

7

DRV

6

GND

5

FB

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the device features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–3–REV. PrK

ADP3088

PRELIMINARY TECHNICAL DATA

THEORY OF OPERATION

The ADP3088 is a fixed frequency buck switching regulator in an MSOP-8 package using an external Schottky rectifier. It features an integrated 1A power switch and switches

at 1MHz. ADP3088 utilizes PWM operation and incorporates soft-start for controlled start-up sequence and over

temperature switch protection. The ADP3088 draws low

current while running in power saving mode, and even

lower current in shutdown.

Refer to the functional block diagram on page 1. The system shown is configured for a 1.8 V output using a 10 µH

inductor. At the beginning of a cycle the 1 MHz oscillator

enables an SR latch, enabling the internal 1 A power

switch. The current sense amplifier and the protection logic

block monitor the current flowing between the IN and SW

pins. The switch is turned off when the current reaches a

level determined by the protection logic block or PWM

comparator, whichever is lower. The error amplifier measures the output voltage through an external resistor divider

tied to the FB pin. This amplifier servos the switch current

to regulate the FB pin voltage to 1.245 V. An internal regulator provides power to the control circuitry. The COMP

pin can be used to shutdown the ADP3088. When pulled

low it turns off the internal regulator, thus biasing down the

chip, reducing the input current and disconnecting the

output from the input. Anti-saturation circuitry is used to

drive the switch to the edge of saturation. This allows the

driver to quickly switch at 1 MHz and maintain good efficiency. And for improved efficiency, the DRV pin may be

connected to the output provided that the input voltage is

at least 1 V greater than the output.

If the output load increases, the error amplifier will detect a

lower voltage on the FB pin, via the resistor divider on the

output, and send a signal to the PWM comparator to increase the on time of the switch. This in effect increases the

duty cycle and provides more current to drive the increased

load during the transient event, until a new operating point

is established.

Reference

The ADP3088 incorporates an internal bandgap reference,

it includes curvature correction for extremely low temperature coefficient. The reference can be disabled by grounding the COMP pin which also turns off the bias for the rest

of the chip.

Error Amplifier

The error amplifier provides a control voltage to the PWM

stage to set the peak inductor current which sets the output

current of the regulator. It is a g

is a current to the COMP pin.

Protection Logic

The protection logic block provides current limit and overtemperature protection. The over temperature protection is

enabled when the temperature of the chip exceeds a specified preset temperature; the switch will be disabled until the

temperature drops below a specified level, then normal

operation will resume. The thermal shutdown only stops

switching, but does not put the chip to power saving mode,

nor does it re-initiate soft start. As the chip cools slightly, it

will cycle in and out of thermal shutdown rapidly, maintaining the die temp at 150°C, but allowing the output voltage

amplifier in that its output

m

and current to swing up and down. The current limit protection overrides the PWM comparator; if this occurs then

the switch pulse will be terminated and the soft start mode

will be reset.

Current Sense Amplifier

The voltage on the internal current sense resistor is sensed

and passed to the ramp input of the PWM comparator.

This current sense signal is also passed to the current limit

comparator for peak current limit shutdown . At current

limit the soft-start capacitor is reset and soft-start is reinitiated. The current limit is normally 1.2 peak switch

current. Slope compensation is added to ADP3088 to stabilize the loop. A generated ramped signal is summed with

the current sense signal to provide slope compensation.

Slope compensation is needed to close the inner loop so

subharmonic oscillation is avoided. The ramp is reset with

each clock cycle so that the ADP3088 is capable of true

100% duty cycle.

Run/Stop Comparators

This block creates the 1 MHz signal sent to the SR latch

which is used for the switching frequency. It also takes the

FB voltage and decides when to go into and wake up from

power saving mode. The decision to induce power saving

mode is based upon duty ratio. During steady-state continuous operation, the duty ratio of a PWM buck regulator

is simply a function of input/output voltage ratio, with second order effects including the voltage drop of the internal

switch and the external diode. Once the load drops to a

certain point, discontinuous operation occurs, and the duty

ratio begins to modulate to maintain regulation. In the

ADP3088, the regulator goes to sleep when the integrated

duty ratio measurements drops to less than half of the minimum expected integrated duty ratio. The minimum expected duty ratio occurs at max input voltage, min output

voltage in continuous mode operation.

PWM Comparator

The PWM comparator looks at the signal from the current

sense amplifier and the error amplifier to determine the

correct switch on time to regulate the output voltage under

a given load.

Soft-Start Timer

Soft start will prevent saturating the inductor which could

cause uncontrolled overshoot of the output voltage and

electrical stress to the system at start up. When first powered up, an internal soft start capacitor is discharged and

the soft start circuitry provides a gradually decaying offset

to the error amplifier to prevent it from saturating and from

commanding maximum switch current to charge the output

capacitor. The output voltage approaches the final regulation voltage with a smooth exponential decay. This will

reduce electrical stress to the system.

Output

The output stage contains the bipolar power switch, and

the circuits necessary to switch it on and off quickly. The

pass switch is driven to the edge of saturation and the result

is a fast switching response and low switch resistance. For

improved efficiency, the DRV pin may be connected to the

output provided that the input voltage is at least 1 V higher

than the output. This will send the current needed to drive

the bipolar switch to the output load instead of routing it to

–4– REV. PrK

Loading...

Loading...