Dual 3 A, 20 V Synchronous Step-Down

Regulator with Integrated High-Side

FEATURES

Input voltage: 4.5 V to 20 V

±1% output accuracy

Integrated 90 mΩ typical high-side MOSFET

Flexible output configuration

Dual output: 3 A/3 A

Parallel single output: 6 A

Programmable switching frequency: 250 kHz to 1.2 MHz

External synchronization input with programmable phase

shift, or internal clock output

Selectable PWM or PFM mode operation

Adjustable current limit for small inductor

External compensation and soft start

Startup into precharged output

APPLICATIONS

Communications infrastructure

Networking and servers

Industrial and instrumentation

Healthcare and medical

Intermediate power rail conversion

DC-to-dc point of load applications

MOSFET

ADP2323

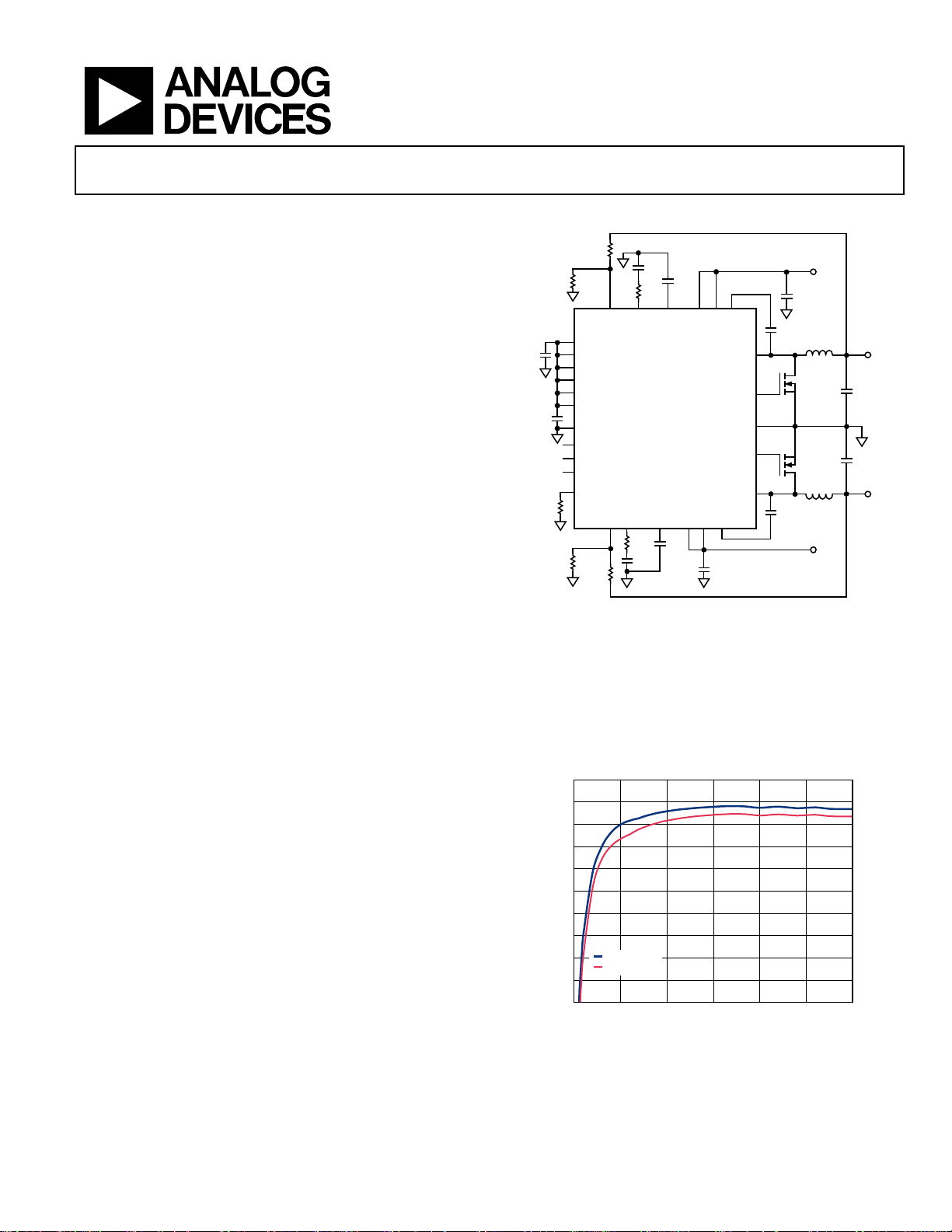

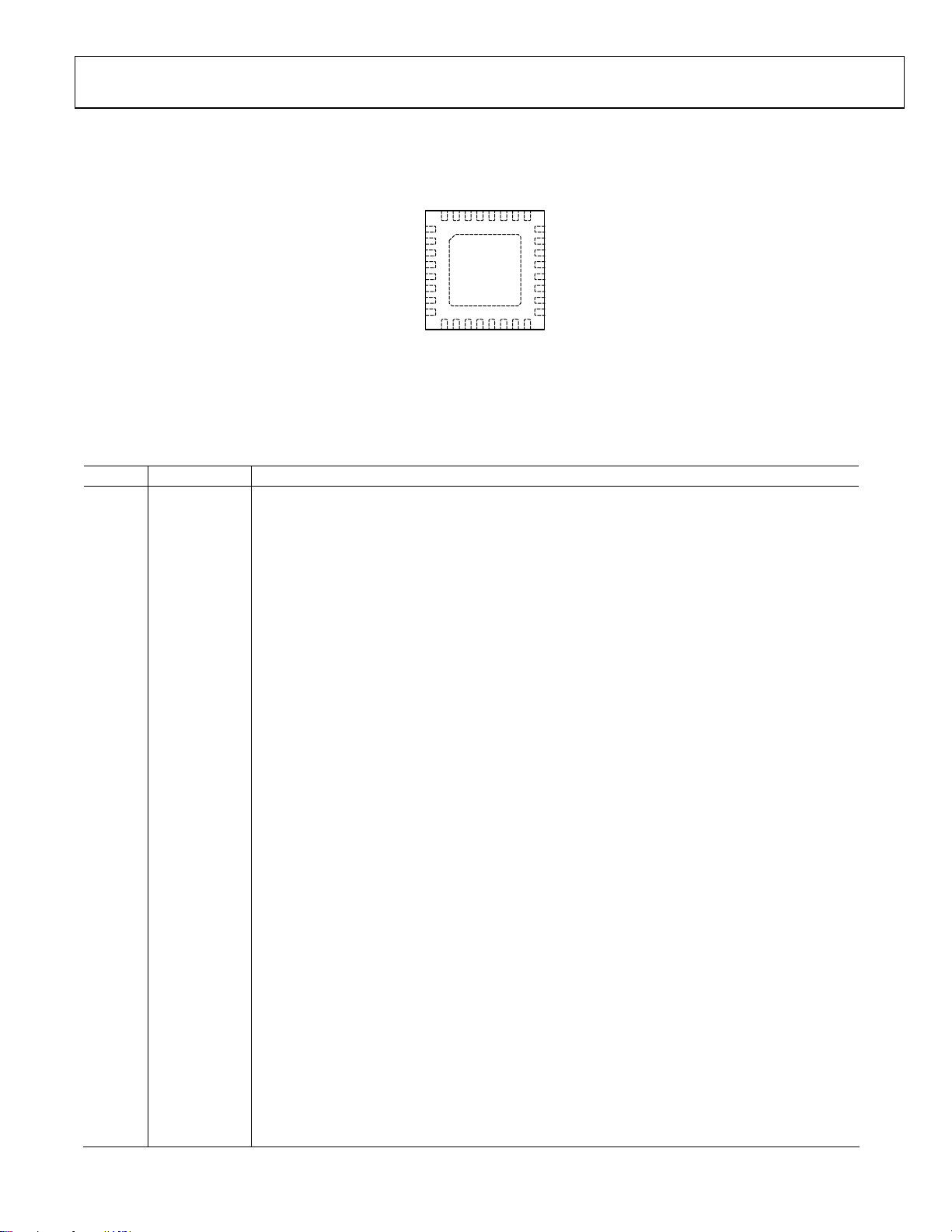

TYPICAL APPLICATION CIRCUIT

R

TOP1

C

FB1

FB2

C1

R

C1

COMP1

ADP2323

COMP2

R

C2

C

C2

C

SS1

SS1

EN1

BST1

PVIN1

SW1

M1

DL1

PGND

DL2

M2

SW2

SS2

EN2

PVIN2

BST2

C

SS2

C

IN2

R

BOT1

DRV

R

OSC

R

BOT2

INTVCC

MODE

SCFG

TRK2

TRK1

VDRV

GND

PGOOD2

PGOOD1

SYNC

RT

R

TOP2

C

INT

C

Figure 1.

C

C

BST1

BST2

V

IN

C

IN1

V

L1

OUT1

C

OUT1

C

OUT2

V

OUT2

L2

V

IN

09357-001

GENERAL DESCRIPTION

The ADP2323 is a full featured, dual output, step-down dc-todc regulator based on current-mode architecture. The ADP2323

integrates two high-side power MOSFETs and two low-side drivers

for the external N-channel MOSFETs. The two pulse-width modulation (PWM) channels can be configured to deliver dual 3 A

outputs or a parallel-to-single 6 A output. The regulator operates

from input voltages of 4.5 V to 20 V, and the output voltage can

be as low as 0.6 V.

The switching frequency can be programmed between 250 kHz

and 1.2 MHz, or synchronized to an external clock to minimize

interference in multirail applications. The dual PWM channels

run 180° out of phase, thereby reducing input current ripple as

well as reducing the size of the input capacitor.

The bidirectional synchronization pin can be programmed at

a 60°, 90°, or 120° phase shift, providing the possibility for a

stackable multiphase power solution.

The ADP2323 can be set to operate in pulse-frequency modulation

(PFM) mode at a light load for higher efficiency or in forced

PWM for noise sensitive applications. External compensation

and soft start provide design flexibility. Independent enable

inputs and power good outputs provide reliable power sequencing.

To enhance system reliability, the device also includes undervoltage

lockout (UVLO), overvoltage protection (OVP), overcurrent protection (OCP), and thermal shutdown (TSD).

The ADP2323 operates over the −40°C to +125°C junction

temperature range and is available in a 32-lead LFCSP_WQ

package.

100

95

90

85

80

75

70

EFFICIENCY (%)

65

V

60

55

50

0 0.5 1.0 1.5 2.0 2.5 3.0

Figure 2. Efficiency vs. Output Current at V

= 5V

OUT

V

= 3.3V

OUT

OUTPUT CURRENT (A)

= 12 V, fSW = 600 kHz

IN

09357-002

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADP2323

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Typical Application Circuit ............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Functional Block Diagram .............................................................. 3

Specifications..................................................................................... 4

Absolute Maximum Ratings............................................................ 6

Thermal Resistance ...................................................................... 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Typical Performance Characteristics ............................................. 9

Theory of Operation ...................................................................... 15

Control Scheme .......................................................................... 15

PWM Mode................................................................................. 15

PFM Mode................................................................................... 15

Precision Enable/Shutdown ...................................................... 15

Separate Input Voltages ............................................................. 15

Internal Regulator (INTVCC).................................................. 15

Bootstrap Circuitry .................................................................... 16

Low-Side Driver.......................................................................... 16

Oscillator ..................................................................................... 16

Synchronization.......................................................................... 16

Soft Start ...................................................................................... 16

Peak Current-Limit and Short-Circuit Protection................. 16

Voltage Tracking......................................................................... 17

Parallel Operation....................................................................... 17

Power Good................................................................................. 17

Overvoltage Protection.............................................................. 17

Undervoltage Lockout............................................................... 18

Thermal Shutdown .................................................................... 18

Applications Information.............................................................. 19

Input Capacitor Selection.......................................................... 19

Output Voltage Setting .............................................................. 19

Voltage Conversion Limitations............................................... 19

Current-Limit Setting................................................................ 19

Inductor Selection...................................................................... 19

Output Capacitor Selection....................................................... 20

Low-Side Power Device Selection............................................ 20

Programming UVLO Input ...................................................... 21

Compensation Components Design ....................................... 21

Design Example.............................................................................. 23

Output Voltage Setting .............................................................. 23

Current-Limit Setting................................................................ 23

Frequency Setting....................................................................... 23

Inductor Selection...................................................................... 23

Output Capacitor Selection....................................................... 23

Low-Side MOSFET Selection ................................................... 24

Compensation Components..................................................... 24

Soft Start Time Programming .................................................. 24

Input Capacitor Selection.......................................................... 24

External Components Recommendation.................................... 25

Typical Application Circuits ......................................................... 26

Outline Dimensions....................................................................... 31

Ordering Guide .......................................................................... 31

REVISION HISTORY

7/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 32

ADP2323

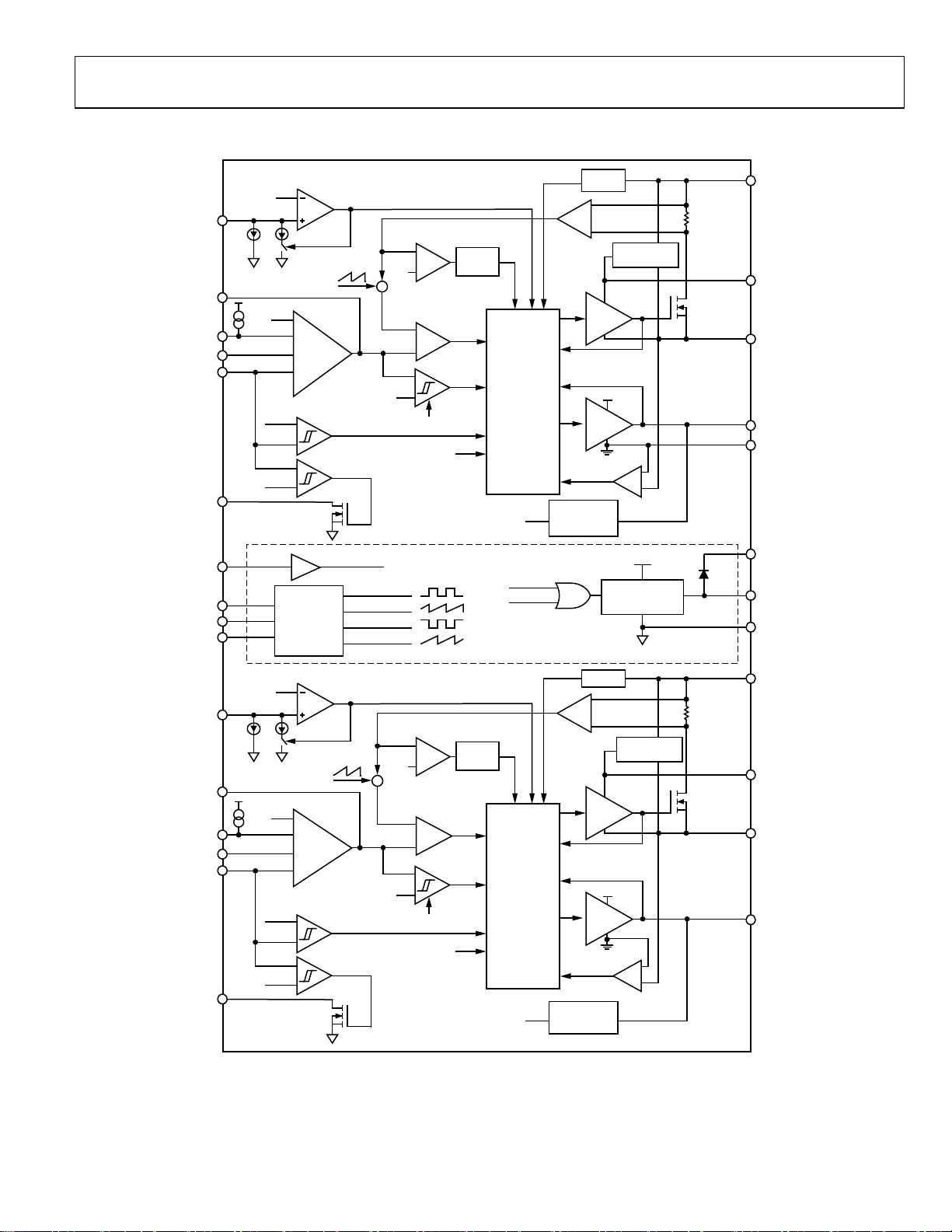

FUNCTIONAL BLOCK DIAGRAM

EN1

COMP1

SS1

TRK1

FB1

PGOOD1

MODE

SCFG

SYNC

RT

1.2V

4µA1µA

SLOPE RAMP1

0.6V

I

SS1

0.7V

0.54V

+

+

AMP1

+

–

OVP

–

+

–

+

OSCILLATOR

EN1_BUF

SKIP MODE

THRESHOLD

MODE_BUF

CLK1

SLOPE RAMP1

CLK2

SLOPE RAMP2

ADP2323

+

HICCUP

OCP

MODE

–

I1

MAX

Σ

+

CMP1

–

SKIP

–

CMP1

+

MODE_BUF

CLK1

CONTROL

LOGIC

AND MOSFET

DRIVER WITH

ANTICROSS

PROTECTION

I1

MAX

EN1_BUF

EN2_BUF

UVLO

+

A

CS1

–

DRIVER

VDRV

DRIVER

ZERO CURRENT

CMP

CURRENT-

LIMIT

SELECTION

5V REGULATO R

BOOST

REGULATOR

–

+

PVIN1

PVIN1

BST1

NFET1

SW1

DL1

PGND

VDRV

INTVCC

GND

EN2

COMP2

SS2

TRK2

FB2

PGOOD2

1.2V

4µA1µA

SLOPE RAMP2

0.6V

I

SS2

0.7V

0.54V

+

+

+

–

–

+

–

+

AMP2

OVP

EN2_BUF

Σ

SKIP MODE

THRESHOLD

UVLO

+

A

CS2

–

DRIVER

VDRV

CMP

BOOST

REGULATOR

–

+

NFET2

+

HICCUP

OCP

MODE

–

I2

MAX

+

CMP2

–

SKIP

–

CMP2

+

MODE_BUF

CLK2

CONTROL

LOGIC

AND MOSFET

DRIVER WITH

ANTICROSS

PROTECTION

I2

MAX

DRIVER

ZERO CURRENT

CURRENT-

LIMIT

SELECTION

PVIN2

BST2

SW2

DL2

09357-042

Figure 3. Functional Block Diagram

Rev. 0 | Page 3 of 32

ADP2323

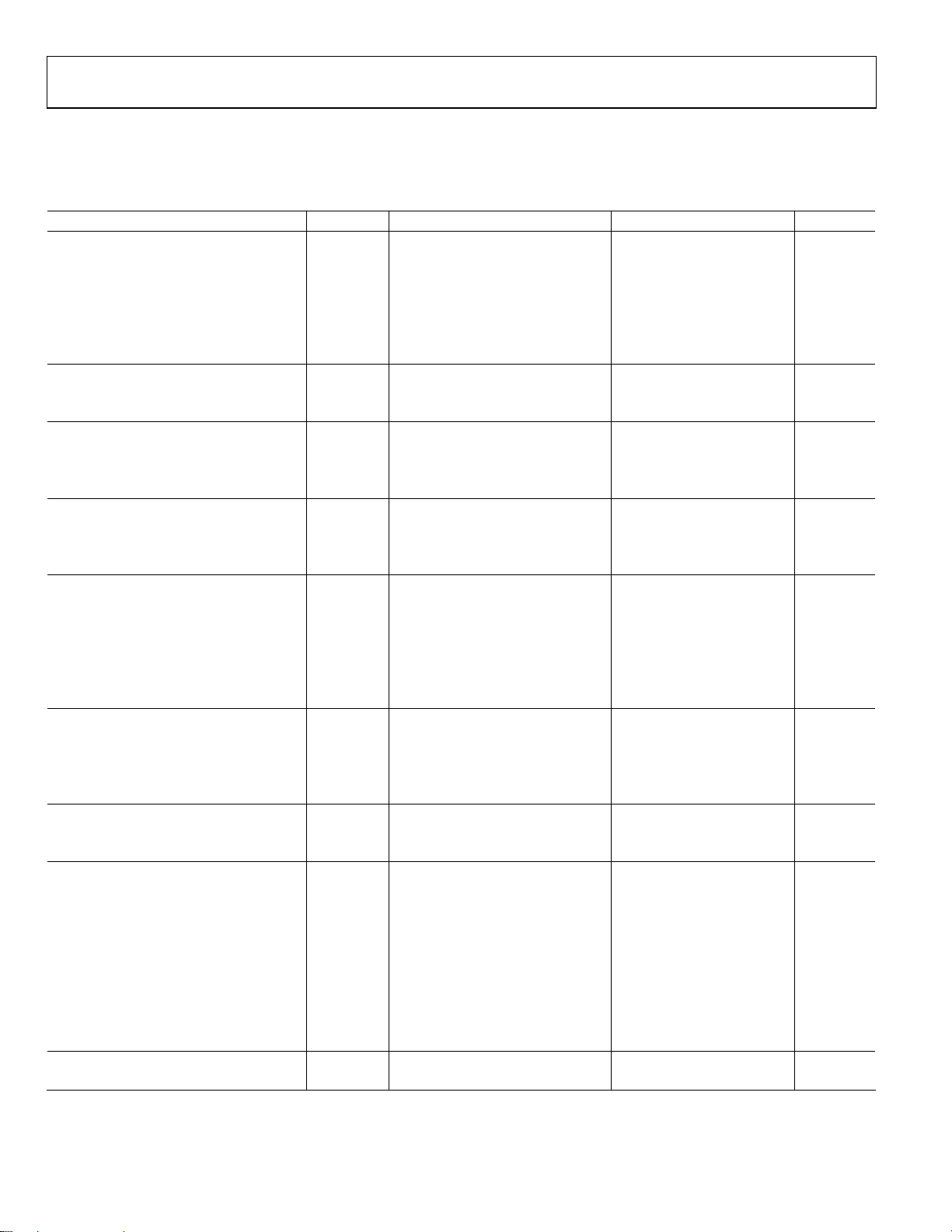

SPECIFICATIONS

PVIN1 = PVIN2 = 12 V at TJ = −40°C to +125°C, unless otherwise noted.

Table 1.

Parameters Symbol Test Conditions/Comments Min Typ Max Units

POWER INPUT (PVINx PINS)

Power Input Voltage Range V

Quiescent Current (PVIN1 + PVIN2) IQ MODE = GND, no switching 3 5 mA

Shutdown Current (PVIN1 + PVIN2) I

PVINx Undervoltage Lockout Threshold UVLO

PVINx Rising 4.3 4.5 V

PVINx Falling 3.5 3.8 V

FEEDBACK (FBx PINS)

FBx Regulation Voltage1 V

FBx Bias Current IFB 0.01 0.1 µA

ERROR AMPLIFIER (COMPx PINS)

Transconductance gm 230 300 370 µS

EA Source Current I

EA Sink Current I

INTERNAL REGULATOR (INTVCC PIN)

INTVCC Voltage 4.75 5 5.25 V

Dropout Voltage I

Regulator Current Limit 40 75 120 mA

SWITCH NODE (SWx PINS)

High-Side On Resistance2 V

SWx Peak Current Limit R

R

R

SWx Minimum On Time3 t

SWx Minimum Off Time3 t

LOW-SIDE DRIVER (DLx PINS )

Rising Time3 C

Falling Time3 C

Sourcing Resistor 4 6 Ω

Sinking Resistor 2 4.5 Ω

OSCILLATOR (RT PIN)

PWM Switching Frequency fSW R

PWM Frequency Range 250 1200 kHz

SYNCHRONIZATION (SYNC PIN)

SYNC Input SYNC configured as input

Synchronization Range 300 1200 kHz

Minimum On Pulse Width 100 ns

Minimum Off Pulse Width 100 ns

High Threshold 1.3 V

Low Threshold 0.4 V

SYNC Output SYNC configured as output

Frequency on SYNC Pin f

Positive Pulse Time 100 ns

SOFT START (SSx PINS)

SSx Pin Source Current ISS 2.5 3.5 4.5 µA

4.5 20 V

PVIN

EN1 = EN2 = GND 50 100 µA

SHDN

PVINx = 4.5 V to 20 V 0.594 0.6 0.606 V

FB

25 45 65 µA

SOURCE

25 45 65 µA

SINK

= 30 mA 400 mV

INTVCC

to VSW = 5 V 90 130 mΩ

BST

= floating, V

ILIM

= 47 kΩ, V

ILIM

= 15 kΩ, V

ILIM

130 ns

MIN_ON

150 ns

MIN_OFF

= 2.2 nF, see Figure 19 20 ns

DL

= 2.2 nF, see Figure 22 10 ns

DL

= 100 kΩ 530 600 670 kHz

OSC

f

CLKOUT

to VSW = 5 V 4 4.8 5.8 A

BST

to VSW = 5 V 2.3 3 3.7 A

BST

to VSW = 5 V 0.8 1.5 2.2 A

BST

kHz

SW

Rev. 0 | Page 4 of 32

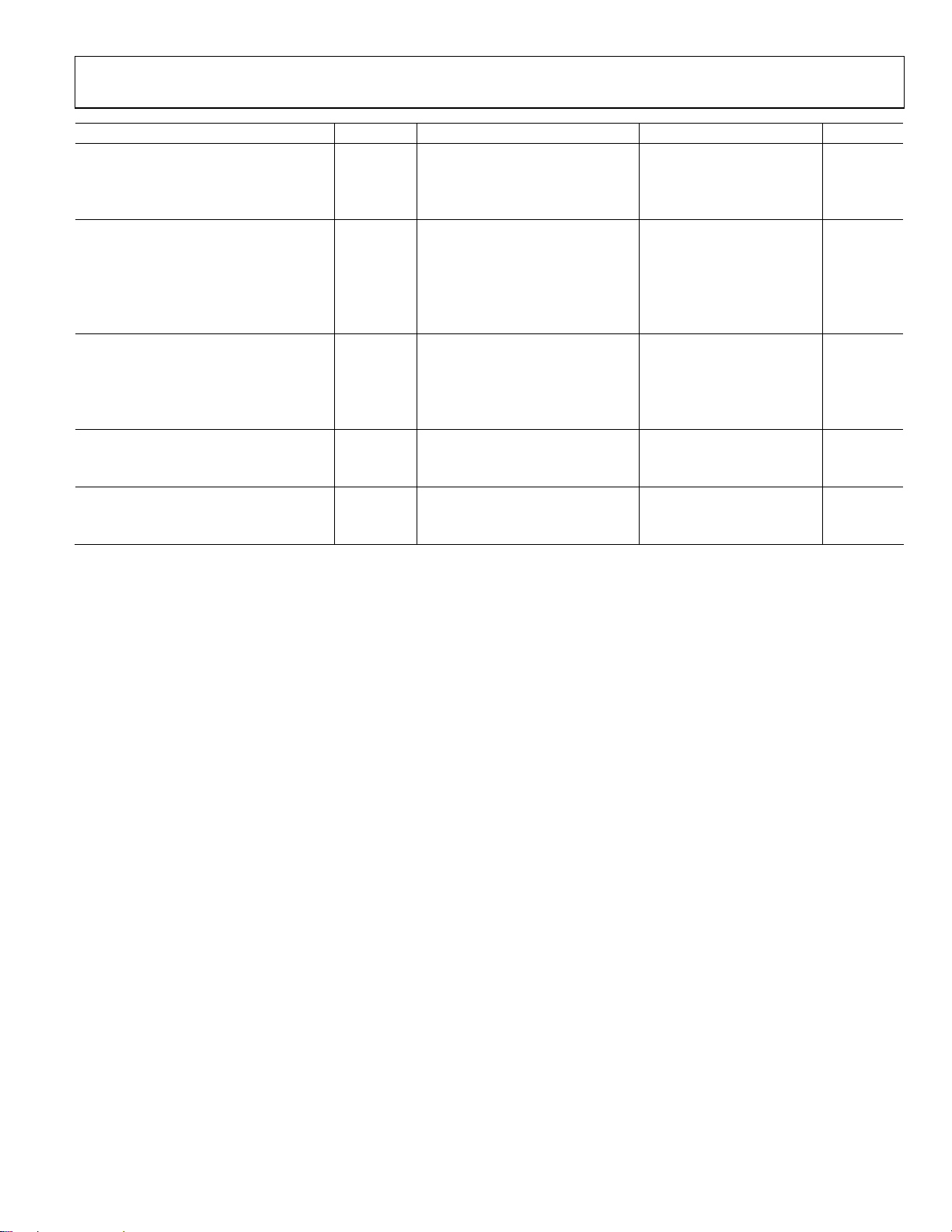

ADP2323

Parameters Symbol Test Conditions/Comments Min Typ Max Units

TRACKING INPUT (TRKx PINS)

TRKx Input Voltage Range 0 600 mV

TRKx-to-FBx Offset Voltage TRKx = 0 mV to 500 mV −10 +10 mV

TRKx Input Bias Current 100 nA

POWER GOOD (PGOODx PINS)

Power Good Rising Threshold 87 90 93 %

Power Good Hysteresis 5 %

Power Good Deglitch Time From FBx to PGOODx 16 Clock cycle

PGOODx Leakage Current V

PGOODx Output Low Voltage I

ENABLE (ENx PINS)

ENx Rising Threshold 1.2 1.28 V

ENx Falling Threshold 1.02 1.1 V

ENx Source Current EN voltage below falling threshold 5 µA

EN voltage above rising threshold 1 µA

MODE (MODE PIN)

Input High Voltage 1.3 V

Input Low Voltage 0.4 V

THERMAL

Thermal Shutdown Threshold 150 °C

Thermal Shutdown Hysteresis 15 °C

1

Tested in a feedback loop that adjusts VFB to achieve a specified voltage on the COMPx pin.

2

Pin-to-pin measurements.

3

Guaranteed by design.

= 5 V 0.1 1 µA

PGOOD

= 1 mA 50 100 mV

PGOOD

Rev. 0 | Page 5 of 32

ADP2323

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

PVIN1, PVIN2, EN1, EN2 −0.3 V to +22 V

SW1, SW2 −1 V to +22 V

BST1, BST2 VSW + 6 V

FB1, FB2, SS1, SS2,COMP1, COMP2,

PGOOD1, PGOOD2, TRK1, TRK2, SCFG,

SYNC, RT, MODE

INTVCC, VDRV, DL1, DL2 −0.3 V to +6 V

PGND to GND −0.3 V to +0.3 V

Temperature Range

Operating (Junction) −40°C to +125°C

Storage −65°C to +150°C

Soldering Conditions JEDEC J-STD-020

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

−0.3 V to +6 V

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Boundary Condition

θJA is measured using natural convection on a JEDEC 4-layer

board, and the exposed pad is soldered to the printed circuit

board (PCB) with thermal vias.

Table 3. Thermal Resistance

Package Type θJA Unit

32-Lead LFCSP_WQ 32.7 °C/W

ESD CAUTION

Rev. 0 | Page 6 of 32

ADP2323

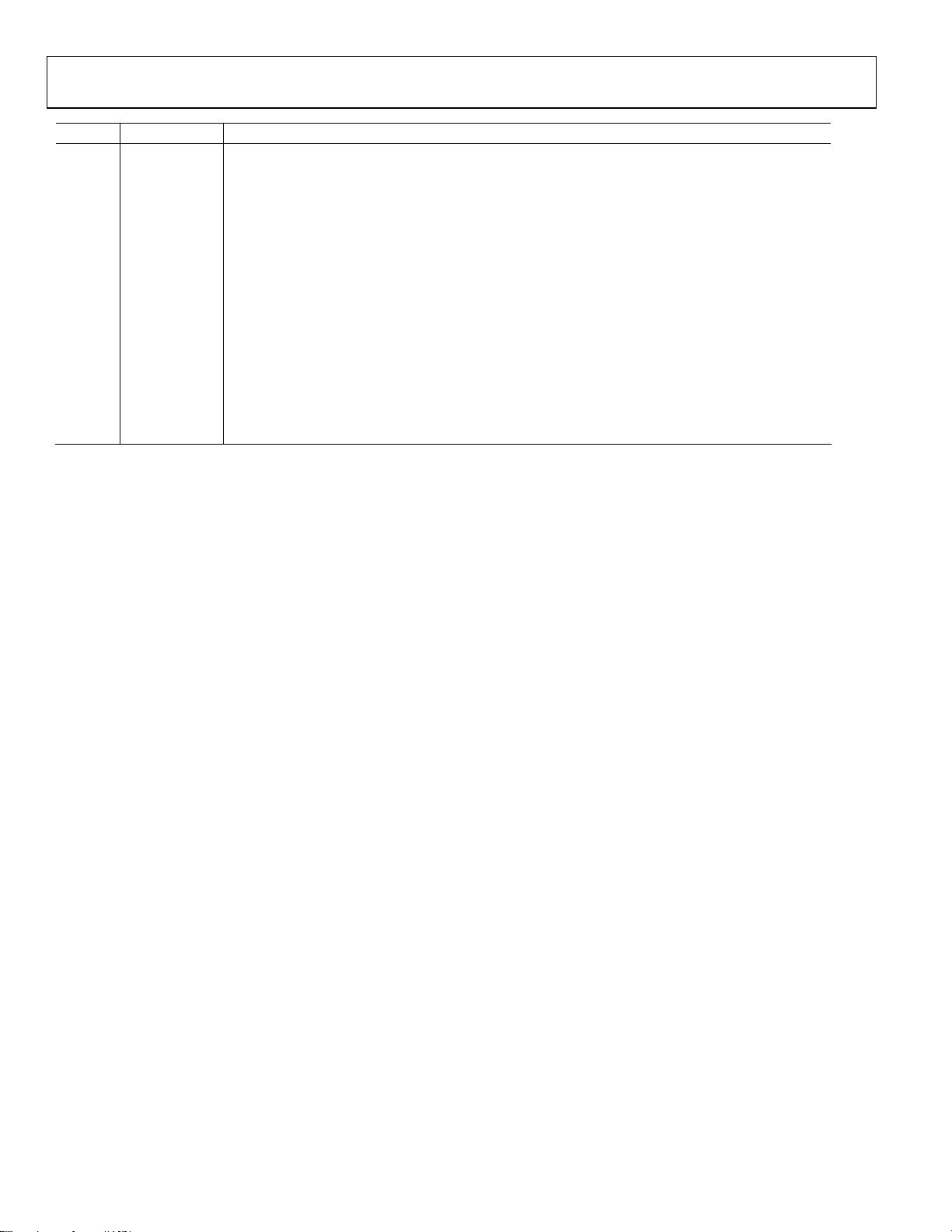

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

FB1

COMP1

SS1

TRK1

EN1

PVIN1

PVIN1

SW1

32313029282726

PGOOD1

1SW1

2

SCFG

SYNC

3

4

5

6

7

8

ADP2323

TOP VIEW

(Not to Scale)

9

10111213141516

FB2

SS2

TRK2

COMP2

GND

INTVCC

RT

MODE

PGOOD2

NOTES

1. THE EXPOSED PAD SHOULD BE SOLDERED TO AN EXTERNAL GND PLANE.

Figure 4. Pin Configuration (Top View)

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 PGOOD1 Power-Good Output (Open Drain) for Channel 1. A pull-up resistor of 10 kΩ to 100 kΩ is recommended.

2 SCFG

Synchronization Configuration Input. The SCFG pin configures the SYNC pin as an input or output.

Connect SCFG to INTVCC to configure SYNC as an output. Using a resistor to pull down to GND

configures SYNC as an input with various phase shift degrees.

3 SYNC

Synchronization. This pin can be configured as an input or an output. When configured as an output,

it provides a clock at the switching frequency. When configured as an input, this pin accepts an

external clock to which the regulators are synchronized and the phase shift is configured by SCFG.

Note that when SYNC is configured as an input, the PFM mode is disabled and the device works only

in continuous conduction mode (CCM).

4 GND Analog Ground. Connect to the ground plane.

5 INTVCC

Internal 5 V Regulator Output. The IC control circuits are powered from this voltage. Place a 1 F

ceramic capacitor between INTVCC and GND.

6 RT

Connect a resistor between RT and GND to program the switching frequency between 250 kHz and

1.2 MHz.

7 MODE

Mode Selection. When this pin is connected to INTVCC, the PFM mode is disabled and the regulator

works only in CCM. When this pin is connected to ground, the PFM mode is enabled. If the low-side

device is a diode, the MODE pin must be connected to ground.

8 PGOOD2

Power-Good Output (Open Drain) for Channel 2. A pull-up resistor of 10 kΩ to 100 kΩ is

recommended.

9 FB2

10 COMP2

Feedback Voltage Sense Input for Channel 2. Connect to a resistor divider from the Channel 2 output

voltage, V

. Connect FB2 to INTVCC for parallel applications.

OUT2

Error Amplifier Output for Channel 2. Connect an RC network from COMP2 to GND. Connect COMP1

and COMP2 together for parallel applications.

11 SS2

Soft Start Control for Channel 2. Connect a capacitor from SS2 to GND to program the soft start time.

For parallel applications, SS2 remains open.

12 TRK2

Tracking Input for Channel 2. To track a master voltage, drive this pin from a voltage divider from the

master voltage. If the tracking function is not used, connect TRK2 to INTVCC.

13 EN2

Enable Pin for Channel 2. An external resistor divider can be used to set the turn-on threshold. When

not using the enable pin, connect EN2 to PVIN2.

14, 15 PVIN2

Power Input for Channel 2. Connect PVIN2 to the input power source, and connect a bypass capacitor

between PVIN2 and ground.

16, 17 SW2 Switch Node for Channel 2.

18 BST2 Supply Rail for the Gate Drive of Channel 2. Place a 0.1 µF capacitor between SW2 and BST2.

19 DL2

Low-Side Gate Driver Output for Channel 2. Connect a resistor between DL2 and PGND to program

the current-limit threshold of Channel 2.

20 VDRV

Low-Side Driver Supply Input. Connect VDRV to INTVCC. Place a 1 µF ceramic capacitor between the

VDRV pin and PGND.

21 PGND Driver Power Ground. Connect to the source of the synchronous N-channel MOSFET.

25

24

23

BST1

DL1

22

PGND

21

20

VDRV

19

DL2

18

BST2

SW2

17

EN2

SW2

PVIN2

PVIN2

09357-003

Rev. 0 | Page 7 of 32

ADP2323

Pin No. Mnemonic Description

22 DL1

23 BST1 Supply Rail for the Gate Drive of Channel 1. Place a 0.1 µF capacitor between SW1 and BST1.

24, 25 SW1 Switch Node for Channel 1.

26, 27 PVIN1

28 EN1

29 TRK1

30 SS1 Soft Start Control for Channel 1. To program the soft start time, connect a capacitor from SS1 to GND.

31 COMP1

32 FB1

Exposed Pad Solder the exposed pad to an external GND plane.

Low-Side Gate Driver Output for Channel 1. Connect a resistor between this pin and PGND to

program the current-limit threshold of Channel 1.

Power Input for Channel 1. This pin is the power input for Channel 1 and also provides power for the

internal regulator. Connect to the input power source and connect a bypass capacitor between PVIN1

and ground.

Enable Pin for Channel 1. An external resistor divider can be used to set the turn-on threshold. When

not using the enable pin, connect the EN1 pin to PVIN1.

Tracking Input for Channel 1. To track a master voltage, drive this pin from a voltage divider from the

master voltage. If the tracking function is not used, connect TRK1 to INTVCC.

Error Amplifier Output for Channel 1. Connect an RC network from COMP1 to GND. Connect COMP1

and COMP2 together for a parallel application.

Feedback Voltage Sense Input for Channel 1. Connect to a resistor divider from the Channel 1 output

voltage, V

OUT1

.

Rev. 0 | Page 8 of 32

ADP2323

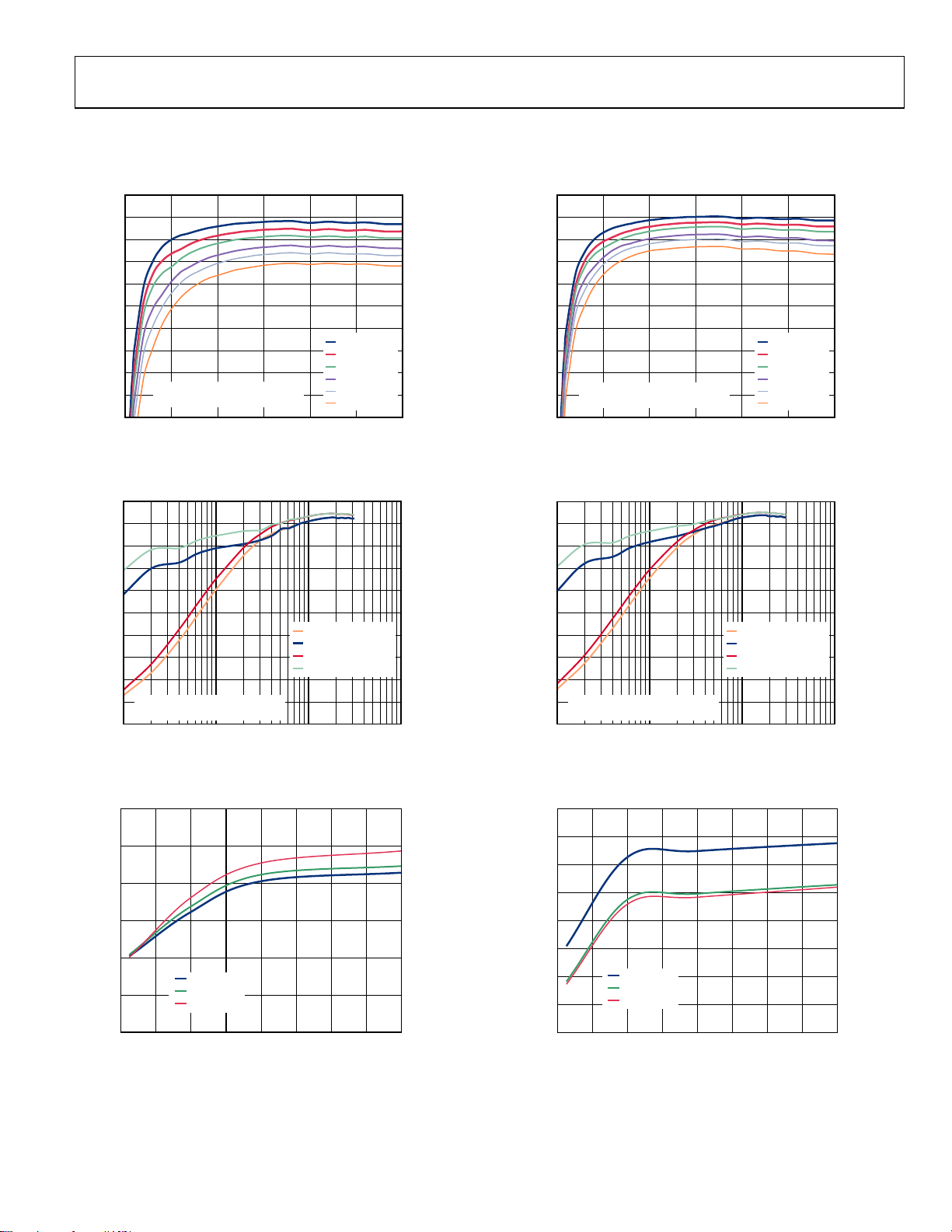

TYPICAL PERFORMANCE CHARACTERISTICS

Operating conditions: TA = 25°C, VIN = 12 V, V

100

95

90

85

80

75

70

EFFICIENCY (%)

65

60

55

50

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

40

INDUCTOR: CDRH105RNP-3R3N

MOSFET: FDS8880

0 0.5 1.0 1.5 2.0 2.5 3.0

OUTPUT CURRENT (A)

Figure 5. Efficiency at V

= 12 V, fSW = 600 kHz, FPWM

IN

V

= 3.3V, FPWM

OUT

V

= 3.3V, PFM

OUT

V

= 5V, FPWM

OUT

V

= 5V, PFM

OUT

INDUCTOR: CDRH105RNP- 3R3N

MOSFET: FDS8880

0

0.01 0. 1 1 10

OUTPUT CURRENT (A)

Figure 6. Efficiency at V

= 12 V, fSW = 600 kHz, PFM

IN

= 3.3 V, L = 4.7 µH, C

OUT

V

= 5.0V

OUT

V

= 3.3V

OUT

V

= 2.5V

OUT

V

= 1.8V

OUT

V

= 1.5V

OUT

V

= 1.2V

OUT

= 2 × 47 µF, fSW = 600 kHz, unless otherwise noted.

OUT

100

95

90

85

80

75

70

EFFICIENCY (%)

65

60

INDUCTOR: CDRH105RNP- 6R8N

55

MOSFET: FDS8880

50

0 0.5 1.0 1.5 2.0 2.5 3.0

09357-005

Figure 8. Efficiency at V

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

INDUCTOR: CDRH105RNP- 6R8N

10

MOSFET: FDS8880

0

0.01 0. 1 1 10

09357-006

Figure 9. Efficiency at V

3.20

OUTPUT CURRENT (A)

= 12 V, fSW = 300 kHz, FPWM

IN

OUTPUT CURRENT (A)

= 12 V, fSW = 300 kHz, PFM

IN

V

= 3.3V, FPWM

OUT

V

= 3.3V, PFM

OUT

V

= 5V, FPWM

OUT

V

= 5V, PFM

OUT

V

= 5.0V

OUT

V

= 3.3V

OUT

V

= 2.5V

OUT

V

= 1.8V

OUT

V

= 1.5V

OUT

V

= 1.2V

OUT

09357-008

09357-009

35

30

25

20

SHUTDOWN CURRENT (μ A)

15

10

4 6 8 10 12 14 16 18 20

TJ = –40°C

TJ = +25°C

TJ = +125°C

VIN (V)

Figure 7. Shutdown Current vs. V

IN

09357-007

Rev. 0 | Page 9 of 32

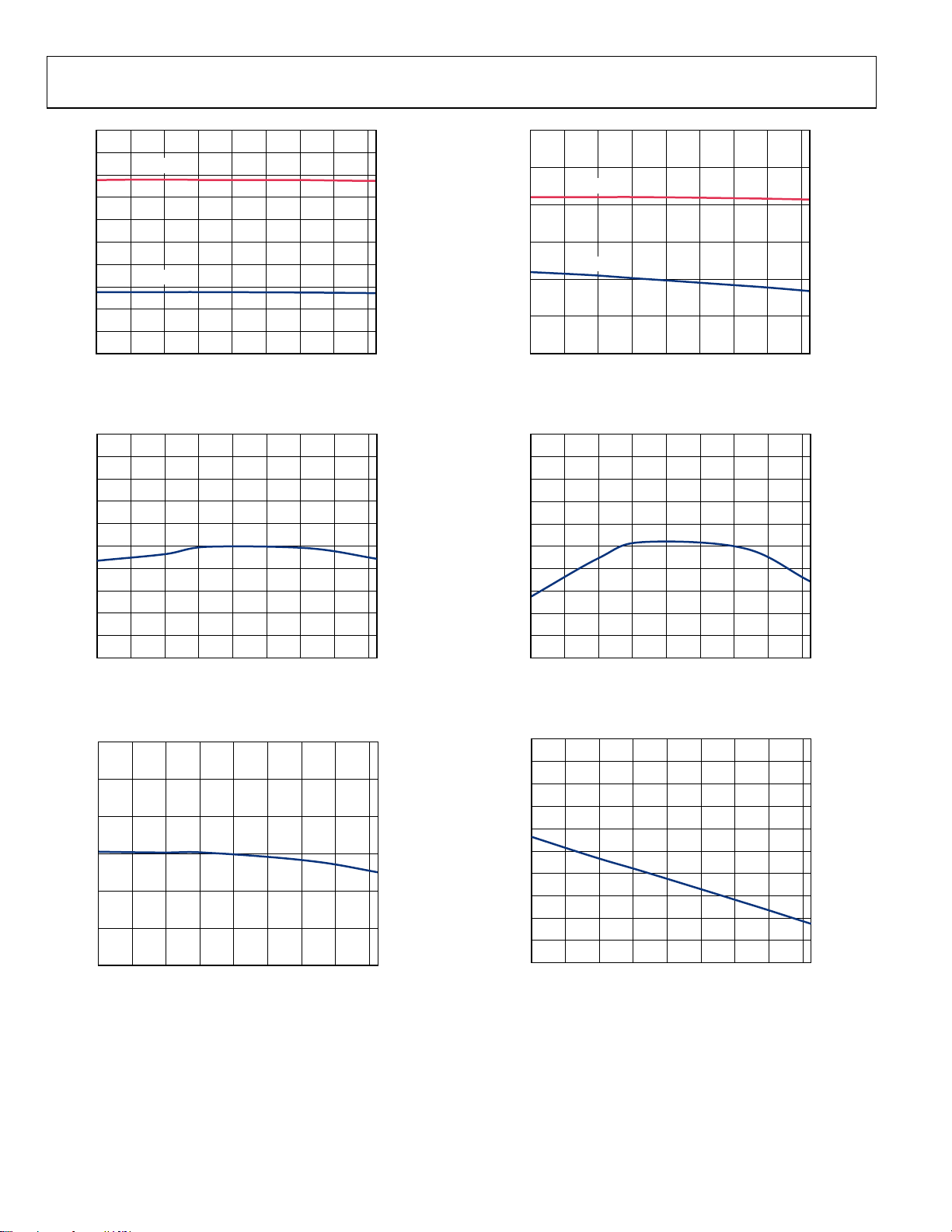

3.15

3.10

3.05

3.00

2.95

2.90

QUIESCENT CURRENT (mA)

2.85

2.80

4 6 8 101214161820

TJ = –40°C

TJ = +25°C

TJ = +125°C

VIN (V)

Figure 10. Quiescent Current vs. V

IN

09357-010

ADP2323

T

C

4.5

4.4

4.3

4.2

4.1

4.0

3.9

3.8

UVLO THRESHOLD (V)

3.7

3.6

3.5

–40 –20 0 20 40 60 80 100 120

1.10

1.08

1.06

1.04

1.02

1.00

0.98

0.96

EN SOURCE CURRENT (µA)

0.94

0.92

0.90

–40 –20 0 20 40 60 80 100 120

606

604

602

AGE (mV)

600

598

FEEDBACK VOL

596

594

–40 –20 0 20 40 60 80 100 120

RISING

FALL ING

TEMPERATURE (°C)

Figure 11. UVLO Threshold vs. Temperature

TEMPERATURE (°C)

Figure 12. EN Source Current at V

= 1.5 V

EN

TEMPERATURE (°C)

Figure 13. FB Voltage vs. Temperature

1.30

1.25

RISING

1.20

1.15

1.10

ENABLE THRESHOL D (V)

1.05

1.00

–40 –20 0 20 40 60 80 100 120

09357-011

FALL ING

TEMPERATURE (°C)

09357-014

Figure 14. EN Threshold vs. Temperature

5.10

5.05

5.00

4.95

4.90

4.85

4.80

4.75

EN SOURCE CURRENT (µA)

4.70

4.65

4.60

–40 –20 0 20 40 60 80 100 120

09357-012

Figure 15. EN Source Current at V

350

340

330

320

310

TANC E (µ S )

300

290

280

TRANSCONDU

270

260

250

–40 –20 0 20 40 60 80 100 120

09357-013

TEMPERATURE (°C)

TEMPERATURE (°C)

Figure 16. g

vs. Temperature

m

= 1 V

EN

09357-015

09357-016

Rev. 0 | Page 10 of 32

Loading...

Loading...