ANALOG DEVICES ADP220 Service Manual

High PSRR Voltage Regulator

ADP220/ADP221

Rev. F

rights of third parties that may result from its use. Specifications subject to change without notice. No

Trademarks and registered trademarks are the prop erty of their respective owner s.

Fax: 781.461.3113 ©2008–2012 Analog Devices, Inc. All rights reserved.

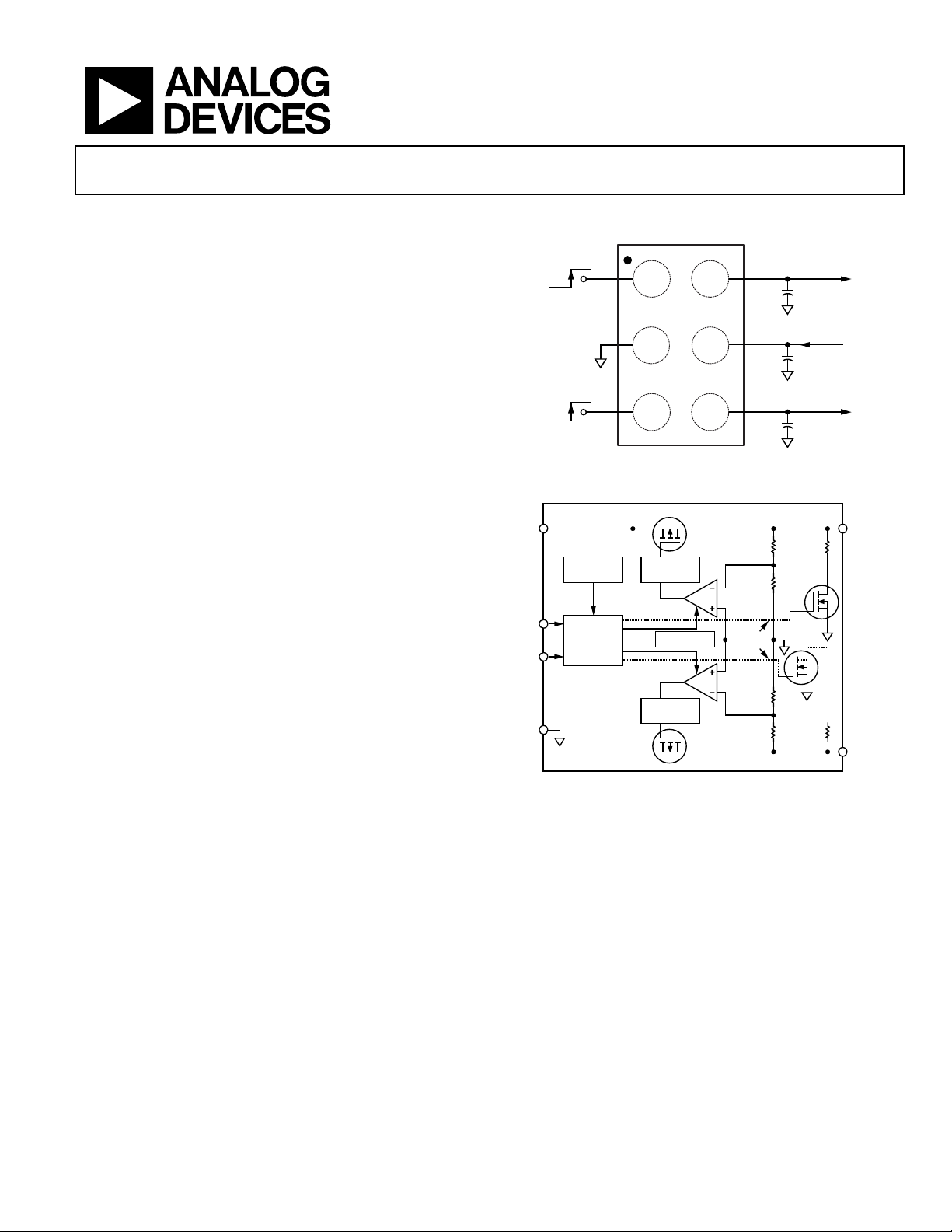

EN1 VOUT1

GND VIN

EN2 VOUT2

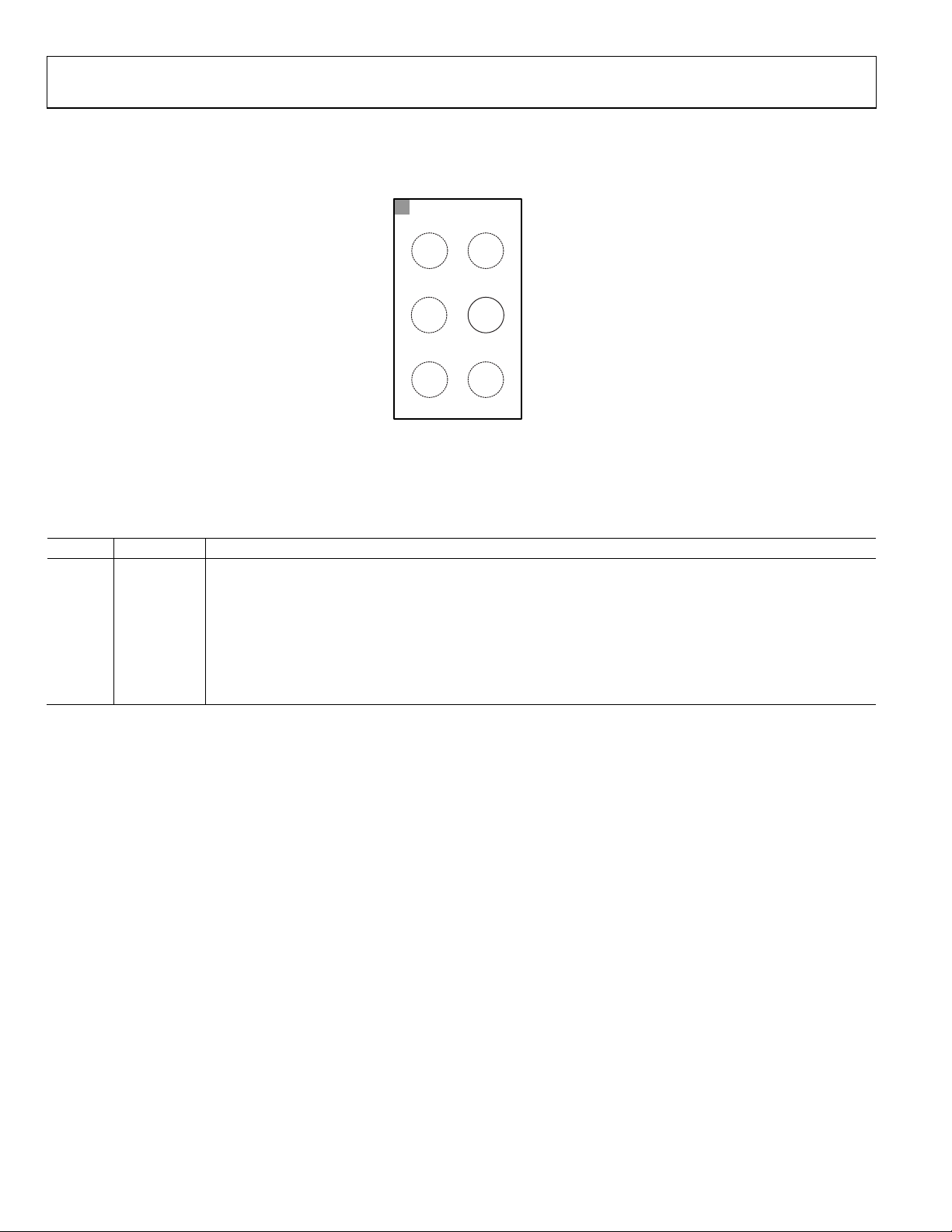

TOP VIEW

(Not to S cale)

1

A

B

C

2

V

OUT1

= 2.8V

1µF

1µF

1µF

V

IN

= 3.3V

V

OUT2

= 2.8V

07572-001

OFF

ON

OFF

ON

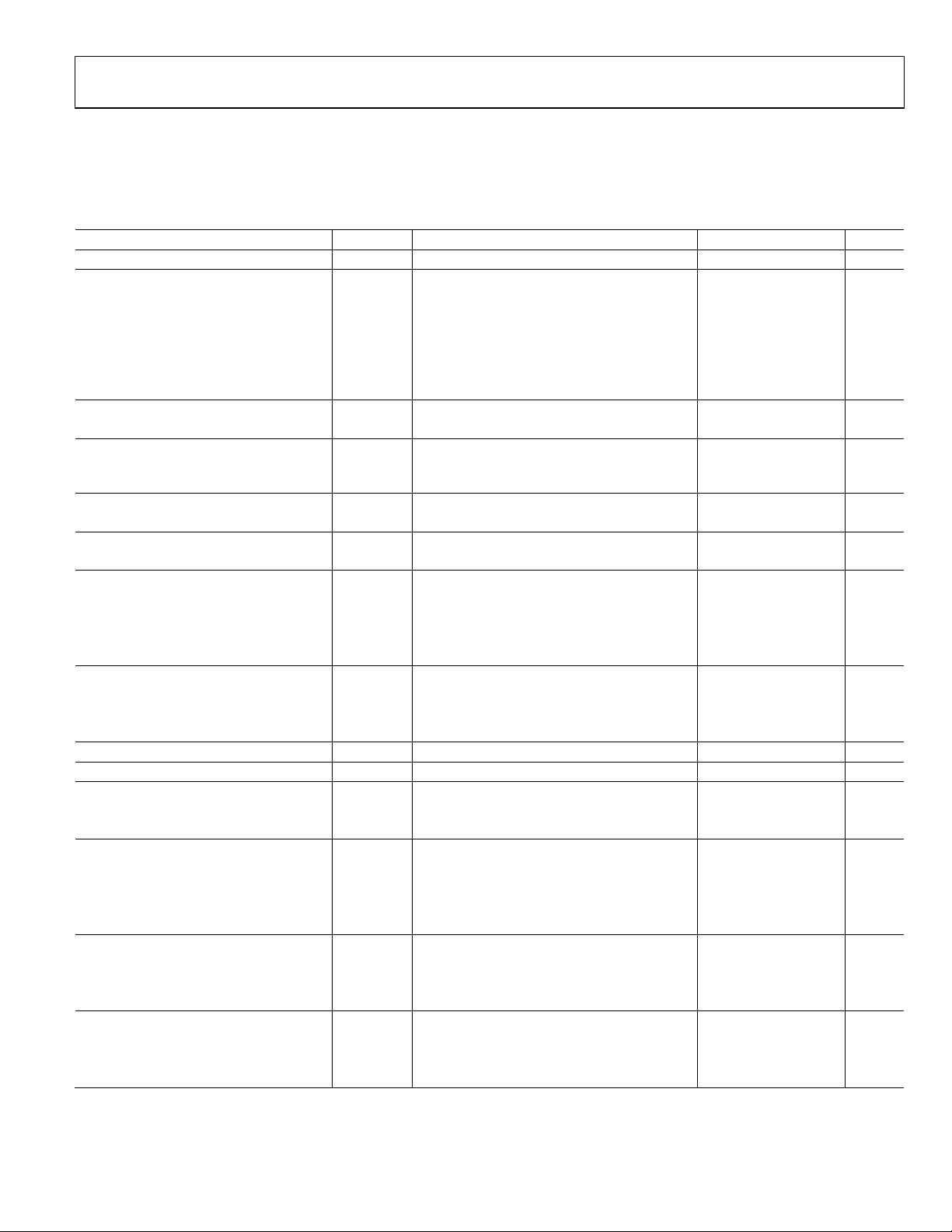

THERMAL

SHUTDOWN

EN1

EN2

GND

CURRENT

LIMIT

CURRENT

LIMIT

60Ω

60Ω

REFERENCE

ADP221

ONLY

CONTROL

LOGIC

AND

ENABLE

VIN VOUT1

VOUT2

ADP220

07572-002

Data Sheet

FEATURES

Input voltage range: 2.5 V to 5.5 V

Dual independent 200 mA low dropout voltage regulators

Miniature 6-ball, 1.0 mm × 1.5 mm WLCSP

Initial accuracy: ±1%

Stable with 1 µF ceramic output capacitors

No noise bypass capacitor required

Two independent logic controlled enables

Overcurrent and thermal protection

Active output pull-down (ADP221)

Key specifications

High PSRR

76 dB PSRR up to 1 kHz

70 dB PSRR at 10 kHz

60 dB PSRR at 100 kHz

40 dB PSRR at 1 MHz

Low output noise

27 µV rms typical output noise at V

50 µV rms typical output noise at V

Excellent transient response

Low dropout voltage: 150 mV @ 200 mA load

60 µA typical ground current at no load, both LDOs enabled

100 µs fast turn-on circuit

Guaranteed 200 mA output current per regulator

−40°C to +125°C junction temperature

= 1.2 V

OUT

= 2.8 V

OUT

Dual, 200 mA, Low Noise,

TYPICAL APPLICATION CIRCUITS

Figure 1. Typical Application Circuit

APPLICATIONS

Mobile phones

Digital cameras and audio devices

Portable and battery-powered equipment

Portable medical devices

Post dc-to-dc regulation

GENERAL DESCRIPTION

The 200 mA dual output ADP220/ADP221 combine high PSRR,

low noise, low quiescent current, and low dropout voltage in a

voltage regulator ideally suited for wireless applications with

demanding performance and board space requirements.

The low quiescent current, low dropout voltage, and wide input

voltage range of the ADP220/ADP221 extend the battery life of

portable devices. The ADP220/ADP221 maintain power supply

rejection greater than 60 dB for frequencies as high as 100 kHz

while operating with a low headroom voltage. The ADP220

offers much lower noise performance than competing LDOs

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Figure 2. Block Diagram of the ADP220/ADP221

without the need for a noise bypass capacitor. The ADP221 also

includes an active pull-down to quickly discharge output loads.

The ADP220/ADP221 are available in a miniature 6-ball

WLCSP package and is stable with tiny 1 µF ± 30% ceramic

output capacitors, resulting in the smallest possible board

area for a wide variety of portable power needs.

The ADP220/ADP221 are available in many output voltage

combinations, ranging from 0.8 V to 3.3 V, and offer overcurrent and thermal protection to prevent damage in adverse

conditions.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

ADP220/ADP221 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Typical Application Circuits ............................................................ 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Input and Output Capacitor, Recommended Specifications .. 4

Absolute Maximum Ratings ............................................................ 5

Thermal Data ................................................................................ 5

Thermal Resistance ...................................................................... 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

REVISION HISTORY

/12—Rev. E to R e v. F

C

hanges to Ordering Guide .......................................................... 17

11/10—Rev. D t o R e v. E

Changes to Ordering Guide .......................................................... 17

5/10—Rev. C to R e v. D

Changes to Figure 1 .......................................................................... 1

Changes to Ordering Guide .......................................................... 17

1/10—Rev. B to R e v. C

Changes to Figure 24 ...................................................................... 10

10/09—Rev. A to Rev. B

Changes to Features Section............................................................ 1

Changes to Table 3 an

d Table 4 ....................................................... 5

Typical Performance Characteristics ..............................................7

Theory of Operation ...................................................................... 11

Applications Information .............................................................. 12

Capacitor Selection .................................................................... 12

Undervoltage Lockout ............................................................... 13

Enable Feature ............................................................................ 13

Current-Limit and Thermal Overload Protection ................. 14

Thermal Considerations ............................................................ 14

Printed Circuit Board (PCB) Layout Considerations ................ 16

Outline Dimensions ....................................................................... 17

Ordering Guide .......................................................................... 17

Changes to Figure 4, Figure 6, Figure 7, and Figure 9 .................. 7

Changes to Figure 10 and Figure 12................................................ 8

Changes to Figure 17 ......................................................................... 9

Changes to Figure 25 ...................................................................... 10

Changes to Enable Feature Section and Figure 32 ..................... 13

Changes to Current-Limit and Thermal Overland Protection

Section and Thermal Considerations Section ............................ 14

Changes to Ordering Guide .......................................................... 17

3/09—Rev. 0 to R e v. A

Changes to Figure 15 ......................................................................... 8

Changes to Figure 16 ......................................................................... 9

Changes to Ordering Guide .......................................................... 17

10/08—Revision 0: Initial Version

Rev. F | Page 2 of 20

Data Sheet ADP220/ADP221

INPUT VOLTAGE RANGE

VIN

TJ = −40°C to +125°C

2.5 5.5

V

I

= 0 µA, TJ = −40°C to +125°C

120

µA

DROPOUT VOLTAGE2

V

V

= 3.3 V

mV

V

= 0.8 V, one initially on, enable second

20 µs

THERMAL SHUTDOWN

Hysteresis

UVLO

100 mV

10 Hz to 100 kHz, VIN = 3.6 V, V

= 2.5 V

45 µV rms

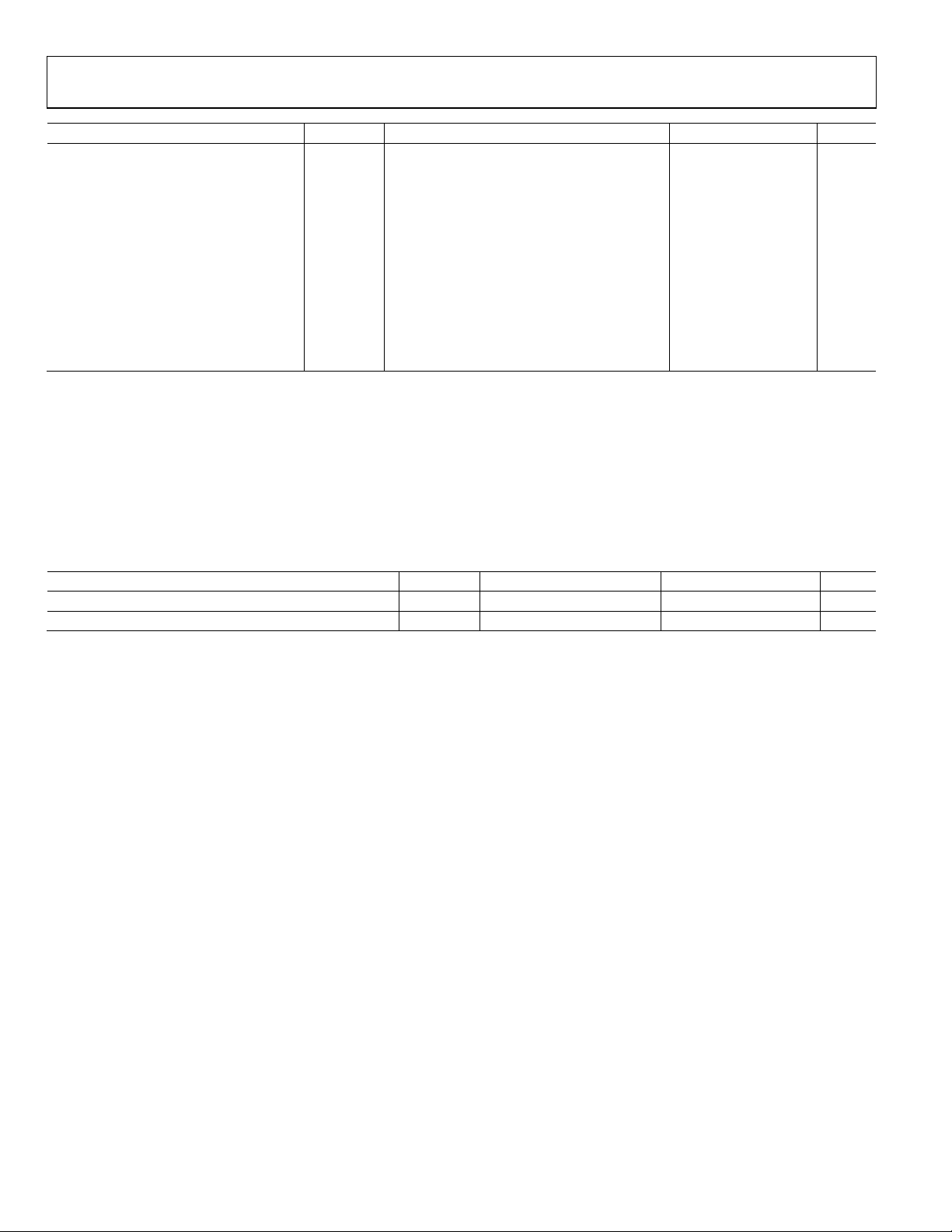

SPECIFICATIONS

VIN = (V

unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

+ 0.5 V) or 2.5 V (whichever is greater), EN1 = EN2 = VIN, I

OUT

OUT1

= I

= 10 mA, CIN = C

OUT2

OUT1

= C

= 1 µF, TA = 25°C,

OUT2

OPERATING SUPPLY CURRENT WITH

I

I

GND

= 0 µA 60 µA

OUT

BOTH REGULATORS ON

OUT

I

I

I

I

SHUTDOWN CURRENT I

EN1= EN2 = GND 0.1 µA

GND-SD

= 10 mA 70 µA

OUT

= 10 mA, TJ = −40°C to +125°C 140 µA

OUT

= 200 mA 120 µA

OUT

= 200 mA, TJ = −40°C to +125°C 220 µA

OUT

EN1= EN2 = GND, TJ = −40°C to +125°C 2 µA

FIXED OUTPUT VOLTAGE ACCURACY V

LINE REGULATION ∆V

VIN = (V

LOAD REGULATION1 ∆V

I

I

I

I

STA RT-UP TIME3 t

V

V

ACTIVE PULL-DOWN RESISTANCE t

CURRENT-LIMIT THRESHOLD4 I

−1 +1 %

OUT

100 µA < I

5.5 V, T

/∆VIN VIN = (V

OUT

/∆I

I

OUT

OUT

DROPOUT

V

STA RT-UP

V

SHUTDOWN

240 300 440 mA

LIMIT

= 1 mA to 200 mA 0.001 %/mA

OUT

= 1 mA to 200 mA, TJ = −40°C to +125°C 0.003 %/mA

OUT

OUT

I

= 10 mA 7.5 mV

OUT

= 10 mA, TJ = −40°C to +125°C 12 mV

OUT

= 200 mA 150 mV

OUT

= 200 mA, TJ = −40°C to +125°C 230 mV

OUT

= 3.3 V, both initially off, enable one 240 µs

OUT

= 0.8 V, both initially off, enable one 100 µs

OUT

= 3.3 V, one initially on, enable second 180 µs

OUT

OUT

= 2.8 V, R

OUT

< 200 mA, VIN = (V

OUT

= −40°C to +125°C

J

+ 0.5 V) to 5.5 V 0.01 %/V

OUT

+ 0.5 V) to 5.5 V, TJ = −40°C to +125°C −0.03 +0.03 %/V

OUT

LOAD

= ∞, C

= 1 μF, ADP221 only 80 Ω

OUT

+ 0.5 V) to

OUT

−2 +2 %

Thermal Shutdown Threshold TSSD TJ rising 155 °C

Thermal Shutdown Hysteresis TS

EN INPUT

EN Input Logic High VIH 2.5 V ≤ VIN ≤ 5.5 V 1.2 V

EN Input Logic Low VIL 2.5 V ≤ VIN ≤ 5.5 V 0.4 V

EN Input Leakage Current V

EN1 = EN2 = VIN or GND, TJ = −40°C to +125°C 1 µA

UNDERVOLTAGE LOCKOUT UVLO

Input Voltage Rising UVLO

Input Voltage Falling UVLO

OUTPUT NOISE OUT

10 Hz to 100 kHz, VIN = 5 V, V

10 Hz to 100 kHz, VIN = 3.6 V, V

15 °C

SD-HYS

EN1 = EN2 = VIN or GND 0.1 µA

I-LEAKAGE

2.45 V

RISE

2.2 V

FAL L

HYS

10 Hz to 100 kHz, VIN = 5 V, V

NOISE

Rev. F | Page 3 of 20

= 3.3 V 56 µV rms

OUT

= 2.8 V 50 µV rms

OUT

OUT

= 1.2 V 27 µV rms

OUT

ADP220/ADP221 Data Sheet

100 kHz

60 dB

100 kHz

60 dB

Parameter Symbol Conditions Min Typ Max Unit

POWER SUPPLY REJECTION RATIO PSRR VIN = 2.5 V, V

100 Hz 76 dB

1 kHz 76 dB

10 kHz 70 dB

1 MHz 40 dB

VIN = 3.8 V, V

100 Hz 68 dB

1 kHz 68 dB

10 kHz 68 dB

1 MHz 40 dB

1

Based on an end-point calculation using 1 mA and 200 mA loads.

2

Dropout voltage is defined as the input-to-output voltage differential when the input voltage is set to the nominal output voltage. This applies only for output

voltages above 2.5 V.

3

Start-up time is defined as the time between the rising edge of ENx to V

4

Current-limit threshold is defined as the current at which the output voltage drops to 90% of the specified typical value. For example, the current limit for a 3.0 V

output voltage is defined as the current that causes the output voltage to drop to 90% of 3.0 V, or 2.7 V.

being at 90% of its nominal value.

OUTx

INPUT AND OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS

= 0.8 V, I

OUT

= 2.8 V, I

OUT

= 100 mA

OUT

= 100 mA

OUT

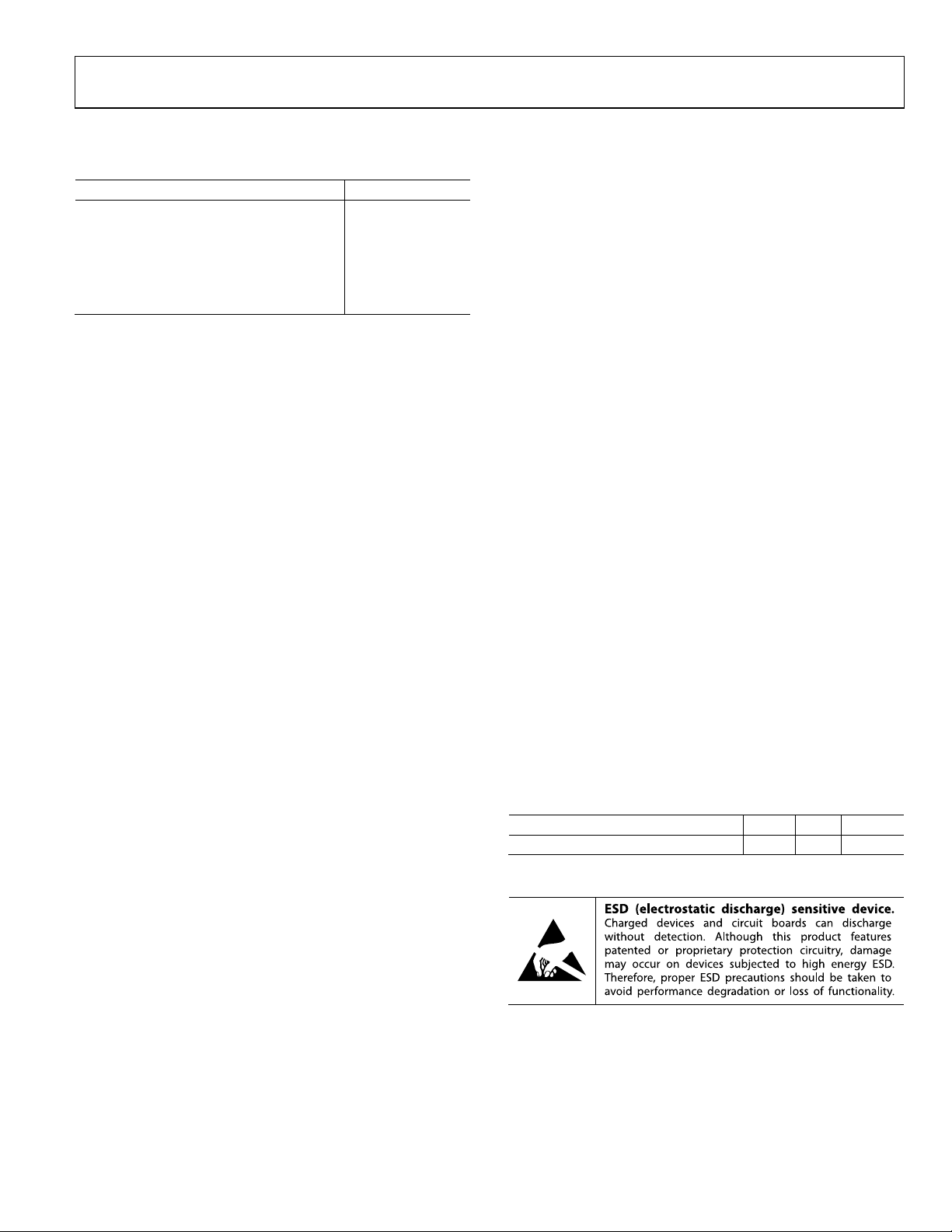

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

MINIMUM INPUT AND OUTPUT CAPACITANCE1 C

CAPACITOR ESR R

1

The minimum input and output capacitance should be greater than 0.70 µF over the full range of operating conditions. The full range of operating conditions in the

application must be considered during device selection to ensure that the minimum capacitance specification is met. X7R and X5R type capacitors are recommended;

Y5V and Z5U capacitors are not recommended for use with LDOs.

TA = −40°C to +125°C 0.70 µF

MIN

TA = −40°C to +125°C 0.001 1 Ω

ESR

Rev. F | Page 4 of 20

Data Sheet ADP220/ADP221

VOUT1, VOUT2 to GND

–0.3 V to VIN

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

VIN to GND –0.3 V to +6.5 V

EN1, EN2 to GND –0.3 V to +6.5 V

Storage Temperature Range –65°C to +150°C

Operating Junction Temperature Range –40°C to +125°C

Soldering Conditions JEDEC J-STD-020

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL DATA

Absolute maximum ratings apply individually only, not in

combination.

The ADP220/ADP221 can be damaged when the junction

temperature limits are exceeded. Monitoring ambient temperature does not guarantee that the junction temperature (T

is within the specified temperature limits. In applications

with high power dissipation and poor thermal resistance, the

maximum ambient temperature may have to be derated. In

applications with moderate power dissipation and low PCB

thermal resistance, the maximum ambient temperature can

exceed the maximum limit as long as the junction temperature

is within specification limits. The junction temperature (T

the device is dependent on the ambient temperature (T

power dissipation of the device (P

thermal resistance of the package (θ

temperature (T

(T

) and power dissipation (PD) using the following formula:

A

= TA + (PD × θJA)

T

J

) is calculated from the ambient temperature

J

), and the junction-to-ambient

D

). Maximum junction

JA

J

), the

A

)

) of

J

Junction-to-ambient thermal resistance (θ

based on modeling and calculation using a 4-layer board. The

junction-to-ambient thermal resistance is highly dependent

on the application and board layout. In applications where high

maximum power dissipation exists, close attention to thermal

board design is required. The value of θ

on PCB material, layout, and environmental conditions. The

specified values of θ

are based on a four-layer, 4 inch × 3 inch,

JA

circuit board. Refer to JEDEC JESD 51-9 for detailed information on the board construction. For additional information,

see the AN-617 Application Note, MicroCSP

Scale Package.

Ψ

is the junction-to-board thermal characterization parameter

JB

with units of °C / W. Ψ

of the package is based on modeling and

JB

calculation using a 4-layer board. The JESD51-12, Guidelines

for Reporting and Using Package Thermal Information, states

that thermal characterization parameters are not the same as

thermal resistances. Ψ

measures the component power flowing

JB

through multiple thermal paths rather than a single path as in

thermal resistance, θ

. Therefore, ΨJB thermal paths include

JB

convection from the top of the package as well as radiation

from the package. Factors that make Ψ

world applications. Maximum junction temperature (T

calculated from the board temperature (T

dissipation (P

= TB + (PD × ΨJB)

T

J

) using the following formula:

D

Refer to JEDEC JESD51-8 and JESD51-12 for more detailed

information on Ψ

.

JB

THERMAL RESISTANCE

θJA and ΨJB are specified for the worst-case conditions, that is, a

device soldered in a circuit board for surface-mount packages.

Table 4.

Package Type θJA ΨJB Unit

6-Ball, 0.5 mm Pitch WLCSP 260 43.8 °C/W

) of the package is

JA

may vary, depending

JA

TM

Wafer Level Chip

more useful in real-

JB

) is

J

) and power

B

ESD CAUTION

Rev. F | Page 5 of 20

ADP220/ADP221 Data Sheet

TOP VIEW

(BALL SI DE DOWN)

Not to Scale

07572-003

1

A

2

EN1 VOUT1

GND VIN

EN2 VOUT2

B

C

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

A1 EN1

Enable Input for Regulator 1. Drive EN1 high to turn on Regulator 1; drive it low to turn off Regulator 1.

For automatic startup, connect EN1 to VIN.

B1 GND Ground Pin.

C1 EN2

Enable Input for Regulator 2. Drive EN2 high to turn on Regulator 2; drive it low to turn off Regulator 2.

For automatic startup, connect EN2 to VIN.

A2 VOUT1 Regulated Output Voltage 1. Connect a 1 µF or greater output capacitor between VOUT1 and GND.

B2 VIN Regulator Input Supply. Bypass VIN to GND with a 1 µF or greater capacitor.

C2 VOUT2 Regulated Output Voltage 2. Connect a 1 µF or greater output capacitor between VOUT2 and GND.

Rev. F | Page 6 of 20

Loading...

Loading...