Compact, 800 mA, 3 MHz,

V

FEATURES

Input voltage: 2.3 V to 5.5 V

Peak efficiency: 95%

3 MHz fixed frequency operation

Low quiescent current: 23 μA

Ultralow shutdown current: 0.2 μA (typical)

VSEL pin for simple dynamic voltage scaling (DVS)

100% duty cycle low dropout mode

Internal synchronous rectifier, compensation, and soft start

Current overload and thermal shutdown protection

Small, 6-ball, 1 mm × 1.5 mm WLCSP package

APPLICATIONS

PDAs and palmtop computers

Wireless handsets

Digital audio portable media players

Digital cameras, GPS navigation units

Low power portable medical equipment

Simple DVS, Buck Regulator

ADP2147

GENERAL DESCRIPTION

The ADP2147 is a high efficiency, low quiescent current, stepdown (buck) dc-to-dc regulator with an output voltage that can

be switched between two different settings under the control of

a select pin. The total solution requires only three tiny external

components.

The buck regulator automatically switches operating modes,

depending on the load current level, to maximize efficiency. At

high output loads, the buck regulator operates in PWM mode.

When the load current falls below a predefined threshold, the

regulator operates in power save mode (PSM), improving the

light-load efficiency.

The ADP2147 runs on input voltages of 2.3 V to 5.5 V, which

allows for single lithium or lithium polymer cells, multiple

alkaline or NiMH cells, PCMCIA, USB, and other standard

power sources. The maximum load current of 800 mA is

achievable across the input voltage range.

The ADP2147 is available with fixed output voltages from 0.8 V

to 3.3 V. All versions include an internal power switch and

synchronous rectifier for minimal external part count and high

efficiency. The ADP2147 has an internal soft start and is

internally compensated. During logic controlled shutdown, the

input is disconnected from the output, and the ADP2147 draws

less than 0.2 A (typical) from the power source.

Other key features include undervoltage lockout to prevent deep

battery discharge and soft start to prevent input current overshoot at startup. The ADP2147 is available in a 6-ball WLCSP.

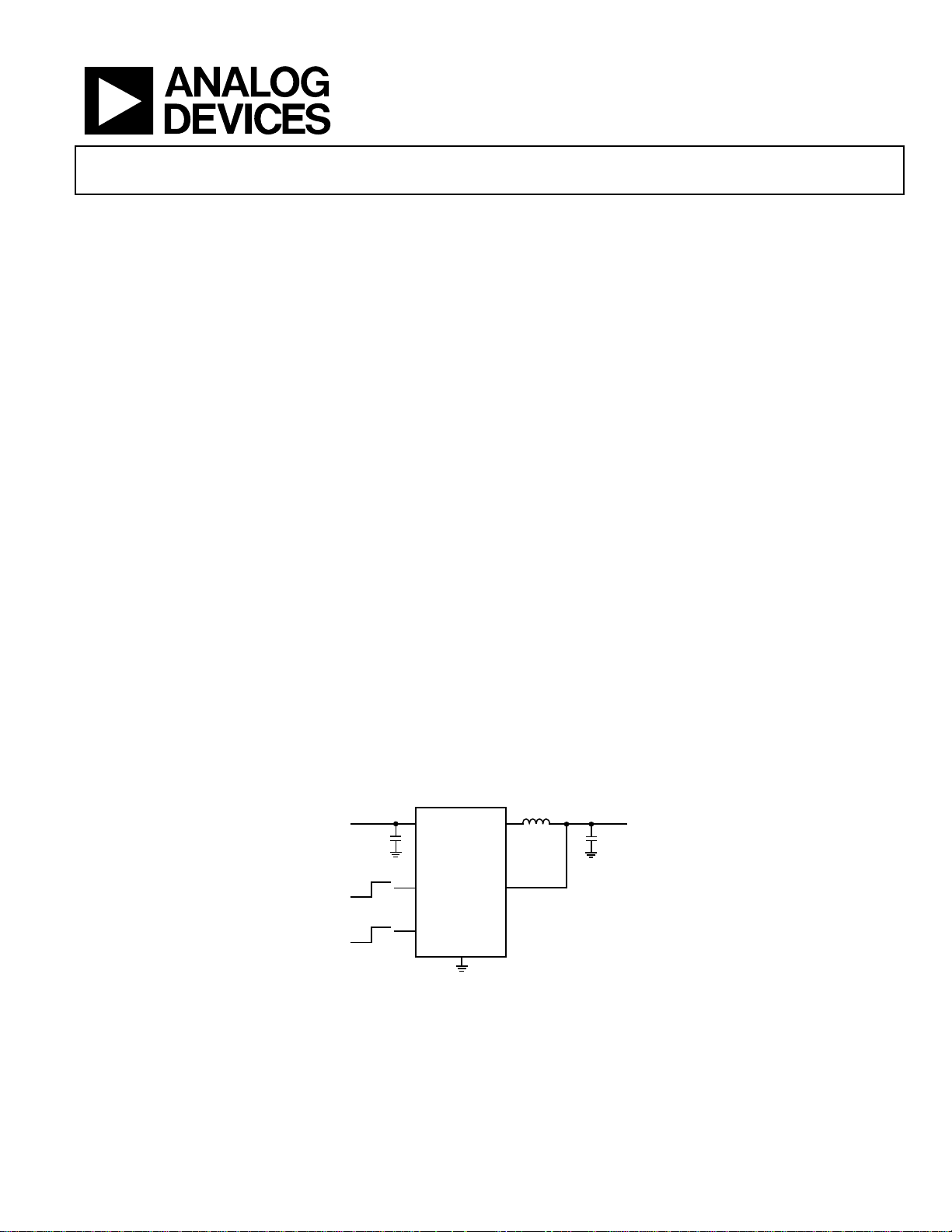

TYPICAL APPLICATIONS CIRCUIT

2.3V TO 5.5V

4.7µF 4.7µF

OFF

V

OUT

_L

OUT

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

ON

_H

VIN SW

ADP2147

EN

VSEL

VOUT

GND

Figure 1.

1.0µH

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

V

OUT

09885-001

ADP2147

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Typical Applications Circuit............................................................ 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Input and Output Capacitor, Recommended

Specifications ................................................................................ 3

Absolute Maximum Ratings............................................................ 4

Thermal Data ................................................................................ 4

Thermal Resistance ...................................................................... 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Typical Performance Characteristics ............................................. 6

Theory of Operation ...................................................................... 11

Control Scheme .......................................................................... 11

PWM Mode................................................................................. 11

Power Save Mode........................................................................ 11

Enable/Shutdown....................................................................... 11

Simple Dynamic Voltage Scaling (DVS) ................................. 12

Short-Circuit Protection............................................................ 12

Undervoltage Lockout............................................................... 12

Thermal Protection.................................................................... 12

Soft Start ...................................................................................... 12

Current Limit.............................................................................. 12

100% Duty Operation................................................................ 12

Applications Information.............................................................. 13

External Component Selection ................................................ 13

Thermal Considerations............................................................ 14

PCB Layout Guidelines.............................................................. 14

Evaluation Board............................................................................ 15

Evaluation Board Layout........................................................... 15

Outline Dimensions....................................................................... 16

Ordering Guide .......................................................................... 16

REVISION HISTORY

5/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 16

ADP2147

SPECIFICATIONS

VIN = 3.6 V, V

unless otherwise noted. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Input Voltage Range 2.3 5.5 V

Undervoltage Lockout Threshold VIN rising 2.3 V

V

OUTPUT CHARACTERISTICS

Output Voltage Accuracy PWM mode, VSEL = Low −2 +2 %

PWM mode, VSEL = High −2.5 +2.5 %

Line Regulation VIN = 2.3 V to 5.5 V, PWM mode 0.25 %/V

Load Regulation I

PWM TO POWER SAVE MODE CURRENT THRESHOLD 100 mA

INPUT CURRENT CHARACTERISTICS

DC Operating Current I

Shutdown Current EN = 0 V, TA = TJ = −40°C to +85°C 0.2 1.0 A

SW CHARACTERISTICS

SW On Resistance pFET 155 240 mΩ

nFET 115 200 mΩ

Current Limit pFET switch peak current limit 1100 1500 1650 mA

ENABLE/VSEL CHARACTERISTICS

Input High Threshold 1.2 V

Input Low Threshold 0.4 V

Input Leakage Current EN = VSEL = 0 V to 3.6 V −1 0 +1 A

OSCILLATOR FREQUENCY 2.6 3.0 3.4 MHz

START-UP TIME 250 s

THERMAL CHARACTERISTICS

Thermal Shutdown Threshold 150 °C

Thermal Shutdown Hysteresis 20 °C

= 0.8 V to 3.3 V, TJ = −40°C to +125°C for minimum/maximum specifications, and TA = 25°C for typical specifications,

OUT

falling 2.00 2.15 2.25 V

IN

= 0 mA to 800 mA −0.95 %/A

LOAD

= 0 mA, device not switching 23 30 A

LOAD

INPUT AND OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS

TA = −40°C to +125°C, unless otherwise specified. All limits at temperature extremes are guaranteed via correlation using standard

statistical quality control (SQC).

Table 2.

Parameter Symbol Min Typ Max Unit

MINIMUM INPUT AND OUTPUT CAPACITANCE C

CAPACITOR ESR R

Rev. 0 | Page 3 of 16

4.7 µF

MIN

0.001 1 Ω

ESR

ADP2147

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

VIN, EN, VSEL −0.4 V to +6.5 V

VOUT, SW to GND −1.0 V to (VIN + 0.2 V)

Temperature Range

Operating Ambient −40°C to +85°C

Operating Junction −40°C to +125°C

Storage Temperature −65°C to +150°C

Lead Temperature Range −65°C to +150°C

Soldering (10 sec) 300°C

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

ESD Model

Human Body ±1500 V

Charged Device ±500 V

Machine ±100 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. These are stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL DATA

Absolute maximum ratings apply individually only, not in

Junction-to-ambient thermal resistance (θ

based on modeling and calculation using a 4-layer board. The

junction-to-ambient thermal resistance is highly dependent on

the application and board layout. In applications where high

maximum power dissipation exists, close attention to thermal

board design is required. The value of θ

PCB material, layout, and environmental conditions. The specified

values of θ

to JEDEC JESD 51-9 for detailed information pertaining to board

construction. For additional information, see the AN-617

Application Note, MicroCSP™ Wafer Level Chip Scale Package.

Ψ

is the junction-to-board thermal characterization parameter

JB

measured in units of °C/W. The package Ψ

and calculation using a 4-layer board. The JESD51-12, Guidelines

for Reporting and Using Package Thermal Information, states that

thermal characterization parameters are not the same as thermal

resistances. Ψ

multiple thermal paths rather than through a single path, which

is the procedure for measuring thermal resistance, θ

fore, Ψ

package as well as radiation from the package, factors that make

Ψ

more useful in real-world applications than θJB. Maximum

JB

junction temperature (T

(T

) and power dissipation (PD) using the formula:

B

T

J

Refer to JEDEC JESD51-8 and JESD51-12 for more detailed

information about Ψ

combination.

The ADP2147 can be damaged if the junction temperature limit is

exceeded. Monitoring ambient temperature does not guarantee

that the junction temperature (T

) is within the specified

J

temperature limit. In applications with high power dissipation

and poor thermal resistance, the maximum ambient temperature

may need to be derated. In applications with moderate power

dissipation and low printed circuit board (PCB) thermal

resistance, the maximum ambient temperature can exceed the

maximum limit if the junction temperature is within specification

limits. The junction temperature (T

on the ambient temperature (T

device (P

package (θ

), and the junction-to-ambient thermal resistance of the

D

). Maximum junction temperature (TJ) is calculated

JA

from the ambient temperature (T

) of the device is dependent

J

), the power dissipation of the

A

) and power dissipation (PD)

A

THERMAL RESISTANCE

θJA and ΨJB are specified for the worst-case conditions, that is, a

device soldered in a circuit board for surface-mount packages.

Table 4. Thermal Resistance

Package Type θJA Ψ

6-Ball WLCSP 170 80 °C/W

ESD CAUTION

using the following formula:

T

= TA + (PD × θJA)

J

are based on a 4-layer, 4 in. × 3 in. circuit board. Refer

JA

measures the component power flowing through

JB

thermal paths include convection from the top of the

JB

) is calculated from the board temperature

J

= TB + (PD × ΨJB)

.

JB

) of the package is

JA

may vary, depending on

JA

is based on modeling

JB

. There-

JB

Unit

JB

Rev. 0 | Page 4 of 16

ADP2147

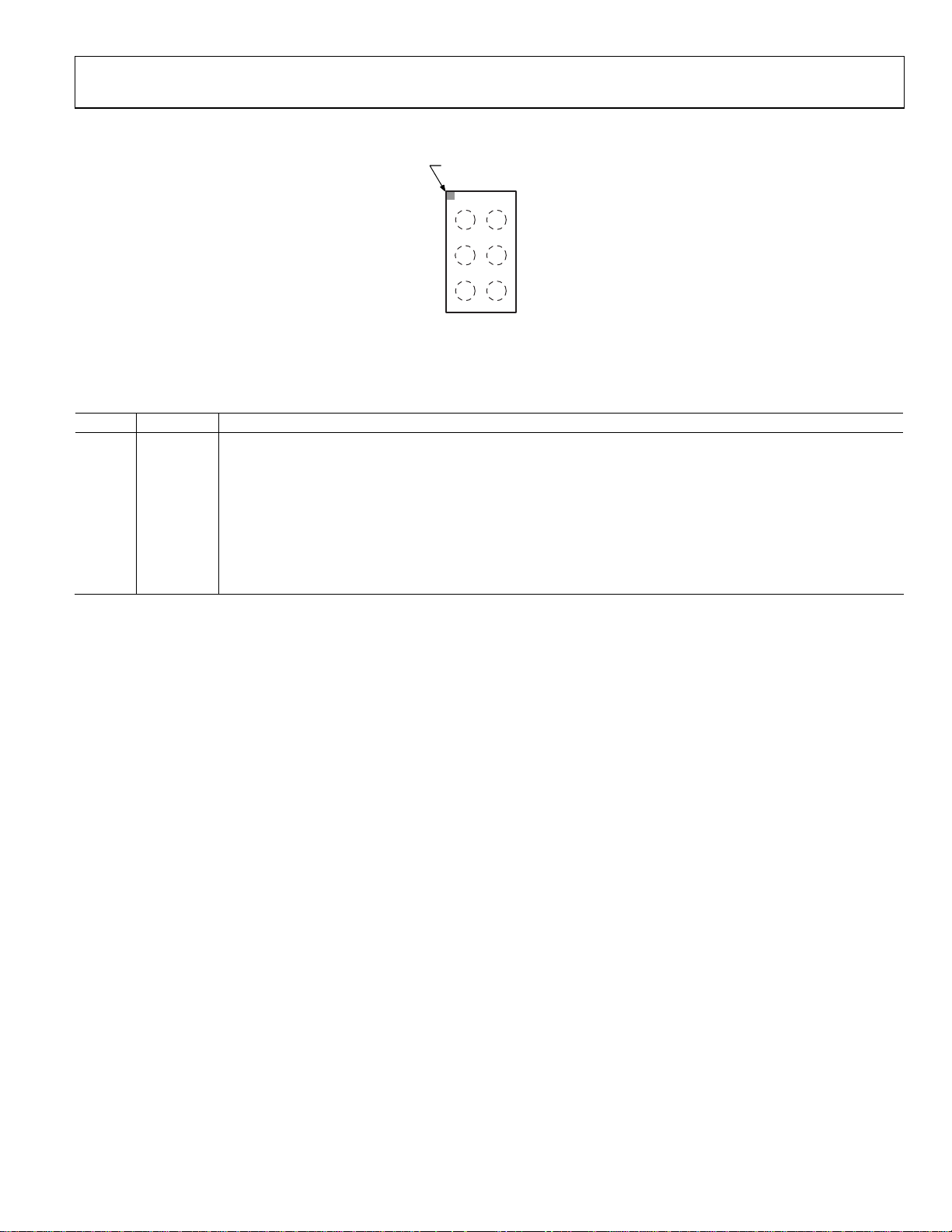

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

BALL A1

INDICA TOR

1

2

VIN EN

A

SW

VSEL

B

GND VOUT

C

ADP2147

TOP VIEW

(BALL SIDE DOWN)

Not to Scale

Figure 2. Pin Configuration (Top View)

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

A1 VIN

Power Source Input. VIN is the source of the pFET high-side switch. Bypass VIN to GND with a 4.7 µF or greater

capacitor as close to the ADP2147 as possible.

B1 SW

Switch Node Output. SW is the drain of the P-channel MOSFET switch and N-channel synchronous rectifier.

Connect the output LC filter between SW and the output voltage.

C1 GND Ground. Connect the input and output capacitors to GND.

A2 EN Buck Activation. To turn on the buck, set EN to high. To turn off the buck, set EN to low.

B2 VSEL

Voltage Select Input for Simple Dynamic Voltage Scaling (DVS). Drive VSEL low to switch the VOUT pin to the

default voltage setting. Drive VSEL high to switch VOUT to the alternate voltage setting.

C2 VOUT Output Voltage Sensing Input.

09885-002

Rev. 0 | Page 5 of 16

ADP2147

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 3.6 V, TA = 25°C, VEN = VIN, unless otherwise noted.

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.001 0.01 0.1 1

I

OUT

(A)

VIN = 2.3V

= 3.6V

V

IN

= 4.2V

V

IN

= 5.5V

V

IN

Figure 3. Efficiency vs. Load Current, Across Input Voltage,

= 1.8 V

V

OUT

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.001 0.01 0.1 1

I

OUT

(A)

VIN = 2.3V

= 3.6V

V

IN

= 4.2V

V

IN

= 5.5V

V

IN

Figure 4. Efficiency vs. Load Current, Across Input Voltage,

V

= 0.8 V

OUT

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.001 0.01 0.1 1

I

OUT

(A)

VIN = 3.9V

V

= 4.2V

IN

V

= 5.5V

IN

Figure 5. Efficiency vs. Load Current, Across Input Voltage,

= 3.3 V

V

OUT

09885-003

09885-005

09885-007

1.825

1.815

1.805

(V)

OUT

V

1.795

1.785

1.775

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

I

OUT

(A)

Figure 6. Load Regulation Across Input Voltage, V

0.815

0.810

0.805

0.800

(V)

OUT

0.795

V

0.790

0.785

0.780

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

I

OUT

(A)

Figure 7. Load Regulation Across Input Voltage, V

3.378

3.358

3.338

3.318

(V)

3.298

OUT

V

3.278

3.258

3.238

3.218

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

I

OUT

(A)

Figure 8. Load Regulation Across Input Voltage, V

VIN = 2.3V

V

= 3.6V

IN

V

= 4.2V

IN

V

= 5.5V

IN

= 1.8 V

OUT

VIN = 2.3V

V

= 3.6V

IN

V

= 4.2V

IN

V

= 5.5V

IN

= 0.8 V

OUT

VIN = 3.9V

V

= 4.2V

IN

V

= 5.5V

IN

= 3.3 V

OUT

09885-006

09885-008

09885-009

Rev. 0 | Page 6 of 16

ADP2147

3.5

3.4

3.3

3.2

3.1

3.0

2.9

FREQUENCY (MHz)

2.8

2.7

2.6

2.5

0.10.20.30.40.50.60.7

I

OUT

(A)

Figure 9. Frequency vs. Output Current, Across Temperature,

= 1.8 V

V

OUT

3.5

3.4

3.3

3.2

3.1

3.0

2.9

FREQUENCY ( MHz)

2.8

2.7

2.6

2.5

0.10.20.30.40.50.60.7

I

OUT

(A)

Figure 10. Frequency vs. Output Current, Across Supply Voltage,

= 1.8 V

V

OUT

90

80

70

60

50

40

30

OUTPUT VOLTAGE (mV)

20

10

I

= 100µA

OUT

I

= 25mA

OUT

I

= 500mA

OUT

0

2.3 2.8 3.3 3.8 4.3 4.8 5.3

INPUT VOLTAGE (V)

Figure 11. Output Voltage Ripple vs. Input Voltage,

Across Output Current, V

OUT

= 1.8 V

+25°C

+85°C

+125°C

–40°C

VIN = 2.3V

VIN = 3.6V

VIN = 4.2V

VIN = 5.5V

350

300

250

200

(mΩ)

150

DSON

R

100

50

0

2.3 2.8 3.3 3.8 4.3 4.8 5.3

09885-010

Figure 12. R

DSON

INPUT VOLTAGE (V)

PFET vs. Input Voltage, Across Temperature

–40°C

+25°C

+125°C

09885-036

250

200

150

(mΩ)

DSON

100

R

50

0

2.3 2.8 3.3 3.8 4.3 4.8 5.3

09885-011

Figure 13. R

DSON

INPUT VOLTAGE (V)

NFET vs. Input Voltage, Across Temperature

–40°C

+25°C

+125°C

09885-037

T

4

4

1

1

2

CH1 100mV

09885-034

CH2 250mA Ω

CH4 5.00V

SW

V

OUT

I

OUT

M 40.0µs A CH2 215mA

T

2

6

.

0

0

%

09885-014

Figure 14. Response to Load Transient, 150 mA to 500 mA,

V

= 1.8 V

OUT

Rev. 0 | Page 7 of 16

ADP2147

T

4

4

1

1

V

I

SW

OUT

OUT

4

4

1

1

T

SW

V

OUT

I

OUT

2

CH1 100mV

CH2 250mA Ω

CH4 5.00V

M 40.0µs A CH2 215mA

T

2

6

.

0

0

%

Figure 15. Response to Load Transient, 50 mA to 200 mA,

= 1.8 V

V

OUT

4

4

1

1

2

CH1 100mV

T

CH2 250mA Ω

CH4 5.00V

SW

V

OUT

I

OUT

M 40.0µs A CH2 215mA

T

2

6

.

0

0

%

Figure 16. Response to Load Transient, 150 mA to 500 mA,

= 0.8 V

V

OUT

T

SW

2

CH1 100mV

09885-015

CH2 250mA Ω

CH4 5.00V

M 40.0µs A CH2 275mA

T

2

6

.

0

0

%

09885-018

Figure 18. Response to Load Transient, 150 mA to 500 mA,

= 3.3 V

V

OUT

T

4

4

1

1

2

CH1 100mV

09885-016

CH2 100mA Ω

CH4 5.00V

SW

V

OUT

I

OUT

M 40.0µs A CH2 114mA

T

2

6

.

0

0

%

09885-019

Figure 19. Response to Load Transient, 50 mA to 200 mA,

= 3.3 V

V

OUT

T

4

4

V

OUT

1

1

I

OUT

2

CH1 100mV

CH2 100mA Ω M 40.0µs A CH2 134mA

CH4 5.00V

T

2

6

.

0

0

%

Figure 17. Response to Load Transient, 50 mA to 200 mA, V

OUT

09885-017

= 0.8 V

Rev. 0 | Page 8 of 16

V

IN

V

1

3

CH1 20.0mV

CH3 1.00V

OUT

M 40.0µs A CH3 4.50V

T –84.0000µs

Figure 20. Response to Line Transient, V

= 3.3 V, VIN = 4.0 V to 4.8 V

OUT

09885-020

ADP2147

T

V

IN

V

1

3

OUT

T

4

2

1

1

1

3

SW

I

IN

V

OUT

E

N

CH1 20.0mV

CH3 1.00V

Figure 21. Response to Line Transient, V

= 4.0 V to 4.8 V

V

IN

V

V

1

3

CH1 20.0mV

CH3 1.00V

OUT

Figure 22. Response to Line Transient, V

V

= 4.0 V to 4.8 V

IN

T

4

2

SW

I

M 40.0µs A CH3 4.50V

T –84.0000µs

= 0.8 V,

OUT

T

IN

M 40.0µs A CH3 4.50V

T –84.0000µs

= 1.8 V,

OUT

IN

CH1 1.00V Ω

09885-021

CH3 5.00V

CH2 500mA Ω M 40.0µs A CH3 2.50V

CH4 5.00V

Figure 24. Startup, V

= 0.8 V, I

OUT

T

1

0

.

4

0

%

OUT

= 10 mA

09885-023

T

4

2

1

1

1

3

CH1 5.00V Ω

09885-033

CH3 5.00V

CH2 500mA Ω M 40.0µs A CH3 2.50V

CH4 5.00V

Figure 25. Startup, V

4

4

SW

I

SW

I

IN

V

OUT

E

N

T

1

0

.

4

0

%

= 3.3 V, I

OUT

T

L

= 10 mA

OUT

09885-024

1

1

1

3

CH1 2.00V Ω

CH3 5.00V

V

OUT

E

N

CH2 500mA Ω M 40.0µs A CH3 2.50V

CH4 5.00V

Figure 23. Startup, V

= 1.8 V, I

OUT

T

1

0

.

4

0

%

OUT

= 10 mA

09885-022

Rev. 0 | Page 9 of 16

2

V

OUT

1

1

CH1 10.0mVΩ

CH2 500mA Ω

CH4 2.00V

Figure 26. Typical Waveform, V

A CH1 3.80mVM 1.00µs

T

5

0

.

0

0

%

= 1.8 V, PSM Mode, I

OUT

= 10 mA

OUT

09885-025

ADP2147

SW

4

I

L

2

V

OUT

1

1

T

1

2

T

CH1 10.0mVΩ CH2 500m A Ω

CH4 2.00V

Figure 27. Typical Waveform, V

T

= 1.8 V, PWM Mode, I

OUT

A CH4 1.32VM 40.0µs

5

0

.

0

0

%

130

120

110

100

RIPPLE (mV)

OUT

V

Figure 28. V

1.8V, VIN = 5.5V, AUTO

1.8V, VIN = 3.6V, AUTO

1.8V, VIN = 2.3V, AUTO

90

80

70

60

50

40

30

20

10

0

0.001 0.01 0. 1 1

Peak-to-Peak Ripple vs. Output Current, V

OUT

I

OUT

T

(A)

= 200 mA

OUT

= 1.8 V

OUT

CH1 100mV CH2 2.00V

09885-026

T 79.64µs

A CH2 1.72VM 40.0µs

09885-130

Figure 30. VSEL Change Triggering VOUT Transition from 1.275 V to 0.981 V,

= 10 mA

I

LOAD

T

1

2

CH1 100mV CH2 2.00V

09885-028

T 50.20%

A CH2 1.76VM 40.0µs

09885-131

Figure 31. VSEL Change Triggering VOUT Transition from 0.981 V to1.275 V,

I

= 200 mA

LOAD

T

1

2

CH1 100mV CH2 2.00V

T –1.966µs

A CH2 1.72VM 40.0µs

09885-129

Figure 29. VSEL Change Triggering VOUT Transition from 0.981 V to 1.275 V,

= 10 mA

I

LOAD

Rev. 0 | Page 10 of 16

1

2

CH1 100mV CH2 2.00V

T 30.00%

A CH2 1.76VM 40.0µs

09885-132

Figure 32. VSEL Change Triggering VOUT Transition from1.275 V to 0.981 V, I

= 200 mA

LOAD

ADP2147

THEORY OF OPERATION

PWM

COMP

GM ERROR

AMP

SOFT START

VOUT

PSM

COMP

CONTROL

OSCILL ATOR

UNDERVOLTAG E

LOCKOUT

VSEL

ADP2147

Figure 33. Functional Block Diagram

The ADP2147 is a step-down dc-to-dc regulator that uses a

fixed frequency and high speed current-mode architecture.

The high switching frequency and tiny 6-ball WLCSP package

enable a small step-down dc-to-dc regulator solution.

The ADP2147 operates with an input voltage of 2.3 V to 5.5 V

and regulates an output voltage down to 0.8 V.

CONTROL SCHEME

The ADP2147 operates with a fixed frequency, current-mode

PWM control architecture at medium to high loads for high

efficiency but shifts to a power save mode control scheme at

light loads to lower the regulation power losses. When operating in

PWM mode, the duty cycle of the integrated switches is adjusted

and regulates the output voltage. When operating in power save

mode at light loads, the output voltage is controlled in a hysteretic manner, with higher V

ripple. During part of this time,

OUT

the converter is able to stop switching and enters an idle mode,

which improves conversion efficiency.

PWM MODE

In PWM mode, the ADP2147 operates at a fixed frequency of

3 MHz, set by an internal oscillator. At the start of each oscillator

cycle, the pFET switch is turned on, sending a positive voltage

across the inductor. Current in the inductor increases until the

magnitude of the current sense signal crosses the peak inductor

current threshold. This turns off the pFET switch and turns on the

nFET synchronous rectifier, which sends a negative voltage across

the inductor, causing the inductor current to decrease. The

synchronous rectifier stays on for the rest of the cycle.

The ADP2147 regulates the output voltage by adjusting the peak

inductor current threshold.

PWM/

PSM

EN

VIN

I

LIMIT

LOW

CURRENT

DRIVER

AND

ANTISHOO T-

THROUGH

THERMAL

SHUTDOWN

SW

GND

09885-027

POWER SAVE MODE

The ADP2147 smoothly transitions to the power save mode of

operation when the load current decreases below the power

save mode current threshold. When the ADP2147 enters power

save mode, an offset is induced in the PWM regulation level,

which makes the output voltage rise. When the output voltage

reaches a level approximately 1.5% above the PWM regulation

level, PWM operation turns off. At this point, both power

switches are off, and the ADP2147 enters idle mode. C

discharges until V

falls to the PWM regulation voltage, at

OUT

which point the device drives the inductor to cause V

OUT

OUT

again to the upper threshold. This process is repeated for as long as

the load current is below the power save mode current

threshold.

Power Save Mode Current Threshold

The power save mode current threshold is set to 100 mA. The

ADP2147 employs a scheme that ensures that this current is

accurately controlled and independent of V

and V

IN

OUT

levels.

The control scheme also ensures that there is very little hysteresis

between the power save mode current threshold and that of the

PWM mode. The power save mode current threshold is optimized for excellent efficiency across all load currents.

ENABLE/SHUTDOWN

The ADP2147 starts operating with soft start when the EN pin

is toggled from logic low to logic high. Pulling the EN pin low

forces the device into shutdown mode, reducing the supply

current to 0.2 A (typical).

to rise

Rev. 0 | Page 11 of 16

ADP2147

SIMPLE DYNAMIC VOLTAGE SCALING (DVS)

The ADP2147 has a VSEL pin that allows the user to force the

output voltage to change from one level (the default VOUT

setting) when VSEL is low and to another level (the alternate

VOUT setting) when VSEL is high. Transition between VOUT

levels is achieved within 40 µs when VOUT is commanded to go

from a lower voltage to a higher voltage. When VOUT is commanded to go from a higher VOUT voltage to a lower one, the

transition time depends on the load current present at that time.

SHORT-CIRCUIT PROTECTION

The ADP2147 includes frequency foldback to prevent output

current runaway on a hard short. When the voltage at the

feedback pin falls below half the target output voltage, indicating the possibility of a hard short at the output, the switching

frequency is reduced to half the internal oscillator frequency.

The reduction in the switching frequency allows more time for

the inductor to discharge, preventing a runaway of output current.

UNDERVOLTAGE LOCKOUT

To protect against battery discharge, undervoltage lockout

(UVLO) circuitry is integrated on the ADP2147. If the input

voltage drops below the 2.15 V UVLO threshold, the ADP2147

shuts down, and both the power switch and the synchronous

rectifier turn off. When the voltage rises above the UVLO

threshold, the soft start period is initiated, and the part is

enabled.

THERMAL PROTECTION

In the event that the ADP2147 junction temperature rises above

150°C, the thermal shutdown circuit turns off the regulator.

Extreme junction temperatures can be the result of high current

operation, poor circuit board design, or high ambient temperature.

A 20°C hysteresis is included so that when thermal shutdown

occurs, the ADP2147 does not return to operation until the onchip temperature drops below 130°C. When coming out of

thermal shutdown, a soft start is initiated.

SOFT START

The ADP2147 has an internal soft start function that ramps the

output voltage in a controlled manner upon startup, thereby

limiting the inrush current. The soft start minimizes input

voltage drop when a battery or a high impedance power source is

connected to the regulator’s input.

After the EN pin is driven high, internal circuits begin to power

up. Start-up time in the ADP2147 is the measure of when the

output is in regulation after the EN pin is driven high. Start-up

time consists of the power-up time plus the soft start time.

CURRENT LIMIT

The ADP2147 has protection circuitry to limit the amount of

positive current flowing through the PFET switch and the

synchronous rectifier. The positive current limit on the power

switch controls the amount of current that can flow from the

power source to the output. The negative current limit prevents

the inductor current from reversing direction and flowing out

of the load.

100% DUTY OPERATION

With a drop in VIN or with an increase in I

eventually reaches a limit where, even with the pFET switch on

100% of the time, V

At this limit, the ADP2147 smoothly transitions to a mode

where the PFET switch stays on 100% of the time. When the input

conditions change again and the required duty cycle falls, the

ADP2147 immediately restarts PWM regulation without

allowing overshoot on V

drops below the desired output voltage.

OUT

.

OUT

, the ADP2147

LOAD

Rev. 0 | Page 12 of 16

ADP2147

APPLICATIONS INFORMATION

EXTERNAL COMPONENT SELECTION

Trade-offs between performance parameters such as efficiency

and transient response can be made by varying the choice of

external components in the applications circuit, as shown in

Figure 1.

Inductor

The high switching frequency of the ADP2147 allows for the

selection of small chip inductors. For best performance, use

inductor values between 0.7 H and 3 H. Recommended

inductors are shown in Tab le 6.

The peak-to-peak inductor current ripple is calculated using

the following equation:

VVV

−×

I

RIPPLE

OUT

LfV

××

2

)(

Dimensions

(mm)

I

SAT

(mA)

DCR

(mΩ)

I

RIPPLE

OUT

=

IN

IN

SW

where:

f

is the switching frequency.

SW

L is the inductor value.

The minimum dc current rating of the inductor must be greater

than the inductor peak current. The inductor peak current is

calculated using the following equation:

II +=

PEAK

)(

MAXLOAD

Inductor conduction losses are caused by the flow of current

through the inductor, which has an associated internal DCR.

Larger sized inductors have smaller DCR, which may decrease

inductor conduction losses. Inductor core losses are related to

the magnetic permeability of the core material. Because the

ADP2147 is a high switching frequency dc-to-dc regulator,

shielded ferrite core material is recommended for its low core

losses and low electromagnetic interference (EMI). Tab l e 6

shows the suggested inductors that can be used for different

output current requirements; several inductors are also listed to

minimize PCB space for small current applications.

Table 6. Suggested 1.0 μH Inductors

Vendor Model

Murata LQM2MPN1R0NG0B 2.0 × 1.6 × 0.9 1400 85

LQM18PN1R0 1.6 × 0.8 × 0.33 700 52

Coilcraft® EPL2014-102ML 2.0 × 2.0 × 1.4 900 59

0603LS-102 1.8 × 1.27 × 1.1 400 81

Toko MDT2520-CN 2.5 × 2.0 × 1.2 1800 100

TDK GLFR1608T1R0M-LR 1.6 × 0.8 × 0.8 360 80

Taiyo Yuden CBMF1608T1R0M 1.6 × 0.8 × 0.8 290 90

Output Capacitor

Increasing the value of the output capacitor reduces the output

voltage ripple and improves load transient response. When

choosing the capacitor value, it is also important to account for

the loss of capacitance due to dc output voltage bias.

Ceramic capacitors are manufactured with a variety of dielectrics,

each with different behavior over temperature and applied voltage.

Capacitors must have a dielectric adequate to ensure the

minimum capacitance over the necessary temperature range

and dc bias conditions. X5R or X7R dielectrics with a voltage

rating of 6.3 V or 10 V are recommended for best performance.

Y5V and Z5U dielectrics are not recommended for use with any

dc-to-dc regulator because of their poor temperature and dc bias

characteristics.

The worst-case capacitance, accounting for capacitor variation

over temperature, component tolerance, and voltage, is

calculated using the following equation:

C

= C

EFF

× (1 − TEMPCO) × (1 − TOL)

OUT

where:

C

is the effective capacitance at the operating voltage.

EFF

TEMPCO is the worst-case capacitor temperature coefficient.

TOL is the worst-case component tolerance.

In this example, the worst-case temperature coefficient (TEMPCO)

over −40°C to +85°C is assumed to be 15% for an X5R dielectric.

The tolerance of the capacitor (TOL) is assumed to be 10%, and

C

is 4.0466 F at 1.8 V, as shown in Figure 34.

OUT

Substituting these values in the equation yields

C

= 4.0466 F × (1 − 0.15) × (1 − 0.1) = 3.0956 F

EFF

To guarantee the performance of the ADP2147, it is imperative

that the effects of dc bias, temperature, and tolerances on the

behavior of the capacitors be evaluated for each application.

6

5

4

3

2

CAPACITANCE (µ F)

1

0

0123456

Figure 34. Typical Capacitor Performance

DC BIAS VOL TAGE (V)

09885-029

The peak-to-peak output voltage ripple for the selected output

capacitor and inductor values is calculated using the following

equation:

V

RIPPLE

=

()

π

SW

IN

CLf

××××

22

OUT

RIPPLE

SW

CfI××=8

OUT

V

Rev. 0 | Page 13 of 16

ADP2147

E

Capacitors with lower equivalent series resistance (ESR) are

preferred to guarantee low output voltage ripple, as shown in

the following equation:

V

ESR ≤

COUT

RIPPLE

I

RIPPL

The effective capacitance needed for stability, which includes

temperature and dc bias effects, is 3 µF.

Table 7. Suggested 4.7 μF Capacitors

Vendor Type Model

Case

Size

Voltage

Rating (V)

Murata X5R GRM188R60J475 0603 6.3

Taiyo Yuden X5R JMK107BJ475 0603 6.3

TDK X5R C1608X5R0J475 0603 6.3

Input Capacitor

Higher value input capacitors help to reduce the input voltage

ripple and improve transient response. Maximum input

capacitor current is calculated using the following equation:

−

VVV

CIN

IN

≥

II

MAXLOAD

OUT

)(

V

IN

OUT

)(

To minimize supply noise, place the input capacitor as close to

the VIN pin of the ADP2147 as possible. As with the output

capacitor, a low ESR capacitor is recommended. The list of

recommended capacitors is shown in Tabl e 8.

Table 8. Suggested 4.7 μF Capacitors

Vendor Type Model

Case

Size

Voltage

Rating (V)

Murata X5R GRM188R60J475 0603 6.3

Taiyo Yuden X5R JMK107BJ475 0603 6.3

TDK X5R C1608X5R0J475 0603 6.3

THERMAL CONSIDERATIONS

Because of the high efficiency of the ADP2147, only a small

amount of power is dissipated inside the ADP2147 package, which

reduces thermal constraints of the design.

However, in applications with maximum loads at high ambient

temperature, low supply voltage, and high duty cycle, the heat

dissipated in the package is high enough that it may cause the

junction temperature of the die to exceed the 125°C maximum.

If the junction temperature exceeds 150°C, the converter enters

thermal shutdown. The regulator recovers when the junction

temperature falls below 130°C.

The junction temperature of the die is the sum of the ambient

temperature of the environment and the temperature rise of the

package due to power dissipation, as shown in the following

equation:

T

= TA + TR

J

where:

TJ is the junction temperature.

T

is the ambient temperature.

A

T

is the rise in temperature of the package due to power

R

dissipation.

The package’s rise in temperature is directly proportional to the

power dissipation in the package. The proportionality constant

for this relationship is the thermal resistance from the junction

of the die to the ambient temperature, as shown in the following

equation:

T

= θJA × PD

R

where:

T

is the rise in temperature of the package.

R

θJA is the thermal resistance from the junction of the die to the

ambient temperature of the package.

P

is the power dissipation in the package.

D

PCB LAYOUT GUIDELINES

Poor layout can affect the ADP2147 performance, causing EMI

and electromagnetic compatibility problems, ground bounce,

and voltage losses. Poor layout can also affect regulation and

stability. To implement a good layout, use the following rules:

• Place the inductor, input capacitor, and output capacitor

close to the IC using short tracks. These components carry

high switching frequencies, and large tracks act as antennas.

• Route the output voltage path away from the inductor and

SW node to minimize noise and magnetic interference.

• Maximize the size of ground metal on the component side

to help with thermal dissipation.

• Use a ground plane with several vias connecting to the com-

ponent side ground to further reduce noise interference on

sensitive circuit nodes.

Rev. 0 | Page 14 of 16

ADP2147

G

V

EVALUATION BOARD

TB1

VIN

JP3

ENABLE

JP2

VSEL

TB5

ND IN

EVALUATION BOARD LAYOUT

CONN PWR 2-P

J6

VIN

VIN

3

3

EN

2

2

1

1

3

3

2

2

1

1

GND

IN GND

VIN

2

1

ADP2147

A1

CIN

4.7µF

VIN

C1

GND

A2

EN

B2

VSEL

SW

U1

VOUT

Figure 35. Evaluation Board Schematic

B1 21

C2

L1

1µH

COUT

4.7µF

TB3

TB4

VOUT

GND OUT

09885-030

Figure 36. Top Layer

09885-136

Figure 37. Bottom Layer

09885-137

Rev. 0 | Page 15 of 16

ADP2147

OUTLINE DIMENSIONS

1.070

1.030

0.990

BALL A1

IDENTIFIER

0.640

0.595

0.550

SEATING

PLANE

TOP VIEW

(BALL SIDE DOWN)

SIDE VIEW

0.340

0.320

0.300

1.545

1.505

1.465

0.370

0.355

0.340

1.00

REF

0.50

REF

0.50 REF

COPLANARITY

0.05

0.270

0.240

0.210

Figure 38. 6-Ball Wafer Level Chip Scale Package [WLCSP]

(CB-6-12)

Dimensions shown in millimeters

ORDERING GUIDE

Model1

Temperature

Range

(V)

V

OUT

(VSEL = 0)

ADP2147ACBZ-110-R7 −40°C to +125°C 1.275 0.981 6-Ball Wafer Level Chip Scale Package [WLCSP] CB-6-12 LLE

ADP2147ACBZ-130-R7 −40°C to +125°C 0.9 1.3 6-Ball Wafer Level Chip Scale Package [WLCSP] CB-6-12 LLF

ADP2147ACBZ-150-R7 −40°C to +125°C 1.2 1.0 6-Ball Wafer Level Chip Scale Package [WLCSP] CB-6-12 LLG

ADP2147ACBZ-170-R7 −40°C to +125°C 0.9 1.1 6-Ball Wafer Level Chip Scale Package [WLCSP] CB-6-12 LLH

ADP2147CB-110EVALZ Evaluation Board

ADP2147CB-130EVALZ Evaluation Board

ADP2147CB-150EVALZ Evaluation Board

ADP2147CB-170EVALZ Evaluation Board

1

Z = RoHS Compliant Part.

(V)

V

OUT

(VSEL = 1) Package Description

12

BOTTOM VIEW

(BALL SIDE UP)

A

B

C

12-07-2010-A

Package

Option Branding

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09885-0-5/11(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...