Ultralow Profile, 500 mA, 6 MHz, Synchronous,

V

FEATURES

1.20 V and 1.26 V fixed output voltage options

Clock signal enable

Logic signal enable also available on certain models

6 MHz operating frequency

Spread spectrum frequency modulation to reduce EMI

500 mA continuous output current

Input voltage: 2.1 V to 5.5 V

0.3 μA (typical) shutdown supply current

Pin-selectable power-saving mode

Compatible with tiny multilayer inductors

Internal synchronous rectifier

Internal compensation

Internal soft start

Output-to-ground short-circuit protection

Current-limit protection

Undervoltage lockout

Thermal shutdown protection

0.330 mm height (maximum), 6-ball BUMPED_CHIP (ADP2126)

0.200 mm height (maximum), 6-pad EWLP (ADP2127)

APPLICATIONS

Mobile phones

Digital still/video cameras

Digital audio

Portable equipment

Camera modules

Image stabilization systems

GENERAL DESCRIPTION

The ADP2126/ADP2127 are high frequency, step-down, dc-todc converters optimized for portable applications in which board

area and battery life are critical constraints. The fixed 6 MHz

operating frequency enables the use of tiny ceramic inductors

and capacitors and the regulators use spread spectrum frequency

modulation to reduce EMI. Additionally, synchronous rectification

improves efficiency and results in fewer external components.

At high load currents, the ADP2126/ADP2127 use a voltage

regulating pulse-width modulation (PWM) mode that maintains

a constant frequency with excellent stability and transient response.

Light load operation is determined by the state of the MODE pin.

In forced PWM mode, the converter continues operating in PWM

for light loads. Under light load conditions in auto mode, the

ADP2126/ADP2127 automatically enter a power-saving mode,

which uses pulse frequency modulation (PFM) to reduce the

effective switching frequency, thus ensuring the longest battery

life in portable applications.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Step-Down, DC-to-DC Converters

ADP2126/ADP2127

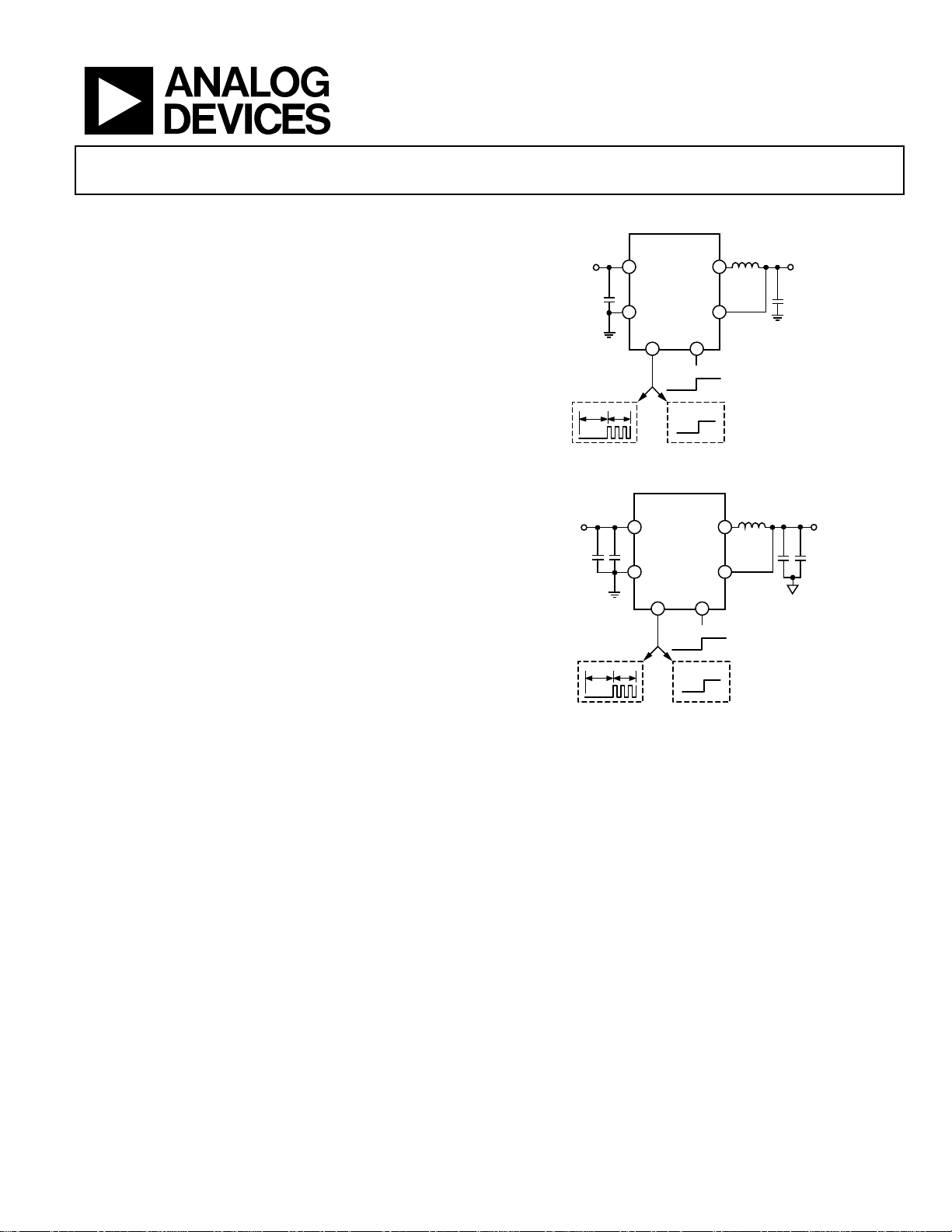

TYPICAL APPLICATION CIRCUITS

SW

PWM

ON

SW

PWM

ON

L

1.0µH

B1

C1

*

L

0.56µH

B1

C1

*

OUTPUT

VOLTAGE

1.20V OR 1. 26V

C

OUT

2.2µF

OUTPUT

VOLTAGE

1.20V OR 1.26V

C

OUT

2 × 1µF

INPUT

VOLTAGE

2.1V TO 5.5V

C

IN

2.2µF

OFF ON

*LOGIC HI GH ENABLE I S ONLY AVAI LABLE ON CE RTAIN MODELS.

ADP2126

A2

VIN

C2

GND FB

EXTCLK MODE

B2 A1

AUTO

OR

OFF

Figure 1. ADP2126 0.33 mm Maximum Height Solution

INPUT

VOLTAGE

2.1V TO 5. 5

C

IN

2 × 1µF

OFF ON

*LOGIC HI GH ENABLE IS ONLY AVAIL ABLE ON CERTAIN MODELS.

ADP2127

A2

VIN

C2

GND FB

EXTCLK MODE

B2 A1

AUTO

OR

OFF

Figure 2. ADP2127 0.22 mm Maximum Height Solution

The ADP2126/ADP2127 are enabled by a 6 MHz to 27 MHz

external clock signal applied to the EXTCLK pin. Certain models

can also be enabled with a logic high signal. When the external clock

is not switching and in a low logic state, the ADP2126/ADP2127

stop regulating and shut down to draw less than 0.3 µA (typical)

from the source.

The ADP2126/ADP2127 have an input voltage range of 2.1 V to

5.5 V, allowing the use of single Li+/Li polymer cell, three-cell

alkaline, NiMH cell, and other standard power sources. The

ADP2126/ADP2127 are internally compensated to minimize

external components and can source up to 500 mA. Other key

features, such as cycle-by-cycle peak current limit, soft start,

undervoltage lockout (UVLO), output-to-ground short-circuit

protection, and thermal shutdown provide protection for internal

and external circuit components.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

09658-001

09658-002

ADP2126/ADP2127

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Typical Application Circuits............................................................ 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Diagrams.......................................................................... 4

Absolute Maximum Ratings............................................................ 5

Thermal Considerations.............................................................. 5

Thermal Resistance ...................................................................... 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics ............................................. 7

Theory of Operation ...................................................................... 11

Overview...................................................................................... 11

External Clock (EXTCLK) Enable........................................... 11

Spread Spectrum Oscillator ...................................................... 12

Mode Selection ........................................................................... 12

Internal Control Features.......................................................... 12

Protection Features .................................................................... 13

Timing Constraints.................................................................... 13

Applications Information.............................................................. 14

Inductor Selection...................................................................... 14

Input Capacitor Selection.......................................................... 14

Output Capacitor Selection....................................................... 15

Thermal Considerations............................................................ 15

PCB Layout Guidelines.................................................................. 16

Outline Dimensions....................................................................... 17

Ordering Guide .......................................................................... 18

REVISION HISTORY

5/11—Rev. 0 to Rev. A

Changes to Figure 35...................................................................... 17

5/11—Revision 0: Initial Version

Rev. A | Page 2 of 20

ADP2126/ADP2127

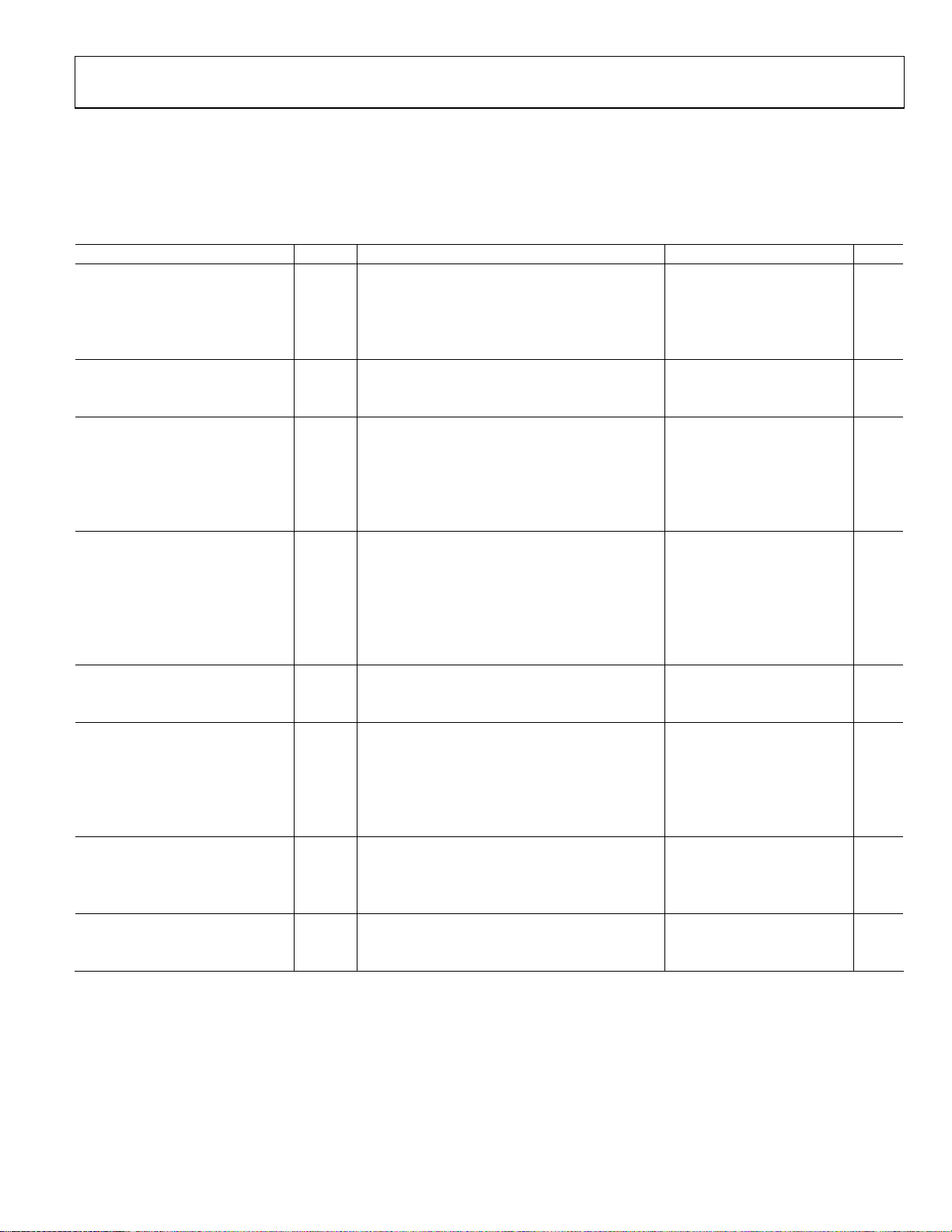

SPECIFICATIONS

VIN = 3.6 V, TA = 25°C for typical specifications, and TA = TJ = −40°C to +85°C for minimum and maximum specifications, unless

otherwise noted.

(SQC) methods. Typical specifications are not guaranteed.

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

SUPPLY

Operating Input Voltage Range VIN 2.1 5.5 V

PWM Mode Quiescent Current No load, V

Auto Mode Quiescent Current No load, V

Shutdown Current1 V

UNDERVOLTAGE LOCKOUT

Rising VIN Threshold 1.9 2.1 V

Falling VIN Threshold 1.5 1.8 V

OUTPUT

Continuous Output Current2 I

PWM Mode Output Accuracy

PFM Mode Output Accuracy

FB Bias Current VFB = V

FB Pull-Down Resistance R

SWITCHING CHARACTERISTICS

PMOS On Resistance ISW = 500 mA 180 340 mΩ

NMOS On Resistance ISW = 500 mA 250 mΩ

SW Leakage Current VSW = 0 V, VIN = 5.5 V 10 μA

PMOS Switch Current Limit Open loop 770 1000 1291 mA

PFM Current Limit V

Oscillator Frequency fSW 4.8 6 6.8 MHz

SHORT-CIRCUIT PROTECTION

Rising V

Falling V

EXTCLK INPUT

High Threshold Voltage V

Low Threshold Voltage V

Leakage Current VIN = 5.5 V, V

Duty Cycle Operating Range D

Frequency Operating Range f

MODE INPUT LOGIC

High Threshold Voltage V

Low Threshold Voltage V

Leakage Current V

THERMAL SHUTDOWN5 PWM mode only

Thermal Shutdown Threshold 146 °C

Thermal Shutdown Hysteresis 13 °C

All specifications at temperature extremes are guaranteed via correlation using the standard statistical quality control

= VIN 12 mA

MODE

= 0 V, VFB > V

MODE

= 0 V, open loop 0.3 1.5 μA

EXTCLK

VIN = 2.1 V to 5.5 V 500 mA

LOAD

3

V

VIN = 2.1 V to 5.5 V, no load V

3, 4

Threshold 0.55 0.7 V

OUT

Threshold 0.4 0.52 V

OUT

OUT

VIN = 2.1 V to 5.5 V V

4 9 μA

OUT

V

DSCHG

VIN = 2.1 V to 5.5 V 1.3 V

EXTCLK(H)

VIN = 2. 1 V to 5.5 V 0.4 V

EXTCLK(L)

40 60 %

EXTCLK

6 27 MHz

EXTCLK

VIN = 2.1 V to 5.5 V 1.3 V

MODE(H)

VIN = 2.1 V to 5.5 V 0.4 V

MODE(L)

= 0 V, IFB = 10 mA 110 180 Ω

EXTCLK

= 0 V, VIN = 3.6 V 170 260 305 mA

MODE

= 2.1 V to 5.5 V 0.01 1 μA

EXTCLK

= 0 V, VIN = V

EXTCLK

MODE

, SW = open 300 500 μA

OUT

− 2% V

OUT

− 3% V

OUT

+ 2% V

OUT

+ 3% V

OUT

= 5.5 V 0.005 1 μA

Rev. A | Page 3 of 20

ADP2126/ADP2127

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

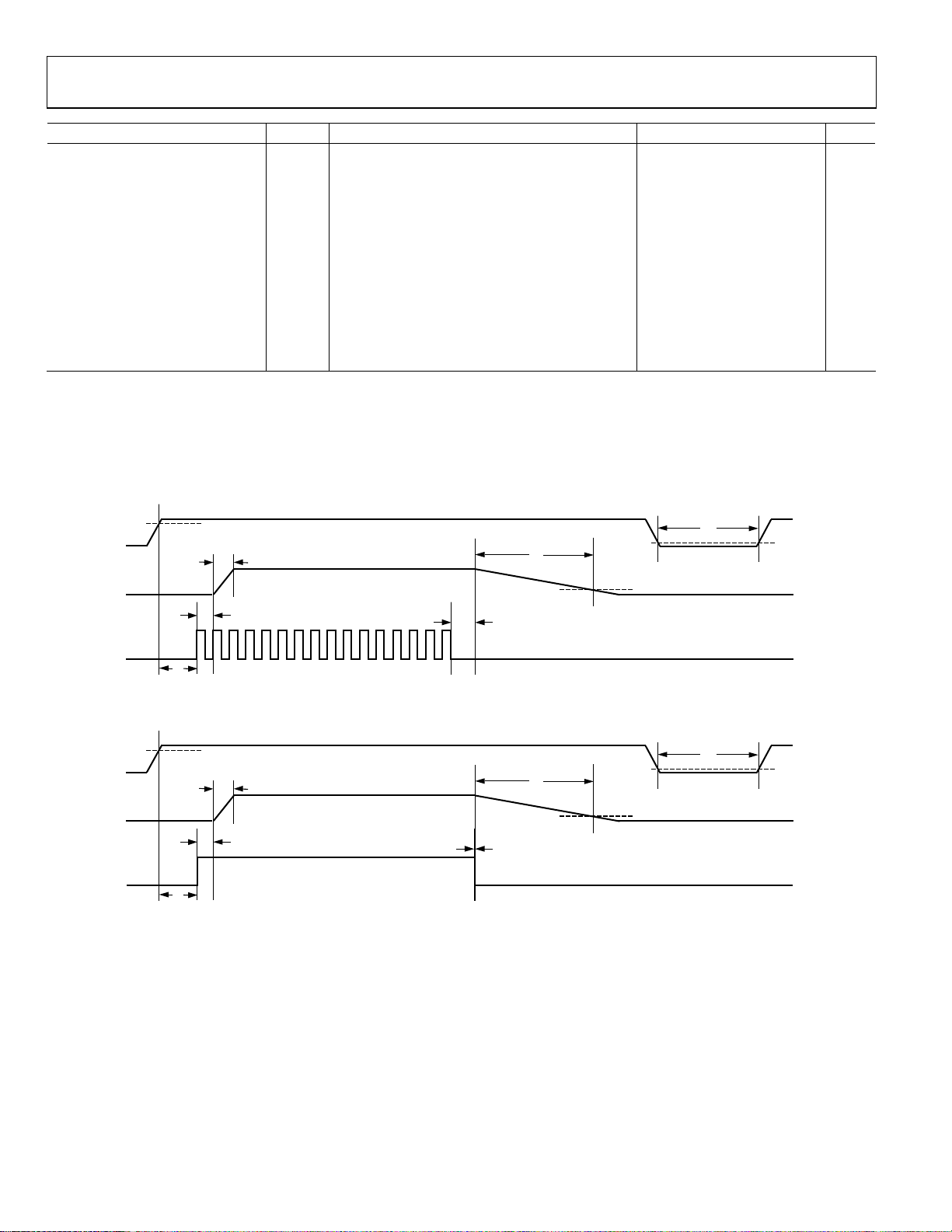

TIMING See Figure 3 and Figure 4

VIN High to EXTCLK On2 t1 V

EXTCLK On to V

Rising t

OUT

2 (CLOCK)

D

EXTCLK On to V

V

Power-Up Time (Soft Start)2 t3 C

OUT

EXTCLK Off to V

EXTCLK Off to V

V

Power-Down Time t6 C

OUT

Rising t

OUT

Falling t

OUT

Falling t

OUT

2 (LOGIC)

5 (CLOCK)

5 (LOGIC)

C

Minimum Shutdown Time2 t

Minimum Power-Off Time2 t

1

The total shutdown current is the addition of VIN shutdown current and SW leakage.

2

Guaranteed by design.

3

Transients not included in voltage accuracy specifications.

4

The PFM output voltage will be higher than the PWM output voltage. See the Typi section. cal Performance Characteristics

5

Thermal shutdown protection is only active in PWM mode.

+ t6 C

5

500 μs

7

TIMING DIAGRAMS

= 2.1 V to 5.5 V 200 μs

IN

D

= 40% to 60%, f

EXTCLK

= 40% to 60%, f

EXTCLK

= 6 MHz 250 320 400 μs

EXTCLK

= 27 MHz 250 320 400 μs

EXTCLK

EXTCLK = logic high 285 315 385 μs

OUT

D

EXTCLK

= 2.2 μF, R

= 40% to 60%, f

= 3.6 Ω 70 200 μs

LOAD

= 6 MHz to 27 MHz 9 17 μs

EXTCLK

EXTCLK = logic high, no load 0 μs

= 2.2 μF, R

OUT

= 2.2 μF, no load 465 μs

OUT

= 2.2 μF, no load 1400 μs

OUT

= 3.6 Ω 16 μs

LOAD

VIN

V

OUT

EXTCLK

t

1

VIN × 90%

t

3

t

2

t

6

V

OUT(NOM)

t

5

× 10%

t

7

V

× 10%

IN

09658-003

Figure 3. Clock Enable I/O Timing Diagram

VIN

V

OUT

EXTCLK

VIN × 90%

t

t

3

t

2

t

1

t

5

6

Figu re 4. Logic E nable I/O Ti ming D iagram (Logic High Enable Feature Only Available on Certain Models)

V

OUT(NOM)

× 10%

t

7

V

× 10%

IN

09658-004

Rev. A | Page 4 of 20

ADP2126/ADP2127

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VIN to GND −0.3 V to +6 V

EXTCLK to GND −0.3 V to +6 V

SW, MODE to GND −0.3 V to VIN

FB to GND −0.3 V to +3.6 V

Operating Ambient Temperature (TA) –40°C to +85°C1

Operating Junction Temperature (TJ)

= 500 mA

at I

LOAD

–40°C to +125°C

Soldering Conditions JEDEC J-STD-020

1

The maximum operating junction temperature (T

maximum operating ambient temperature (T

Considerations section for more information.

) supersedes the

J (MAX)

). See the Thermal

A (MAX)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Absolute maximum ratings apply individually only, not in

combination.

THERMAL CONSIDERATIONS

The maximum operating junction temperature (T

supersedes the maximum operating ambient temperature

(T

) because the ADP2126/ADP2127 may be damaged

A (MAX)

when the junction temperature limits are exceeded. Monitoring

ambient temperature does not guarantee that T

specified temperature limits.

In applications with high power dissipation and poor PCB

thermal resistance, the maximum ambient temperature may

need to be derated. In applications with moderate power

dissipation and good PCB thermal resistance, the maximum

)

J (MAX)

is within the

J

ambient temperature can exceed the maximum limit as long as

the junction temperature is within specification limits.

The operating junction temperature (T

on the ambient temperature (T

device (P

the package (θ

), and the junction-to-ambient thermal resistance of

D

). TJ is calculated using the following formula:

JA

= TA + (PD × θJA) (1)

T

J

) of the device is dependent

J

), the power dissipation of the

A

See the Applications Information section for further information

on calculating the operating junction temperature for a specific

application.

THERMAL RESISTANCE

θJA of the package is based on modeling and calculation using a

4-layer board. θ

is highly dependent on the application and

JA

board layout. In applications where high maximum power

dissipation exists, attention to thermal board design is required.

The value of θ

may vary, depending on PCB material, layout,

JA

and environmental conditions.

θ

is specified for worst-case conditions, that is, a device soldered

JA

on a circuit board for surface-mount packages. θ

is determined

JA

according to JEDEC Standard JESD51-9 on a 4-layer printed

circuit board (PCB).

Table

3. Thermal Resistance (4-Layer PCB)

Package Type θJA Unit

6-Ball Bumped Bare Die Sales 105 °C/W

6-Pad Embedded Wafer Level Package 105 °C/W

ESD CAUTION

Rev. A | Page 5 of 20

ADP2126/ADP2127

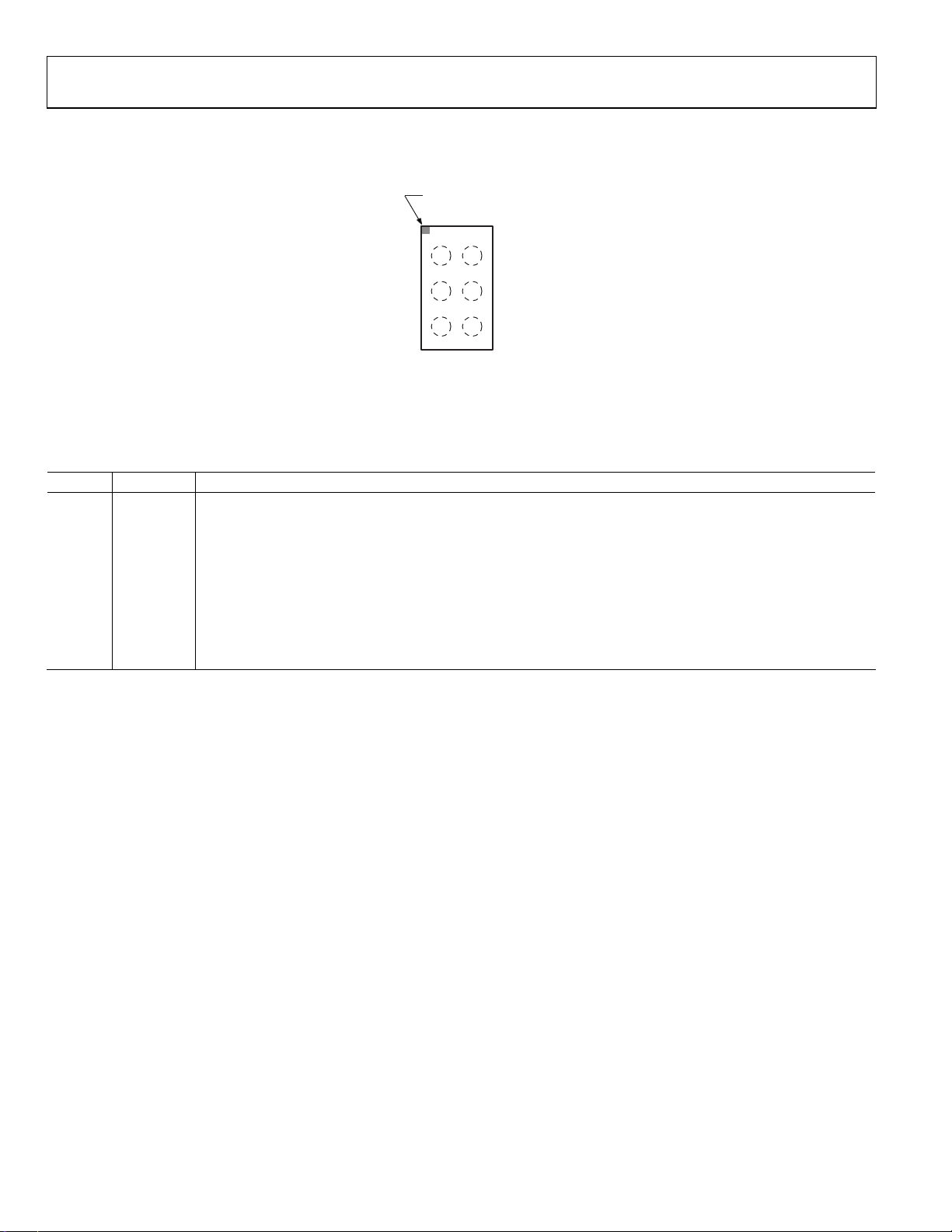

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

BALLA1

INDICATOR

2

1

MODE VIN

A

SW

EXTCLK

B

FB GND

C

TOP VIEW

BALL/PAD SIDE DOWN

4. Pin Function Descriptions

Table

Pin No. Mnemonic Description

A1 MODE

Mode Select. This pin toggles between auto mode (PFM and PWM switching) and PWM mode. Set MODE low to

allow the part to operate in auto mode. Pull MODE high to force the part to operate in PWM mode. The voltage

applied to MODE should never be higher than the voltage applied to VIN. Do not leave this pin floating.

A2 VIN Power Supply Input.

B1 SW Switch Node.

B2 EXTCLK

External Clock Enable Signal. The ADP2126/ADP2127 power up when a clock signal (6 MHz to 27 MHz) or a logic high

signal (EXTCLK ≥ 1.3 V) is detected on this pin. (The logic high enable feature is only available on certain models.)

C1 FB

Feedback Divider Input. Connect the output capacitor from FB to GND to set the output voltage ripple and to

complete the control loop.

C2 GND Ground.

BUMPS/PADS ON OPPOSITE SIDE

(Not to Scale)

Figure 5. Pin Configuration

09658-005

Rev. A | Page 6 of 20

Loading...

Loading...