2 A/1.25 A, 1.2 MHz, Synchronous,

V

FEATURES

Continuous output current

ADP2119: 2 A

ADP2120: 1.25 A

145 mΩ and 70 mΩ integrated MOSFETs

Input voltage range from 2.3 V to 5.5 V

Output voltage from 0.6 V to V

±1.5% output accuracy

1.2 MHz fixed switching frequency

Synchronizable between 1 MHz and 2 MHz

Selectable PWM or PFM mode operation

Current mode architecture

Precision threshold enable input

Power-good flag

Voltage tracking

Integrated soft start

Internal compensation

Startup with precharged output

UVLO, OVP, OCP, and thermal shutdown

10-lead, 3 mm × 3 mm LFCSP_WD package

APPLICATIONS

Point of load conversion

Communications and networking equipment

Industrial and instrumentation

Consumer electronics

Medical applications

GENERAL DESCRIPTION

The ADP2119/ADP2120 are low quiescent current, synchronous,

step-down dc-to-dc regulators in a compact 3 mm × 3 mm

LFCSP_WD package. Both devices use a current mode, constant

frequency pulse-width modulation (PWM) control scheme for

excellent stability and transient response. Under light load conditions,

they can be configured to operate in a pulse frequency modulation

(PFM) mode, which reduces switching frequency to save power.

The ADP2119/ADP2120 support input voltages from 2.3 V to

5.5 V. The output voltage can be adjusted from 0.6 V up to the

input voltage (V

output version is available in preset output voltage options of 3.3 V,

2.5 V, 1.8 V, 1.5 V, 1.2 V, and 1.0 V. The ADP2119/ADP2120 require

minimal external parts and provide a high efficiency solution with

their integrated power switches, synchronous rectifiers, and internal

compensation. Each IC draws less than 2 μA current from the input

source when it is disabled. Other key features include undervoltage

lockout (UVLO), integrated soft start to limit inrush current at

startup, overvoltage protection (OVP), overcurrent protection

(OCP), and thermal shutdown (TSD).

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

) for the adjustable version, whereas the fixed

IN

IN

Step-Down DC-to-DC Regulators

ADP2119/ADP2120

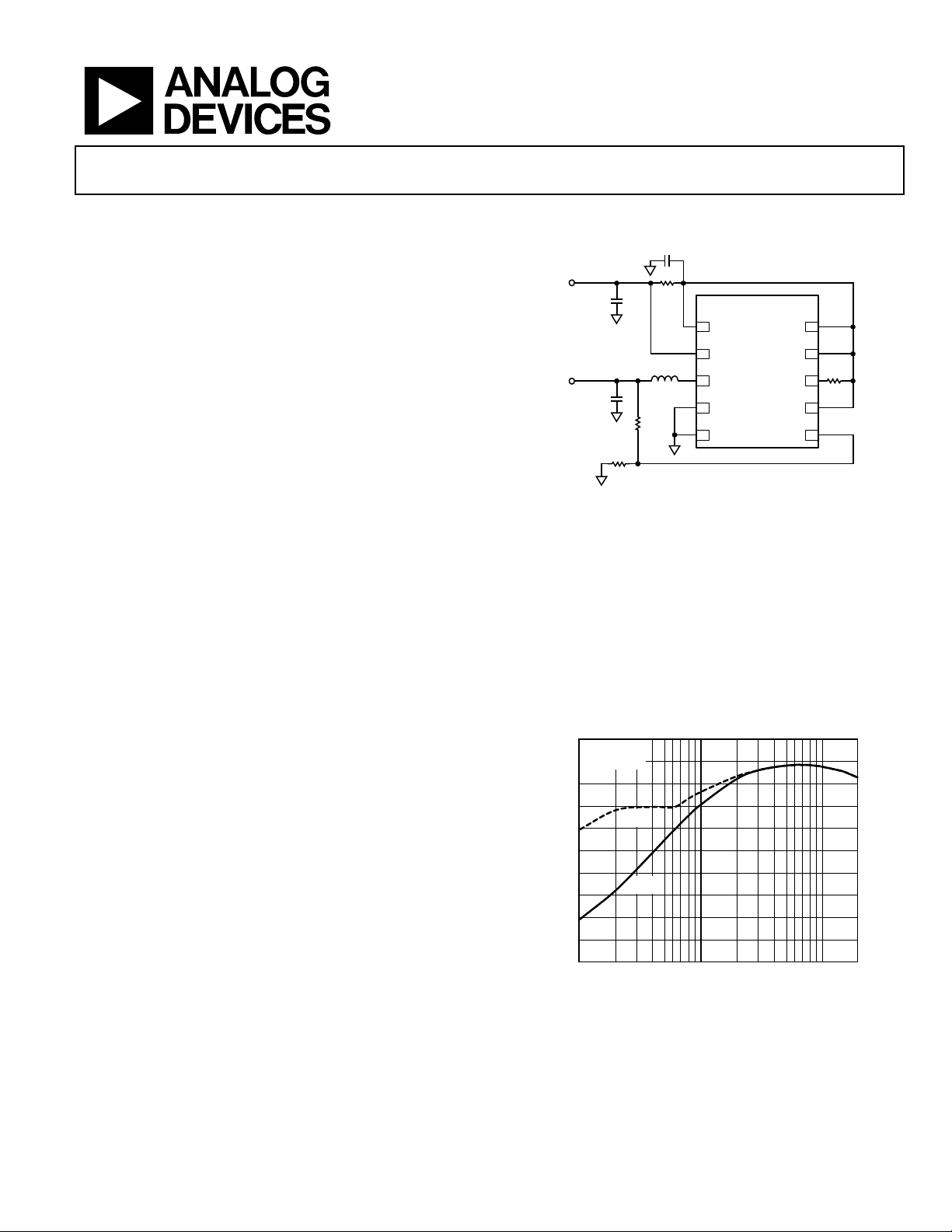

TYPICAL APPLICATION CIRCUIT

C1

0.1µF

V

IN

5V

C

IN

22µF

X5R

6.3V

OUT

3.3V

C

OUT

22µF

X5R

6.3V

R

BOT

2.21kΩ

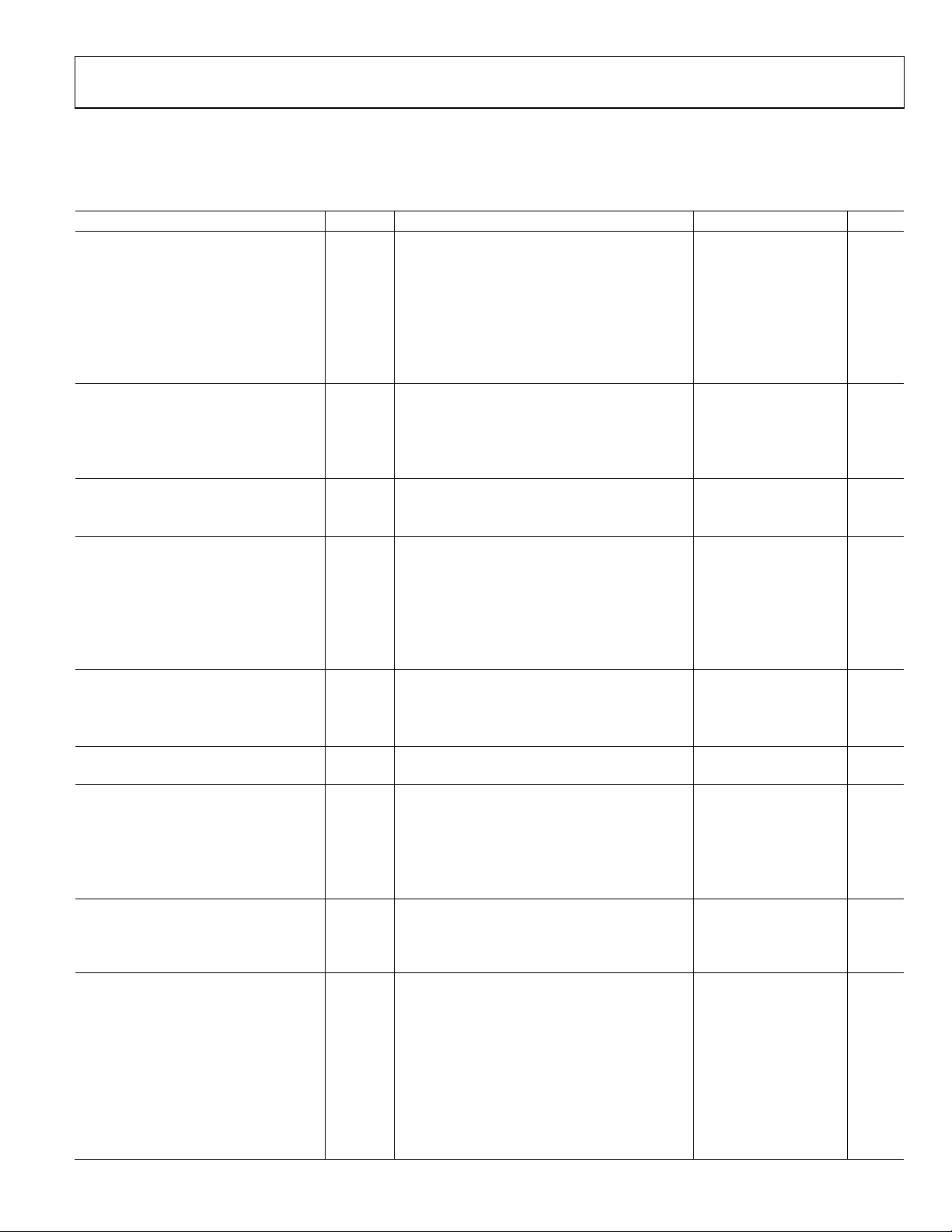

100

= 5V

V

IN

V

= 1.8V

OUT

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.01 0.1 1

Figure 2. ADP2119 Efficiency vs. Output Current

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

R1

10Ω

L

1.5µH

R

TOP

10kΩ

PFM

FPWM

OUTPUT CURRENT (A)

ADP2119/ADP2120

1

VIN

2

SYNC/MODE

PVIN

3

SW

4

PGND

5

GND

Figure 1.

EN

PGOOD

TRK

FB

10

9

R2

10kΩ

8

7

6

08716-001

08716-002

ADP2119/ADP2120

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Typical Application Circuit ............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 5

Thermal Resistance ...................................................................... 5

Boundary Condition .................................................................... 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

Typical Performance Characteristics ............................................. 7

Functional Block Diagram ............................................................ 15

Theory of Operation ...................................................................... 16

Control Scheme .......................................................................... 16

PWM Mode Operation .............................................................. 16

PFM Mode Operation ................................................................ 16

Slope Compensation .................................................................. 16

Enable/Shutdown ....................................................................... 16

Integrated Soft Start ................................................................... 16

Tracking ....................................................................................... 17

Oscillator and Synchronization ................................................ 17

Current Limit and Short-Circuit Protection .............................. 17

Overvoltage Protection (OVP) ................................................. 17

Undervoltage Lockout (UVLO) ............................................... 17

Thermal Shutdown .................................................................... 17

Power Good (PGOOD) ............................................................. 17

Applications Information .............................................................. 18

Output Voltage Selection ........................................................... 18

Inductor Selection ...................................................................... 18

Output Capacitor Selection ....................................................... 18

Input Capacitor Selection .......................................................... 19

Voltage Tracking ......................................................................... 19

Typical Application Circuits ......................................................... 20

Outline Dimensions ....................................................................... 22

Ordering Guide .......................................................................... 22

REVISION HISTORY

6/10—Revision 0: Initial Version

Rev. 0 | Page 2 of 24

ADP2119/ADP2120

SPECIFICATIONS

VIN = V

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

VIN and PVIN

VIN Voltage Range VIN 2.3 5.5 V

PVIN Voltage Range V

Quiescent Current I

Switching, no load, SYNC/MODE = VIN 680 900 μA

Shutdown Current I

VIN Undervoltage Lockout Threshold UVLO VIN rising 2.2 2.3 V

V

OUTPUT CHARACTERISTICS

Load Regulation1 ADP2119, IO = 0 A to 2 A 0.08 %/A

Load Regulation2 ADP2120, IO = 0 A to 1.25 A 0.08 %/A

Line Regulation1 ADP2119, IO = 1 A 0.05 %/V

Line Regulation2 ADP2120, IO = 1 A 0.05 %/V

FB

FB Regulation Voltage VFB V

FB Bias Current IFB V

SW

High-Side On Resistance3 V

Low-Side On Resistance3 V

SW Peak Current Limit High-side switch, VIN = V

High-side switch, VIN = V

SW Maximum Duty Cycle VIN = V

SW Minimum On Time4 V

TRK

TRK Input Voltage Range 0 600 mV

TRK-to-FB Offset Voltage TRK = 0 mV to 500 mV −15 +15 mV

TRK Input Bias Current 100 nA

FREQUENCY

Oscillator Frequency fS 1.02 1.2 1.38 MHz

SYNC/MODE

Synchronization Range 1 2 MHz

SYNC Minimum Pulse Width 100 ns

SYNC Minimum Off Time 100 ns

SYNC Input High Voltage 1.3 V

SYNC Input Low Voltage 0.4 V

INTEGRATED SOFT START

Soft Start Time All switching frequencies 1024

f

PGOOD

Power-Good Range FB rising threshold 105 110 115 %

FB rising hysteresis 2.5 %

FB falling threshold 85 90 95 %

FB falling hysteresis 2.5 %

Power-Good Deglitch Time From FB to PGOOD 16

PGOOD Leakage Current V

PGOOD Output Low Voltage I

PGOOD Output Low Resistor I

= 3.3 V, EN = VIN, SYNC/MODE = VIN at TJ = −40°C to +125°C, unless otherwise noted.

PVIN

2.3 5.5 V

PVIN

No switching, SYNC/MODE = GND 150 200 μA

VIN

V

SHDN

= V

= 5.5 V, EN = GND 0.3 2 μA

IN

PVIN

falling 2 2.1 V

IN

= 2.3 V to 5.5 V 0.591 0.6 0.609 V

IN

= 2.3 V to 5.5 V 0.01 0.1 μA

IN

= V

= 3.3 V, ISW = 200 mA 145 190 mΩ

IN

PVIN

= V

= 3.3 V, ISW = 200 mA 70 100 mΩ

IN

PVIN

= 3.3 V (ADP2119) 2.5 3 3.5 A

PVIN

= 3.3 V (ADP2120) 1.6 2 2.4 A

PVIN

= 5.5 V, full frequency 100 %

PVIN

= V

= 5.5 V, full frequency 100 ns

IN

PVIN

= 1.2 MHz 853 μs

S

= 5 V 0.1 1 μA

PGOOD

= 1 mA 150 200 mV

PGOOD

= 1 mA 150 200 Ω

PGOOD

Rev. 0 | Page 3 of 24

Clock

cycles

Clock

cycles

ADP2119/ADP2120

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

EN

EN Input Rising Threshold VIN = 2.3 V to 5.5 V 1.12 1.2 1.28 V

EN Input Hysteresis VIN = 2.3 V to 5.5 V 100 mV

EN Pull-Down Resistor 1 MΩ

THERMAL

Thermal Shutdown Threshold 150 °C

Thermal Shutdown Hysteresis 25 °C

1

Specified by the circuit in . Figure 54

2

Specified by the circuit in . Figure 58

3

Pin-to-pin measurements.

4

Guaranteed by design.

Rev. 0 | Page 4 of 24

ADP2119/ADP2120

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VIN, PVIN −0.3 V to +6 V

SW −0.3 V to +6 V

FB, SYNC/MODE, EN, TRK, PGOOD −0.3 V to +6 V

PGND to GND −0.3 V to +0.3 V

Operating Junction Temperature Range −40°C to +125°C

Storage Temperature Range −65°C to +150°C

Soldering Conditions JEDEC J-STD-020

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type θJA Unit

10-Lead LFCSP_WD 40 °C/W

BOUNDARY CONDITION

θJA is measured using natural convection on a JEDEC 4-layer

board, and the exposed pad is soldered to the printed circuit

board (PCB) with thermal vias.

ESD CAUTION

Rev. 0 | Page 5 of 24

ADP2119/ADP2120

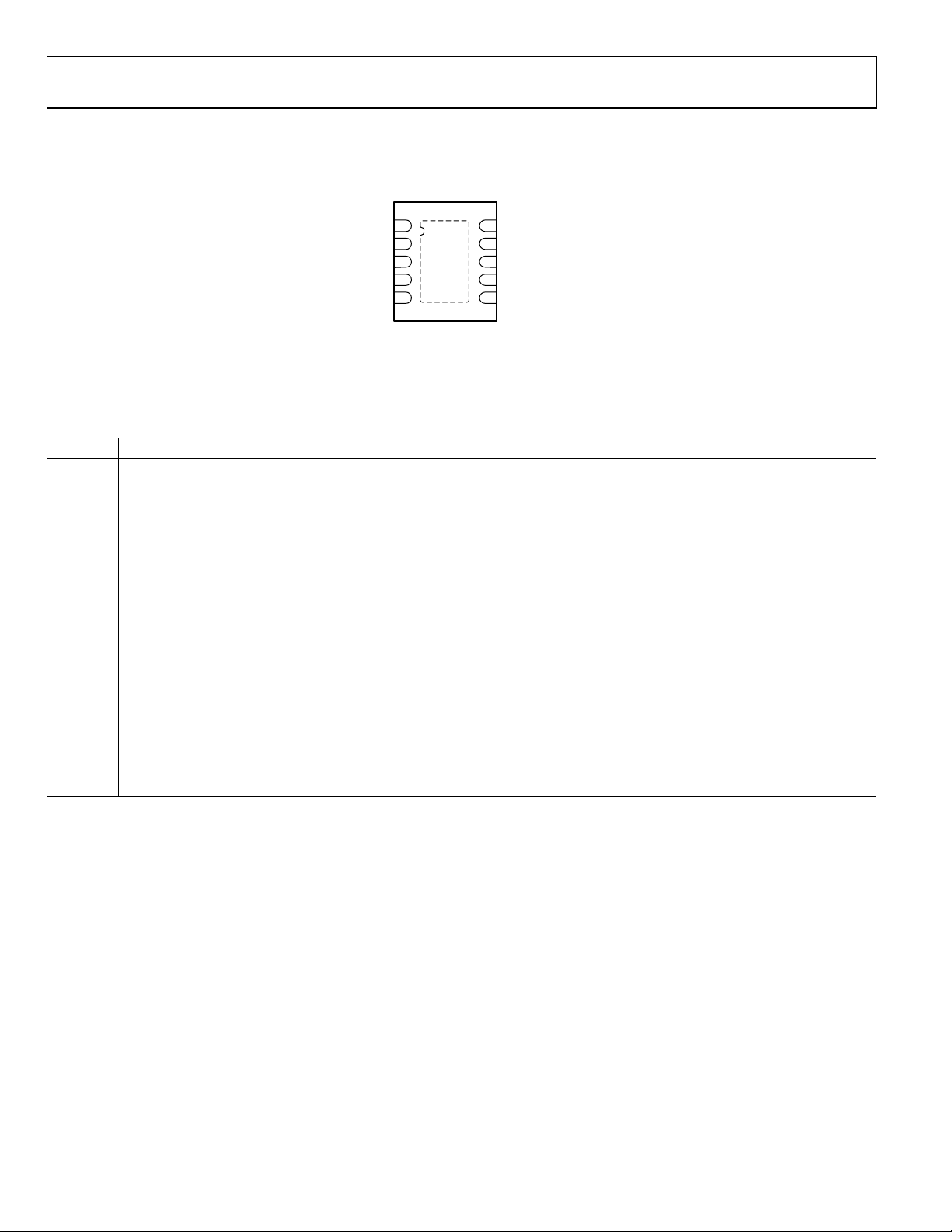

A

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

DP2119/ADP2120

1

VIN

2

PVIN

3

SW

PGND

GND

NOTES

1. THE EXPOSED PAD SHOULD BE SO LDERED TO

AN EXTERNAL GROUND PLANE UNDERNEAT H

THE IC FOR THERMAL DISSIPATION.

EXPOSED

4

PAD

5

10

EN

9

SYNC/MODE

8

PGOOD

7

TRK

6

FB

08716-003

Figure 3. Pin Configuration (Top View)

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 VIN

Bias Voltage Input Pin. Connect a bypass capacitor (0.1 μF minimum) between this pin and GND and a

small (10 Ω) resistor between this pin and PVIN.

2 PVIN Power Input Pin. Connect this pin to the input power source. Connect a bypass capacitor between this pin and PGND.

3 SW Switch Node Output. Connect this pin to the output inductor.

4 PGND Power Ground. Connect this pin to the power ground plane and to the high current return for the power MOSFET.

5 GND Analog Ground. Connect this pin to the ground plane.

6 FB

7 TRK

Feedback Voltage Sense Input. Connect this pin to a resistor divider from V

connect to V

directly.

OUT

Tracking Input. To track a master voltage, drive TRK from a resistor divider from the master voltage. If the

. For the fixed output version,

OUT

tracking function is not used, connect TRK to VIN.

8 PGOOD Power-Good Output (Open Drain). Connect this pin to a resistor to any pull-up voltage < 5.5 V.

9 SYNC/MODE

Synchronization Input (SYNC). Connect this pin to an external clock between 1 MHz and 2 MHz to synchronize

the switching frequency to the external clock (see the Oscillator and Synchronization section for details).

FPWM/PFM Selection (MODE). When this pin is connected to VIN, the PFM mode is disabled and the part works

in continuous conduction mode (CCM) only. When this pin is connected to ground, the PFM mode is enabled

and becomes active at light loads.

10 EN

Precision Threshold Enable Input Pin. An external resistor divider can be used to set the turn-on threshold. To

enable the part automatically, connect the EN pin to VIN. This pin has a 1 MΩ pull-down resistor to GND.

EPAD Exposed Pad The exposed pad should be soldered to an external ground plane underneath the IC for thermal dissipation.

Rev. 0 | Page 6 of 24

ADP2119/ADP2120

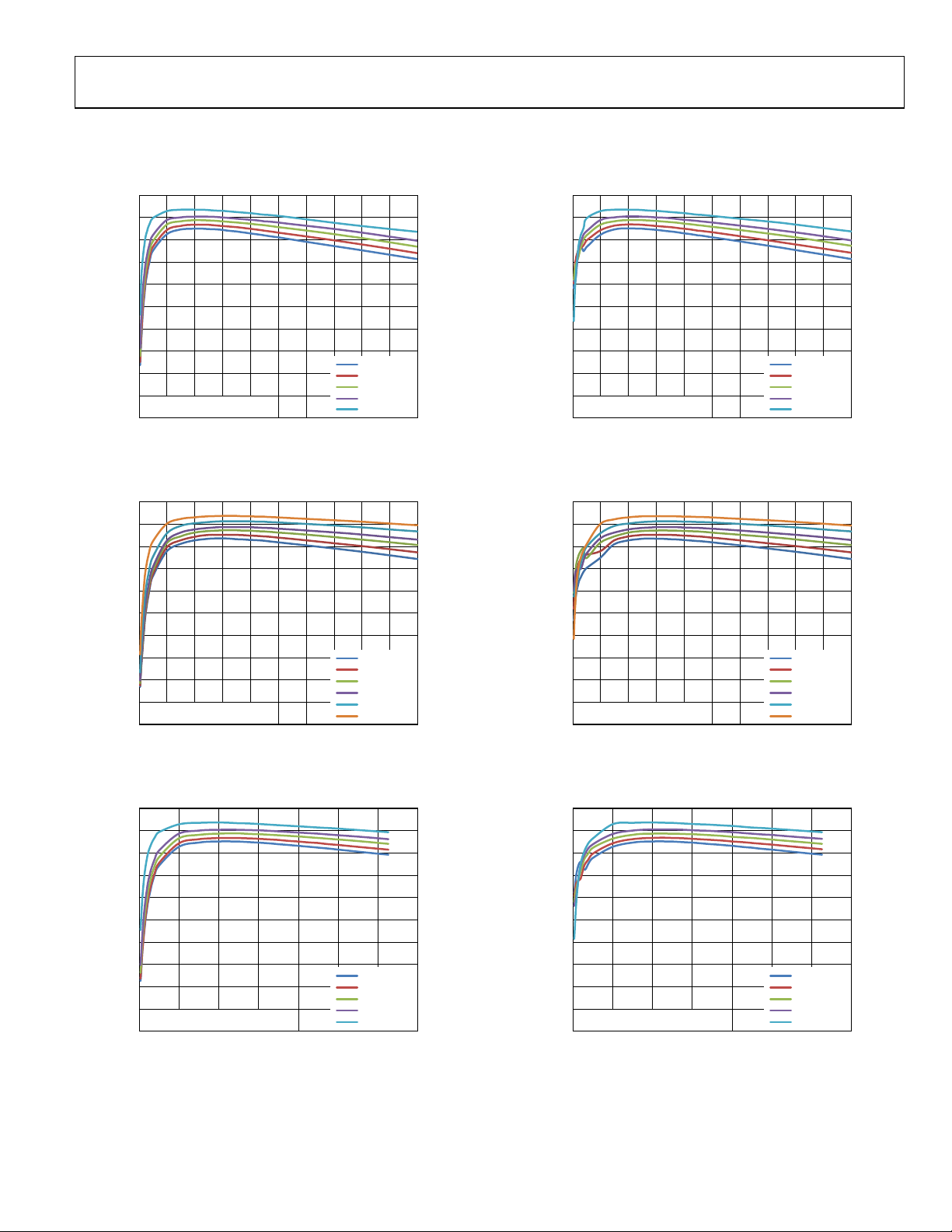

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, VIN = V

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

Figure 4. Efficiency (ADP2119, VIN = 3.3 V, FPWM) vs. Output Current

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

Figure 5. Efficiency (ADP2119, VIN = 5 V, FPWM) vs. Output Current

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

Figure 6. Efficiency (ADP2120, VIN = 3.3 V, FPWM) vs. Output Current

= 5 V, V

PVIN

OUTPUT CURRENT (A)

OUTPUT CURRENT (A)

OUTPUT CURRENT (A)

= 1.2 V, L = 1.5 μH, CIN = 22 μF, C

OUT

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

= 2 × 22 μF, unless otherwise noted.

OUT

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

08716-004

OUTPUT CURRENT (A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

08716-007

Figure 7. Efficiency (ADP2119, VIN = 3.3 V, PFM) vs. Output Current

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

08716-005

OUTPUT CURRENT (A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

08716-008

Figure 8. Efficiency (ADP2119, VIN = 5 V, PFM) vs. Output Current

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

08716-006

OUTPUT CURRENT (A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

08716-009

Figure 9. Efficiency (ADP2120, VIN = 3.3 V, PFM) vs. Output Current

Rev. 0 | Page 7 of 24

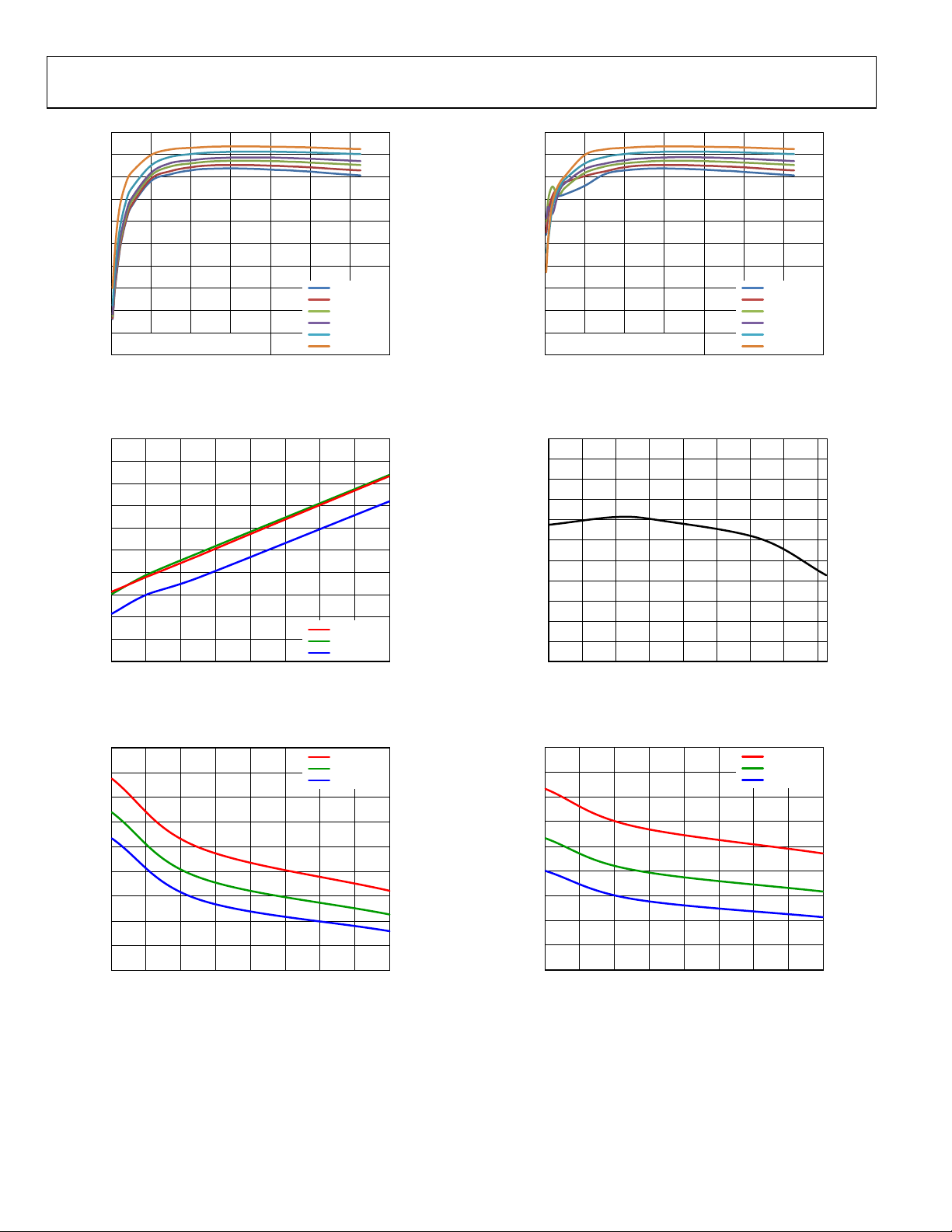

ADP2119/ADP2120

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

OUTPUT CURRENT (A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

Figure 10. Efficiency (ADP2120, VIN = 5 V, FPWM) vs. Output Current

900

850

800

750

700

650

600

550

QUIESCENT CURRENT (µ A)

500

450

400

2.3 5.55.14.74.33.93.53.12.7

VIN (V)

TJ = +125°C

TJ = +25°C

TJ = –40°C

Figure 11. Quiescent Current vs. VIN (Switching)

275

250

225

200

175

150

125

PFET RESISTO R ( mΩ)

100

75

50

2.3 5.55.14.74.33.93.53.12.7

VIN (V)

TJ = +125°C

TJ = +25°C

TJ = –40°C

Figure 12. PFET Resistor vs. VIN (Pin-to-Pin Measurements)

08716-010

08716-011

08716-012

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR SUMIDA

CDRH5D18BHPNP-1R5M

0

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

OUTPUT CURRENT (A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

Figure 13. Efficiency (ADP2120, VIN = 5 V, PFM) vs. Output Current

605

604

603

602

601

600

599

598

597

FEEDBACK VOLTAGE (mV)

596

595

594

–40 120100806040200–20

TEMPERATURE (°C)

Figure 14. Feedback Voltage vs. Temperature (VIN = 3.3 V)

120

110

100

90

80

70

60

NFET RESIS TOR (mΩ)

50

40

30

2.3 5.55.14.74.33.93.53.12.7

VIN (V)

TJ = +125°C

TJ = +25°C

TJ = –40°C

Figure 15. NFET Resistor vs. VIN (Pin-to-Pin Measurements)

08716-013

08716-014

08716-015

Rev. 0 | Page 8 of 24

Loading...

Loading...