ANALOG DEVICES ADP1871 Service Manual

Synchronous Buck Controller with

V

V

V

Constant On-Time and Valley Current Mode

FEATURES

Power input voltage range: 2.95 V to 20 V

On-board bias regulator

Minimum output voltage: 0.6 V

0.6 V reference voltage with ±1.0% accuracy

Supports all N-channel MOSFET power stages

Available in 300 kHz, 600 kHz, and 1.0 MHz options

No current-sense resistor required

Power saving mode (PSM) for light loads (ADP1871 only)

Resistor-programmable current-sense gain

Thermal overload protection

Short-circuit protection

Precision enable input

Integrated bootstrap diode for high-side drive

Starts into a precharged load

Small, 10-lead MSOP and LFCSP packages

APPLICATIONS

Telecom and networking systems

Mid to high end servers

Set-top boxes

DSP core power supplies

12 V input POL supplies

GENERAL DESCRIPTION

The ADP1870/ADP1871 are versatile current-mode, synchronous

step-down controllers that provide superior transient response,

optimal stability, and current-limit protection by using a constant

on-time, pseudo-fixed frequency with a programmable currentlimit, current-control scheme. In addition, these devices offer

optimum performance at low duty cycles by utilizing valley

current-mode control architecture. This allows the ADP1870/

ADP1871 to drive all N-channel power stages to regulate output

voltages as low as 0.6 V.

The ADP1871 is the power saving mode (PSM) version of the

device and is capable of pulse skipping to maintain output

regulation while achieving improved system efficiency at light

loads (see the Power Saving Mode (PSM) Version (ADP1871)

section for more information).

Available in three frequency options (300 kHz, 600 kHz, and

1.0 MHz, plus the PSM option), the ADP1870/ADP1871 are well

suited for a wide range of applications that require a single-input

power supply range from 2.95 V to 20 V. Low voltage biasing is

supplied via a 5 V internal LDO.

ADP1870/ADP1871

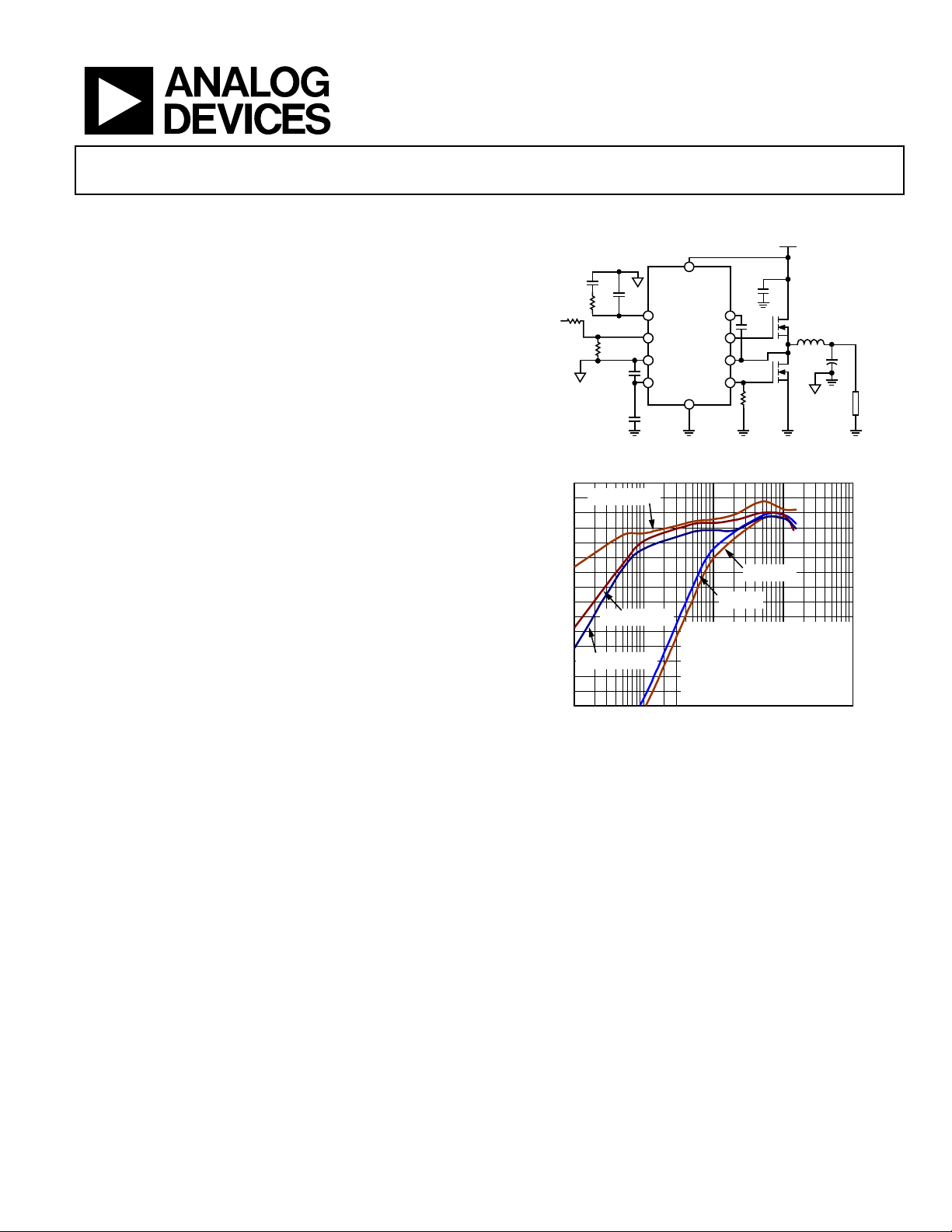

TYPICAL APPLICATIONS CIRCUIT

= 2.95V TO 2 0

IN

C

C

C

C2

R

C

R

TOP

OUT

R

BOT

C

VREG2

C

VREG

100

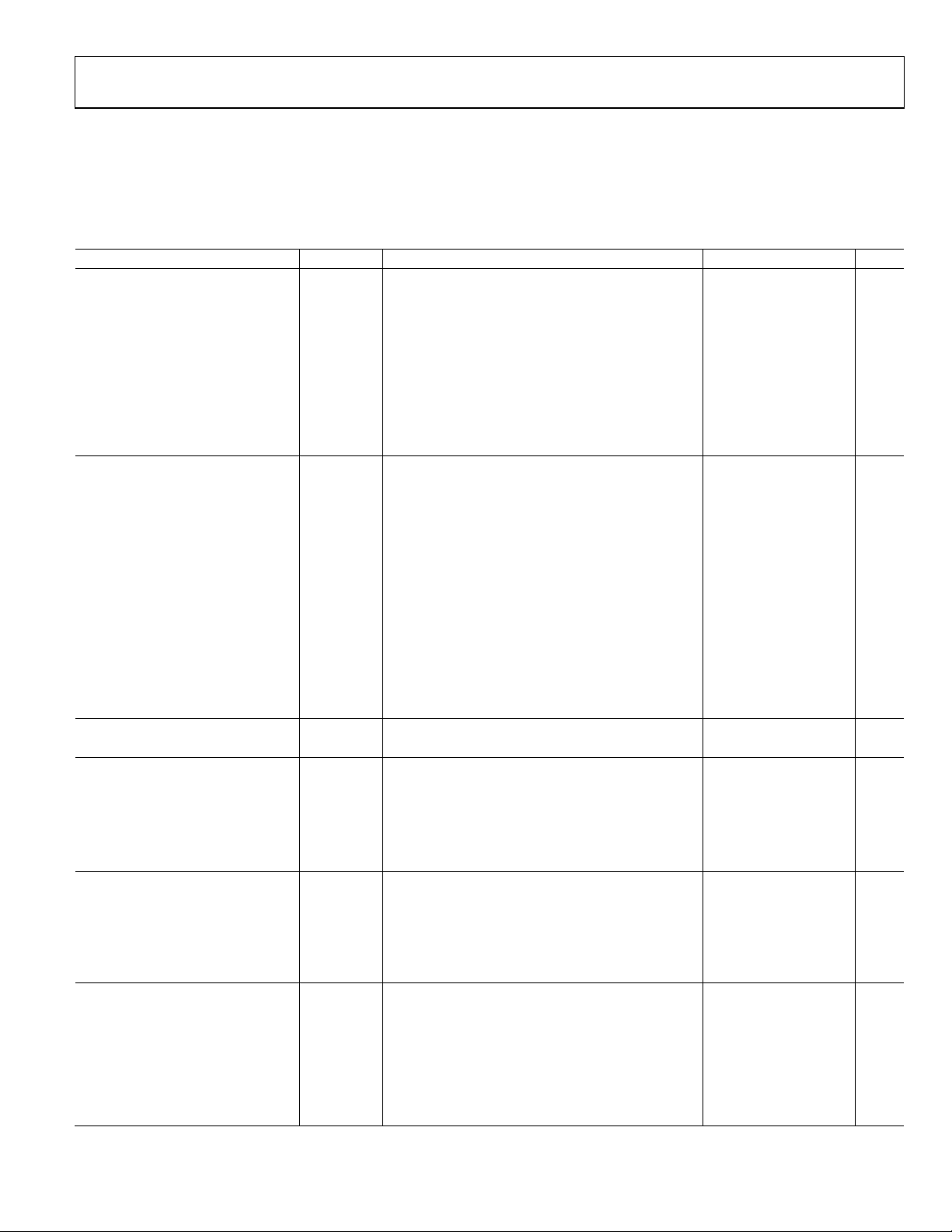

VIN = 5V (PSM)

95

90

85

80

75

70

65

60

VIN = 13V (PSM)

55

EFFICIENCY (%)

50

45

VIN = 16.5V (PS M )

40

35

30

25

10 100 1k 10k 100k

Figure 2. Efficiency vs. Load Current (V

In addition, an internally fixed soft start period is included to limit

input in-rush current from the input supply during startup and

to provide reverse current protection during soft start for a precharged output. The low-side current-sense, current-gain scheme

and integration of a boost diode, along with the PSM/forced pulsewidth modulation (PWM) option, reduce the external part count

and improve efficiency.

The ADP1870/ADP1871 operate over the −40°C to +125°C

junction temperature range and are available in a 10-lead MSOP

and LFCSP packages.

VIN

ADP1870/

ADP1871

COMP/EN BST

FB DRVH

GND SW

VREG DRVL

PGND

C

BST

R

RES

Figure 1.

VIN = 16.5V

VIN = 13V

TA = 25°C

V

= 1.8V

OUT

f

= 300kHz

SW

WÜRTH INDUCTOR:

744325120, L = 1. 2µH, DCR = 1.8m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 1.8 V, 300 kHz)

OUT

C

IN

Q1

L

V

OUT

C

OUT

Q2

LOAD

08730-001

08730-102

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

ADP1870/ADP1871

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Typical Applications Circuit ............................................................ 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 5

Thermal Resistance ...................................................................... 5

Boundary Condition .................................................................... 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

Typical Performance Characteristics ............................................. 7

ADP1870/ADP1871 Block Diagram ............................................ 18

Theory of Operation ...................................................................... 19

Startup .......................................................................................... 19

Soft Start ...................................................................................... 19

Precision Enable Circuitry ........................................................ 19

Undervoltage Lockout ............................................................... 19

On-Board Low Dropout Regulator .......................................... 19

Thermal Shutdown ..................................................................... 20

Programming Resistor (RES) Detect Circuit .......................... 20

Valley Current-Limit Setting .................................................... 20

Hiccup Mode During Short Circuit ......................................... 21

Synchronous Rectifier ................................................................ 22

Power Saving Mode (PSM) Version (ADP1871) ................... 22

Timer Operation ........................................................................ 22

Pseudo-Fixed Frequency ........................................................... 23

Applications Information .............................................................. 24

Feedback Resistor Divider ........................................................ 24

Inductor Selection ...................................................................... 24

Output Ripple Voltage (VRR) .................................................. 24

Output Capacitor Selection ....................................................... 24

Compensation Network ............................................................ 25

Efficiency Considerations ......................................................... 26

Input Capacitor Selection .......................................................... 27

Thermal Considerations ............................................................ 28

Design Example .......................................................................... 29

External Component Recommendations .................................... 31

Layout Considerations ................................................................... 33

IC Section (Left Side of Evaluation Board) ............................. 37

Power Section ............................................................................. 37

Differential Sensing .................................................................... 38

Typical Applications Circuits ........................................................ 39

15 A, 300 kHz High Current Application Circuit .................. 39

5.5 V Input, 600 kHz Application Circuit ............................... 39

300 kHz High Current Application Circuit ............................ 40

Outline Dimensions ....................................................................... 41

Ordering Guide .......................................................................... 42

REVISION HISTORY

6/10—Rev. 0 to Rev. A

Added LFCSP Package ....................................................... Universal

Changes to Applications Section .................................................... 1

Changes to Internal Regulator Characteristics Parameter,

Table 1 ............................................................................................ 3

Changes to Table 2 and Table 3 ....................................................... 5

Changes to Figure 3 and Table 4 ..................................................... 6

Change to Figure 22 ....................................................................... 10

Changes to Figure 65 ...................................................................... 18

Changes to Efficiency Considerations Section ........................... 26

Changes to Table 9 ................................................................................... 28

Added Figure 84; Renumbered Sequentially ...................................... 28

Added Figure 96 ....................................................................................... 41

Changes to Ordering Guide ................................................................... 42

3/10—Revision 0: Initial Version

Rev. A | Page 2 of 44

ADP1870/ADP1871

SPECIFICATIONS

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC). V

− VSW = V

V

BST

REG

− V

RECT_DROP

(see Figure 40 to Figure 42). VIN = 12 V. The specifications are valid for TJ = −40°C to +125°C,

unless otherwise specified.

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

POWER SUPPLY CHARACTERISTICS

High Input Voltage Range VIN C

= 22 µF to PGND (at Pin 1)

IN

ADP1870ARMZ-0.3/ADP1871ARMZ-0.3 (300 kHz) 2.95 12 20 V

ADP1870ARMZ-0.6/ADP1871ARMZ-0.6 (600 kHz) 2.95 12 20 V

ADP1870ARMZ-1.0/ADP1871ARMZ-1.0 (1.0 MHz) 3.25 12 20 V

Quiescent Current I

Shutdown Current

Q_REG

I

REG,SD

I

BST,SD

+ I

VFB = 1.5 V, no switching 1.1 mA

Q_BST

+

COMP/EN < 285 mV 190 280 A

Undervoltage Lockout UVLO Rising VIN (see Figure 35 for temperature variation) 2.65 V

UVLO Hysteresis Falling VIN from operational state 190 mV

INTERNAL REGULATOR

CHARACTERISTICS

VREG Operational Output Voltage V

VREG should not be loaded externally because it is

intended to only bias internal circuitry.

C

REG

VREG

= 1 µF to PGND, 0.22 µF to GND, VIN = 2.95 V to 20 V

ADP1870ARMZ-0.3/ADP1871ARMZ-0.3 (300 kHz) 2.75 5 5.5 V

ADP1870ARMZ-0.6/ADP1871ARMZ-0.6 (600 kHz) 2.75 5 5.5 V

ADP1870ARMZ-1.0/ADP1871ARMZ-1.0 (1.0 MHz) 3.05 5 5.5 V

VREG Output in Regulation VIN = 7 V, 100 mA 4.8 4.981 5.16 V

V

= 12 V, 100 mA 4.8 4.982 5.16 V

IN

Load Regulation 0 mA to 100 mA, VIN = 7 V 32 mV

0 mA to 100 mA, VIN = 20 V 33 mV

Line Regulation VIN = 7 V to 20 V, 20 mA 2.5 mV

V

VIN to V

Dropout Voltage 100 mA out of V

REG

= 7 V to 20 V, 100 mA 2.0 mV

IN

, VIN ≤ 5 V 300 415 mV

REG

Short VREG to PGND VIN = 20 V 229 320 mA

SOFT START

Soft Start Period See Figure 58 3.0 ms

ERROR AMPLIFER

FB Regulation Voltage VFB T

T

T

= +25°C 600 mV

J

= −40°C to +85°C 596 600 604 mV

J

= −40°C to +125°C 594.2 600 605.8 mV

J

Transconductance Gm 320 496 670 µS

FB Input Leakage Current I

V

FB, Leak

= 0.6 V, COMP/EN = released 1 50 nA

FB

CURRENT-SENSE AMPLIFIER GAIN

Programming Resistor (RES)

RES = 47 kΩ ± 1% 2.7 3 3.3 V/V

Value from DRVL to PGND

RES = 22 kΩ ± 1% 5.5 6 6.5 V/V

RES = none 11 12 13 V/V

RES = 100 kΩ ± 1% 22 24 26 V/V

SWITCHING FREQUENCY

ADP1870ARMZ-0.3/

Typical values measured at 50% time points with 0 nF

at DRVH and DRVL; maximum values are guaranteed

by bench evaluation

1

300 kHz

ADP1871ARMZ-0.3 (300 kHz)

On-Time VIN = 5 V, V

= 2 V, TJ = 25°C 1120 1200 1280 ns

OUT

Minimum On-Time VIN = 20 V 146 190 ns

Minimum Off-Time 84% duty cycle (maximum) 340 400 ns

REG

= 5 V,

Rev. A | Page 3 of 44

ADP1870/ADP1871

Parameter Symbol Conditions Min Typ Max Unit

ADP1870ARMZ-0.6/

ADP1871ARMZ-0.6 (600 kHz)

On-Time VIN = 5 V, V

Minimum On-Time VIN = 20 V, V

Minimum Off-Time 65% duty cycle (maximum) 340 400 ns

ADP1870ARMZ-1.0/

ADP1871ARMZ-1.0 (1.0 MHz)

On-Time VIN = 5 V, V

Minimum On-Time VIN = 20 V 60 85 ns

Minimum Off-Time 45% duty cycle (maximum) 340 400 ns

OUTPUT DRIVER CHARACTERISTICS

High-Side Driver

Output Source Resistance I

Output Sink Resistance I

Rise Time2 t

Fall Time2 t

Low-Side Driver

Output Source Resistance I

Output Sink Resistance I

Rise Time2 t

Fall Time2 t

Propagation Delays

DRVL Fall to DRVH Rise2 t

DRVH Fall to DRVL Rise2 t

SW Leakage Current I

Integrated Rectifier

Channel Impedance I

PRECISION ENABLE THRESHOLD

Logic High Level VIN = 2.9 V to 20 V, V

Enable Hysteresis VIN = 2.9 V to 20 V, V

COMP VOLTAGE

COMP Clamp Low Voltage V

COMP Clamp High Voltage V

COMP Zero Current Threshold V

THERMAL SHUTDOWN T

Thermal Shutdown Threshold Rising temperature 155 °C

Thermal Shutdown Hysteresis 15 °C

Hiccup Current Limit Timing 6 ms

1

The maximum specified values are with the closed loop measured at 10% to 90% time points (see Figure and Figure 61), C

MOSFETs being Infineon BSC042N03MSG.

2

Not automatic test equipment (ATE) tested.

600 kHz

= 2 V, TJ = 25°C 500 540 580 ns

OUT

= 0.8 V 82 110 ns

OUT

1.0 MHz

= 2 V, TJ = 25°C 285 312 340 ns

OUT

= 1.5 A, 100 ns, positive pulse (0 V to 5 V) 2.25 3 Ω

SOURCE

= 1.5 A, 100 ns, negative pulse (5 V to 0 V) 0.7 1 Ω

SINK

V

r,DR VH

V

f,DRV H

V

r,DR VL

V

f,DRV L

V

tpdhDRVH

V

tpdhDRVL

V

SWLEAK

COMP(l ow)

(2.75 V ≤ V

COMP(h igh)

(2.75 V ≤ V

COMP_ZC T

TMSD

− VSW = 4.4 V, CIN = 4.3 nF (see Figure 60) 25 ns

BST

− VSW = 4.4 V, CIN = 4.3 nF (see Figure 61) 11 ns

BST

= 1.5 A, 100 ns, positive pulse (0 V to 5 V) 1.6 2.2 Ω

SOURCE

= 1.5 A, 100 ns, negative pulse (5 V to 0 V) 0.7 1 Ω

SINK

= 5.0 V, CIN = 4.3 nF (see Figure 61) 18 ns

REG

= 5.0 V, CIN = 4.3 nF (see Figure 60) 16 ns

REG

− VSW = 4.4 V (see Figure 60) 15.4 ns

BST

− VSW = 4.4 V (see Figure 61) 18 ns

BST

= 25 V, VSW = 20 V, V

BST

= 10 mA 22 Ω

SINK

From disabled state, release COMP/EN pin to enable

device (2.75 V ≤ V

REG

≤ 5.5 V) 2.55 V

REG

≤ 5.5 V) 1.07 V

REG

= 5 V 110 µA

REG

= 2.75 V to 5.5 V 245 285 330 mV

REG

= 2.75 V to 5.5 V 37 mV

REG

0.47 V

≤ 5.5 V)

60

= 4.3 nF, and the upper- and lower-side

GATE

Rev. A | Page 4 of 44

ADP1870/ADP1871

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VREG to PGND, GND −0.3 V to +6 V

VIN to PGND −0.3 V to +28 V

FB, COMP/EN to GND −0.3 V to (V

DRVL to PGND −0.3 V to (V

SW to PGND −2.0 V to +28 V

BST to SW −0.6 V to (V

BST to PGND −0.3 V to 28 V

DRVH to SW −0.3 V to V

PGND to GND

θJA (10-Lead MSOP)

2-Layer Board 213.1°C/W

4-Layer Board 171.7°C/W

θJA (10-Lead LFCSP)

4-Layer Board 40°C/W

Operating Junction Temperature

Range

Storage Temperature Range −65°C to +150°C

Soldering Conditions JEDEC J-STD-020

Maximum Soldering Lead

Temperature (10 sec)

±0.3 V

−40°C to +125°C

300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Absolute maximum ratings apply individually only, not in

combination. Unless otherwise specified, all other voltages are

referenced to PGND.

REG

REG

REG

REG

+ 0.3 V)

+ 0.3 V)

+ 0.3 V)

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type θ

θJA (10-Lead MSOP)

2-Layer Board 213.1 °C/W

4- Layer Board 171.7 °C/W

θJA (10-Lead LFCSP)

4- Layer Board 40 °C/W

1

θJA is specified for the worst-case conditions; that is, θJA is specified for the

device soldered in a circuit board for surface-mount packages.

1

Unit

JA

BOUNDARY CONDITION

In determining the values given in Ta b l e 2 and Ta ble 3 , natural

convection was used to transfer heat to a 4-layer evaluation board.

ESD CAUTION

Rev. A | Page 5 of 44

ADP1870/ADP1871

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VIN

1

GND

FB

ADP1870/

2

ADP1871

3

TOP VIEW

4

(Not to Scale)

5

COMP/EN

VREG

NOTES

1. THE EXPOSED PAD MUST BE CONNECTED

TO GROUND.

Figure 3. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 VIN High Input Voltage. Connect VIN to the drain of the upper-side MOSFET.

2 COMP/EN Output of the Internal Error Amplifier/IC Enable. When this pin functions as EN, applying 0 V to this pin disables the IC.

3 FB Noninverting Input of the Internal Error Amplifier. This is the node where the feedback resistor is connected.

4 GND

Analog Ground Reference Pin of the IC. All sensitive analog components should be connected to this ground

plane (see the Layout Considerations section).

5 VREG

Internal Regulator Supply Bias Voltage for the ADP1870/ADP1871 Controller (Includes the Output Gate Drivers).

A bypass capacitor of 1 µF directly from this pin to PGND and a 0.1 µF across VREG and GND are recommended.

VREG should not be loaded externally because it is intended to only bias internal circuitry.

6 DRVL

Drive Output for the External Lower-Side, N-Channel MOSFET. This pin also serves as the current-sense gain

setting pin (see Figure 69).

7 PGND Power GND. Ground for the lower-side gate driver and lower-side, N-channel MOSFET.

8 DRVH Drive Output for the External Upper-Side, N-Channel MOSFET.

9 SW Switch Node Connection.

10 BST

Bootstrap for the Upper-Side MOSFET Gate Drive Circuitry. An internal boot rectifier (diode) is connected

between VREG and BST. A capacitor from BST to SW is required. An external Schottky diode can also be

connected between VREG and BST for increased gate drive capability.

10

9

8

7

6

BST

SW

DRVH

PGND

DRVL

08730-003

Rev. A | Page 6 of 44

ADP1870/ADP1871

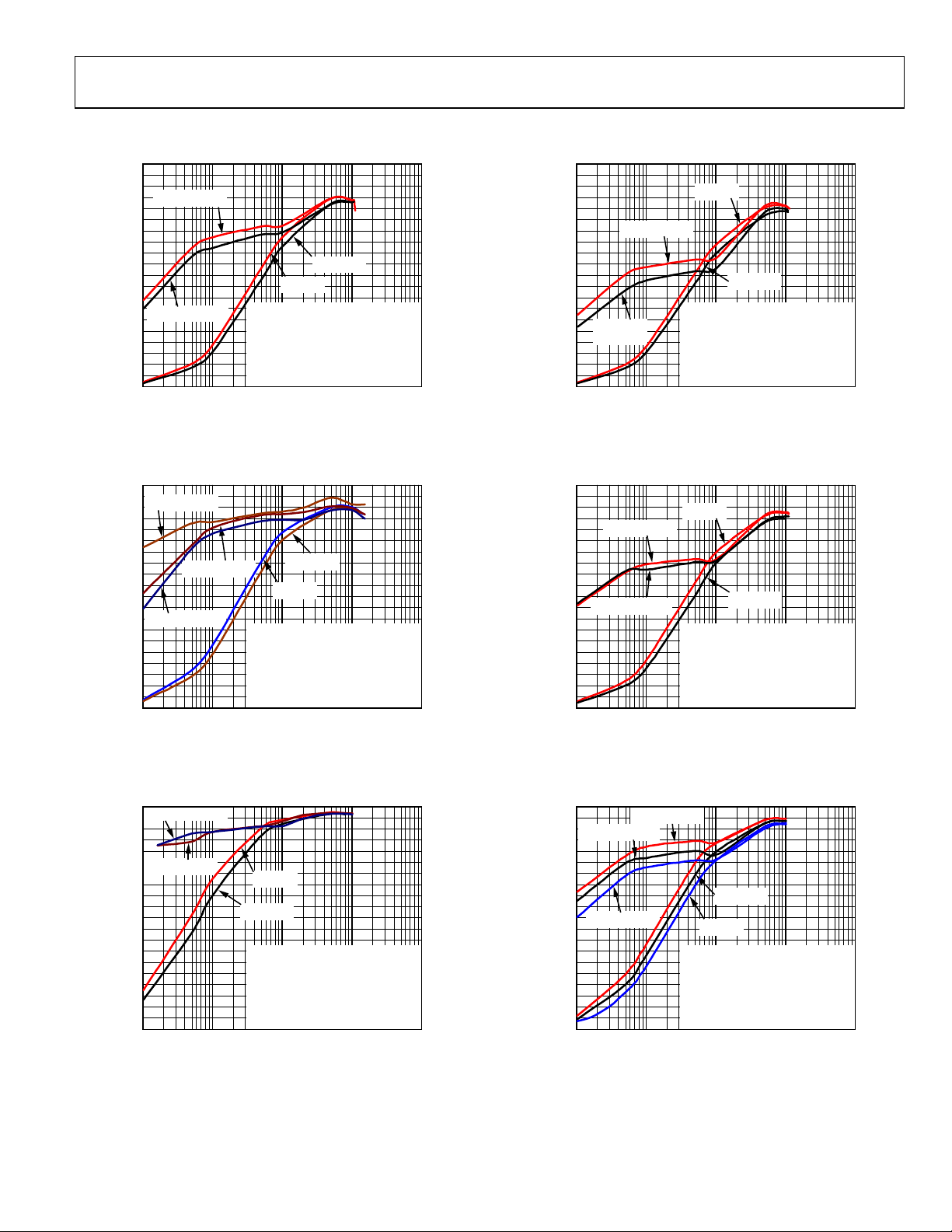

TYPICAL PERFORMANCE CHARACTERISTICS

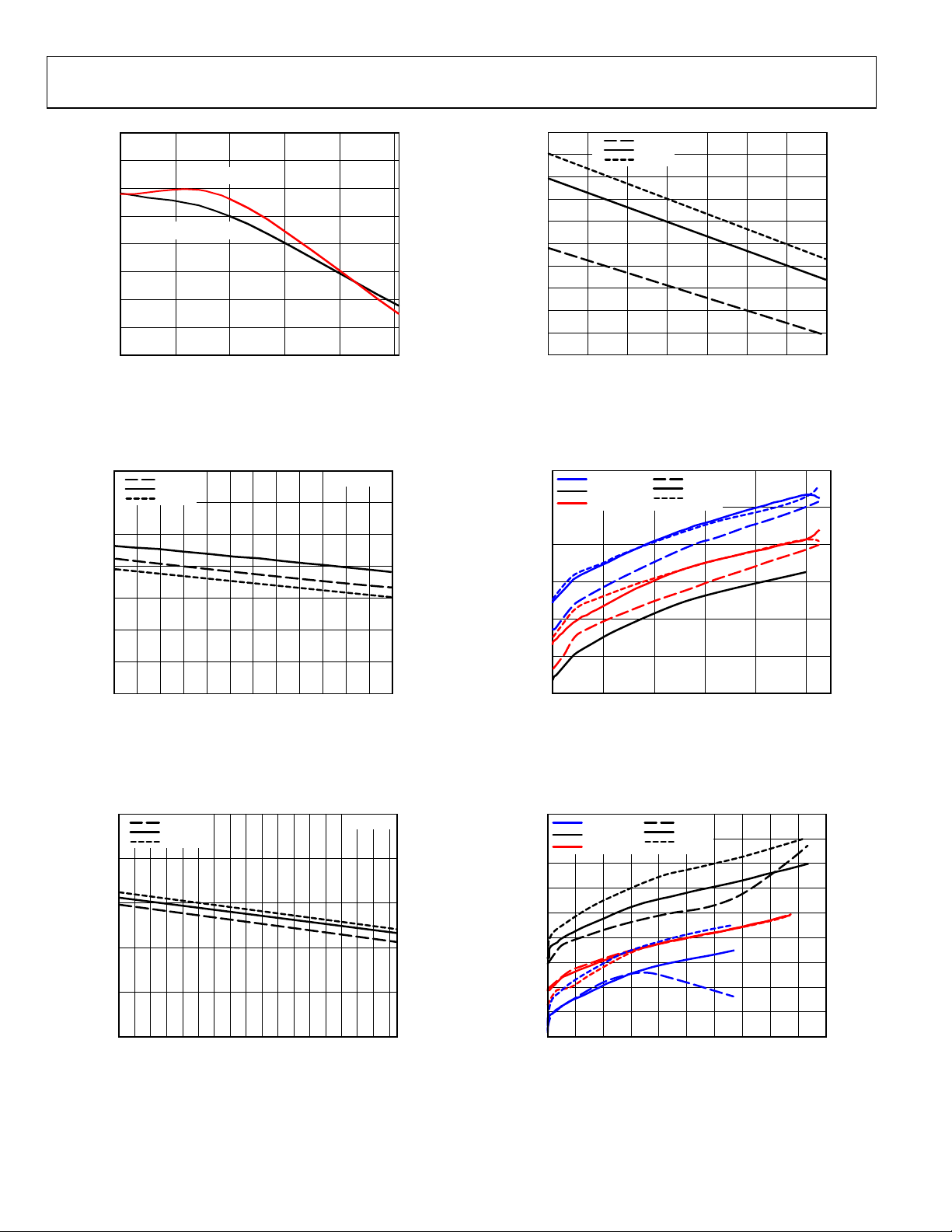

100

95

90

VIN = 13V (PSM)

85

80

75

70

65

60

55

50

45

40

EFFICIENCY (%)

35

VIN = 16.5V (PS M )

30

25

20

15

10

5

0

10 100 1k 10k 100k

TA = 25°C

V

OUT

f

= 300kHz

SW

WÜRTH INDUCTOR:

744325072, L = 0. 72µH, DCR = 1.3m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

Figure 4. Efficiency—300 kHz, V

VIN = 13V

= 0.8V

VIN = 16.5V

= 0.8 V

OUT

08730-104

100

95

90

85

80

75

70

65

60

55

50

45

40

EFFICIENCY (%)

35

30

25

20

15

10

5

0

10 100 1k 10k 100k

VIN = 13V (PSM)

VIN = 16.5V

(PSM)

Figure 7. Efficiency—600 kHz, V

VIN = 13V

VIN = 16.5V

TA = 25°C

= 0.8V

V

OUT

f

= 600kHz

SW

WÜRTH INDUCTOR:

744355147, L = 0. 47µH, DCR = 0.67m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 0.8 V

OUT

08730-107

100

95

VIN = 5V (PSM)

90

85

80

75

70

65

60

55

50

45

40

EFFICIENCY (%)

35

30

25

20

15

10

5

0

VIN = 13V (PSM)

VIN = 16.5V (PS M )

10 100 1k 10k 100k

LOAD CURRENT (mA)

Figure 5. Efficiency—300 kHz, V

100

VIN = 16.5V (PS M )

95

90

85

80

75

VIN = 13V (PSM)

70

65

60

55

50

45

40

EFFICIENCY (%)

35

30

25

20

15

10

5

0

10 100 1k 10k 100k

LOAD CURRENT (mA)

Figure 6. Efficiency—300 kHz, V

VIN = 16.5V

VIN = 13V

TA = 25°C

= 1.8V

V

OUT

f

= 300kHz

SW

WÜRTH INDUCTOR:

744325120, L = 1. 2µH, DCR = 1.8m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

= 1.8 V

OUT

VIN = 13V

VIN = 16.5V

TA = 25°C

= 7V

V

OUT

f

= 300kHz

SW

WÜRTH INDUCTOR:

7443551200, L = 2.0µH, DCR = 2.6m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

= 7 V

OUT

100

95

90

85

VIN = 13V (PSM)

80

75

70

65

60

55

50

VIN = 16.5V (PSM)

45

40

EFFICIENCY (%)

35

30

25

20

15

10

5

0

10 100 1k 10k 100k

08730-105

Figure 8. Efficiency—600 kHz, V

100

95

90

VIN = 16.5V (PS M )

85

80

75

70

65

60

55

50

45

40

EFFICIENCY (%)

35

30

25

20

15

10

5

0

10 100 1k 10k 100k

08730-106

VIN = 13V (PSM)

VIN = 20V (PSM)

Figure 9. Efficiency—600 kHz, V

VIN = 13V

VIN = 16.5V

TA = 25°C

= 1.8V

V

OUT

f

= 600kHz

SW

WÜRTH INDUCTOR:

744325072, L = 0. 72µH, DCR = 1.3m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 1.8 V

OUT

VIN = 16.5V

VIN = 20V

TA = 25°C

= 5V

V

OUT

f

= 600kHz

SW

WÜRTH INDUCTOR:

744318180, L = 1. 4µH, DCR = 3.2m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 5 V

OUT

08730-108

08730-109

Rev. A | Page 7 of 44

ADP1870/ADP1871

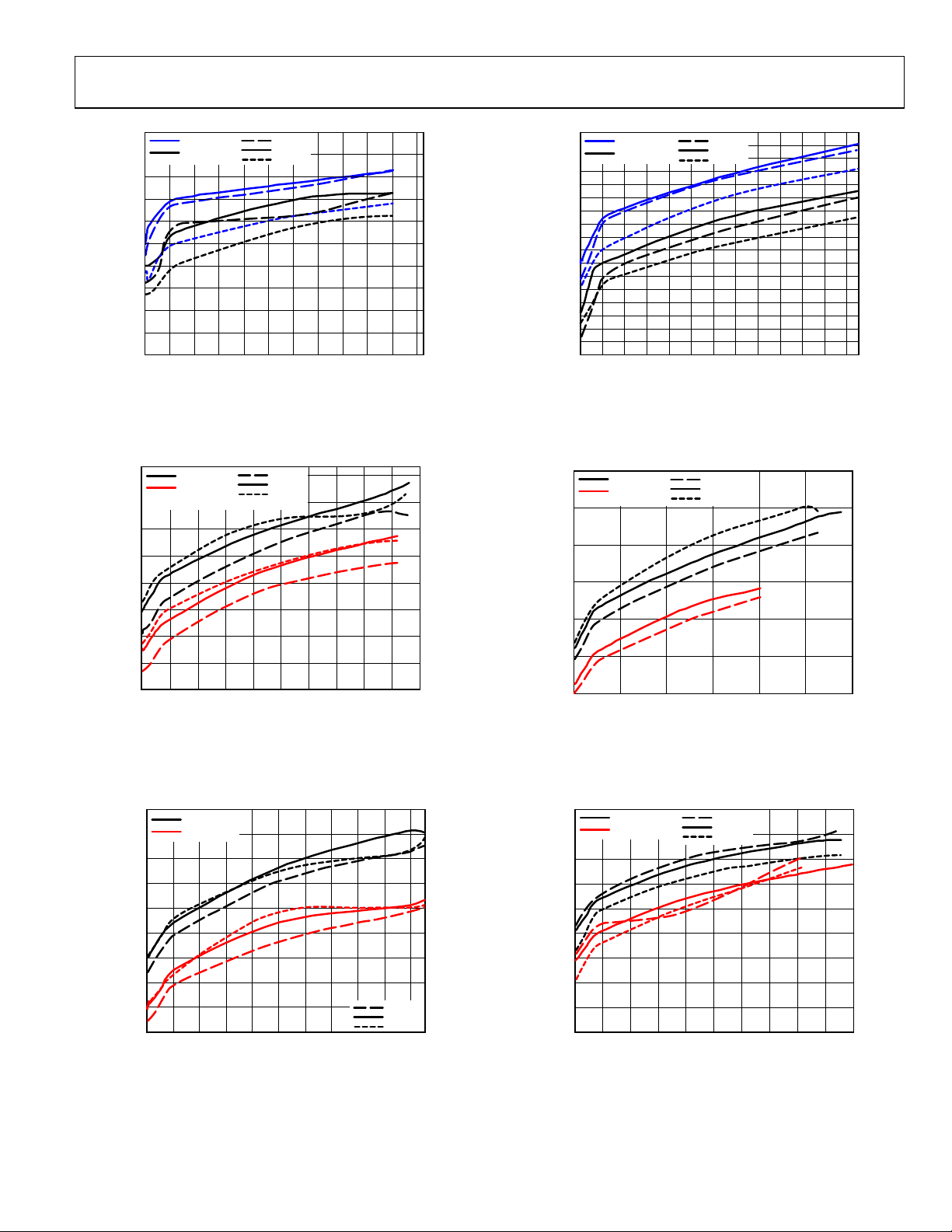

100

95

90

85

80

75

70

VIN = 13V (PSM)

65

60

55

50

45

40

EFFICIENCY (%)

35

30

VIN = 16.5V (PS M )

25

20

15

10

5

0

10 100 1k 10k 100k

Figure 10. Efficiency—1.0 MHz, V

VIN = 13V

VIN = 16.5V

TA = 25°C

= 0.8V

V

OUT

f

= 1.0MHz

SW

WÜRTH INDUCTOR:

744303012, L = 0. 12µH, DCR = 0.33m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 0.8 V

OUT

08730-110

0.807

0.806

0.805

0.804

0.803

0.802

0.801

0.800

0.799

0.798

0.797

OUTPUT VOLTAGE (V)

0.796

0.795

VIN = 13V

0.794

0.793

0.792

+125°C

+25°C

–40°C

0 2000 4000 6000 8000 10,000

VIN = 16.5V

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

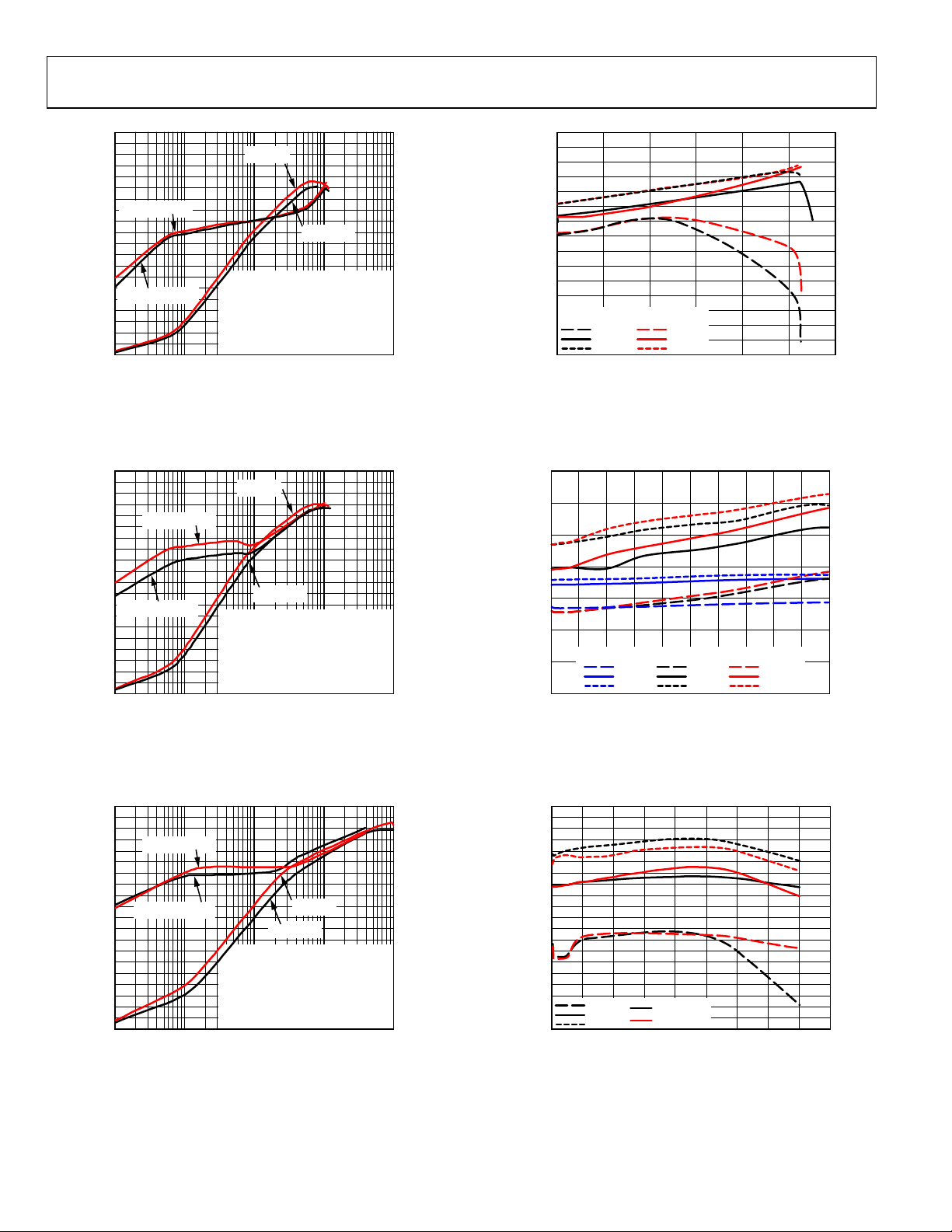

Figure 13. Output Voltage Accuracy—300 kHz, V

OUT

08730-013

= 0.8 V

100

95

90

85

80

VIN = 13V (PSM)

75

70

65

60

55

50

45

40

VIN = 16.5V (PSM)

EFFICIENCY (%)

35

30

25

20

15

10

5

0

10 100 1k 10k 100k

Figure 11. Efficiency—1.0 MHz, V

100

95

90

85

VIN = 13V (PSM)

80

75

70

65

60

55

VIN = 16.5V (PS M )

50

45

40

EFFICIENCY (%)

35

30

25

20

15

10

5

0

10 100 1k 10k 100k

Figure 12. Efficiency—1.0 MHz, V

VIN = 13V

VIN = 16.5V

TA = 25°C

= 1.8V

V

OUT

f

= 1.0MHz

SW

WÜRTH INDUCTOR:

744303022, L = 0. 22µH, DCR = 0.33m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 1.8 V

OUT

VIN = 13V

VIN = 16.5V

TA = 25°C

= 5V

V

OUT

f

= 1.0MHz

SW

WÜRTH INDUCTOR:

744355090, L = 0. 9µH, DCR = 1.6m

INFINEON FETs:

BSC042N03MS G (UPPER/ LOWER)

LOAD CURRENT (mA)

= 5 V

OUT

1.821

1.816

1.811

1.806

1.801

OUTPUT VOLTAGE (V)

1.796

1.791

1.786

0 1500 3000 4500 6000 7500 9000 10,500 12,000 13,500 15,000

08730-111

VIN = 5.5V

+125°C

+25°C

–40°C

Figure 14. Output Voltage Accuracy—300 kHz, V

7.100

7.095

7.090

7.085

7.080

7.075

7.070

7.065

7.060

7.055

7.050

7.045

7.040

7.035

7.030

OUTPUT VOLTAGE (V)

7.025

7.020

7.015

7.010

7.005

7.000

08730-112

+125°C

+25°C

–40°C

0 1000 2000 3000 4000 5000 6000 7000 8000 9000

Figure 15. Output Voltage Accuracy—300 kHz, V

VIN = 13V

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

VIN = 13V

VIN = 16.5V

LOAD CURRENT (mA)

VIN = 16.5V

+125°C

+25°C

–40°C

OUT

OUT

08730-014

= 1.8 V

08730-015

= 7 V

Rev. A | Page 8 of 44

ADP1870/ADP1871

0.808

0.806

0.804

0.802

0.800

0.798

FREQUENCY (kHz)

0.796

0.794

0.792

+125°C

+25°C

–40°C

0 1000 2000 3000 4000 5000 6000 7000 8000 10,0009000

VIN = 13V

VIN = 16.5V

LOAD CURRENT (mA)

Figure 16. Output Voltage Accuracy—600 kHz, V

= 0.8 V

OUT

08730-115

0.807

0.805

0.803

0.801

0.799

0.797

0.795

0.793

OUTPUT VOLTAGE (V)

0.791

0.789

0.787

0 2000 4000 6000 8000 10,000

VIN = 13V

LOAD CURRENT (mA)

+125°C

+25°C

–40°C

VIN = 16.5V

+125°C

+25°C

–40°C

Figure 19. Output Voltage Accuracy—1.0 MHz, V

OUT

= 0.8 V

08730-118

1.818

1.816

1.814

1.812

1.810

1.808

1.806

1.804

1.802

1.800

1.798

1.796

1.794

1.792

1.790

1.788

1.786

1.784

OUTPUT VOLTAGE (V)

1.782

1.780

1.778

1.776

1.774

1.772

1.770

0 12,00010,500900075006000450030001500

VIN = 13V

LOAD CURRENT (mA)

+125°C

+25°C

–40°C

VIN = 16.5V

+125°C

+25°C

–40°C

Figure 17. Output Voltage Accuracy—600 kHz, V

5.030

5.025

5.020

5.015

5.010

5.005

5.000

4.995

4.990

OUTPUT VOLTAGE (V)

4.985

4.980

4.975

4.970

+125°C

+25°C

–40°C

0 1000 2000 3000 4000 5000 6000 7000 8000 9000 10,000

VIN = 13V

VIN = 16.5V

VIN = 20V

LOAD CURRENT (mA)

Figure 18. Output Voltage Accuracy—600 kHz, V

= 1.8 V

OUT

OUT

= 5 V

1.820

1.815

1.810

1.805

1.800

OUTPUT VOLTAGE (V)

1.795

1.790

0

08730-016

VIN = 13V

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

Figure 20. Output Voltage Accuracy—1.0 MHz, V

5.04

5.03

5.02

5.01

5.00

4.99

4.98

4.97

4.96

4.95

OUTPUT VOLTAGE (V)

4.94

4.93

4.92

4.91

4.90

08730-017

VIN = 13V

LOAD CURRENT (mA)

Figure 21. Output Voltage Accuracy—1.0 MHz, V

+125°C

+25°C

–40°C

VIN = 16.5V

+125°C

+25°C

–40°C

VIN = 16.5V

+125°C

+25°C

–40°C

7200640056004800400024001600 32000 960088008000800

OUT

OUT

10,0000 1000 2000 3000 4000 5000 6000 7000 8000 9000

08730-019

= 1.8 V

08730-020

=5 V

Rev. A | Page 9 of 44

ADP1870/ADP1871

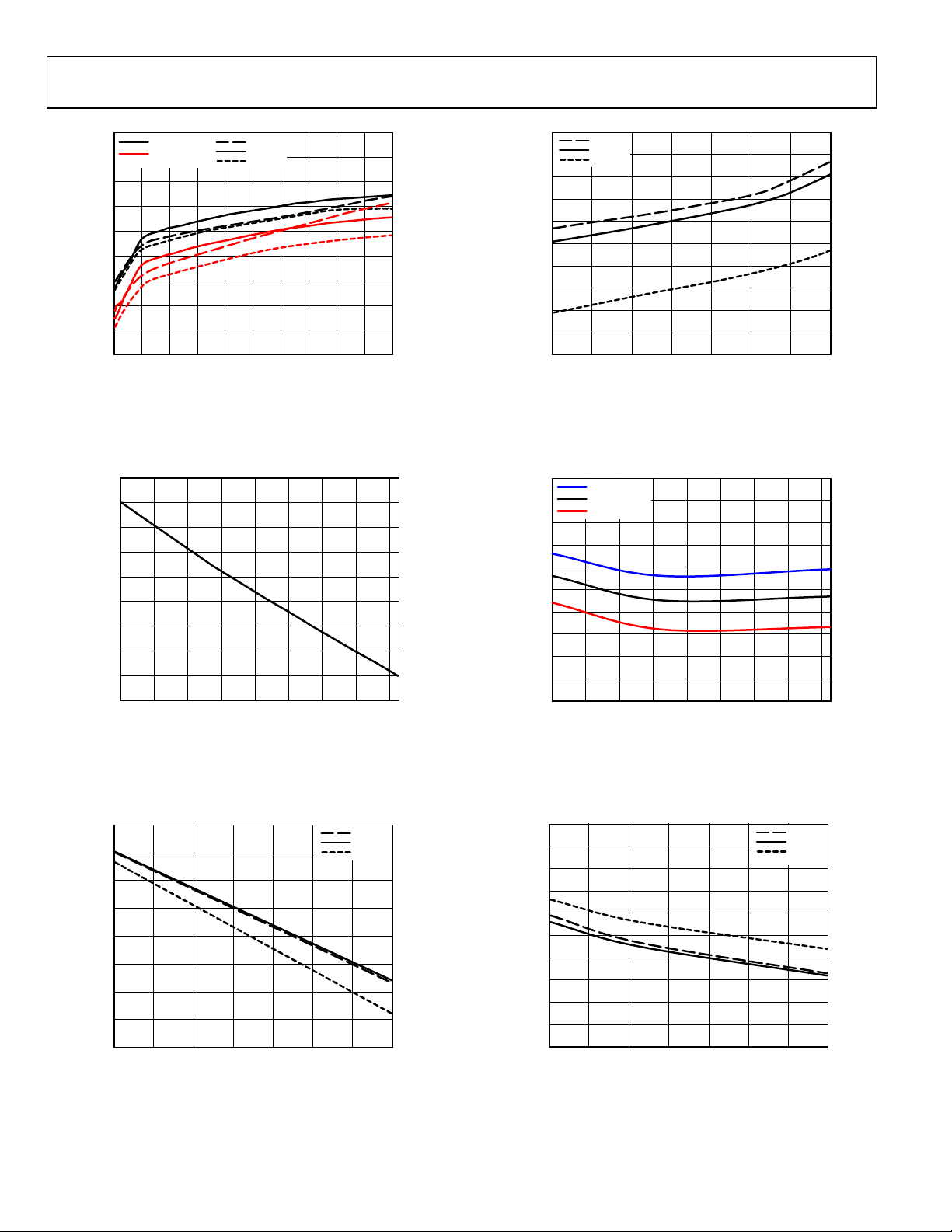

601.0

600.5

600.0

599.5

599.0

598.5

FEEDBACK VOLTAGE (V)

598.0

597.5

597.0

V

REG

–40.0 –7.5 25.0 57.5 90.0 122.5

= 5V, VIN = 20V

V

REG

= 5V, VIN = 13V

TEMPERATURE (°C)

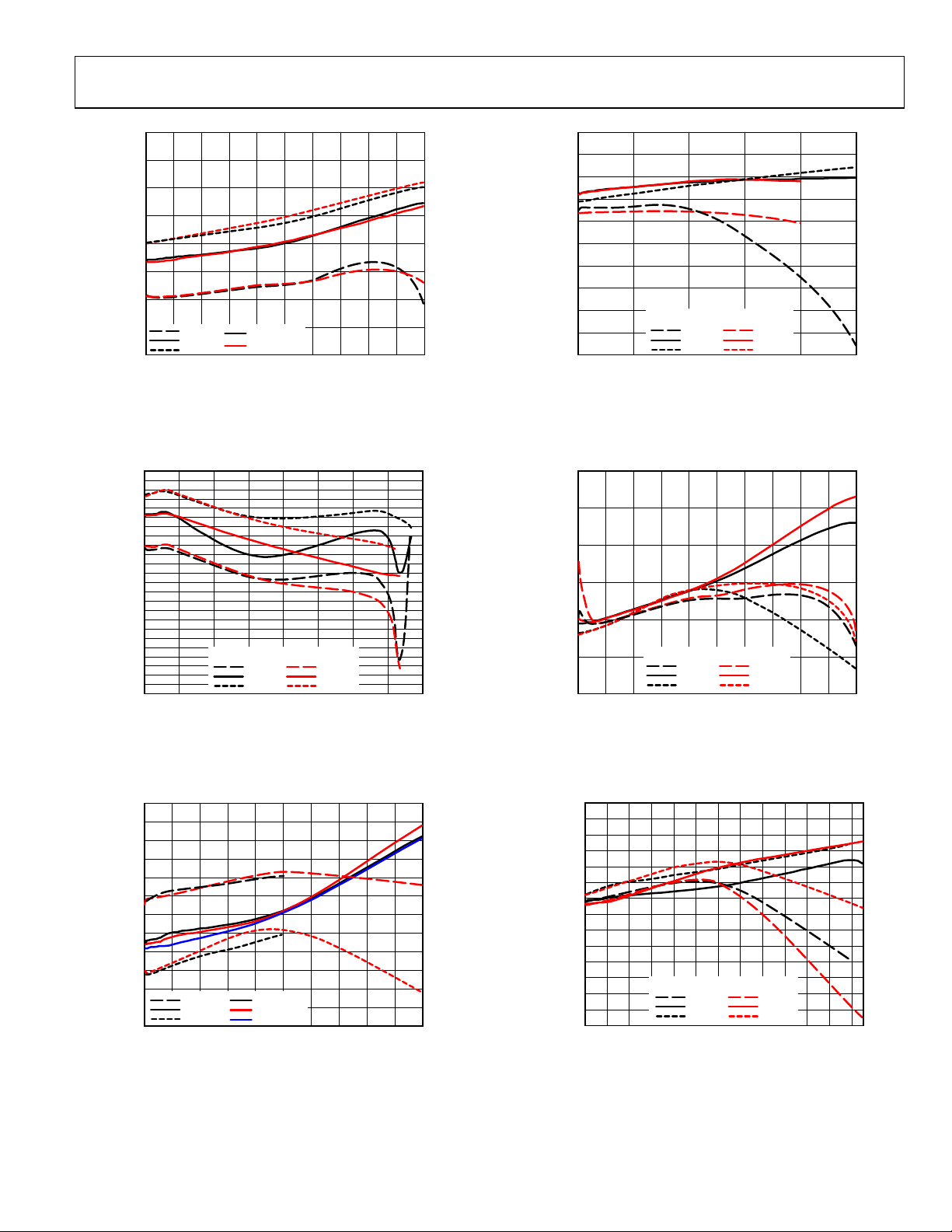

Figure 22. Feedback Voltage vs. Temperature

08730-121

900

880

860

840

820

800

780

760

SWITCHING FREQUENCY (kHz)

740

720

700

13.0 13.5 14.0 14.5 15.0 15.5 16.0 16.5

+125°C

+25°C

–40°C

VIN (V)

Figure 25. Switching Frequency vs. High Input Voltage, 1.0 MHz,

Range = 13 V to 16.5 V

V

IN

08730-124

325

315

305

295

285

275

SWITCHI NG FREQUENCY (kHz)

265

255

10.8 11.0 11.2 11.4 11.6 11.8 12.0 12.2 12.4 12.6 12.8 13.0 13.2

+125°C

+25°C

–40°C

VIN (V)

NO LOAD

08730-022

Figure 23. Switching Frequency vs. High Input Voltage, 300 kHz, ±10% of 12 V

650

600

550

500

SWITCHI NG FREQUENCY (kHz)

450

400

13.0 13.4 13.8 14.2 14.6 15.0 15.4 15.8 16.2

Figure 24. Switching Frequency vs. High Input Voltage, 600 kHz, V

+125°C

+25°C

–40°C

Range = 13 V to 16.5 V

V

IN

VIN (V)

NO LOAD

= 1.8 V,

OUT

08730-123

280

265

250

235

220

FREQUENCY (kHz)

205

190

VIN = 13V

VIN = 20V

VIN = 16.5V

0 10,0008000600040002000

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

Figure 26. Frequency vs. Load Current, 300 kHz, V

330

320

310

300

290

280

270

FREQUENCY (kHz)

260

250

240

0 15,0012,000 13,50010,500900075006000450030001500

VIN = 20V

VIN = 13V

VIN = 16.5V

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

Figure 27. Frequency vs. Load Current, 300 kHz, V

OUT

OUT

= 0.8 V

= 1.8 V

08730-025

08730-026

Rev. A | Page 10 of 44

ADP1870/ADP1871

338

334

330

326

322

318

314

FREQUENCY (kHz)

310

306

302

298

0 6400 7200 8000 8800560048004000320024001600800

VIN = 13V

VIN = 16.5V

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

Figure 28. Frequency vs. Load Current, 300 kHz, V

OUT

08730-027

= 7 V

740

733

726

719

712

705

698

691

684

677

670

663

FREQUENCY (kHz)

656

649

642

635

628

621

0 96008800800072006400560048004000320024001600800

VIN = 13V

VIN = 16.5V

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

Figure 31. Frequency vs. Load Current, 600 kHz, V

OUT

08730-030

= 5 V

540

510

480

450

420

390

FREQUENCY (kHz)

360

330

300

VIN = 13V

VIN = 16.5V

0 12,0001200 2400 3600 4800 6000 7200 8400 9600 10,800

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

Figure 29. Frequency vs. Load Current, 600 kHz, V

675

655

635

615

595

575

555

FREQUENCY (kHz)

535

515

495

VIN = 13V

VIN = 16.5V

0 1000 2000 3000 4000 5000 6000 7000 8000 9000 10,000

LOAD CURRENT (mA)

Figure 30. Frequency vs. Load Current, 600 kHz, V

OUT

OUT

= 0.8 V

+125°C

+25°C

–40°C

= 1.8 V

850

775

700

625

550

FREQUENCY (kHz)

475

400

08730-028

Figure 32. Frequency vs. Load Current, V

1225

1150

1075

1000

925

850

775

FREQUENCY (kHz)

700

625

550

08730-029

Figure 33. Frequency vs. Load Current, 1.0 MHz, V

VIN = 13V

VIN = 16.5V

0 12,00010,0008000600040002000

VIN = 13V +125°C

VIN = 16.5V

0 12,0009600 10,8008400720060004800360024001200

+125°C

+25°C

–40°C

LOAD CURRENT (mA)

+25°C

–40°C

LOAD CURRENT (mA)

= 1.0 MHz, 0.8 V

OUT

= 1.8 V

OUT

08730-031

08730-032

Rev. A | Page 11 of 44

ADP1870/ADP1871

FREQUENCY (kHz)

1450

1400

1350

1300

1250

1200

1150

1100

1050

1000

VIN = 13V +125°C

VIN = 16.5V

0 8000800 1600 2400 3200 4000 4800 5600 6400 7200

LOAD CURRENT (mA)

+25°C

–40°C

Figure 34. Frequency vs. Load Current, 1.0 MHz, V

OUT

08730-033

= 5 V

82

80

78

76

74

72

70

68

MAXIMUM DUTY CY CLE (%)

66

64

62

5.5 6.7 7.9 9.1 10.3 11.5 12.7 13.9 15.1 16.3

+125°C

+25°C

–40°C

VIN (V)

Figure 37. Maximum Duty Cycle vs. High Voltage Input (VIN)

08730-036

2.658

2.657

2.656

2.655

2.654

2.653

UVLO (V)

2.652

2.651

2.650

2.649

–40 120100806040200–20

TEMPERATURE ( °C)

Figure 35. UVLO vs. Temperature

95

90

85

80

75

70

65

MAXIMUM DUTY CY CLE (%)

60

55

300 400 500 600 700 800 900 1000

FREQUENCY (kHz)

Figure 36. Maximum Duty Cycle vs. Frequency

+125°C

+25°C

–40°C

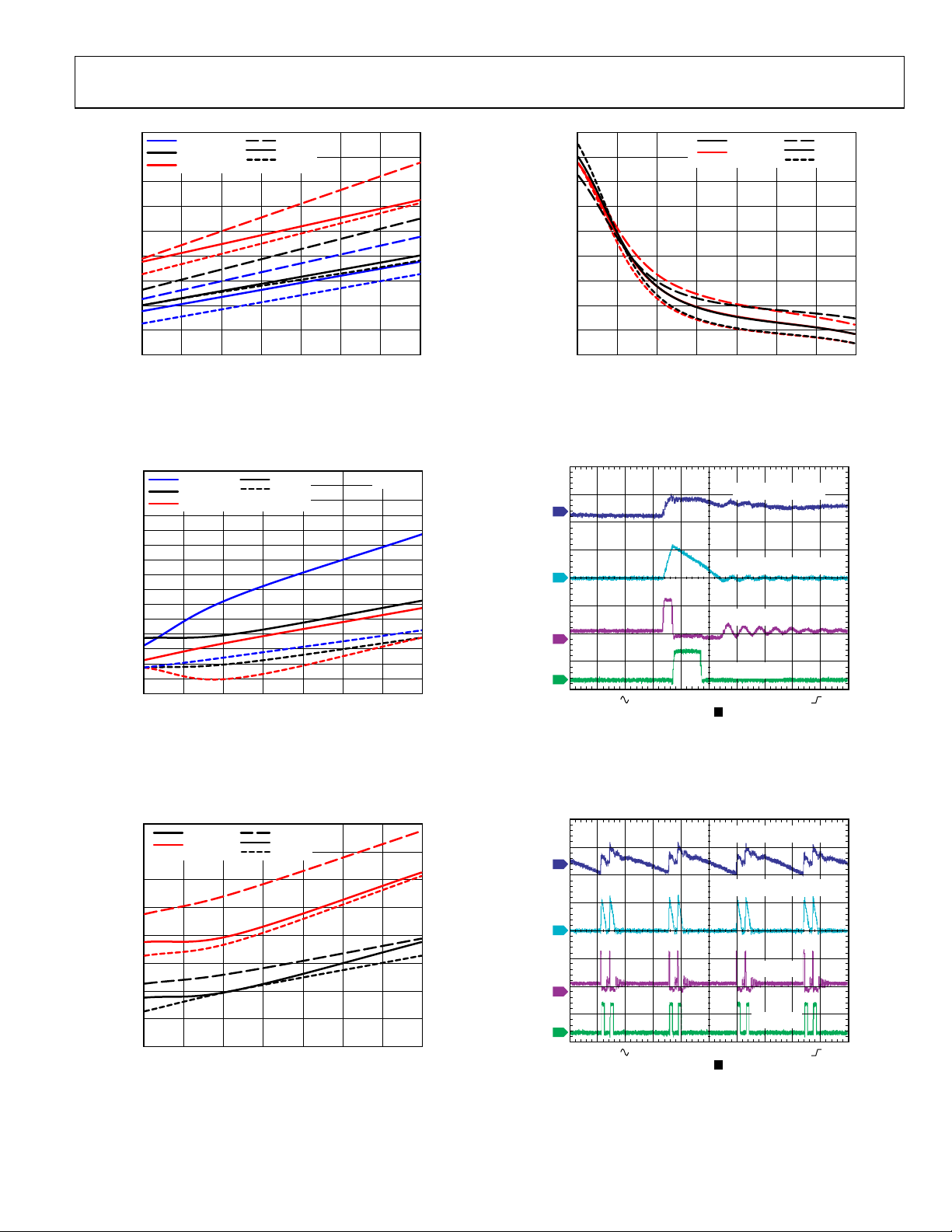

680

630

580

530

480

430

380

330

MINUMUM OF F-TIME (ns)

280

230

180

–40 120100806040200–20

08730-034

V

= 2.7V

REG

V

= 3.6V

REG

V

= 5.5V

REG

TEMPERATURE (°C)

08730-037

Figure 38. Minimum Off-Time vs. Temperature

680

630

580

530

480

430

380

330

MINUMUM OFF-TIME (ns)

280

230

180

2.7 5.55.14.74.33.93.53.1

08730-035

Figure 39. Minimum Off-Time vs. V

V

(V)

REG

(Low Input Voltage)

REG

+125°C

+25°C

–40°C

08730-038

Rev. A | Page 12 of 44

ADP1870/ADP1871

800

720

640

560

480

400

320

RECTIFI ER DROP (mV)

240

160

80

300 400 500 600 700 800 900 1000

V

= 2.7V

REG

V

= 3.6V

REG

V

= 5.5V

REG

+125°C

+25°C

–40°C

FREQUENCY (kHz)

Figure 40. Internal Rectifier Drop vs. Frequency

08730-039

80

72

64

56

48

40

32

24

BODY DIODE CONDUCT I ON TIME (n s)

16

8

2.73.13.53.94.34.75.15.5

300kHz +125°C

1MHz

V

(V)

REG

+25°C

–40°C

Figure 43. Lower-Side MOSFET Body Diode Conduction Time vs. V

08730-042

REG

1280

1200

1120

1040

960

880

800

720

640

560

480

RECTIFI ER DROP (mV)

400

320

240

160

80

2.73.13.53.94.34.75.15.5

Figure 41. Internal Boost Rectifier Drop vs. V

720

640

560

480

400

VIN = 5.5V

VIN = 13V

VIN = 16.5V

300kHz +125°C

1MHz

Over V

1MHz

300kHz

V

REG

Variation

IN

+25°C

–40°C

(V)

TA = 25°C

(Low Input Voltage)

REG

OUTPUT VOLTAGE

1

2

3

4

CH1 50mV

08730-040

CH3 10V

B

B

W

W

CH2 5A

CH4 5V

INDUCTOR CURRENT

SW NODE

LOW SIDE

M400ns A CH2 3.90A

T 35.8%

08730-043

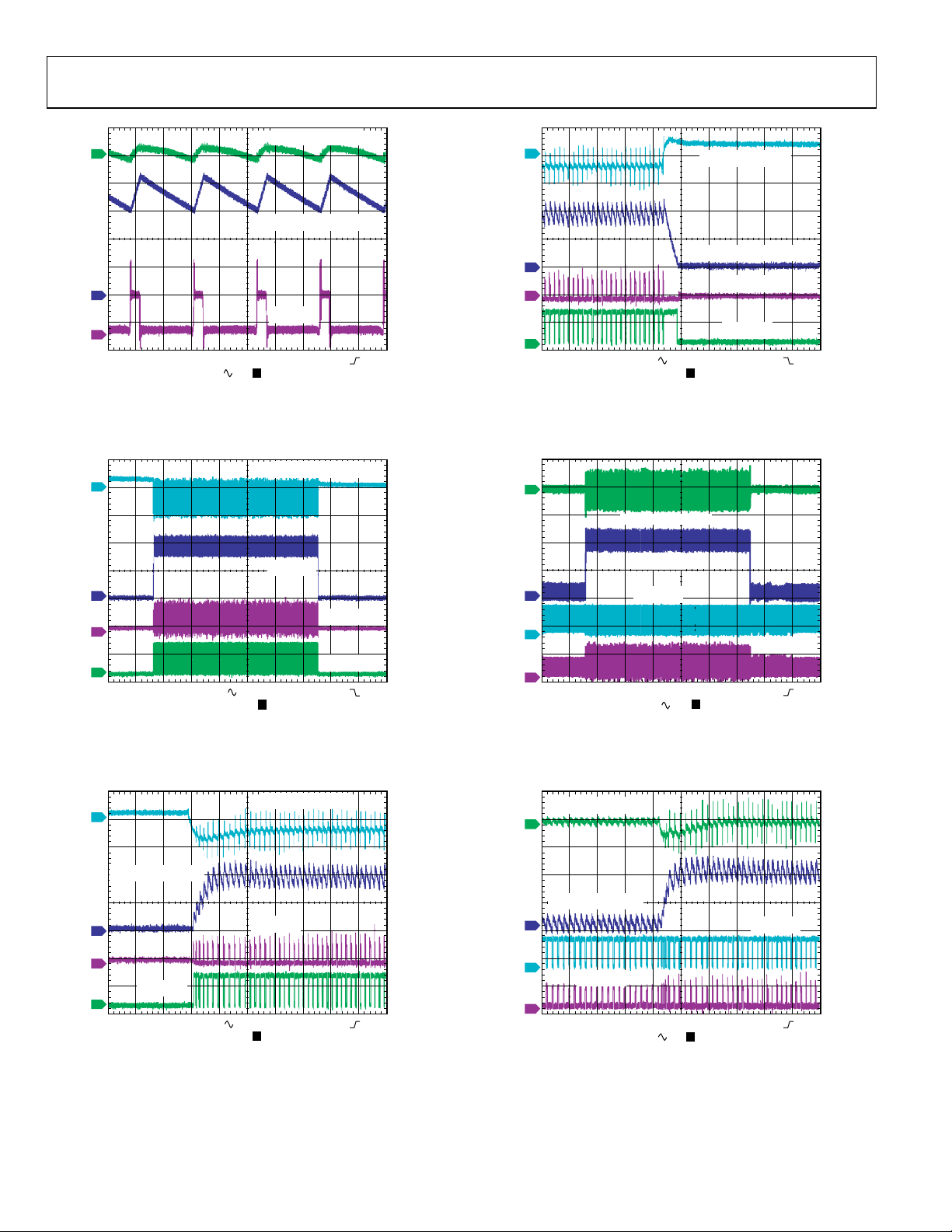

Figure 44. Power Saving Mode (PSM) Operational Waveform, 100 mA

OUTPUT VOLTAGE

1

INDUCTOR CURRENT

2

320

RECTIFI ER DROP (mV)

240

160

80

2.73.13.53.94.34.75.15.5

Figure 42. Internal Boost Rectifier Drop vs. V

V

(V)

REG

REG

08730-041

Rev. A | Page 13 of 44

3

4

CH1 50mV

CH3 10V

B

B

W

W

CH2 5A

CH4 5V

M4.0µs A CH2 3.90A

T 35.8%

Figure 45. PSM Waveform at Light Load, 500 mA

SW NODE

LOW SIDE

08730-044

ADP1870/ADP1871

OUTPUT VOLTAGE

4

INDUCTOR CURRENT

2

OUTPUT VO LTAGE

1

SW NODE

3

CH1 5A

CH3 10V CH4 100mV

M400ns A CH3 2.20V

B

T 30.6%

W

Figure 46. CCM Operation at Heavy Load, 12 A

(See Figure 94 for Application Circuit)

OUTPUT VOLTAGE

2

12A STEP

1

3

4

CH1 10A CH2 200mV

CH3 20V CH4 5V

B

M2ms A CH1 3.40A

W

T 75.6%

Figure 47. Load Transient Step—PSM Enabled, 12 A

(See Figure 94 Application Circuit)

SW NODE

LOW SIDE

1

3

SW NODE

LOW SIDE

12A NEGATIVE STEP

4

CH1 10A CH2 200mV

08730-045

CH3 20V CH4 5V

B

M20µs A CH1 3.40A

W

T 48.2%

08730-048

Figure 49. Negative Step During Heavy Load Transient Behavior—PSM Enabled,

12 A (See Figure 94 Application Circuit)

4

OUTPUT VO LTAGE

12A STEP

1

2

3

CH1 10A CH2 5V

08730-046

CH3 20V CH4 200mV

LOW SIDE

SW NODE

M2ms A CH1 6.20A

B

T 15.6%

W

08730-049

Figure 50. Load Transient Step—Forced PWM at Light Load, 12 A

(See Figure 94 Application Circuit)

2

12A POSITIVE ST EP

OUTPUT VOLTAGE

1

3

SW NODE

LOW SIDE

4

CH1 10A CH2 200mV

CH3 20V CH4 5V

B

M20µs A CH1 3.40A

W

T 30.6%

08730-047

Figure 48. Positiv e Step During Heavy Load Trans ient Behavior—PSM Enabled,

12 A, V

= 1.8 V (See Figure 94 Application Circuit)

OUT

Rev. A | Page 14 of 44

OUTPUT VOLTAGE

4

12A POSITIVE STEP

1

2

3

SW NODE

CH1 10A CH2 5V

CH3 20V CH4 200m V

M20µs A CH1 6.20A

B

T 43.8%

W

LOW SIDE

08730-050

Figure 51. Positive Step During Heavy Load Transient Behavior—Forced PWM

at Light Load, 12 A, V

= 1.8 V (See Figure 94 Application Circuit)

OUT

Loading...

Loading...