ANALOG DEVICES ADP1740 Service Manual

2 A, Low VIN, Low Dropout

V

V

V

V

V

V

V

www.BDTIC.com/ADI

FEATURES

Maximum output current: 2 A

Input voltage range: 1.6 V to 3.6 V

Low shutdown current: 2 µA

Low dropout voltage: 160 mV @ 2 A load

Initial accuracy: ±1%

Accuracy over line, load, and temperature: ±2%

7 fixed output voltage options with soft start:

0.75 V to 2.5 V (ADP1740)

Adjustable output voltage options with soft start:

0.75 V to 3.0 V (ADP1741)

High PSRR

65 dB @ 1 kHz

65 dB @ 10 kHz

54 dB @ 100 kHz

23 V rms at 0.75 V output

Stable with small 4.7 µF ceramic output capacitor

Excellent load and line transient response

Current-limit and thermal overload protection

Power-good indicator

Logic-controlled enable

Reverse current protection

APPLICATIONS

Server computers

Memory components

Telecommunications equipment

Network equipment

DSP/FPGA/microprocessor supplies

Instrumentation equipment/data acquisition systems

Linear Regulator

ADP1740/ADP1741

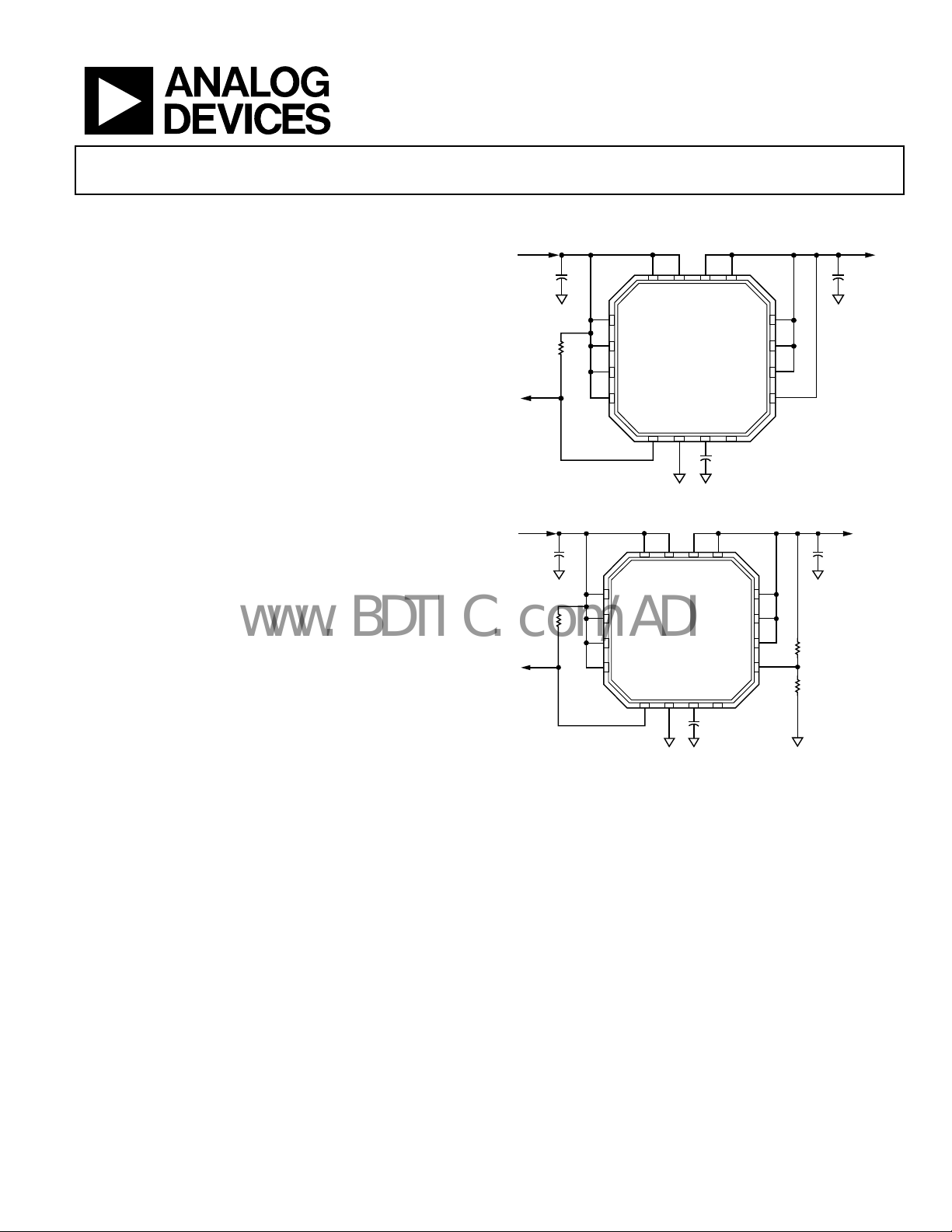

TYPICAL APPLICATION CIRCUITS

= 1.8

IN

4.7µF 4.7µF

100kΩ

PG

1

2

3

4

VIN

VIN

VIN

EN

16

VIN

VIN

ADP1740

TOP VIEW

(Not to Scale)

GND

PG

5

15

6

14

VOUT

SS

7

VOUT

10nF

13

VOUT

VOUT

VOUT

SENSE

NC

8

12

11

10

9

Figure 1. ADP1740 with Fixed Output Voltage, 1.5 V

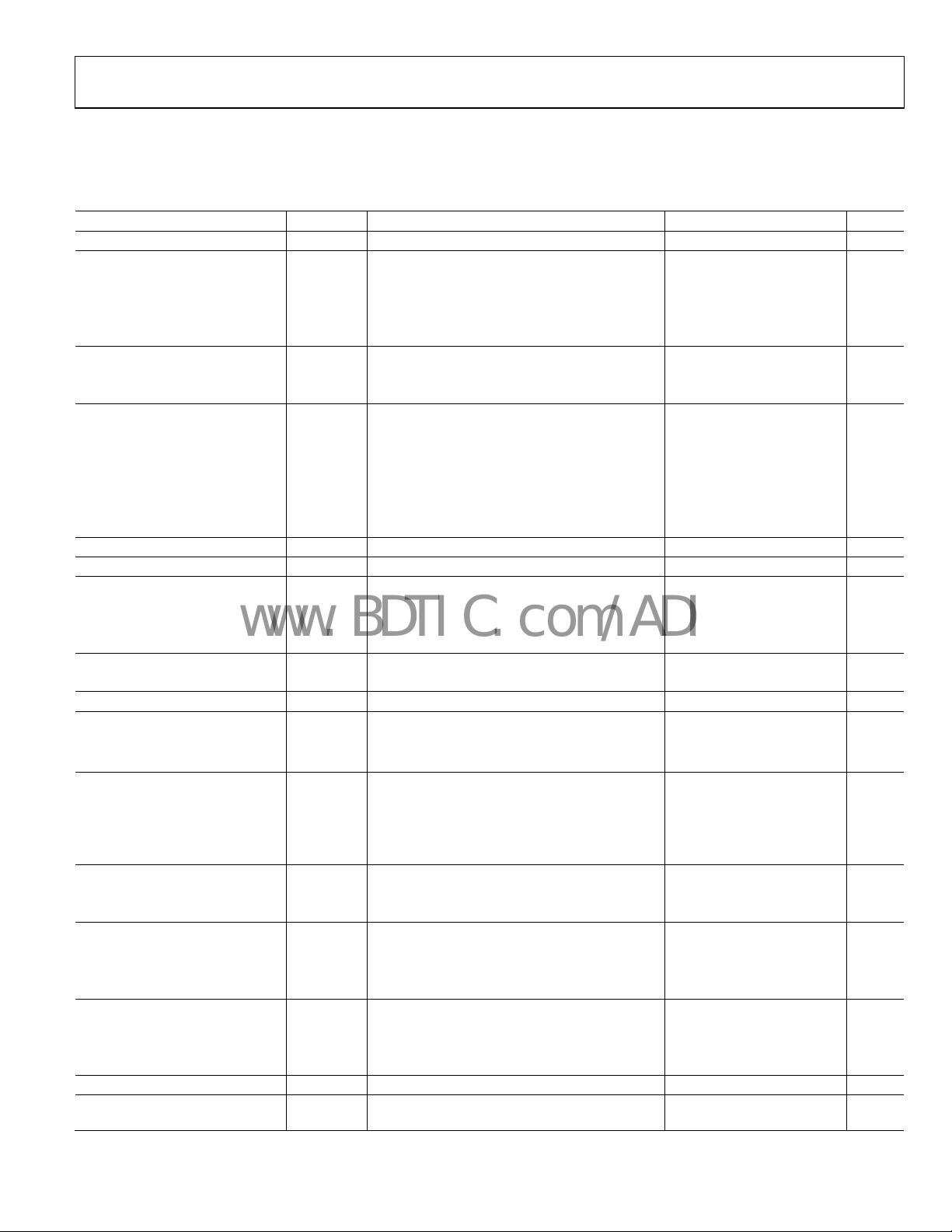

= 1.8

IN

4.7µF 4.7µF

100kΩ

PG

1

2

3

4

VIN

VIN

VIN

EN

16

VIN

ADP1741

TOP VIEW

(Not to Scale)

GND

PG

5

15

VIN

6

13

14

VOUT VOUT

VOUT

VOUT

VOUT

ADJ

NC

SS

8

7

10nF

12

11

10

9

Figure 2. ADP1741 with Adjustable Output Voltage, 0.75 V to 3.0 V

= 0.5V(1 + R1/R2)

OUT

R1

R2

OUT

= 1.5

07081-001

07081-002

GENERAL DESCRIPTION

The ADP1740/ADP1741 are low dropout (LDO) CMOS linear

regulators that operate from 1.6 V to 3.6 V and provide up to 2 A

of output current. These low V

lation of nanometer FPGA geometries operating from 2.5 V down

to 1.8 V I/O rails, and for powering core voltages down to 0.75 V.

Using an advanced, proprietary architecture, the ADP1740/

ADP1741 provide high power supply rejection ratio (PSRR) and

low noise, and achieve excellent line and load transient response

with only a small 4.7 µF ceramic output capacitor.

The ADP1740 is available in seven fixed output voltage options.

The ADP1741 is an adjustable version that allows output

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

LDOs are ideal for regu-

IN/VOUT

voltages ranging from 0.75 V to 3.0 V via an external divider.

The ADP1740/ADP1741 allow an external soft start capacitor

to be connected to program the startup. A digital power-good

output allows power system monitors to check the health of the

output voltage.

The ADP1740/ADP1741 are available in a 16-lead, 4 mm ×

4 mm LFCSP, making them not only very compact solutions,

but also providing excellent thermal performance for applications that require up to 2 A of output current in a small, low

profile footprint.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

ADP1740/ADP1741

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Typical Application Circuits ............................................................ 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Input and Output Capacitor, Recommended Specifications .. 4

Absolute Maximum Ratings ............................................................ 5

Thermal Data ................................................................................ 5

Thermal Resistance ...................................................................... 5

ESD Caution .................................................................................. 5

Pin Configurations and Function Descriptions ........................... 6

Typical Performance Characteristics ............................................. 7

REVISION HISTORY

10/08—Revision 0: Initial Version

Theory of Operation ...................................................................... 11

Soft Start Function ..................................................................... 11

Adjustable Output Voltage (ADP1741) ................................... 12

Enable Feature ............................................................................ 12

Power-Good Feature .................................................................. 12

Reverse Current Protection Feature ........................................ 13

Applications Information .............................................................. 14

Capacitor Selection .................................................................... 14

Undervoltage Lockout ............................................................... 15

Current-Limit and Thermal Overload Protection ................. 15

Thermal Considerations ............................................................ 15

PCB Layout Considerations ...................................................... 17

Outline Dimensions ....................................................................... 19

Ordering Guide .......................................................................... 19

Rev. 0 | Page 2 of 20

ADP1740/ADP1741

www.BDTIC.com/ADI

SPECIFICATIONS

VIN = (V

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT VOLTAGE RANGE VIN T

OPERATING SUPPLY CURRENT

I

I

I

I

SHUTDOWN CURRENT I

EN = GND, VIN = 1.6 V, TJ = −40°C to +85°C 30 µA

EN = GND, VIN = 3.6 V, TJ = −40°C to +85°C 100 µA

OUTPUT VOLTAGE ACCURACY

Fixed Output Voltage Accuracy

Adjustable Output Voltage

LINE REGULATION V

LOAD REGULATION

DROPOUT VOLTAGE

I

I

I

START-UP TIME

C

CURRENT-LIMIT THRESHOLD

THERMAL SHUTDOWN

Thermal Shutdown Threshold TSSD T

Thermal Shutdown Hysteresis TS

PG OUTPUT LOGIC LEVEL

PG Output Logic High PG

PG Output Logic Low PG

PG Output Delay from EN

PG OUTPUT THRESHOLD

Output Voltage Falling PG

Output Voltage Rising PG

EN INPUT

EN Input Logic High VIH 1.6 V ≤ VIN ≤ 3.6 V 1.2 V

EN Input Logic Low VIL 1.6 V ≤ VIN ≤ 3.6 V 0.4 V

EN Input Leakage Current V

UNDERVOLTAGE LOCKOUT UVLO

Input Voltage Rising UVLO

Input Voltage Falling UVLO

Hysteresis UVLO

SOFT START CURRENT ISS 1.6 V ≤ VIN ≤ 3.6 V 0.6 0.9 1.2 µA

ADJ INPUT BIAS CURRENT

(ADP1741)

+ 0.4 V) or 1.6 V (whichever is greater), I

OUT

1

I

GND

GND-SD

V

(ADP1740)

OUT

I

10 mA < I

V

Accuracy (ADP1741)

2

ADJ

I

10 mA < I

3

V

4

V

5

t

6

I

DROPOUT

START-UP

LIMIT

1.6 V ≤ V

Transition, Low to High

I-LEAKAGE

ADJ

= 100 mA, CIN = C

OUT

= −40°C to +125°C 1.6 3.6 V

J

I

= 500 µA 90 µA

OUT

= 100 mA 400 µA

OUT

= 100 mA, TJ = −40°C to +125°C 800 µA

OUT

= 2 A 1.5 mA

OUT

= 2 A, TJ = −40°C to +125°C 1.8 mA

OUT

= 4.7 µF, TA = 25°C, unless otherwise noted.

OUT

EN = GND, VIN = 3.6 V 2 6 µA

I

I

/VIN VIN = (V

OUT

/I

OUT

OUT

I

= 100 mA −1 +1 %

OUT

= 10 mA to 2 A −1.5 +1.5 %

OUT

< 2 A, TJ = −40°C to +125°C −2 +2 %

OUT

= 100 mA 0.495 0.5 0.505 V

OUT

= 10 mA to 2 A 0.492 0.508 V

OUT

< 2 A, TJ = −40°C to +125°C 0.490 0.510 V

OUT

+ 0.4 V) to 3.6 V, TJ = −40°C to +125°C −0.3 +0.3 %/V

OUT

I

= 10 mA to 2 A, TJ = −40°C to +125°C 0.5 %/A

OUT

= 100 mA, V

OUT

= 100 mA, V

OUT

= 2 A, V

OUT

= 2 A, V

OUT

CSS = 0 nF, I

= 10 nF, I

SS

≥ 1.8 V 10 mV

OUT

≥ 1.8 V, TJ = −40°C to +125°C 18 mV

OUT

≥ 1.8 V 160 mV

OUT

≥ 1.8 V, TJ = −40°C to +125°C 280 mV

OUT

= 10 mA 200 µs

OUT

= 10 mA 5.2 ms

OUT

2.4 3 5 A

rising 150

J

15

SD-HYS

1.6 V ≤ VIN ≤ 3.6 V, IOH < 1 µA 1.0 V

HIGH

1.6 V ≤ VIN ≤ 3.6 V, IOL < 2 mA 0.4 V

LOW

≤ 3.6 V, CSS = 10 nF 5.5 ms

IN

1.6 V ≤ VIN ≤ 3.6 V −10 %

FAL L

1.6 V ≤ VIN ≤ 3.6 V −6.5 %

RISE

°C

°C

EN = VIN or GND 0.1 1 µA

1.58 V

RISE

1.25 V

FAL L

100 mV

HYS

1.6 V ≤ VIN ≤ 3.6 V, TJ = −40°C to +125°C 10 150 nA

I-BIAS

Rev. 0 | Page 3 of 20

ADP1740/ADP1741

www.BDTIC.com/ADI

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

1.6 V ≤ VIN ≤ 3.6 V 10 µA

SENSE INPUT BIAS CURRENT

(ADP1740)

OUTPUT NOISE OUT

10 Hz to 100 kHz, V

POWER SUPPLY REJECTION RATIO PSRR VIN = V

1 kHz, V

1 kHz, V

10 kHz, V

10 kHz, V

100 kHz, V

100 kHz, V

1

Minimum output load current is 500 A.

2

Accuracy when VOUT is connected directly to ADJ. When VOUT voltage is set by external feedback resistors, absolute accuracy in adjust mode depends on the tolerances

of the resistors used.

3

Based on an endpoint calculation using 10 mA and 2 A loads. See for typical load regulation performance. Figure 6

4

Dropout voltage is defined as the input to output voltage differential when the input voltage is set to the nominal output voltage. This applies only to output voltages

above 1.6 V.

5

Start-up time is defined as the time between the rising edge of EN to V

6

Current-limit threshold is defined as the current at which the output voltage drops to 90% of the specified typical value. For example, the current limit for a 1.0 V

output voltage is defined as the current that causes the output voltage to drop to 90% of 1.0 V, or 0.9 V.

INPUT AND OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS

SNS

I-BIAS

10 Hz to 100 kHz, V

NOISE

OUT

OUT

OUT

= 0.75 V 23 µV rms

OUT

= 2.5 V 65 µV rms

OUT

+ 1 V, I

= 10 mA

OUT

= 0.75 V 65 dB

= 2.5 V 56 dB

= 0.75 V 65 dB

OUT

= 2.5 V 56 dB

OUT

= 0.75 V 54 dB

OUT

= 2.5 V 51 dB

OUT

being at 95% of its nominal value.

OUT

Table 2.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

MINIMUM INPUT AND OUTPUT CAPACITANCE

CAPACITOR ESR R

1

The minimum input and output capacitance should be greater than 3.3 µF over the full range of operating conditions. The full range of operating conditions in the

application must be considered during capacitor selection to ensure that the minimum capacitance specification is met. X7R and X5R type capacitors are recommended;

Y5V and Z5U capacitors are not recommended for use with this LDO.

1

C

T

MIN

T

ESR

= –40°C to +125°C 3.3 µF

A

= –40°C to +125°C 0.001 0.1 Ω

A

Rev. 0 | Page 4 of 20

ADP1740/ADP1741

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

VIN to GND −0.3 V to +3.6 V

VOUT to GND −0.3 V to VIN

EN to GND −0.3 V to +3.6 V

SS to GND −0.3 V to +3.6 V

PG to GND −0.3 V to +3.6 V

SENSE/ADJ to GND −0.3 V to +3.6 V

Storage Temperature Range −65°C to +150°C

Operating Junction Temperature Range −40°C to +125°C

Soldering Conditions JEDEC J-STD-020

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL DATA

Absolute maximum ratings apply only individually, not in

combination. The ADP1740/ADP1741 may be damaged when

junction temperature limits are exceeded. Monitoring ambient

temperature does not guarantee that the junction temperature is

within the specified temperature limits. In applications with

high power dissipation and poor PCB thermal resistance, the

maximum ambient temperature may need to be derated. In

applications with moderate power dissipation and low PCB

thermal resistance, the maximum ambient temperature can

exceed the maximum limit as long as the junction temperature

is within specification limits.

The junction temperature (T

ambient temperature (T

), and the junction-to-ambient thermal resistance of the

(P

D

package (θ

). TJ is calculated using the following formula:

JA

= TA + (PD × θJA)

T

J

The junction-to-ambient thermal resistance (θ

) of the device is dependent on the

J

), the power dissipation of the device

A

) of the package

JA

board design is required. The value of θ

on PCB material, layout, and environmental conditions. The

specified values of θ

board. Refer to JEDEC JESD51-7 for detailed information about

board construction. For more information, see the AN-772

Application Note, A Design and Manufacturing Guide for the

Lead Frame Chip Scale Package (LFCSP), at www.analog.com.

Ψ

is the junction-to-board thermal characterization parameter

JB

with units of °C/W. Ψ

calculation using a 4-layer board. The JEDEC JESD51-12

document, Guidelines for Reporting and Using Electronic Package

Thermal Information, states that thermal characterization

parameters are not the same as thermal resistances. Ψ

the component power flowing through multiple thermal paths

rather than through a single path, as in thermal resistance (θ

Therefore, Ψ

the package, as well as radiation from the package, factors that

make Ψ

junction temperature (T

ature (T

formula:

T

= TB + (PD × ΨJB)

J

Refer to the JEDEC JESD51-8 and JESD51-12 documents for

more detailed information about Ψ

THERMAL RESISTANCE

θJA and ΨJB are specified for the worst-case conditions, that is, a

device soldered in a circuit board for surface-mount packages.

Table 4. Thermal Resistance

Package Type θJA ΨJB Unit

16-Lead LFCSP with Exposed Pad 130 32.7 °C/W

ESD CAUTION

is based on modeling and calculation using a 4-layer board. The

junction-to-ambient thermal resistance is highly dependent on

the application and board layout. In applications where high

maximum power dissipation exists, close attention to thermal

are based on a 4-layer, 4 in × 3 in circuit

JA

of the package is based on modeling and

JB

thermal paths include convection from the top of

JB

more useful in real-world applications. Maximum

JB

) is calculated from the board temper-

J

) and the power dissipation (PD) using the following

B

may vary, depending

JA

.

JB

measures

JB

).

JB

Rev. 0 | Page 5 of 20

ADP1740/ADP1741

T

T

2

T

T

2

www.BDTIC.com/ADI

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

VOU

VIN

VIN

VOU

14

13

15

16

PIN 1

INDICATO R

1VIN

2VIN

ADP1740

3VIN

TOP VIEW

(Not to Scale)

4EN

5

6

PG

NOTES

1. NC = NO CONNECT.

. THE EXPOS ED PAD ON THE BOTTOM O F THE LFCSP ENHANCES

THERMAL PERFORMANCE AND IS ELECTRICALLY CONNECTED TO GND

INSIDE THE PACKAGE. IT IS RECOMMENDED THAT THE EXP OSED PAD

BE CONNECTED TO THE GROUND PL ANE ON THE BOARD.

GND

7

SS

8

C

N

12 VOUT

11 VOUT

10 VOUT

9SENSE

1VIN

2VIN

ADP1741

3VIN

TOP VIEW

(Not to Scale)

4EN

NOTES

1. NC = NO CONNECT.

. THE EXPOS ED PAD ON THE BOTTOM O F THE LFCSP ENHANCES

THERMAL PERFORMANCE AND IS ELECTRICALLY CONNECTED TO GND

INSIDE THE PACKAGE. IT IS RECOMMENDED THAT THE EXP OSED PAD

07081-003

BE CONNECTED TO THE GROUND PL ANE ON THE BOARD.

VIN

VIN

15

16

PIN 1

INDICATO R

5

6

PG

GND

VOU

VOU

14

13

12 VOUT

11 VOUT

10 VOUT

9ADJ

8

7

C

SS

N

Figure 3. ADP1740 Pin Configuration Figure 4. ADP1741 Pin Configuration

Table 5. Pin Function Descriptions

Pin No.

ADP1740 ADP1741

1, 2, 3, 15, 16 1, 2, 3, 15, 16 VIN

Mnemonic Description

Regulator Input Supply. Bypass VIN to GND with a 4.7 µF or greater capacitor. Note that all

five VIN pins must be connected to the source supply.

4 4 EN

Enable Input. Drive EN high to turn on the regulator; drive it low to turn off the regulator. For

automatic startup, connect EN to VIN.

5 5 PG

Power-Good Output. This open-drain output requires an external pull-up resistor to VIN. If

the part is in shutdown mode, current-limit mode, or thermal shutdown, or if it falls below

90% of the nominal output voltage, the PG pin immediately transitions low.

6 6 GND Ground.

7 7 SS Soft Start Pin. A capacitor connected to this pin determines the soft start time.

8 8 NC Not Connected. No internal connection.

9 SENSE

Sense Input. This pin measures the actual output voltage at the load and feeds it to the error

amplifier. Connect the SENSE pin as close to the load as possible to minimize the effect of IR

drop between the regulator output and the load.

9 ADJ Adjust Pin. A resistor divider from VOUT to ADJ sets the output voltage.

10, 11, 12,

13, 14

10, 11, 12,

13, 14

EP EP

VOUT

Exposed

pad

Regulated Output Voltage. Bypass VOUT to GND with a 4.7 µF or greater capacitor. Note that

all five VOUT pins must be connected to the load.

The exposed pad on the bottom of the LFCSP enhances thermal performance and is

electrically connected to GND inside the package. It is recommended that the exposed pad

be connected to the ground plane on the board.

07081-004

Rev. 0 | Page 6 of 20

Loading...

Loading...