4.25 Gbps 3.3V Low Noise

Preliminary Technical Data

FEATURES

Technology: high performance SiGe

Bandwidth: 3.2 GHz minimum

Input noise current density: 10 pA√Hz

Optical sensitivity: −22 dBm

Differential transimpedance: 4000 V/A

Power dissipation: 75 mW

Differential output swing: 250 mV p-p

Input current overload: +3.25 dBm

Output resistance: 50 Ω side

RSSI voltage and current ratio: 0.8V/mA

Low-freq cutoff: 15 kHz

On-chip PD filter: R

Die size: 0.7 mm × 1.2 mm

APPLICATIONS

4.25 Gbps optical modules

SFF-8472 compliant receivers

PIN/APD-TIA receive optical subassembly

SONET/GbE/FC optical receivers, transceivers, transponders

= 200 Ω CF = 20 pF

F

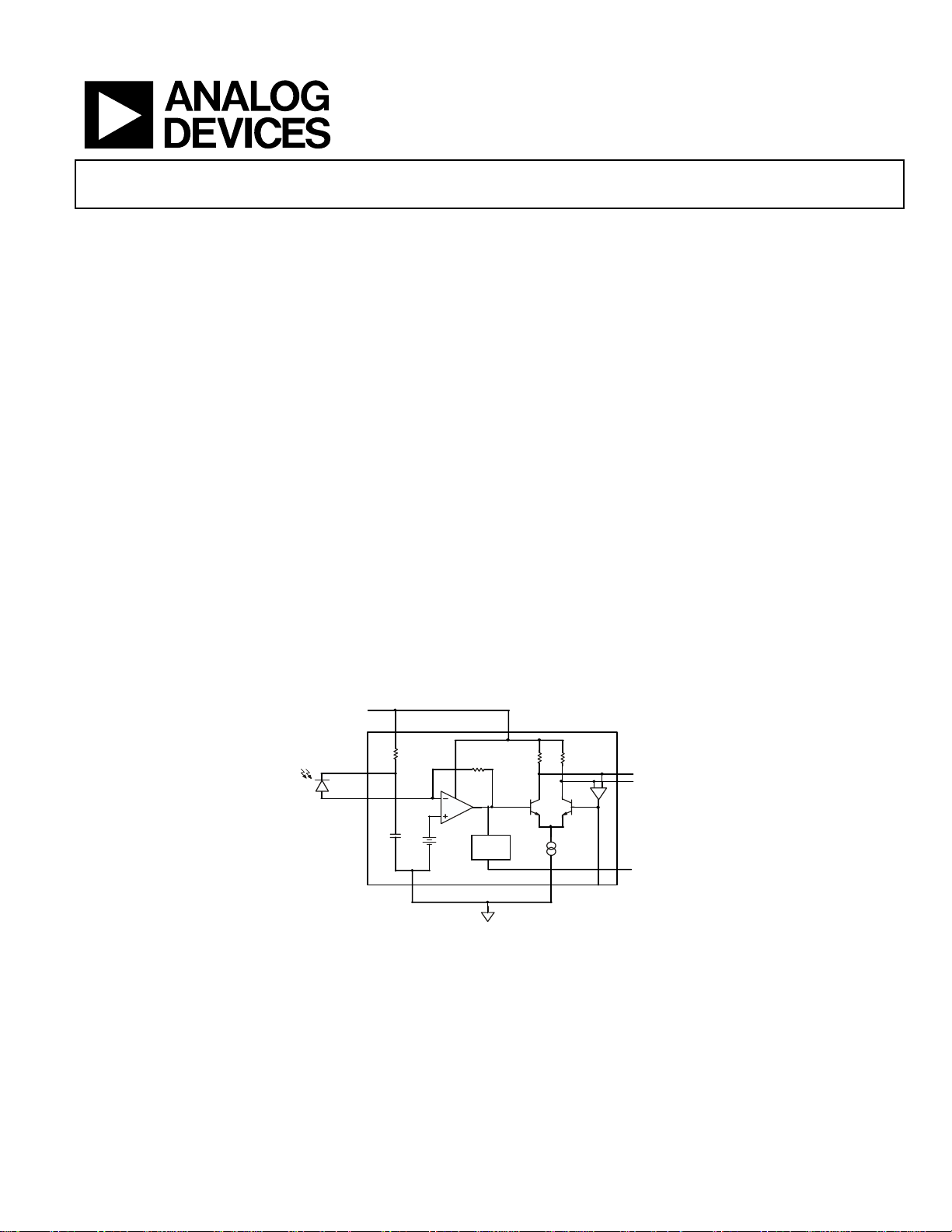

FUNCTIONAL BLOCK DIAGRAM

Transimpedance Amplifier

ADN2882

PRODUCT DESCRIPTION

The ADN2882 is a compact, high performance 3.3 V power

supply SiGe transimpedance amplifier (TIA) optimized for

small form factor 4.25 Gbps metro-access, Ethernet PIN/APDTIA modules and 1×/2×/4× Fibre channel receiver applications

and meets OC48 SR/IR sensitivity requirements. The ADN2882

is a single-chip solution for detecting photodiode current with a

differential output voltage. The ADN2882 features low input

referred noise current of 600 nA enabling −22 dBm sensitivity;

3.2 GHz minimum bandwidth enables up to 4.25 Gbps

operation; +3.25 dBm nominal operation at 10dB extinction

ratio. RSSI output signal proportional to average input current

is available for monitoring and alarm generation. To facilitate

assembly in small form factor packages such as a TO-46 or TO56 header, the ADN2882 integrates the photodiode filter

network on chip and features 15 kHz low frequency cutoff

without any external components. The ADN2882 chip area is

less than 1 mm

available in die form.

2

, operates with a 3.3 V power supply and is

3.3V

VCC_FILTER

FILTER

IN

Rev. PrD November 04 2004

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

200Ω

20pF

0.85V

GND

Figure 1. ADN2882 Block Diagram

1100Ω

VCC

50Ω50Ω

OUT

OUTB

5mA

GND

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

CAP

ADN2882 Preliminary Technical Data

TABLE OF CONTENTS

Electrical Specifications ...................................................................3

Pad Layout..........................................................................................6

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pad Description ................................................................................ 5

REVISION HISTORY

07/04—Revision PrB July 27 2004

09/04 - Revision PrC Sept 30 2004: spec changes

11/04 – Revision PrD: RSSI added in

Pad Coordinates ............................................................................6

Die Information.............................................................................6

Assembly Recommendations...........................................................7

Rev. PrD Nov. 04 2004 | Page 2 of 10

Preliminary Technical Data ADN2882

ELECTRICAL SPECIFICATIONS

Table 1.

Parameter Conditions1 Min Typ Max Unit

DYNAMIC PERFORMANCE

Bandwidth (BW)2 −3 dB 3.3 3.8 GHz

Total Input RMS Noise (I

Small Signal Transimpedance (ZT) 100MHz 2800 3800 4800 V/A

Low Frequency Cutoff

Output Return Loss DC to 4.25GHz, differential −20 −12 dB

Input Overload Current3 Pavg TBD 3.25 dBm

Maximum Output Swing pk-pk diff, I

Output Data Transition Time 20% to 80% rise/fall time I

PSRR <10 MHz −40 dB

Group Delay Variation 50 MHz to 1.0 GHz TBD ps

Transimpedance Ripple 50 MHz to 1.0 GHz TBD dB

Total Jitter 10 µA < I

100 µA < I

Deterministic Jitter 10 µA < I

Linear Output Range

DC PERFORMANCE

Power Dissipation I

Input Voltage 0.85 V

Output Common Mode Voltage DC terminated to VCC Vcc − 0.12 V

Output Impedance Single-ended 50 Ω

PD FILTER Resistance RF 200 Ω

PD FILTER Capacitance CF 20 pF

RSSI Sensitivity I

RSSI Offset I

1

Min/Max VCC = +3.3 V ± 0.3 V, T

2

Photodiode capacitance CD = 0.5pF ± 0.15pF, photodiode resistance = 5 Ω . Load impedance = 50Ω (each output, ac-coupled).

3

–10

10

BER, 10 dB ER,

)2 DC to 4.0 GHz 520 TBD nA

RMS

= −40°C to +95°C; Typ V

a

= 10µA

I

IN

IIN = 500µA

= 2.0 mA 180 250 350 mV

IN,PK- PK

= 2.5 mA 40 ps

IN,PK- PK

≤ 100 µA TBD TBD ps

IN,PK- PK

≤ 2.0 µA TBD TBD ps

IN,PK- PK

≤ 100 µA 2 ps

IN,PK- PK

100 µA < I

IN,PK- PK

≤ 2.0 µA

Pk-pk, < 1dB compression

= 0 50 75 120 mW

IN,AVE

= 0 uA to 1 mA 0.8 V/mA

IN, AVE

= 0 uA TBD mV

IN, AVE

= 3.3 V, Ta = +25C.

CC

15

TBD

4

TBD

kHz

Ps

kHz

mV

Rev. PrD Nov. 04 2004 | Page 3 of 10

ADN2882 Preliminary Technical Data

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage (VCC to GND) 5 V

Maximum Input Current 10 mA

Storage Temperature Range −65°C to +125°C

Operating Ambient Temperature Range −40°C to +95°C

Maximum Junction Temperature 165°C

Die Attach Temperature (<60 seconds) 450°C

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Rating

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. PrD Nov. 04 2004 | Page 4 of 10

Preliminary Technical Data ADN2882

PAD DESCRIPTION

B

FILTER

RSSI

Table 3.

Pad No. Pad Name Function

1 GND Ground (input return).

2 IN Current input. Bond directly to PD anode.

3 TEST Test probe Pad. Leave floating.

4 FILTER Filter Output

5 FILTER Filter Output

6 GND Ground.

7 RSSI Voltage Output (provides average input current reading)

8 CAP Low Frequency setpoint. Connect with 1 nF capacitance to GND for < 15 kHz.

9 GND Ground.

10 GND Ground (output return).

11 OUTB Negative Output. Drives 50 Ω termination (ac or dc termination).

12 OUT Positive Output. Drives 50 Ω termination (ac or dc termination).

13 GND Ground (output return).

14 GND Ground.

15 VCCFILTER Filter Supply. Connect to VCC to enable on-chip 200 Ω, 20 pf Filter.

16 VCC 3.3 V positive Supply. Recommended bypass to GND is 200 pF RF capacitor.

17 VCC 3.3 V positive Supply. Recommended bypass to GND is 200 pF RF capacitor.

Rev. PrD Nov. 04 2004 | Page 5 of 10

ADN2882 Preliminary Technical Data

PAD LAYOUT

B

FILTER

RSSI

Figure 2.. Pad Layout

PAD COORDINATES

Table 4.

PAD # PAD X (um) Y (um)

1 GND −500 260

2 IN −500 130

3 TEST −500 10

4 FILTER −500 −120

5 FILTER −500 −260

6 GND −350 −260

7 RSSI −200 −260

8 CAP −50 −260

9 GND 130 −260

10 GND 500 −260

11 OUTB 350 −60

12 OUT 350 60

13 GND 500 260

14 GND 130 260

15 VCCFILTER −50 260

16 VCC −200 260

17 VCC −350 260

DIE INFORMATION

Die Size

0.7mm × 1.2mm

(edge-edge including 1mil scribe)

Die Thickness

10mils = 0.25mm

Passivation Openings

0.075 mm × 0.075 mm

(pads 1-8, 9, 10, 13, 15, 16, 17)

0.144mm × 0.075mm

(pads 9, 11, 12, 14)

Passivation Composition

5000Å Si3N4 (top)

+5000 Å SiO

Pad Composition

Al/1%Cu

Backside Contact

(bot)

2

Rev. PrD Nov. 04 2004 | Page 6 of 10

Preliminary Technical Data ADN2882

ASSEMBLY RECOMMENDATIONS

VPD

OUTB

Figure 3. 5-Pin TO-46 with External Photodiode Supply V

1× Vendor-Specific (0.3 mm × 0.3 mm) 4.25 Gbps Photo Diode

560pF

VCC

200pF

OUT

PD

1× ADN2882 (0.7 mm × 1.2 mm) Analog Devices SiGe 4.25 Gbps Transimpedance Amplifier

1× 200 pF RF single-layer capacitor

1× 560pF RF Single-layer capacitor

Notes

Minimize all GND bond wire lengths

Minimize IN, OUT and OUTB bond wire lengths

Maintain symmetry between IN and OUT/OUTB bond wires

Rev. PrD Nov. 04 2004 | Page 7 of 10

ADN2882 Preliminary Technical Data

ASSEMBLY RECOMMENDATIONS

VCC

200pF

OUTB

Figure 4. Recommended Layout for 4 pin TO-46

Ceramic

Standoff

OUT

1× Vendor-Specific (0.3 mm × 0.3 mm) 4.25 Gbps Photo Diode

1× ADN2882 (0.7 mm × 1.2 mm) Analog Devices SiGe 4.25 Gbps Transimpedance Amplifier

1× 200 pF RF single-layer capacitor

1× ceramic standoff

Notes

Minimize all GND bond wire lengths

Minimize IN, OUT and OUTB bond wire lengths

Maintain symmetry between IN and OUT/OUTB bond wires

Rev. PrD Nov. 04 2004 | Page 8 of 10

Preliminary Technical Data ADN2882

TYPICAL SIGNAL PERFORMANCE

Rev. PrD Nov. 04 2004 | Page 9 of 10

ADN2882 Preliminary Technical Data

PR04946-0-11/04(PrD)

ORDERING GUIDE

Model Temperature Package Description Package Option

ADN2882XCHIPS-WP -40oC to 95oC NA Tested Die

Rev. PrD Nov. 04 2004 | Page 10 of 10

Loading...

Loading...