查询ADN2860供应商查询ADN2860供应商

3-Channel Digital

Potentiometer with

a

Nonvolatile Memory

Preliminary Technical Data ADN2860

FEATURES

3 Channels: Dual 512-Position

Single 128-Position

Ω or 150KΩ Full-Scale Resistance

25K

Low Temperature Coefficient: 35ppm/°C

Nonvolatile Memory Retains Wiper Settings

Permanent Memory Write-Protection

Linear Increment/Decrement

Log taper Increment/Decrement

2

C Compatible Serial Interface

I

3V to 5V Single Supply Operation

±2.5V Dual Supply Operation

256 Bytes General Purpose User EEPROM

11 Bytes RDAC user EEPROM

GBIC and SFP Compliant EEPROM

100-year Typical Data Retention at TA=55°C

APPLICATIONS

Laser Diode Drivers

Optical Amplifiers

TIA Gain Setting

TEC Controller Temperature Set Points

GENERAL DESCRIPTION

The ADN2860 provides dual 512-position and a single 128position digitally controlled variable resistor

4x4mm LFCSP package. This device performs the same

electronic adjustment function as a potentiometer, trimmer, or

variable resistor. Each VR offers a completely programmable

value of resistance between the A terminal and the Wiper or the

B terminal and the Wiper. The fixed A-to-B terminal resistance

of 25kΩ or 250kΩ has a 1% channel-to-channel matching

tolerance and a nominal temperature coefficient of 35ppm/°C.

Wiper position programming, EEPROM reading, and EEPROM

writing is conducted via the standard 2-wire I

Previous/Default wiper position settings can be stored in

memory, and refreshed upon system power-up.

Additional features of the ADN2860 include preprogrammed

linear and logarithmic increment/decrement wiper changing, and

actual resistor tolerances are stored in EEPROM so that the

1

(VR) in a single

2

C interface.

VDD

VDD

VDD

VSS

VSS

VSS

GND

GND

GND

SCL

SCL

SCL

SDA

SDA

SDA

A0_R

A0_R

A0_R

A1_R

A1_R

A1_R

A0_E

A0_E

A0_E

A1_E

A1_E

A1_E

PRB

PRB

PRB

WPB

WPB

actual end-to-end resistance is known, which is valuable for

calibration in precision applications.

The ADN2860 EEPROM, channel resolution, and package size

conforms to GBIC and SFP specifications. The ADN2860 is

available in a 4x4mm 24-lead LFCSP package. All parts are

guaranteed to operate over the extended industrial temperature

range of –40C to 85°C.

1. The term nonvolatile memory, EEMEM, and EEPROM are used

2. The term programmable resistor, variable resistor, RDAC, and digital

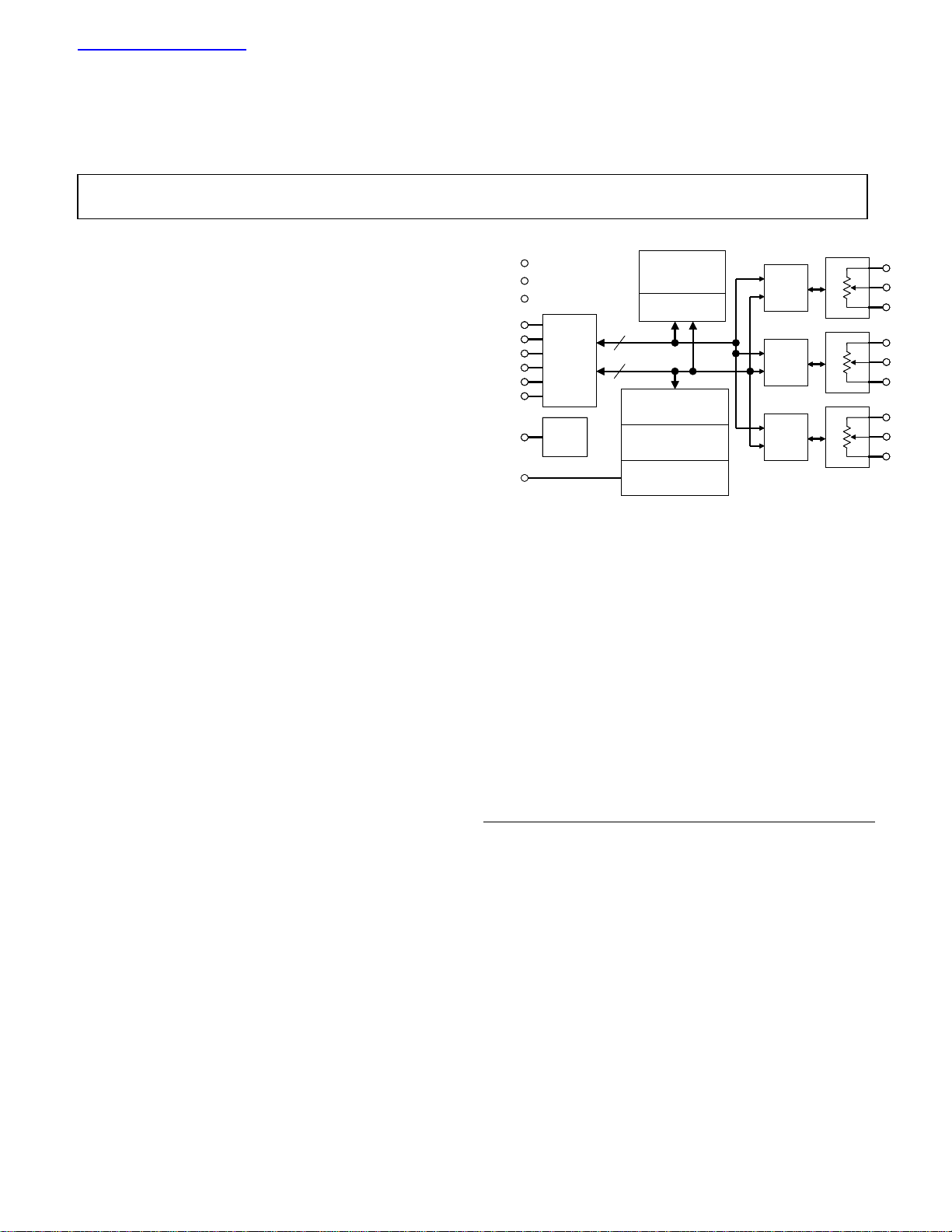

FUNCTIONAL BLOCK DIAGRAM

256 bytes

256 bytes

256 bytes

USER EEPROM

USER EEPROM

USER EEPROM

32 bytes

32 bytes

32 bytes

RDAC EEPROM

RDAC EEPROM

RDAC EEPROM

DATA

8

DATA

I2C

I2C

I2C

SERIAL

SERIAL

SERIAL

INTERFACE

INTERFACE

INTERFACE

POWER

POWER

POWER

POWER

ON RESET

ON RESET

ON RESET

ON RESET

interchangeably

potentiometer are used interchangeably.

8

CONTROL

CONTROL

COMMAND DECODE LOGIC

COMMAND DECODE LOGIC

ADDRESS DECODE LOGIC

ADDRESS DECODE LOGIC

CONTROL LOGIC

CONTROL LOGIC

RDAC0

RDAC0

RDAC0

RDAC0

REGISTER

REGISTER

REGISTER

REGISTER

RDAC1

RDAC1

RDAC1

RDAC1

REGISTER

REGISTER

REGISTER

REGISTER

RDAC2

RDAC2

RDAC2

RDAC2

REGISTER

REGISTER

REGISTER

REGISTER

RDAC0

RDAC0

RDAC0

9 bit

9 bit

9 bit

RDAC1

RDAC1

RDAC1

9 bit

9 bit

9 bit

RDAC2

RDAC2

RDAC2

7 bit

7 bit

7 bit

A0

A0

A0

W0

W0

W0

B0

B0

B0

A1

A1

A1

W1

W1

W1

B1

B1

B1

A2

A2

A2

W2

W2

W2

B2

B2

B2

REV. PrD Page 1 of 15

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

Preliminary Technical Data ADN2860

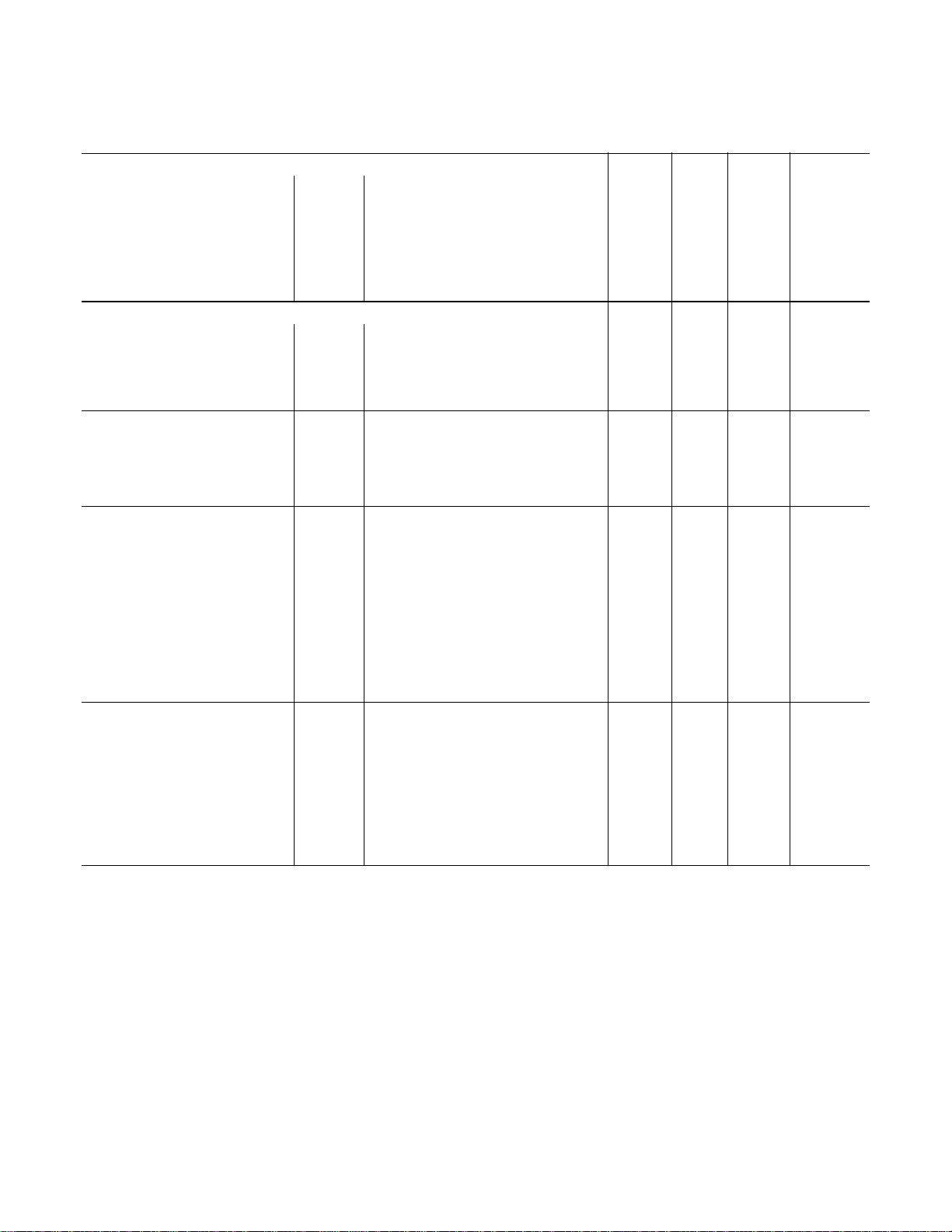

ADN2860 ELECTRICAL CHARACTERISTICS 25k, 250k VERSIONS

( V

= 3V to 5.5V and –40C <TA<+85C, unless otherwise noted)

DD

Parameter Symbol Conditions Min Typ

DC CHARACTERISTICS RHEOSTAT MODE (Specifications apply to all RDACs)

Resistor Differential Nonlinearity2 R-DNL RWB -2 +2 LSB

Resistor Integral Nonlinearity2 R-INL RWB -4 +4 LSB

Resistance Temperature Coefficent ∆RAB/∆T 35 ppm/°C

Wiper Resistance RW V

V

Channel Resistance Matching ∆RWB/RWB Ch 1 and 2 RWB, Dx = 3FFH 0.1 %

Nominal Resistor tolerance ∆RWB Dx = 3FFH -30 30 %

DC CHARACTERISTICS POTENTIOMETER DIVIDER MODE Specifications apply to all VRs

Differential Nonlinearity3 DNL –2 +2 LSB

Integral Nonlinearity3 INL –4 +4 LSB

Voltage Divider Temperature Coefficent ∆VW/∆T Code = Half-scale 15 ppm/°C

Full-Scale Error V

Zero-Scale Error V

Code = Full-scale -1.5 0 LSB

WFSE

Code = Zero-scale 0 +1.5 LSB

WZSE

RESISTOR TERMINALS

Terminal Voltage Range4 V

Capacitance5 Ax, Bx C

VSS V

A, B, W

f = 1 MHz, measured to GND, Code = Half-scale 11 pF

A,B

Capacitance5 Wx CW f = 1 MHz, measured to GND, Code = Half-scale 80 pF

Common-mode Leakage Current

5,6

I

V

CM

DIGITAL INPUTS & OUTPUTS

Input Logic High VIH with respect to GND, VDD = 5V 2.4 V

Input Logic Low VIL with respect to GND, VDD = 5V 0.8 V

Input Logic High VIH with respect to GND, VDD = 3V 2.1 V

Input Logic Low VIL with respect to GND, VDD = 3V 0.6 V

Input Logic High VIH with respect to GND, VDD = +2.5V, VSS=-2.5V 2.0 V

Input Logic Low VIL with respect to GND, VDD = +2.5V, VSS=-2.5V 0.5 V

Output Logic High (SDO, RDY) VOH R

Output Logic Low VOL I

Input Current IIL V

Input Capacitance5 C

5 pF

IL

POWER SUPPLIES

Single-Supply Power Range VDD V

Dual-Supply Power Range VDD/VSS ±2.25 ±2.75 V

Positive Supply Current IDD V

Positive Supply Current IDD V

Programming Mode Current I

VIH = VDD or VIL = GND 35 mA

DD(PG)

Negative Supply Current ISS V

Power Dissipation8 P

Power Supply Sensitivity5 P

V

DISS

∆VDD = +5V ±10% 0.002 0.01 %/%

SS

NOTES: See bottom of table next page.

= +5V, IW = 1V/RWB 70 100 Ω

DD

= +3V, IW = 1V/RWB 200 Ω

DD

= VDD/2 0.01 1 µA

W

= 2.2KΩ to +5V 4.9 V

PULL-UP

= 1.6mA, V

OL

= 0V or VDD ±5 µA

IN

= 0V 3.0 5.5 V

SS

= VDD or VIL = GND, TA=25oC 2 4.5 µA

IH

= VDD or VIL = GND 3.5 10 µA

IH

= VDD or VIL = GND, V

IH

= VDD or VIL = GND 18 50 µW

IH

= +5V 0.4 V

LOGIC

= 2.5V, V

DD

= -2.5V 3.5 10 µA

SS

1

Max Units

V

DD

Page 2 of 15

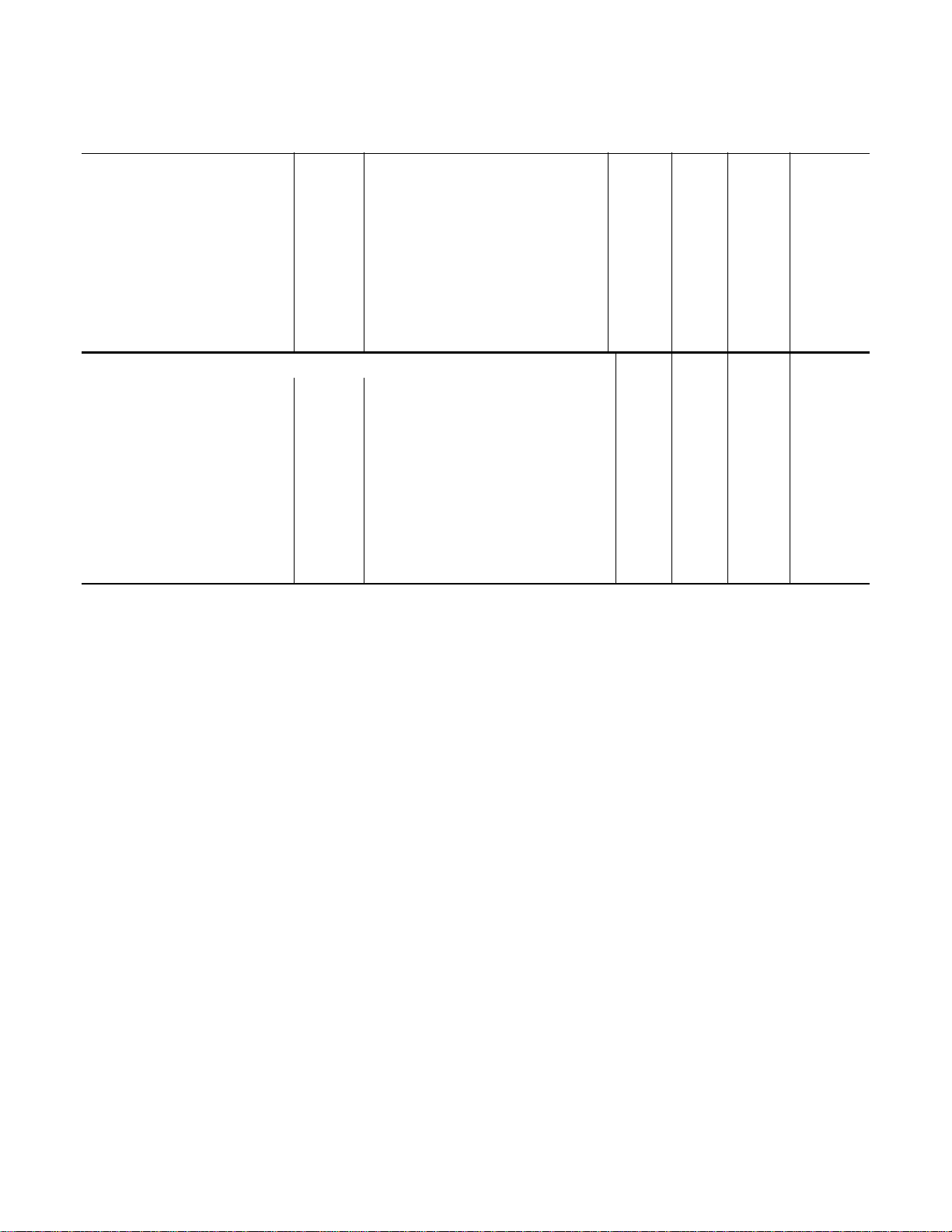

Preliminary Technical Data ADN2860

ADN2860 ELECTRICAL CHARACTERISTICS 25k, 250k VERSIONS

( V

= 3V to 5.5V and –40C <TA<+85C, unless otherwise noted)

DD

Parameter Symbol Conditions Min Typ1 Max Units

DYNAMIC CHARACTERISTICS

Bandwidth –3dB BW VDD/VSS = +/-2.5 V, RAB = 25 kΩ / 250 kΩ 125/12 kHz

Total Harmonic Distortion THDW V

VW Settling Time tS V

code 000H to 200H. RAB = 25 k/250 kΩ 4 / 36 µs

Resistor Noise Spectral Density e

Crosstalk (CW1/CW2) CT V

making full scale change, RAB = 25 k/250 kΩ 90/21 nV-s

Analog Crosstalk CTA V

V

Code 2 = 3FFH, RAB = 25 kΩ / 250 kΩ -81/-62 dB

INTERFACE TIMING CHARACTERISTICS applies to all parts(Notes 6,12)

SCL Clock Frequency f

t

Bus free time between STOP & START t

BUF

t

Hold Time (repeated START) t2 After this period the first clock pulse is generated 600 ns

HD;STA

t

Low Period of SCL Clock t3 1.3 µs

LOW

t

High Period of SCL Clock t4 0.6 50 µs

HIGH

t

Setup Time For START Condition t5 600 ns

SU;STA

t

Data Hold Time t6 900 ns

HD;DAT

t

Data Setup Time t7 100 ns

SU;DAT

tR Rise Time of both SDA & SCL signals t8 300 ns

tF Fall Time of both SDA & SCL signals t9 300 ns

t

Setup time for STOP Condition t10 600 ns

SU;STO

NOTES:

1. Typical represent average readings at +25°C, VDD = +5V.

2. Resistor position non-linearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the

relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See figure 20 test circuit.

3. INL and DNL are measured at V

DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions. See Figure 19 test circuit.

4. Resistor terminals A, B, W have no limitations on polarity with respect to each other.

5. Guaranteed by design and not subject to production test.

6. Bandwidth, noise and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value

results in the minimum overall power consumption.

7. P

8. All dynamic characteristics use V

9. See timing diagram for location of measured values.

10. Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117 and measured at –40 °C, +25°C and +85°C, typical endurance at 25°C is 700,000 cycles.

11. Retention lifetime equivalent at junction temperature (T

The ADN2860 contains 21,035 transistors. Die size: 88.2 mil x 87.0 mil, 7673 sq. mil.

Specifications Subject to Change without Notic

is calculated from (IDD x VDD). CMOS logic level inputs result in minimum power dissipation.

DISS

temperature.

5, 9

=1Vrms, VB = 0V, f=1 kHz 0.05 %

A

= VDD, VB=0V, VW=0.50% error band,

A

RAB = 25 kΩ / 250 kΩ, TA = 25oC 20 / 64 nV√Hz

N_WB

= VDD, VB = 0V, Measured VW1 with VW2

A

= VA1 = +2.5 V, VSS = VB1 = -2.5 V, Measure

DD

with V

W1

0 400 KHz

SCL

1.3 µs

1

with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0V.

W

= +5V.

DD

) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6eV will derate with junction

J

= 5V p-p @ f = 1kHz, Code1 = 200H,

W2

Page 3 of 15

Preliminary Technical Data ADN2860

Absolute Maximum Rating1 (T

= +25°C, unless

A

otherwise noted)

VDD to GND..........................................................-0.3 V, +7 V

VSS to GND ..........................................................+0.3 V, -7 V

VDD to VSS........................................................................+7 V

V

, VB, VW to GND.............................VSS-0.3 V, VDD+0.3 V

A

IA, IB, IW

2

Intermittent

.................................................±20 mA

Continuous..................................................... ±2 mA

Digital Inputs & Output Voltage to GND... -0.3 V, VDD+0.3 V

Operating Temperature Range3.......................-40°C to +85°C

Maximum Junction Temperature (T

Storage Temperature......................................-65°C to +150°C

Lead Temperature, Soldering

MAX

)...................+150°C

J

4

Vapor Phase (60 sec) .......................................+215 °C

Infrared (15 sec)...............................................+220 °C

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

ADN2860 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

Thermal Resistance Junction-to-Ambient θ

JA,

LFCSP-24................................................... TBD °C/W

θ

Thermal Resistance Junction-to-Case

JC,

LFCSP-24................................................... TBD °C/W

Package Power Dissipation = (T

MAX - TA) / θ

J

JA

NOTES

1. Stresses above those listed under Absolute Maximum Ratings may

cause permanent damage to the device. This is a stress rating; functional

operation of the device at these or any other conditions above those

listed in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods

may affect device reliability.

2. Maximum terminal current is bounded by the maximum current

handling of the switches, maximum power dissipation of the package,

and maximum applied voltage across any two of the B, and W terminals

at a given resistance.

3. Includes programming of Nonvolatile memory

Page 4 of 15

Preliminary Technical Data ADN2860

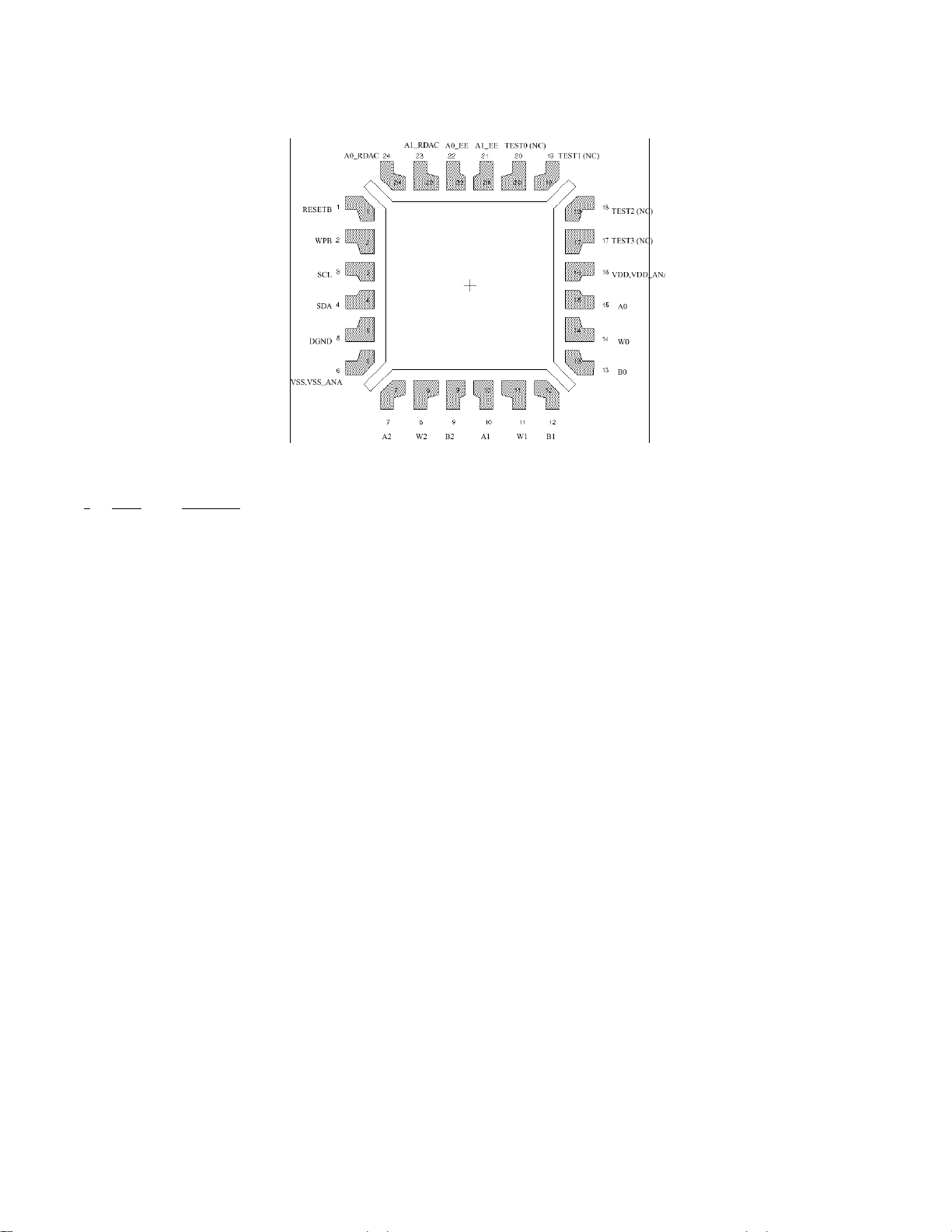

ADN2860ACP PIN CONFIGURATION

PIN DESCRIPTIONS

# Name Description

1 RESET Reset the scratch pad register with current contents of the EEMEM register. Factory defaults midscale before any programming

2 WP Write Protect Pin. When active low, WP prevents any changes to the present register contents, except PR and cmd 1 and 8 will refresh the

3 SCL Serial Input Register clock pin. Shifts in one bit at a time on positive clock edges.

4 SDA Serial Data Input Pin. Shifts in one bit at a time on positive clock CLK edges. MSB loaded first.

5 DGND Ground pin, logic ground reference

Negative Supply. Connect to zero volts for single supply applications.

6 V

SS

7 A2 A terminal of RDAC2.

8 W2 Wiper terminal of RDAC2

9 B2 B terminal of RDAC2.

10 A1 A terminal of RDAC1.

11 W1 Wiper terminal of RDAC1

12 B1 B terminal of RDAC1

13 A0 A terminal of RDAC0.

14 W0 Wiper terminal of RDAC0.

15 B0 B terminal of RDAC0

16 V

17 TEST3 Test pin 3 (Do Not Connect)

18 TEST2 Test pin 2 (Do Not Connect)

19 TEST1 Test pin 1 (Do Not Connect)

20 TEST0 Test pin 0 (Do Not Connect)

21 A1_EE I2C Device Address 1 for EEMEM

22 A0_EE I2C Device Address 0 for EEMEM

23 AD1 I2C Device Address 1 for RDAC

24 AD0 I2C Device Address 0 for RDAC

Positive Power Supply Pin.

DD

RDAC register from EEMEM. Execute a NOP instruction before returning to WP high.

Page 5 of 15

Loading...

Loading...