Analog Devices ADN2850ACP25-RL7, ADN2850ARU25-REEL7, ADN2850ARU25, ADN2850ACP250-RL7, ADN2850ACP250 Datasheet

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory, Dual 1024

a

Position Programmable Resistors

Preliminary Technical Data ADN2850

FEATURES

Dual, 1024 Position Resolution

25K, 250K Ohm Full Scale Resistance

Low Temperature Coefficient -- 35ppm/°C

Nonvolatile Memory

1

Preset Maintains Wiper Settings

Wiper Settings Read Back

Linear Increment/Decrement

Log taper Increment/Decrement

SPI Compatible Serial Interface

+3V to +5V Single Supply or ±2.5V Dual Supply

26 bytes User Nonvolatile Memory for Constant Storage with

Current Monitoring Configurable Function

APPLICATIONS

SONET, SDH, ATM, Gigabit Ethernet, DWDM Laser Diode

Driver Optical Supervisory Systems

GENERAL DESCRIPTION

The ADN2850 provides dual channel, digitally controlled

programmable resistors

devices perform the same electronic adjustment function as a

mechanical rheostat. The ADN2850’s versatile programming via a

standard serial interface allows sixteen mode of operations and

adjustment including scratch pad programming, memory storing

and retrieving, increment/decrement, log taper adjustment, wiper

setting readback, and extra user defined EEMEM.

In the scratch pad programming mode, a specific setting can be

programmed directly to the RDAC

resistance between terminals W-and-B. The RDAC register can

also be loaded with a value previously stored in the EEMEM

register. The value in the EEMEM can be changed or protected.

When changes are made to the RDAC register, t he value of the new

setting can be saved into the EEMEM. Thereafter, such value will

be transferred automatically to the RDAC register during system

power ON. It is enabled by the internal preset strobe. EEME M can

also be retrieved through direct programming and external preset

pin control.

Other key mode of operations include linear step increment and

decrement commands such that the setting in the RDAC register

can be moved UP or DOWN, on e st ep at a time. For logarithmic

changes in wiper setting, a left/right bit shift command adjusts the

level in ±6dB steps.

The ADN2850 is available in the 5mm x 5mm LFCSP-16 Lead

Frame Chip Scale and thin TSSOP-16 packages. All p arts are

guaranteed to operate over the extended industrial temperature

range of -40°C to +85°C.

2

with resolution of 1024 positions. These

2

register, which sets the

1

FUNCTIONAL BLOCK DIAGRAM

CS

CLK

SDI

SDO

RDY

V

V

GND

PR

WP

DD

SS

ADDRESS

DECODE

SERIAL

INPUT

REGISTER

PWR ON

PRESET

EEMEM

CONTROL

26 BYTES

USER EEMEM

100%

75%

50%

25%

RW B(D) [% of Full Scale RW B]

0%

0 256 512 768

Figure 1. RWB(D) vs Decimal Code

Notes:

1. The term nonvo latile memory and EEMEM a re used interchangebly

2. The term programmable resistor and RDAC are used interchangebly

RDAC1

REGISTER

EEMEM1

RDAC2

REGISTER

EEMEM2

D - C o d e in De c im al

RDAC1

RDAC1

CURRENT

MONITOR

I

1

I

2

1023

W1

W2

B1

B2

V

1

V

2

REV PrH, 13, AUG 2001

Information furnished by Analog Devices is believ ed to be accurate and reli able. However, no

responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or

other rights of third parties which may result fr om its us e. No lic ense is granted by im plic ation

or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106,

Tel: 617/329-4700 Fax:617/326-8703

Norwood, MA 02062-9106 U.S.A.

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Programmable Resistors

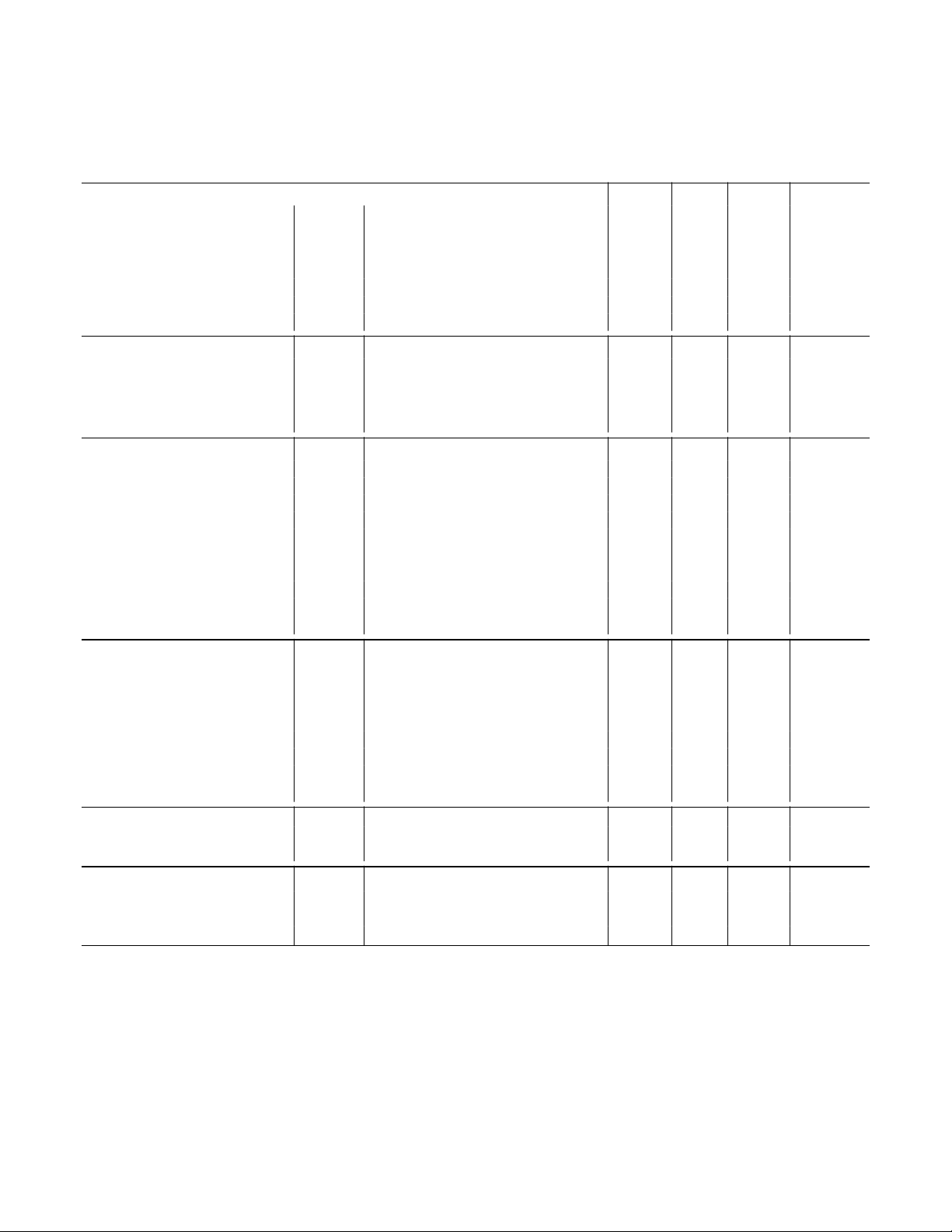

ELECTRICAL CHARACTERISTICS 25K , 250K OHM VERSIONS

-40°C < T

Parameter Symbol Conditions Min Typ

< +85°C unless otherwise noted12.)

A

(VDD = +3V to +5.5V and,

ADN2850

1

Max Units

DC CHARACTERISTICS RHEOSTAT MODE Specifications apply to all VRs

Resistor Differential Nonlinearity

Resistor Integral Nonlinearity

2

2

R-DNL R

R-INL R

WB

WB

-2 +2 LSB

-4 +4 LSB

Resistance Temperature Coefficent ∆RWB/∆T 35 ppm/°C

Wiper Resistance R

W

Channel Resistance Matching ∆RWB/R

Nominal Resistor t olerance ∆R

WB

VDD = +5V, IW = 1V/R

VDD = +3V, IW = 1V/R

Ch 1 and 2 RWB, Dx = 3FF

WB

Dx = 3FF

WB

WB

H

H

-30 30 %

50 100 Ω

200 Ω

0.2 %

RESISTOR TERMINALS

Terminal Voltage Range

Capacitance4 Bx C

Capacitance4 Wx C

Common-mode Leakage Current

3

5

V

W, B

B

W

I

CM

f = 1 MHz, measured to GND, Code = Half-scale 8 pF

f = 1 MHz, measured to GND, Code = Half-scale 80 pF

VW = VB = VDD/2 0.01 1 µA

V

SS

V

DD

DIGITAL INPUTS & OUTPUTS

Input Logic High V

Input Logic Low V

Input Logic High V

Input Logic Low V

Input Logic High V

Input Logic Low V

Output Logic High (SDO, RDY) V

Output Logic Low V

Input Current I

Input Capacitance

4

IH

IL

IH

IL

IH

IL

OH

OL

IL

C

IL

with respect to GND, VDD = 5V 2.4 V

with respect to GND, VDD = 5V 0.8 V

with respect to GND, VDD = 3V 2.1 V

with respect to GND, VDD = 3V 0.6 V

with respect to GND, VDD = +2.5V, VSS=-2.5V 2.0 V

with respect to GND, VDD = 5V, VSS=-2.5V 0.5 V

R

= 2.2KΩ to +5V 4.9 V

PULL-UP

IOL = 1.6mA, V

VIN = 0V or V

= +5V 0.4 V

LOGIC

DD

±1 µA

5pF

POWER SUPPLIES

Single-Supply Power Range V

DD

Dual-Supply Power Range VDD/V

Positive Supply Current I

Programming Mode Current I

Read Mode Current I

Negative Supply Current I

Power Dissipation

6

DD

DD(PG)

DD(READ)

SS

P

DISS

VSS = 0V 3.0 5.5 V

SS

±2.25 ±2.75 V

VIH = VDD or VIL = GND 2 20 µA

VIH = VDD or VIL = GND 35 mA

VIH = VDD or VIL = GND 3 mA

VIH = VDD or VIL = GND, V

= 2.5V, V

DD

= -2.5V 2 20 µA

SS

VIH = VDD or VIL = GND 6 110 µW

Power Supply Sensitivity PSS ∆VDD = +5V ±10% 0.002 0.01 %/%

CURRENT MONITOR Terminals

Current Sink at V

Current Sink at V

DYNAMIC CHARACTERISTICS

Resistor Noise Spectral Density e

7

1

2

4, 8

I

1

I

2

N_WB

0.0001 10 mA

10 mA

R

= 25KΩ / 250KΩ, TA = 25oC 20 / 64 nV√Hz

WB_FS

Analog Crosstalk (CW1/CW2)CTVB1 = VB2 = 0V, Measured VW1 with

V

= 100 mV p-p @ f = 100 kHz, Code

W2

1,2

= 200

H

-65 dB

NOTES: See bottom of table next page.

V

REV PrH, 13, AUG 2001 2

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Programmable Resistors

ELECTRICAL CHARACTERISTICS 25K , 250K OHM VERSIONS

-40°C < T

Parameter Symbol Conditions Min Typ

< +85°C unless otherwise noted12.)

A

(VDD = +3V to +5.5V and,

ADN2850

1

Max Units

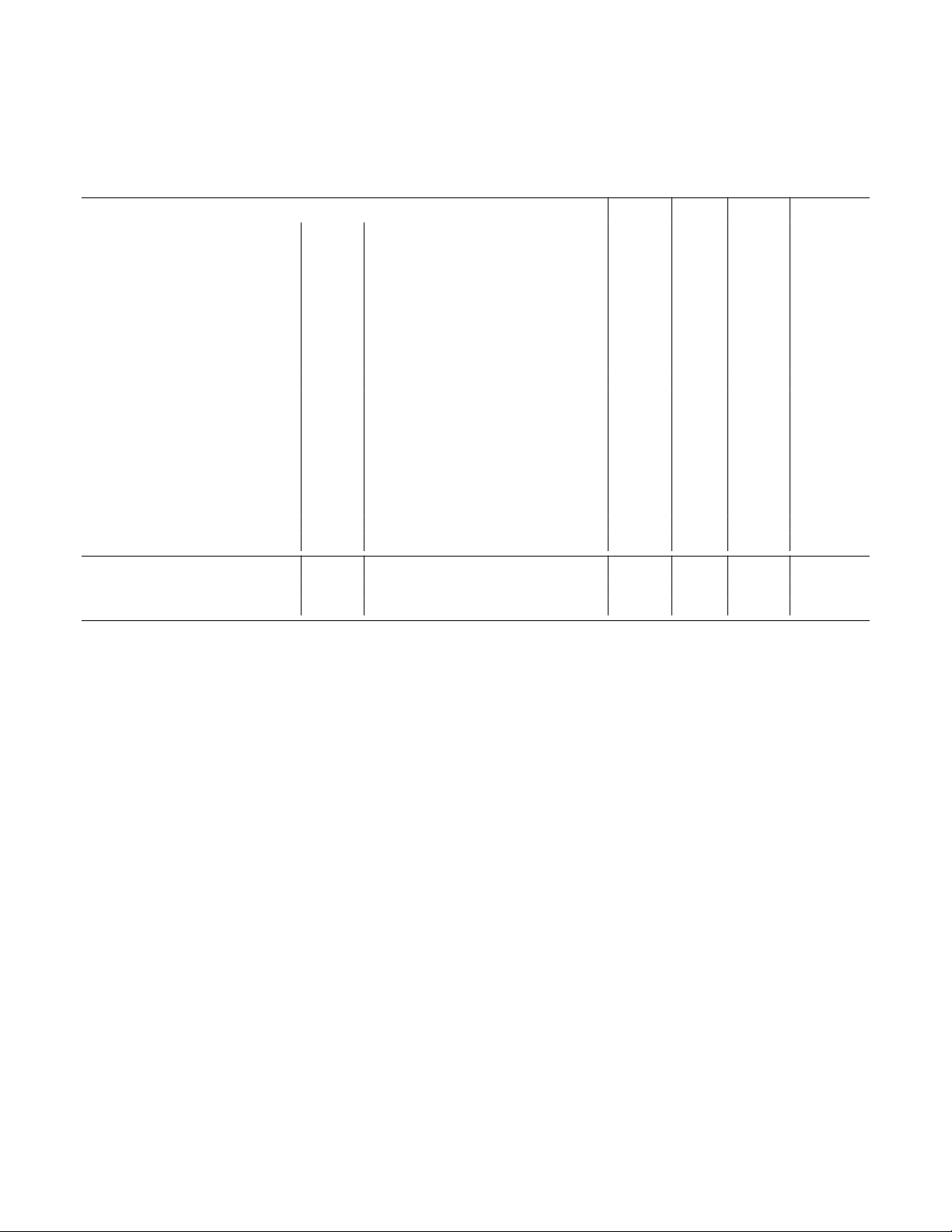

INTERFACE TIMING CHARACTERISTICS applies to all parts(Notes 4, 9)

Clock Cycle Time (t

CS Setup Time t

CLK Shutdown Time to CS rise t

)t

CYC

1

2

3

20 ns

10 ns

1t

CYC

Input Clock Pulse Width t 4 , t 5Clock level high or low 10 ns

Data Setup Time t

Data Hold Time t

CS to SDO - SPI line acquire t

CS to SDO - SPI line release t

CLK to SDO Propagation Delay

10

CLK to SDO Data Hold Time t

CS High Pulse Width t

CS High to CS High t

RDY Rise to CS Fall t

CS Rise to RDY fall time t

Read/Store to Nonvolatile EEMEM

11

CS Rise to Clock Edge Setup t

Preset Pulse Width (Asynchronous) t

Preset Response Time to RDY High t

FLASH/EE MEMORY RELIABILITY

13

6

7

8

9

t

10

11

12

13

14

15

t

16

17

PRW

PRESP

From Positive CLK transition 5 ns

From Positive CLK transition 5 ns

640 ns

34 100 ns

RP = 2.2KΩ, CL < 20pF 34 100 ns

RP = 2.2KΩ, CL < 20pF 0 ns

10 ns

4t

CYC

01 µs

0.11 ms

Applies to Command 2H, 3H, 9

H

25 ms

10 ns

Not shown in timing diagram 50 ns

PR pulsed low to refreshed wiper positions 70 us

Endurance 100,000 Cycles

Data Retention

14

100 Years

NOTES:

1. Typicals represent average readings at +25°C and VDD = +5V.

2. Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the

relative step change from ideal between successive tap positions. I

3. Resistor terminals W,B have no limitations on polarity with respect to each other.

4. Guaranteed by design and not subject to production test.

5. Common mode leakage current is a measure of the DC leakage from any terminal B and W to a common mode bias level of V

6. P

7. Applies to Photo Diode of Optical Receiver.

8. All dynamic characteristics use V

9. See timing diagram for location of measured values. All input control voltages are specified with t

10. Propagation delay depends on value of V

11. RDY pin low only for commands 2, 3, 8, 9, 10, and PR hardware pulse: CMD_8 ~ 1ms; CMD_9,10 ~0.1ms; CMD_2,3 ~20ms. Device operation at T

12. Parts can be operated at +2.7V single supply, except from 0

13. The ADN2850 contains 16,000 transistors. Die size: 100 mil x 150 mil, 10,500 sq. mil.

14. Retention lifetime equivalent at junction temperature (T

Specifications Subject to Change without Notice

is calculated from (IDD x VDD) + (ISS x VSS)

DISS

= +5V and V

DD

are measured using both V

to 35ms.

temperature as shown in Figure xxx in the Flash/EE Memory description sect ion of this data sheet.

= +3V and +5V.

DD

= 0V

SS

, R

, and CL see applications text.

DD

PULL_UP

) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6eV will derate with junction

J

~ 50uA for VDD= +2.7V and IW ~ 400uA for VDD=+5V. See test circuit f igure xxxx

W

/ 2.

DD

=2.5ns(10% to 90% of 3V) and timed from a voltage level of 1.5V. Switching characteristics

R=tF

o

C to –40oC where minimum +3V is needed

=-40oC & VDD<+3V extends the save time

A

REV PrH, 13, AUG 2001 3

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Programmable Resistors

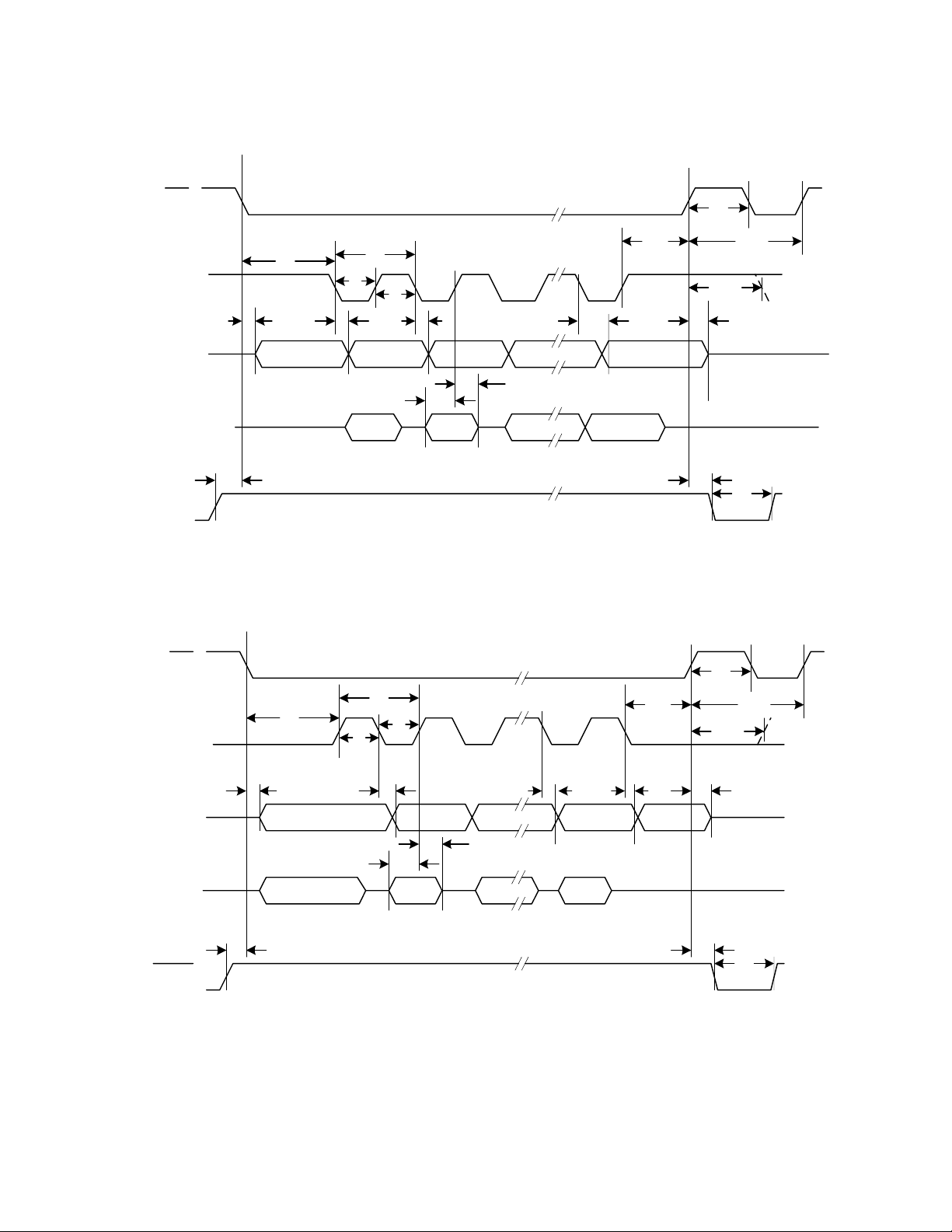

Timing Diagram

CPHA = 1

CS

t

t

1

t

5

t

4

t

10

MSB LSB OUT

t

7

t

6

MSB LSB

CLK

CPOL=1

SDO

SDI

t

2

t

t

8

10

*

t

14

RDY

Note: Not d efined, but normally LS B of character prev iously transmitted

*

* Note: Not defined, but normally LSB of character previously transmitted. The CPOL=1 micro

To be fully compliant the CPHA=1, CPOL=1 mode should be used when shifting more

controller command aligns the incoming data to the positive edge of the clock.

than 8-bits to gether as the

of a serial command will not take place until

controller command aligns the incoming data to the positive edge of the clock .

line can remain low (useful for daisy chaining). Processing

CS

returns high. The CPOL = 0 micro

CS

Figure 2A. CPHA=1 Timing Diagram

CPHA = 0

CS

t

1

t

5

t

4

CLK

CPOL=0

t

2

t

11

3

t

9

t

15

t

3

ADN2850

t

12

t

13

t

17

t

16

t

12

t

13

t

17

SDO

SDI

t

8

MSB OUT LSB

MSB IN LSB

t

14

t

10

t

7

t

6

RDY

Note: Not defined, but normally MSB of character just received

*

* Note: Not defined, but normally MSB of character just received. The CPOL=0 micro controller

can remain low for the CPHA=0, CPOL=0 mode between multiple bytes;

CS

command aligns the incoming data to the positive edge of the clock.

however this is not strictly SPI compliant. The CPOL = 0 micro controller

command aligns t he incoming data to the pos itive edge of the clock .

Figure 2B. CPHA=0 Timing Diagram

REV PrH, 13, AUG 2001 4

t

11

t

11

t

9

*

t

15

t

16

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Programmable Resistors

Absolute Maximum Rating1 (

TA = +25°C, unless

otherwise noted)

to GND............................................................-0.3V, +7V

V

DD

to GND ............................................................+0.3V, -7V

V

SS

to VSS.........................................................................+7V

V

DD

V

, VW to GND..................................... VSS-0.3V, VDD+0.3V

B

– WX.......................................................................±20mA

B

X

Intermittent2..................................................±20mA

Continuous...................................................±1.3mA

Digital Inputs & Output Voltage to GND.....-0.3V, V

Operating Temperature Range

Maximum Junction Temperature (T

Storage Temperature......................................-65°C to +150°C

Lead Temperature, Soldering

3

........................-40°C to +85°C

)...................+150°C

MAX

J

4

DD

+0.3V

Vapor Phase (60 sec).......................................+215 °C

Infrared (15 sec)...............................................+220 °C

Thermal Resistance Junction-to-Ambient

θ

JA,

LFCSP-16........................................................35°C/W

TSSOP-16 ..................................................... 150°C/W

Thermal Resistance Junction-to-Case

LFCSP-16............................................................. TBD

TSSOP-16 ....................................................... 28°C/W

Package Power Dissipation = (TJMAX - TA) / θ

NOTES

1. Stresses above those listed under Absolute Maximum Ratings may

cause permanent damage to the device. This is a stress rating; functional

operation of t he device at these or any other conditions above those

listed in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods

may affect device reliability.

2. Maximum terminal current is bounded by the maximum current

handling of the switches, maximum power dissipation of the package,

and maximum applied voltage across any two of the B, and W termi nals

at a given resistance.

3. Includes programming of Nonvolatile memory

4. Applicable to TSSOP-16 only. For LFCSP-16, please consult factory

for detail

ADN2850

θ

JC,

JA

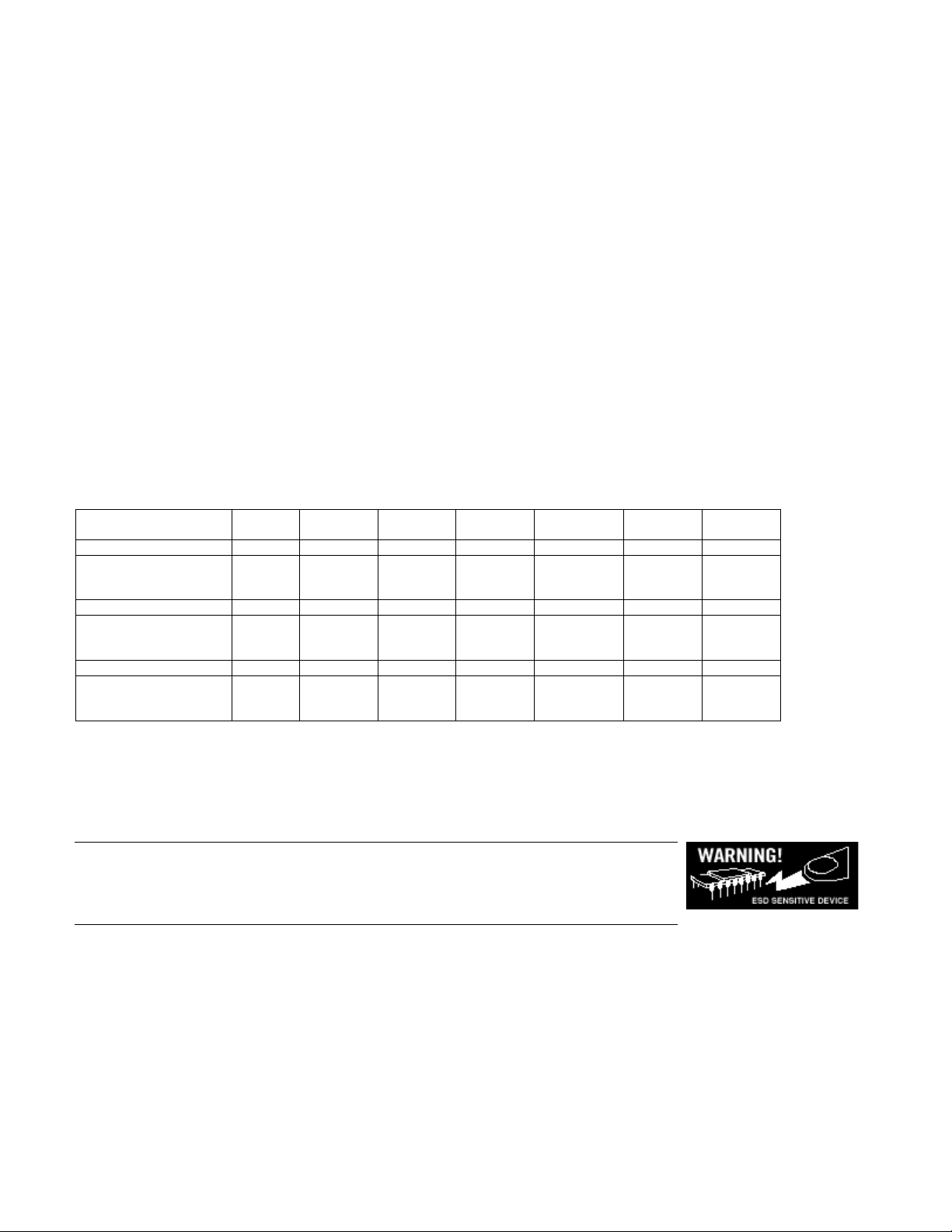

Ordering Guide

Model R

ADN2850ACP25 25 ±2 ±4 -40/+85°C LFCSP-16 CP-16 ACP25

ADN2850ACP25-RL7 25 ±2 ±4 -40/+85°C LFCSP-16

ADN2850ACP250 250 ±2 ±4 -40/+85°C LFCSP-16 CP-16 ACP250

ADN2850ACP250-RL7 250 ±2 ±4 -40/+85°C LFCSP-16

ADN2850ARU25 25 ±2 ±4 -40/+85°C TSSOP-16 RU-16 ARU25

ADN2850ARU25-REEL7 25 ±2 ±4 -40/+85°C TSSOP-16

* Line 1 contains ADI logo symbol and date code YYWW, line 2 contains product number ADN2850, line 3 branding containing differentiating detail by part type, line

4 contains lot number.

WB

(k Ohm)

RDNL

(LSB)

RINL

(LSB)

Temp

Range

Package

Description

1500 Pieces

7” Reel

1500 Pieces

7” Reel

1000 Pieces

7” Reel

Package

Option

CP-16 ACP25

CP-16 ACP250

RU-16 ARU25

Top Mark*

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

ADN2850 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high-energy electrostatic discharges. Therefore, p r oper ESD precaution s are recommended

to avoid performance degradation or loss of functionality.

REV PrH, 13, AUG 2001 5

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Programmable Resistors

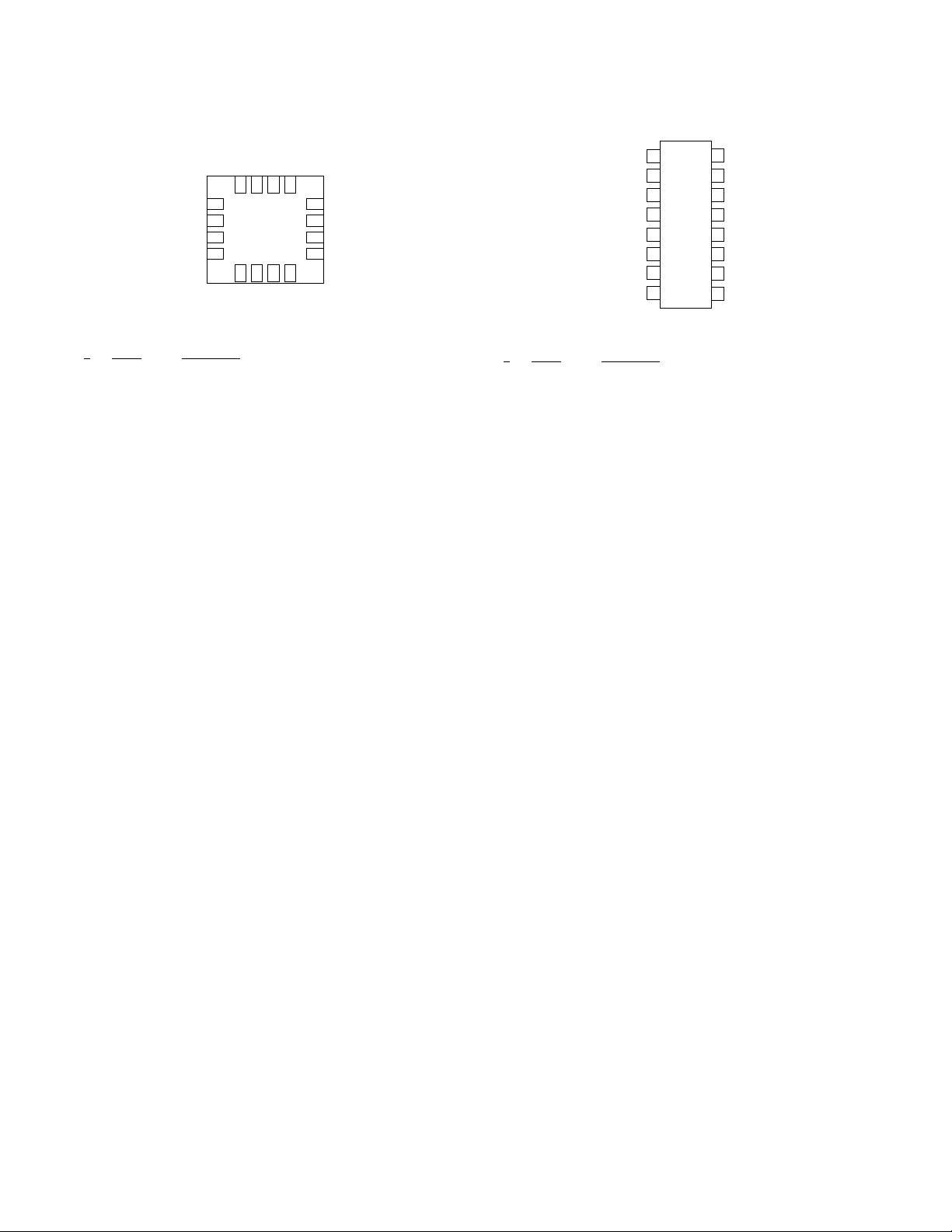

ADN2850ACP PIN CONFIGURATION

CS

PR

12

WP

11

V

DD

10

V

2

9

SDO

GND

V

V

SS

1

SDI CLK RDY

16 15 14 13

1

2

3

4

5678

W1 B1 B2 W2

ADN2850ACP PIN DESCRIPTION

#Name Description

1 SDO Serial Data Output Pin. Open Drain Output requires

2 GND Ground pin, logic ground reference

3V

4V

SS

1

5 W1 Wiper terminal of RDAC1 . ADDR(RDAC1) = 0

6 B1 B terminal of RDAC1

7 B2 B terminal of RDAC2.

8 W2 Wiper terminal of RDAC2 . ADDR(RDAC2) = 1

9V

10 V

2

DD

11 WP Write Protect Pin. When active low, WP prevents

12 PR Hardware over ride preset pin. Refreshes the scratch

13 CS Serial Register chip select active low. Serial register

14 RDY Ready. Active-high open drain output. Identifies

15 CLK Serial Input Register clock pin. Shifts in one bit at a

16 SDI Serial Data Input Pin. Shifts in one bit at a time on

external pull-up resistor. Commands 9 and 10

activate the SDO output. See Instr uction operation

Truth Table. Table 2. Other commands shift out the

previously loaded SDI bit pattern delayed by 24

clock pulses. This allows daisy-chain operation of

multiple packages.

Negative Supply. Connect to zero volts for single

supply applications.

Log Output Voltage 1 generated from internal diode

configured transistor

H

H

Log Output Voltage 2 generated from internal diode

configured transistor

Positive Power Supply Pin.

any changes to the pres ent register contents, except

PR and cmd 1 and 8 will refresh the RDAC register

from EEMEM.

pad register with current contents of the EEMEM

register. Factory default loads midscale 512

10

until

EEMEM loaded with a new value by the user (PR is

activated at the logic high transition).

operation takes place when CS returns to logic h igh.

completion of commands 2, 3, 8, 9, 10, and PR.

time on positive clock edges.

positive clock CLK edges. MSB loaded firs t.

ADN2850ARU PIN DESCRIPTION

#Name Description

1 CLK Serial Input Register clock pin. Shifts in one bit at a

2 SDI Serial Data Input Pin. Shifts in one bit at a time on

3 SDO Serial Data Output Pin. Open Drain Output requires

4 GND Ground pin, logic ground reference

.

.

5V

6V

7 W1 Wiper terminal of RDAC1. ADDR(RDAC1) = 0

8 B1 B terminal of RDAC1

9 B2 B terminal of RDAC2.

10 W2 Wiper terminal of RDAC2. ADDR(RDAC2) = 1

11 V

12 V

13 WP Write Protect Pin. When active low, WP prevents

14 PR Hardware over ride preset pin. Refreshes the sc ratch

15 CS Serial Register chip select active low. Serial register

16 RDY Ready. Active-high open drain output. Identifies

ADN2850ARU PIN CONFIGURATION

1

CLK

2

SDI

SDO

3

4

GND

V

5

SS

V

6

1

7

W1

B1

8

time on positive clock edges.

positive clock CLK edges. MSB loaded first.

external pull-up resistor. Commands 9 and 10

activate the SDO output. See Instr uction operation

Truth Table. Table 2. Other commands shift out the

previously loaded SDI bit pattern delayed by 24

clock pulses. This allows daisy-chain operation of

multiple packages

SS

1

2

DD

Negative Supply. Connect to zero volts for single

supply applications.

Log Output Voltage 1 generated from internal diode

configured transistor

Log Output Voltage 2 generated from internal diode

configured transistor

Positive Power Supply Pin.

any chan ges to the pres ent contents except PR and

cmd 1 and 8 will refresh the RDAC register from

E2MEM.

pad register with current contents of the EEMEM

register. Factory default loads midscale 512

EEMEM loaded with a new value by the user (PR is

activated at the logic high transition).

operation takes place when CS returns to logic h igh.

completion of commands 2, 3, 8, 9, 10, and PR.

ADN2850

16

RDY

CS

CS

CSCS

15

PR

PR

PRPR

14

WP

WP

WPWP

13

V

12

DD

V

11

2

W2

10

B2

9

until

10

.

H

.

H

REV PrH, 13, AUG 2001 6

Loading...

Loading...