Page 1

10.7 Gbps Electro-Absorption Modulator Driver

Preliminary Technical Data

FEATURES

Data Rates up to 10.709Gb/s

Typical Rise/Fall Time 27ps

Power Dissipation 900mW (at 2V swing, 1V offset)

Programmable Modulation Voltage up to 3V

Programmable Bias Offset Voltage up to 2V

Voltage-input control for offset, modulation

Cross Point Adjust Range 30%- 85%

Selectable Data Retiming

PECL/CML Data & Clock Inputs

50Ω on Chip Data & Clock Terminations

Modulation Ebnable/Disable

|<-10dB , |S22|<-8dB at 10GHz

|S

11

Positive or negative 5.2 or 5.0V single supply operation

Available in dice and 4x4mm 24 Lead LFCSP package

APPLICATIONS

SONET OC-192 Optical Transmitters

SDH STM-64 Optical Transmitters

10Gb Ethernet IEEE802.3

XFP/X2/XENPACK/MSA-300 Optical Modules

PRODUCT DESCRIPTION

The ADN2849 is a low power 10.7Gbps driver for electroabsorption modulator (EAM) applications. The modulation

voltage is programmable via an external voltage up to a

maximum swing of 3V when driving 50Ω. The bias offset

voltage and output eye cross point are also programmable. Onchip 50Ω resistor is provided for back termination of the

output. The ADN2849 is driven by AC coupled differential

CML level data and has selectable data retiming to remove jitter

from data input signal. The modulation voltage can be enabled

or disabled by driving the MOD_ENB pin with the proper logic

levels. It can operate with positive or negative (5.2V or 5.0V)

supply voltage.

The ADN284949 is available in a compact 4x4mm plastic

package or dice format.

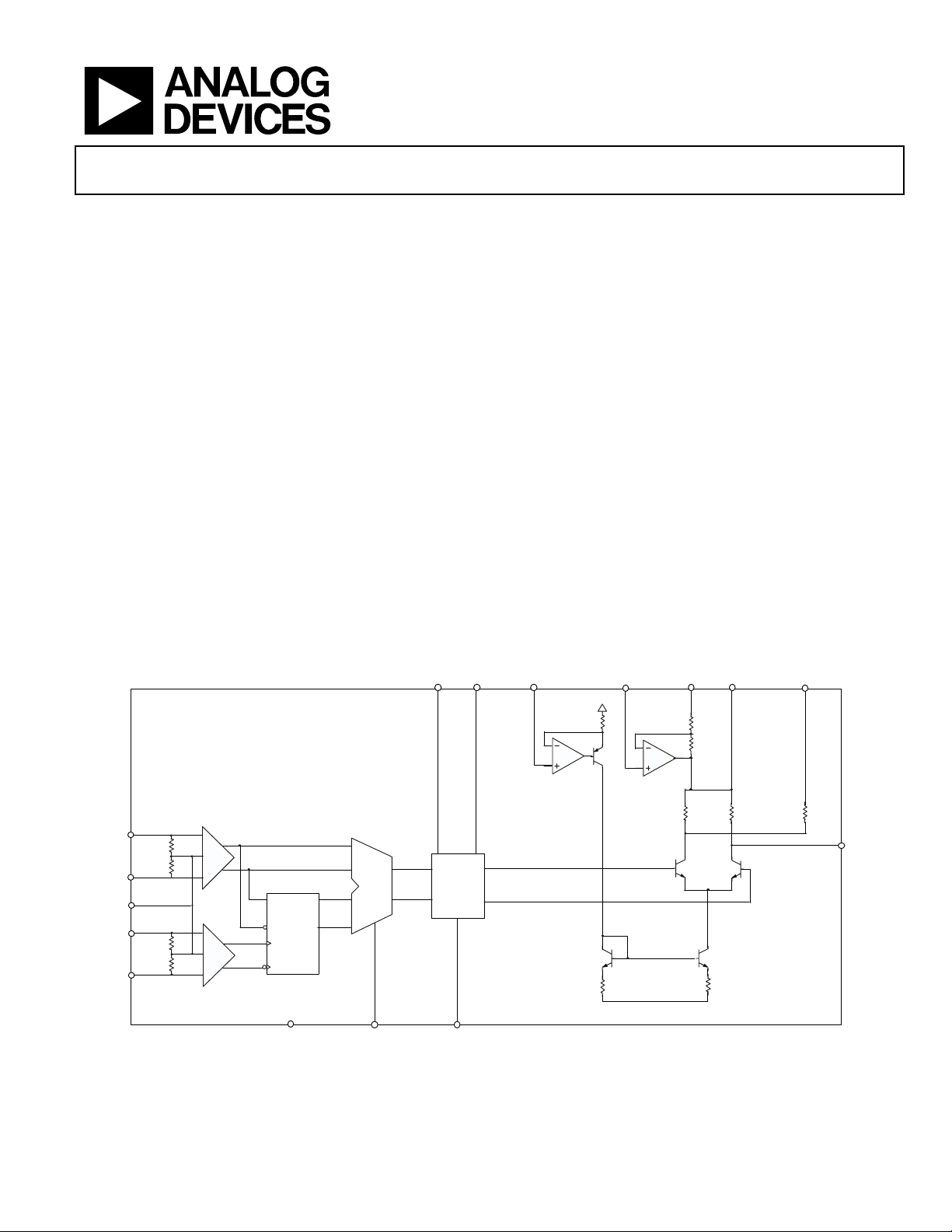

CPAP CPAN MOD_SET

BIAS_SET VTERM

GND MODN_TERM

ADN2849

ADN2849

DATAP

DAT AN

VBB

CLKP

CLKN

Rev. Pr. G August 2004

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective owners.

50

Ω

50

Ω

MUX

D

Q

50

Ω

50

Ω

VEE

CLK_SELB MOD_ENB

CROSS

POINT

ADJUST

Figure 1. Functional Block Diagram

GND

R

R

50

Ω

VEE

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

MODP

Page 2

ADN2849

Preliminary Technical Data

Specifications

(Electrical Specifications (VEE=VEE

0

specified at 25

Table 1.

C)

MIN

to VEE

. All specifications T

MAX

min

to T

, ZL=50Ω unless otherwise noted. Typical values

max

Parameter Min Typ Max Unit Conditions

Bias Offset Voltage(MODP)

Bias offset voltage -0.25 -2.0 V Note 1

BIAS_SET voltage to bias offset voltage gain 0.9 1.1 V/V Ta=250C, VEE=-5.2V

Bias offset voltage drift over temperature and VEE -5 5 %

Modulation Voltage(MODP)

Modulation voltage swing 0.6 3.0 V Note1

MOD_SET voltage to modulation voltage swing gain 1.5 1.9 V/v Ta=250C, VEE=-5.2V

Modulation voltage drift over temperature and VEE -5 5 %

Back termination resistance 40 60

Ω

Rise time (20% - 80%) 27 36 ps

Fall time (20% - 80%) 27 36 ps

Random jitter 0.75 ps RMS

Total jitter 10 ps

p-p

Cross point adjust range 30 85 %

Cross point drift over temperature and VEE -5 5 %

Minimum output voltage(single ended) VEE+1.7 V Note1

|S22|

-8 dB At 10GHz

Modulation enable time 100 ns

Modulation disable time 100 ns

Data Inputs (DATAP, DATAN)

Differential Input voltage 600 1600 mV

Termination resistance 40 60

p-p

Ω

Setup time (see figure 2) 25 ps CLK_SELB=’0’

Hold time (see figure 2) 25 ps CLK_SELB=’0’

|S11| -10 DB At 10GHz

Clock Inputs (CLKP, CLKN)

Differential Input voltage 600 1600 mV

Termination resistance 40 60

p-p

Ω

|S11| -10 dB At 10GHz

Cross point adjust (CPAN, CPAP)

Input voltage range -0.85 -1.85 V

CPAP, CPAN differential voltage 0.6 V

Input current 85 115

Logic Inputs (MOD_ENB, CLK_SELB)

V

IH

V

IL

I

IL

I

IH

VEE+2 V

VEE+0.8 V

-400

20

200

Supply

p-p

µA

µA

µA

µA

VI=VEE+0.4V

VI=VEE+2.4V

VI=0V

VEE -4.75 -5.2 -5.5 V IMOD=0

I

EE

Notes:

Minimum supply voltage and minimum output voltage determine maximum output swing and maximum bias offset that can be achieved concurrently.

Measured using the characterization circuit shown in figure 3.

52 mA V

MODP/MODN

=0

Rev. Pr. G | Page 2 of 17

Page 3

Preliminary Technical Data

ADN2849

SETUP HOLD

t

S

t

H

DATAP/N

CLKP/N

Figure 2. Setup and hold time

Figure 3. High-speed characterization circuit

Rev. Pr. G | Page 3 of 17

Page 4

ADN2849

Preliminary Technical Data

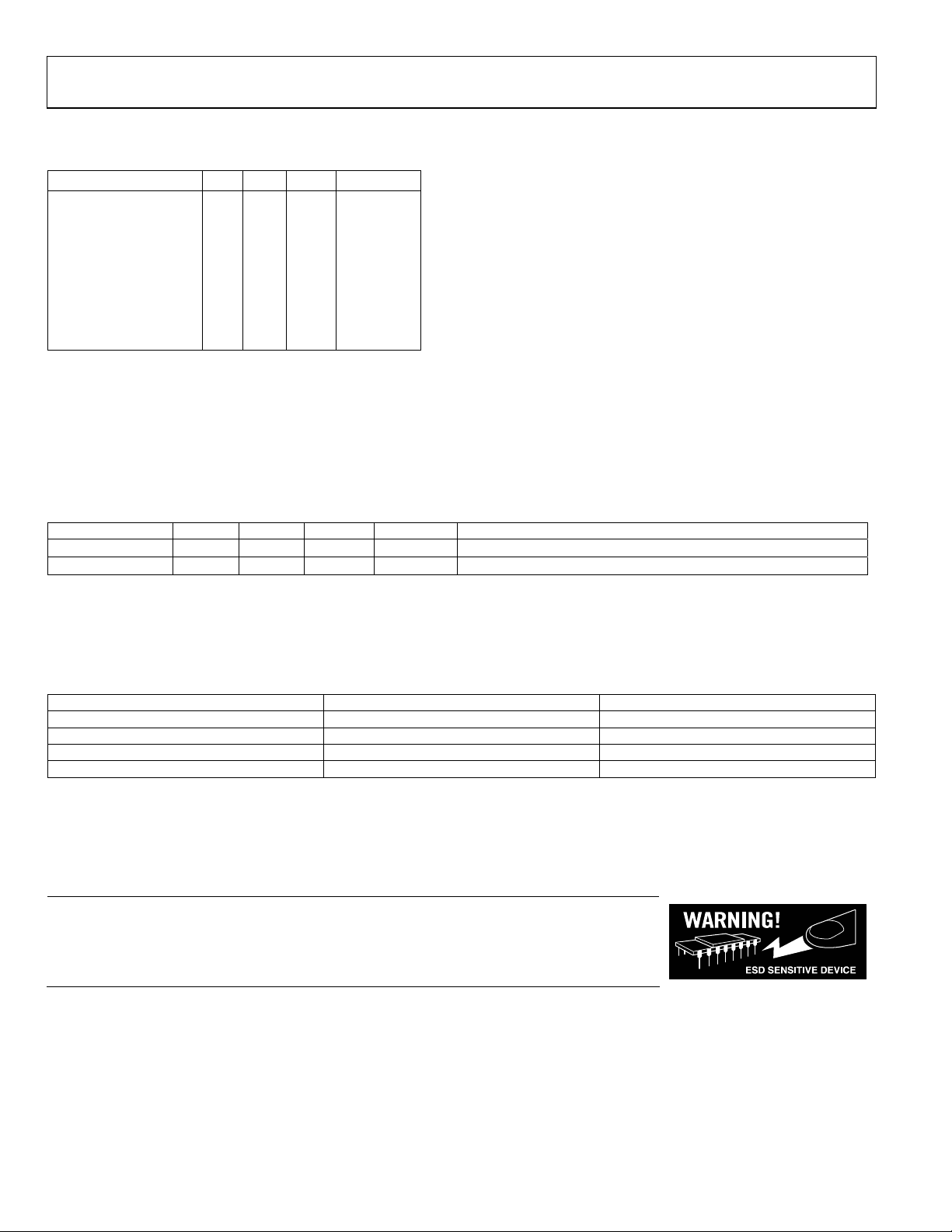

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Min Max Units Conditions

VEE to GND TBD TBD V

VBB to GND TBD TBD V

DATAP, DATAN to GND TBD TBD V

CLKP, CLKN to GND TBD TBD V

CPAP, CPAN to GND TBD TBD V

MOD_SET to GND TBD TBD V

BIAS_SET to GND TBD TBD V

MOD_ENB to GND TBD TBD V

CLK_SELB to GND TBD TBD V

Staorage temperature range -60 +150 0C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only;

functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

PACKAGE THERMAL SPECIFICATIONS

Table 3.

PARAMETER MIN TYP MAX UNITS CONDITIONS/COMMENTS

θ

θ

J-TOP

J-PAD

TBD TBD TBD 0C/W Thermal resistance from junction to top of package

TBD TBD TBD 0C/W

Thermal resistance from junction to bottom of exposed pad

ORDERING GUIDE

Table 4.

Model Temperature range Package description

ADN2849ACP -400C to +850C 24 Lead LFCSP

ADN2849ACP-RL -400C to +850C 24 Lead LFCSP

ADN2849ACP-RL7 -400C to +850C 24 Lead LFCSP

ADN2849SURF -400C to +850C Bare die

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

this product features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

Rev. Pr. G | Page 4 of 17

Page 5

Preliminary Technical Data

TYPICAL PERFORMANCE CHARACTERISTICS (TA=250C, VEE=-5.2V)

000

000

ADN2849

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 000 000 000 000 000

TBD

ALL CAPS (Initial cap)

Figure 4. Rise time vs. Swing

000

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

TBD

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 000 000 000 000 000

TBD

ALL CAPS (Initial cap)

Figure 7. Total jitter vs. Swing

000

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

TBD

000

000 000 000 000 000 000

ALL CAPS (Initial cap)

Figure 5. Fall time vs. Swing

000

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 000 000 000 000 000

TBD

ALL CAPS (Initial cap)

Figure 6. Random jitter vs. Swing

000

000 000 000 000 000 000

ALL CAPS (Initial cap)

Figure 8. Cross point vs. differential voltage at CPAP/CPAN pins

000

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 000 000 000 000 000

Figure 9. Differential S11 vs. frequency

TBD

ALL CAPS (Initial cap)

Rev. Pr. G | Page 5 of 17

Page 6

ADN2849

Preliminary Technical Data

000

000

000

)

p

a

c

l

000

a

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 000 000 000 000 000

TBD

ALL CAPS (Initial cap)

Figure 10. Single-ended S22 vs. frequency

000

000

)

p

a

c

l

000

a

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

TBD

000

)

p

a

c

l

000

a

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 00 0 000 000 000 000

TBD

ALL CAPS (Initial cap)

Figure 13. Electrical eye diagram

(2.5V swing, 0.5V offset, PRBS31 at 10.7Gbps)

000

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

TBD

000

000 000 000 000 000 000

ALL CAPS (Initial cap)

Figure 21. Total supply current vs. Swing with retiming disabled

000

000

)

p

a

c

l

a

000

i

t

i

n

I

(

S

P

A

000

C

L

L

A

000

000

000 000 000 000 000 000

TBD

ALL CAPS (Initial cap)

Figure 12. Total supply current vs. Swing with retiming enabled

000

000 000 000 000 000 000

Figure 14. Optical eye diagram using the FLD5F20NP EML

ALL CAPS (Initial cap)

(Pav=0dBm, ER=10dB, PRBS31 pattern at 9.95328Gbps, SONET

OC192 mask test)

Rev. Pr. G | Page 6 of 17

Page 7

Preliminary Technical Data

PIN CONFIGURATION AND FUNCTION DESCRIPTION

T

E

N

A

P

C

S

A

P

C

E

A

E

I

V

B

S

_

P

M

R

D

E

N

T

G

V

ADN2849

GND

DATAP

DAT AN

VBB

CLKP

CLKN

1

ADN2849

B

B

L

N

E

E

_

S

_

D

K

O

L

M

C

T

E

S

_

D

O

M

D

D

N

N

G

G

E

E

V

VTERM

GND

MODP

MODN_TERM

GND

VEE

Figure 15. Pin configuration

Note: There is a n exposed pad on the bottom of the package that must be connected to the most negative supply rail of the ADN2849

Table 5.

Pin number Mnemonic Description

1, 10, 11, 14,17, 20 GND Positive power supply

2 DATAP AC coupled CML data, positive differential terminal

3 DATAN AC coupled CML data, negative differential terminal

4 VBB CML termination resistor

5 CLKP AC coupled CML clock, positive differential terminal

6 CLKN AC coupled CML clock, negative differential terminal

7 MOD_ENB Modulation enable logic input

8 CLK_SELB Retiming select logic input

9 MOD_SET Modulation voltage set input

12, 13, 21 VEE Negative power supply

15 MODN_TERM Termination resistor for MODN

16 MODP Positive modulation voltage output

18, 19 VTERM Back termination voltage output

22 BIAS_SET Bias offset voltage set input

23 CPAP Cross point adjust positive control input

24 CPAN Cross point adjust negative control input

Exposed Pad Pad Connect to the most negative supply rail of the ADN2849

Rev. Pr. G | Page 7 of 17

Page 8

ADN2849

Preliminary Technical Data

PAD CONFIGURATION AND FUNCTION DESCRIPTION

1919202122232425

1

2

3

4

4

5

6

26 7 8 9 10 11 12 27

(Die size 2.05×2.05mm, single bond pad size 84×84µm with 76×76µm glass opening, double bond pad size 184×84µmwith 176×76µm)

Notes:

1. The metallization photograph and the die pad coordinates appear at the end of this document.

2.The pads that have the same number must be bonded together.

3. The back side of the die must be connected to the most negative supply rail of the ADN2849

ADN2849

Figure 16. Pad configuration

18

17

16

15

14

13

Table 6.

Pad number Mnemonic Description

1, 10, 11, 14,17, 20, 25, 26, 27 GND Positive power supply

2 DATAP AC coupled CML data, positive differential terminal

3 DATAN AC coupled CML data, negative differential terminal

4 VBB CML termination resistor

5 CLKP AC coupled CML clock, positive differential terminal

6 CLKN AC coupled CML clock, negative differential terminal

7 MOD_ENB Modulation enable logic input

8 CLK_SELB Retiming select logic input

9 MOD_SET Modulation voltage set input

12, 13, 21 VEE Negative power supply

15 MODN_TERM Termination resistor for MODN

16 MODP Positive modulation voltage output

18, 19 VTERM Back termination voltage output

22 BIAS_SET Bias offset voltage set input

23 CPAP Cross point adjust positive control input

24 CPAN Cross point adjust negative control input

Rev. Pr. G | Page 8 of 17

Page 9

Preliminary Technical Data

N

THEORY OF OPERATION

GENERAL

Figure 17 shows a typical EA modulator characteristic. Vm

represents the voltage across the modulator and Pout represents

the optical output power. For small voltages across the

modulator it is in its high transmission state. As the voltage

becomes more negative, the modulator becomes less

transparent to the laser light. Fig. 17 also shows a typical drive

signal for an EA modulator. It consists of a modulation signal

with a swing Vs, and a bias offset voltage Vb

DATAP/CLKP

DATAN/CLKN

VEE

G

GND

ADN2849

D

VEE

Pout

Vm

Vb

Vs

Figure 17. Typical transfer function of an EA modulator

As shown in the functional block diagram (figure 1), the

ADN2849 consists of an input stage for data signals, a cross

point adjust block and the output stage that generates the bias

offset and modulation voltages. The retiming option allows the

user to reduce the jitter by applying a reference clock to the

clock inputs of the ADN2849. The cross point adjust block predistorts the data signal applied to the output stage in order to

compensate for the non-linear transfer function of the EA

modulator as shown in figure 17. The modulation and the bias

offset voltage can be programmed via external DC voltages

applied to the ADN2849. These voltages are converted to

currents internally and applied to the output stage. The singleended output stage provides both the bias offset and

modulation voltages at the same pin (MODP) without the need

of any external components. The ADN2849 can operate with

positive or negative (5.0V or 5.2V) supply voltage.

VEE

GND

VBB

VEE

Figure 18. Equivalent circuit for the data and clock input pins

50Ω 50Ω

VEE

The data and clock input pins are internally terminated with a

100Ω differential termination resistor to minimize signal

reflections at the input pins that could otherwise lead to

degradation in the output eye diagram. The ADN2849 input

pins must be AC-coupled with the signal source to eliminate the

need of matching between the common mode voltages of the

data signal source and the inputs stage of the driver. Also, the

common mode terminal of the internal termination resistors

(VBB) must be externally decoupled. Figure 19 shows the

recommended connection between the data/signal source and

the ADN2849 input pins.

50Ω

50Ω

C

DATAP/CLKP

C

DATAN/CLKN

ADN2849

VBB

INPUT STAGE

The input stage of the ADN2849 gains the data and clock

signals applied to the DATAP, DATAN and CLKP, CLKN pins

respectively to a level that ensures proper operation of the

ADN2849’s output stage. The data and clock inputs are

PECL/CML compatible and can accept input signal swings in

the range of 600mV to 1600mV peak-to peak differential. The

equivalent circuit for the data and clock input pins is shown in

figure 18.

Rev. Pr. G | Page 9 of 17

Data/clock signal source

Figure 19. AC-coupling the data/clock signal source to the ADN2849

input pins

C

GND

Page 10

ADN2849

Preliminary Technical Data

The capacitors used AC-coupling and the decoupling of the

VBB pin must have an impedance less than 50Ω over the

required operating frequency range. Generally this is achieved

using values from 10nF to 100nF.

The retiming feature of the ADN2849 allows the user to remove

the data dependent jitter present on the DATAP and DATAN

pins by applying the data and clock signals to the ADN2849’s

internal latch. The retiming feature can be enabled or disabled

depending on the logic level applied to the CLK_SELB pin as

described in table 7. Note that any jitter present on the CLKP

and CLKN pins is added to the output.

Table 7.

CLK_SELB logic level Retiming function

High Disabled

Low Enabled

If the retiming feature is disabled the CLKP and CLKN inputs

can be left floating.

The CLK_SELB is a 5V TTL and CMOS compatible digital

input. Its equivalent circuit is shown in figure 20.

CROSS POINT ADJUST

The cross point adjust function allows the user to move the eye

crossing level in the modulation voltage to compensate for

asymmetry in the EA modulator electrical-to- optical transfer

function. Figure 21 shows an example on how the cross point

adjust can compensate the asymmetry of the EA modulator

transfer function. The 50% cross point in the optical eye can be

obtained in this case by moving the cross point of the signal

applied to the EA modulator away from the 50% point.

Optical

Output

Electrical

Input

CLK_SELB

GND

GND

180K

40K

VEE

VEE

Figure 20. Equivalent circuit of the CLK_SELB pin

60K

Figure 21. Cross point adjust compensation

The cross point is controlled by the differential voltage applied

to the CPAP and CPAN pins. The equivalent circuit of the

CPAP and CPAN pins is shown in figure 22.

GND

CPAP

VEE

CPAN

GND

VEE

100Ω

VEE

100Ω

100µA 100µA

Rev. Pr. G | Page 10 of 17

VEE VEE

Figure 22. Equivalent circuit of the CPAP and CPAN pins

VEE

Page 11

Preliminary Technical Data

The single-ended voltage at CPAP and CPAN pins must be

within the –0.8V to-1.85V range for proper operation of the

cross point adjust block. The cross point will be controlled by

the differential voltage obtained from the single-ended voltages

applied to CPAP and CPAN pins. A simple implementation of a

cross point adjust circuit is shown in figure 23 where a 20KΩ

potentiometer generates the required differential voltage within

the specified input voltage range.

ADN2849

The MOD_ENB pin is a 5V TTL and CMOS compatible logic

input. Its equivalent circuit of the MOD_ENB pin is shown in

figure 24.

GND GND

GND

180K

60K

GND

20kΩ

CPAP

CPAN

Cross

Point

Adjust

100uA

100uA

VEEVEE

Figure 23. Cross point adjust control circuit

An alternative implementation is to use a voltage DAC and a

single-ended to differential conversion amplifier such as the

AD138 that will allow digital control of the cross point. When

designing the circuitry that will drive the voltages at the CPAP

and CPAN pins the user should take in account that each pin is

sinking 100µΑ. If the cross point adjust feature is not required

both the CPAP and CPAN pins should be connected to GND.

This will automatically set the cross point to 50%. Once the

cross point adjust has been calibrated under nominal conditions

it has very low drift over temperature and supply voltage

variations.

MODULATION ENABLE

The modulation voltage generated by the ADN2849 can be

enabled or disabled under the control of the MOD_ENB pin.

When the modulation is disabled, the input data is ignored and

the voltage at the output of the ADN2849 will place the EA

modulator in a high absorption (low transparency) state. The

relationship between the logic state of the MOD_ENB input and

the modulation voltage is described in table 8.

Table 8.

MOD_ENB logic level Modulation voltage

Low Enabled

High Disabled

MOD_ENB

40K

VEE

VEE

Figure 24. Equivalent circuit of the MOD_ENB pin

OUTPUT STAGE

The output stage of the ADN2849 can provide up to 2V bias

offset and up to 3V modulation voltage across a single-ended

50Ω load. Both the bias offset and the modulation voltage are

made available at a single pin (MODN) eliminating the need for

external bias inductors as shown in figure 25.

GND

V

MOD_SET

ADN2849

From cross

point adjust

block

+

V

-

T

E

S

_

D

O

M

Figure 25. Output stage of the ADN2849

BIAS_S ET

GND

+

-

T

E

S

_

S

A

I

B

VEE

100nF

M

R

E

T

_

M

N

R

E

T

V

IMOD

D

O

M

50

Ω

50

Ω

MODP

EAM

D

N

G

R

R

Rev. Pr. G | Page 11 of 17

Page 12

ADN2849

N

Preliminary Technical Data

Modulation voltage

The modulation voltage is established by switching the

modulation current through the parallel combination of the

modulator terminating impedance (50Ω) and the 50Ω backtermination resistor on the ADN2849. The modulation set

voltage applied to the MOD_SET pin is converted into current

(IMOD) using a voltage-to-current converter which forces a

voltage equal to V

across an internal fixed resistor. For

MOD_SET

IMOD range of 24mA to 120mA, the MOD_SET voltage ranges

from 340mV to 1.7V. With its maximum modulation current of

120mA, the ADN2849 is capable of generating a 3V modulation

voltage across the equivalent load resistance (25Ω). The

equivalent circuit of the MOD_SET pin is shown in figure 26.

GND

MOD_SET

VEE

Figure 26. Equivalent circuit of the MOD_SET pin

100Ω

100Ω

VEE

Bias offset voltage

The bias offset voltage is set by adjusting the voltage between

the BIAS_SET pin and GND. An internal operational amplifier

sets the termination voltage for the internal 50Ω output backtermination resistors (VTERM) by gaining up the BIAS_SET

voltage by two. This gain of two cancels out the attenuation of

the dividing network formed by the 50Ω back- termination

resistor from the ADN2849 output and the 50Ω load

termination, providing a nominal gain of one from the

BIAS_SET input to the bias offset voltage available at the output

of the ADN2849 (MODP pin). For proper operation, an

external low ESR 100nF decoupling capacitor is required

between the VTERM pin and GND to prevent transient

disturbances on this node. The equivalent circuits of the

BIAS_SET, MODP, MODN_TERM and VTERM pins are

shown in figure27.

G

D

VTERM

MODN_TERM

50Ω

10K

VEE

100Ω

GND

BIAS_SET

VEE

Figure 27. Equivalent circuit of the BIAS_SET, MODP, MODN_TERM

5K

VEE

and VTERM pins

VEE

MODP

During factory calibration of the optical transmitter, the user

adjusts the BIAS_SET and MOD_SET voltages to achieve the

desired bias offset and modulation voltages. This adjustment

calibrates out BIAS_SET to bias offset voltage and MOD_SET to

modulation voltage gain variations in the ADN2849 due to

resistor process variations and the offset of the internal

amplifiers. The drift in the bias offset and modulation voltages

over temperature and supply voltage variations is very low once

it has been calibrated under nominal conditions.

Headroom calculations

The ADN2849 is capable of delivering up to 2V bias offset and

up to 3V modulation voltage on a 50Ω single-ended load.

However, these values for the bias offset and modulation

voltages cannot be obtained at the same time due to headroom

constraints. The minimum supply voltage and the MODP

minimum output voltage specifications determine the

maximum modulation and bias offset voltages that can be

achieved concurrently. In order to guarantee proper operation

of the ADN2849, the bias offset and modulation voltages must

satisfy the following condition:

VVEEVV −≤+

minMODPffsetO BiasModulation

Where,

V

V

= the required modulation voltage

Modulatio n

= the required bias offset voltage

Bias Offset

VEE = the supply voltage

V

Rev. Pr. G | Page 12 of 17

= the minimum voltage at the MODP pin (see table 1)

MODPmin

Page 13

Preliminary Technical Data

POWER DISSIPATION

The power dissipated by the ADN2849 is a function of the

supply voltage and the level of bias offset and modulation

voltages required. Figure 28 shows the power dissipation of the

ADN2849 vs. modulation voltage for different bias offset

voltages. To ensure long-term reliable operation, the junction

temperature of the ADN2849 must not exceed 125

000

000

)

p

a

c

l

000

a

i

t

i

n

I

(

S

P

A

000

C

L

L

A

0

C.

TBD

ADN2849

For improved heat dissipation the module’s case can be used as

heat sink as shown in figure 29. A compact optical module is a

complex thermal environment, and calculations of device

junction temperature using the package θ

Ambient thermal resistance) do not yield accurate results

(Junction-to-

J-A

.

000

000

000 000 000 000 000 000

ALL CAPS (Initial cap)

Figure 28. Power dissipation of the ADN2849 vs. bias offset and modulation voltage

Thermal Com pound Module Case

Die

Package

PCB

Copper Plane

Filled Vias

T

TOP

T

J

T

PAD

Thermo-couple

Figure 29. Typical optical module structure

Rev. Pr. G | Page 13 of 17

Page 14

ADN2849

×

+×+××

θθθ

θ

Preliminary Technical Data

The following procedure can be used to estimate the IC

junction temperature.

T

= Temperature at top of package in 0C.

TOP

= Temperature at package exposed paddle in 0C.

T

PAD

= IC junction temperature in 0C.

T

J

P = Power disipation in W.

= Thermal resistance from IC junction to package top.

θ

J-TOP

= Thermal resistance from IC junction to package

θ

J-PAD

exposed pad.

T

TOP

θ

T

J

θ

T

J-TOP

J-PAD

PAD

T

TOP

T

TOP

and T

can be determined by measuring the temperature

PAD

at points inside the module, as shown in fig. 30. The thermocouples should be positioned so as to obtain an accurate

measurement of the package top and paddle temperatures.

Using this model the junction temperature can be calculated

using the formula:

T

=

J

)(

+

θθ

TOPJPADJ

−−

TTP

Where

dissipated by the ADN2849 obtained from the graph shown in

figure 28

θ

J-TOP

and θ

are given in table 3 and P is the power

J-PAD

.

TOPJPADPADJTOPTOPJPADJ

−−−−

T

PAD

Fig. 32. Electrical model for thermal calculations

Rev. Pr. G | Page 14 of 17

Page 15

Preliminary Technical Data

APPLICATIONS INFORMATION

TYPICAL APPLICATION CIRCUIT

Figure 31 shows the typical application circuit for the

ADN2849. Applying DC voltages to the BIAS_SET and

MOD_SET pins can control the Modulation and bias offset

voltages. The data signal source must be connected to the

DATA P an d DATA N p i n s us i ng 5 0 Ω impedance transmission

lines. If a reference clock signal is available, the retiming option

can be enabled using the CLK_SELB input. Note that the

connection between the clock signal source and

JP1

R4

Z0=50

Z0=50

GND

Ω

GND

Ω

C7

JP2

CPAN CPAP

GND

DATAP

DATAN

VBB

CLKP

CLKN

MOD_ENB

GND

Z0=50

GND

Z0=50

GND

Ω

GND

Ω

GND

GND

C1

J1

J2

C2

GND

GND

C3

J3

J4

C4

GND

R3

C15

GND

BIAS_SET VEE

ADN2849

CLK_SELB

the CLKP and CLKN pins must be made using

50Ω transmission lines. The cross point can be adjusted using

the potentiometer R3. The modulation voltage can be enabled

or disabled using the MOD_ENB pin.

The ADN2849 can operate with positive or negative (5.0V or

5.2V) supply voltage. Care should be taken to connect the GND

pins to the positive rail of the supply voltage while the VEE and

the exposed pad to the negative rail of the supply voltage.

BIA S_ SE T

U1

MOD_SET

VEE

C18 C13

GND

GND

VTERM

VTERM

GND

MODP

MODN_TERM

GND

VEE

GND GND

GND

Z0=50

GND

C11

VEE

GND

50

Ω

Ω

EAM

ADN2849

-5.2V

GND

GND

VEE

C5

GND

C6

MOD_ENB

CLK_SELB

Figure 31. Typical ADN2849 application circuit

PCB LAYOUT GUIDELINES

Due to the high frequencies at which the ADN2849 operates,

care should be taken when designing the PCB layout in order to

obtain optimum performance. It is recommended to use

controlled impedance transmission lines for the high-speed

signal paths The length of the transmission lines must be kept

to a minimum to reduce losses and pattern dependant jitter. All

the VEE and GND pins must be connected to solid copper

planes using low inductance connections. When the

connections are made through vias, multiple vias can be

connected in parallel to reduce the parasitic inductance. The

Rev. Pr. G | Page 15 of 17

GND

C10

VEE

C12

GND

MOD_SET

VTERM, VBB, MODN_TERM and VEE pins must be locally

decoupled with high quality capacitors. If proper decoupling

cannot be achieved using a single capacitor, the user can use

multiple capacitors in parallel for each GND pin. A 20µF

tantalum capacitor must be used as general decoupling

capacitor for the entire module The exposed pad should be

connected to the most negative rail of the supply voltage using

filled vias so that solder does not leak through the vias during

reflow. Using filled vias under the package greatly enhances the

reliability of the connectivity of the exposed pad to the GND

plane during reflow.

Page 16

ADN2849

Preliminary Technical Data

DESIGN EXAMPLE

This section describes a design example that covers the

followings:

• Headroom calculation for the required bias offset and

modulation voltages

• Required voltage range at the BIAS_SET and

MOD_SET pins to generate the required bias offset

and modulation voltages

This design example assumes a -5.2V supply voltage, 0.5V bias

offset voltage and 2V modulation voltage.

Headroom calculations

In order to operate properly, the bias offset and modulation

voltages must satisfy the following condition:

MOD_SET voltage range

The voltage range at the MOD_SET pin to generate 2V bias

offset voltage at the MODP pin can be calculated using the

MOD_SET voltage to bias offset voltage gain specification from

table1 using the formulae:

V

MODULATION

=

V

MODULATION

=

K

max

K

min

Where K

min

V

V

and K

minSET_MOD

maxSET_MOD

are the minimum and maximum values of

max

the MOD_SET voltage to offset bias voltage gain from table1.

Substituting the values the MOD_SET voltage range is 1.05V to

1.33V.

Assuming that V

VVEEVV −≤+

=1.7V (see table1), the above condition

MODPmin

minMODPffsetO BiasModulation

became:

V5.37.12.5V5.2 =−≤

BIAS_SET voltage range

The voltage range at the BIAS_SET pin to generate 0.5V bias

offset voltage at the MODP pin can be calculated using the

BIAS_SET voltage to bias offset voltage gain specification from

table1 using the formulae:

V

OFFSET BIAS

K

max

V

OFFSET BIAS

K

min

Where K

min

V

V

and K

=

minSET_BIAS

=

maxSET_BIAS

are the minimum and maximum values of

max

the BIAS_SET voltage to offset bias voltage gain from table1.

Substituting the values the BIAS_SET voltage range is 0.45V to

0.55V.

Rev. Pr. G | Page 16 of 17

Page 17

Preliminary Technical Data

PR04323-0-9/04(PrG)

OUTLINE DIMENSIONS

ADN2849

4.0

BSC SQ

0.60MAX

0.60 MAX

PIN 1

INDICATOR

1

VIEW

24

2.25

SQ

2.10

6

7

1.95

0.25 MIN

2.50 REF

X(µm) Y(µm)

19

PIN 1

INDICATOR

TOP

VIEW

3.75

BSCSQ

0.50

BSC

0.50

0.40

18

13

12

BOTTOM

0.30

1.00

0.85

0.80

12MAX

SEATING

PLANE

0.80 MAX

0.65 TYP

0.30

0.23

0.18

0.05 MAX

0.02 NO M

0.20REF

COPLANARITY

0.08

COMPLIANTTO JEDEC STANDARDS MO-220-VGGD-2

Figure 32. 24-Lead Lead Frame Chip Scale Package (LFCSP) 4mm×4mm Body (CP-24)

Dimensions shown in millimeters

Figure 33. ADN2849 metallization photograph

Table 9. Die pad coordinates

Pad Number

1 -920.50 685.00

2 -920.50 331.55

3 -920.50 103.05

4 -920.50 -48.75

4 -920.50 -220.15

5 -920.50 -371.95

6 -920.50 -525.55

7 -609.10 -920.50

8 -457.30 -920.50

9 -305.50 -920.50

10 -103.70 -920.50

11 324.85 -920.50

12 584.00 -920.50

13 920.50 -688.20

14 920.50 -484.20

15 920.50 -271.10

16 920.50 274.50

17 920.50 490.00

18 920.50 694.00

19 628.00 920.50

19 501.10 920.50

20 349.30 920.50

21 182.40 920.50

22 3.50 920.50

23 -457.30 920.50

24 -609.10 920.50

25 -736.00 920.50

26 -736.00 -920.50

27 738.00 -920.50

Note: The coordinates are measured between the center of the die and the center

of the pad

.

Rev. Pr. G | Page 17 of 17

Loading...

Loading...