Multirate to 2.7 Gb/s Clock and Data

Recovery IC with Integrated Limiting Amp

FEATURES

Meets SONET requirements for jitter

transfer/generation/tolerance

Quantizer sensitivity: 4 mV typical

Adjustable slice level: ±100 mV

1.9 GHz minimum bandwidth

Patented clock recovery architecture

Loss of signal detect range: 3 mV to 15 mV

Single reference clock frequency for all rates, including

15/14 (7%) wrapper rate

Choice of 19.44 MHz, 38.88 MHz, 77.76 MHz, or 155.52 MHz

REFCLK

LVPECL/LVDS/LVCMOS/LVTTL compatible inputs

(LVPECL/LVDS only at 155.52 MHz)

19.44 MHz oscillator on-chip to be used with external crystal

Loss of lock indicator

Loopback mode for high speed test data

Output squelch and bypass features

Single-supply operation: 3.3 V

Low power: 540 mW typical

7 mm × 7 mm 48-lead LFCSP

APPLICATIONS

SONET OC-3/-12/-48, SDH STM-1/-4/-16, GbE and 15/14

FEC rates

WDM transponders

Regenerators/repeaters

Test equipment

Backplane applications

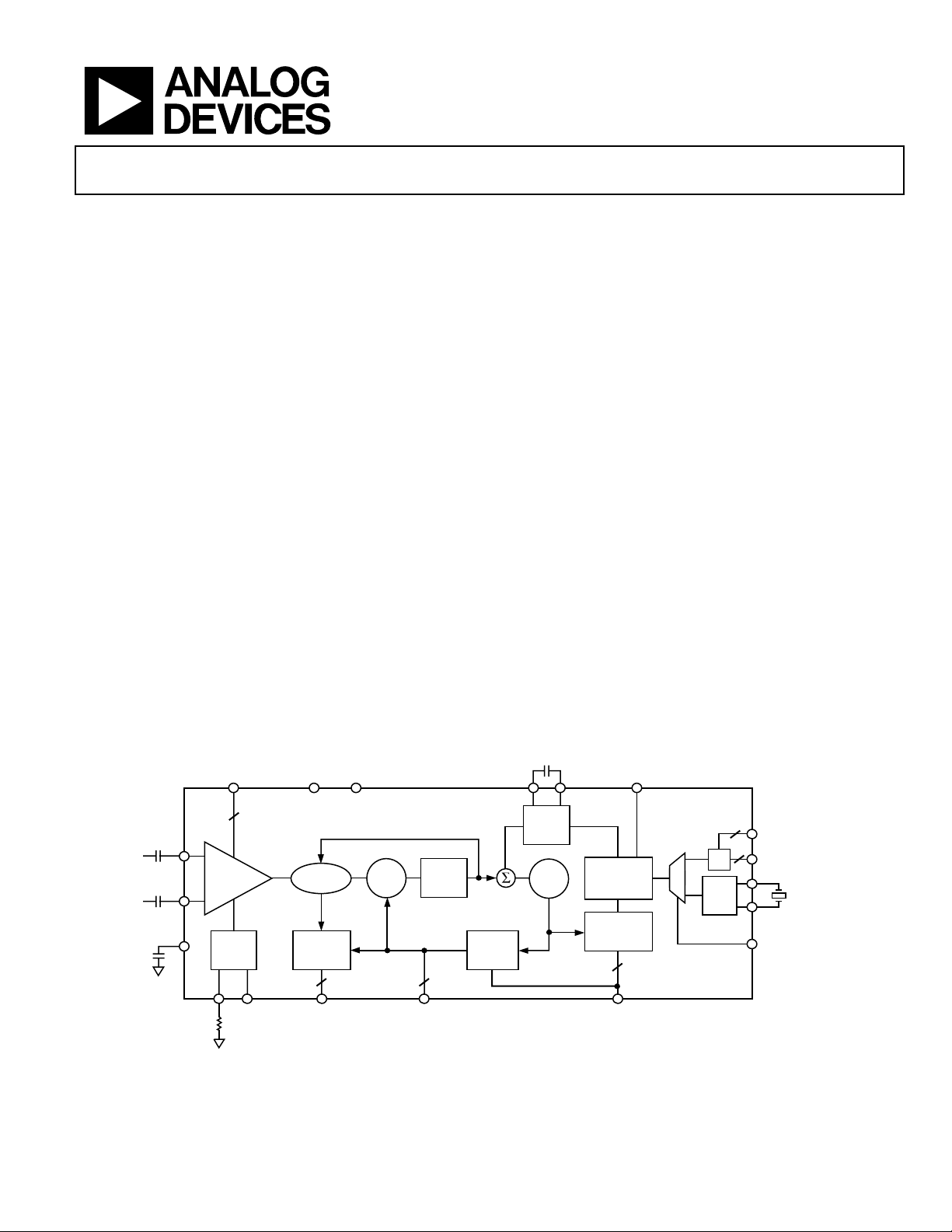

FUNCTIONAL BLOCK DIAGRAM

SLICEP/N VCC VEE

ADN2819

PRODUCT DESCRIPTION

The ADN2819 provides the receiver functions of quantization,

signal level detect, and clock and data recovery at rates of OC-3,

OC-12, OC-48, Gigabit Ethernet, and 15/14 FEC rates. All

SONET jitter requirements are met, including jitter transfer,

jitter generation, and jitter tolerance. All specifications are

quoted for –40°C to +85°C ambient temperature, unless

otherwise noted.

The device is intended for WDM system applications, and can

be used with either an external reference clock or an on-chip

oscillator with external crystal. Both native rates and 15/14 rate

digital wrappers are supported by the ADN2819, without any

change of reference clock.

This device, together with a PIN diode and a TIA preamplifier,

can implement a highly integrated, low cost, low power, fiber

optic receiver.

The receiver front end signal detect circuit indicates when the

input signal level has fallen below a user-adjustable threshold.

The signal detect circuit has hysteresis to prevent chatter at the

output.

The ADN2819 is available in a compact 7 mm × 7 mm, 48-lead

chip scale package.

CF1 CF2

LOL

ADN2819

2

PIN

QUANTIZER

NIN

VREF

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

THRADJ

LEVEL

DETECT

PHASE

SHIFTER

DAT A

RETIMING

PHASE

DET.

LOOP

FILTER

22

DIVIDER

1/2/4/16

Figure 1.

LOOP

FILTER

FREQUENCY

VCO

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

LOCK

DETECTOR

FRACTIONAL

DIVIDER

3

SEL[0..2]CLKOUTP/NDATAOUTP/NSDOUT

www.analog.com

/n

XTAL

OSC

2

2

REFSEL[0..1]

REFCLKP/N

XO1

XO2

REFSEL

02999-0-001

ADN2819

TABLE OF CONTENTS

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 6

Thermal Characteristics .............................................................. 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Definition of Terms.......................................................................... 9

Maximum, Minimum, and Typical Specifications................... 9

Input Sensitivity and Input Overdrive....................................... 9

Single-Ended vs. Differential ...................................................... 9

LOS Response Time................................................................... 10

Jitter Specifications..................................................................... 10

Theory of Operation ...................................................................... 12

Functional Description.................................................................. 14

Multirate Clock and Data Recovery......................................... 14

Limiting Amplifier ..................................................................... 14

Slice Adjust.................................................................................. 14

Loss of Signal (LOS) Detector .................................................. 14

Reference Clock.......................................................................... 14

Lock Detector Operation .......................................................... 15

Squelch Mode ............................................................................. 16

Test Modes: Bypass and Loopback........................................... 16

Applications Information.............................................................. 17

PCB Design Guidelines ............................................................. 17

Choosing AC-Coupling Capacitors......................................... 19

DC-Coupled Application .......................................................... 20

LOL Toggling During Loss of Input Data............................... 20

Outline Dimensions....................................................................... 21

Ordering Guide .......................................................................... 21

REVISION HISTORY

5/04—Data Sheet Changed from Rev. A to Rev. B

Updated Format..............................................................Universal

Changes to Specifications............................................................ 3

Changes to Table 7 and Table 8................................................. 15

Updated Outline Dimensions................................................... 21

Changes to Ordering Guide...................................................... 21

1/03—Data Sheet Changed from Rev. 0 to Rev. A

Changes to Table IV ................................................................... 12

Updated OUTLINE DIMENSIONS ........................................ 16

Rev. B | Page 2 of 24

ADN2819

SPECIFICATIONS

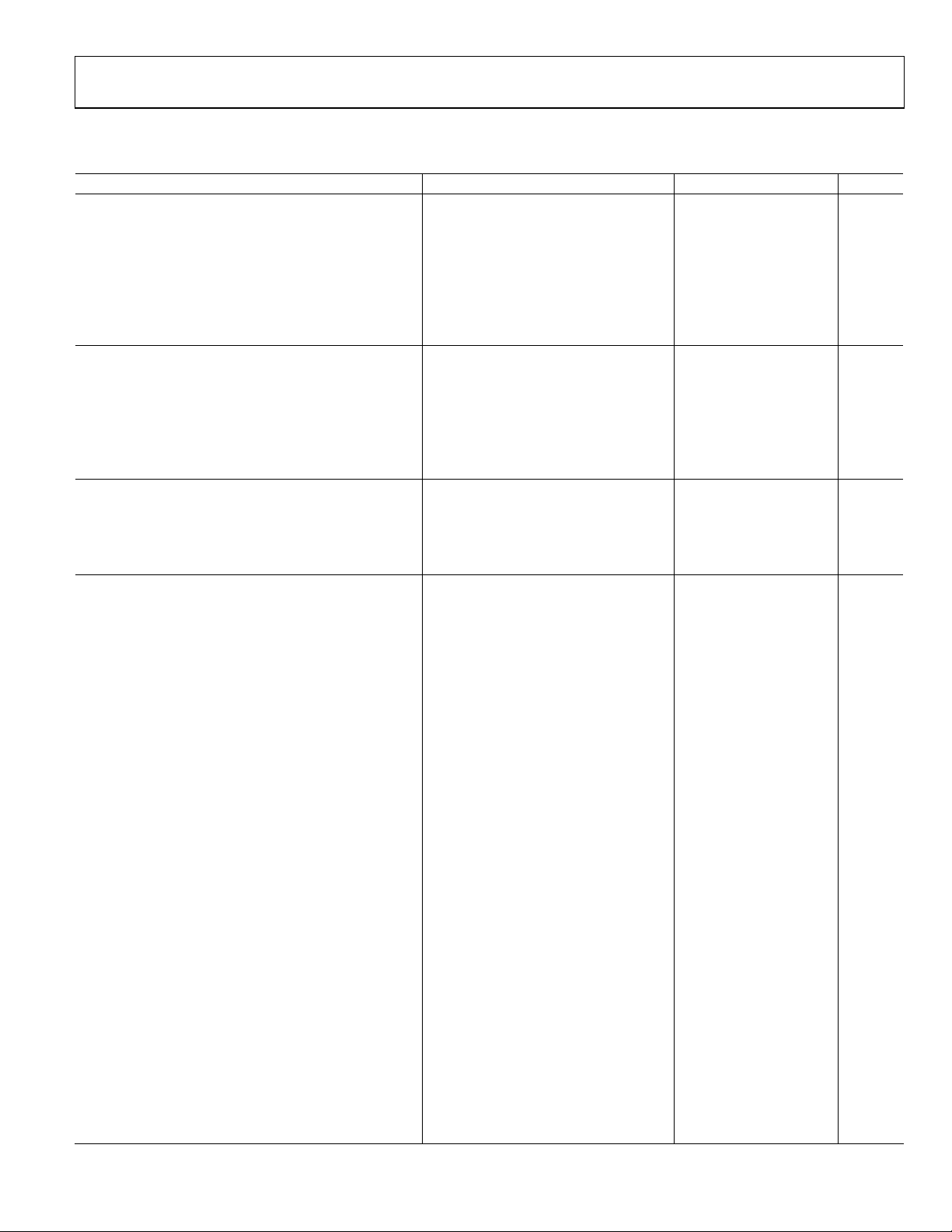

Table 1. TA = T

Parameter Conditions Min Typ Max Unit

QUANTIZER—DC CHARACTERISTICS

Input Voltage Range @ PIN or NIN, dc-coupled 0 1.2 V

Peak-to-Peak Differential Input 2.4 V

Input Common-Mode Level DC-coupled (See Figure 28) 0.4 V

Differential Input Sensitivity PIN-NIN, ac-coupled1, BER = 1 × 10

Input Overdrive See Figure 8 2 5 mV p-p

Input Offset 500 µV

Input rms Noise BER = 1 × 10

QUANTIZER—AC CHARACTERISTICS

Upper –3 dB Bandwidth 1.9 GHz

Small Signal Gain Differential 54 dB

S11 @ 2.5 GHz –15 dB

Input Resistance Differential 100 Ω

Input Capacitance 0.65 pF

Pulse Width Distortion2 10 ps

QUANTIZER SLICE ADJUSTMENT

Gain SLICEP–SLICEN = ±0.5 V 0.11 0.20 0.30 V/V

Control Voltage Range SLICEP–SLICEN –0.8 +0.8 V

@ SLICEP or SLICEN 1.3 VCC V

Slice Threshold Offset ±1.0 mV

LEVEL SIGNAL DETECT (SDOUT)

Level Detect Range (See Figure 4) R

R

R

Response Time DC-coupled 0.1 0.3 5 µs

Hysteresis (Electrical) OC-48, PRBS 223

R

R

R

OC-12, PRBS 223

R

R

R

R

OC-3, PRBS 223

R

R

R

R

OC-48, PRBS 27

R

R

R

OC-12, PRBS 27

R

R

R

MIN

to T

, VCC = V

MAX

MIN

to V

, VEE = 0 V, CF = 4.7 µF, SLICEP = SLICEN = VCC, unless otherwise noted.

MAX

–10

4 10 mV p-p

–10

244 µV rms

= 2 Ω 9.4 13.3 18.0 mV

THRESH

= 20 kΩ 2.5 5.3 7.6 mV

THRESH

= 90 kΩ 0.7 3.0 5.2 mV

THRESH

= 2 kΩ 5.6 6.6 7.8 dB

THRESH

= 20 kΩ 3.9 6.2 8.5 dB

THRESH

= 90 kΩ 3.2 6.7 9.9 dB

THRESH

= 2 kΩ 4.7 6.4 7.8 dB

THRESH

= 20 kΩ 1.8 6.0 10.0 dB

THRESH

= 90 kΩ 6.3 dB

THRESH

= 90 kΩ @ 25°C 4.8 6.9 8.9 dB

THRESH

= 2 kΩ 3.6 6.2 8.5 dB

THRESH

= 20 kΩ 5.6 dB

THRESH

= 90 kΩ 5.6 dB

THRESH

= 90 kΩ @ 25°C 3.4 6.6 9.9 dB

THRESH

= 2 kΩ 5.6 6.6 7.8 dB

THRESH

= 20 kΩ 3.9 6.2 8.5 dB

THRESH

= 90 kΩ 3.2 6.7 9.9 dB

THRESH

= 2 kΩ 5.7 6.6 7.8 dB

THRESH

= 20 kΩ 3.9 6.2 8.5 dB

THRESH

= 90 kΩ 3.2 6.7 9.9 dB

THRESH

Rev. B | Page 3 of 24

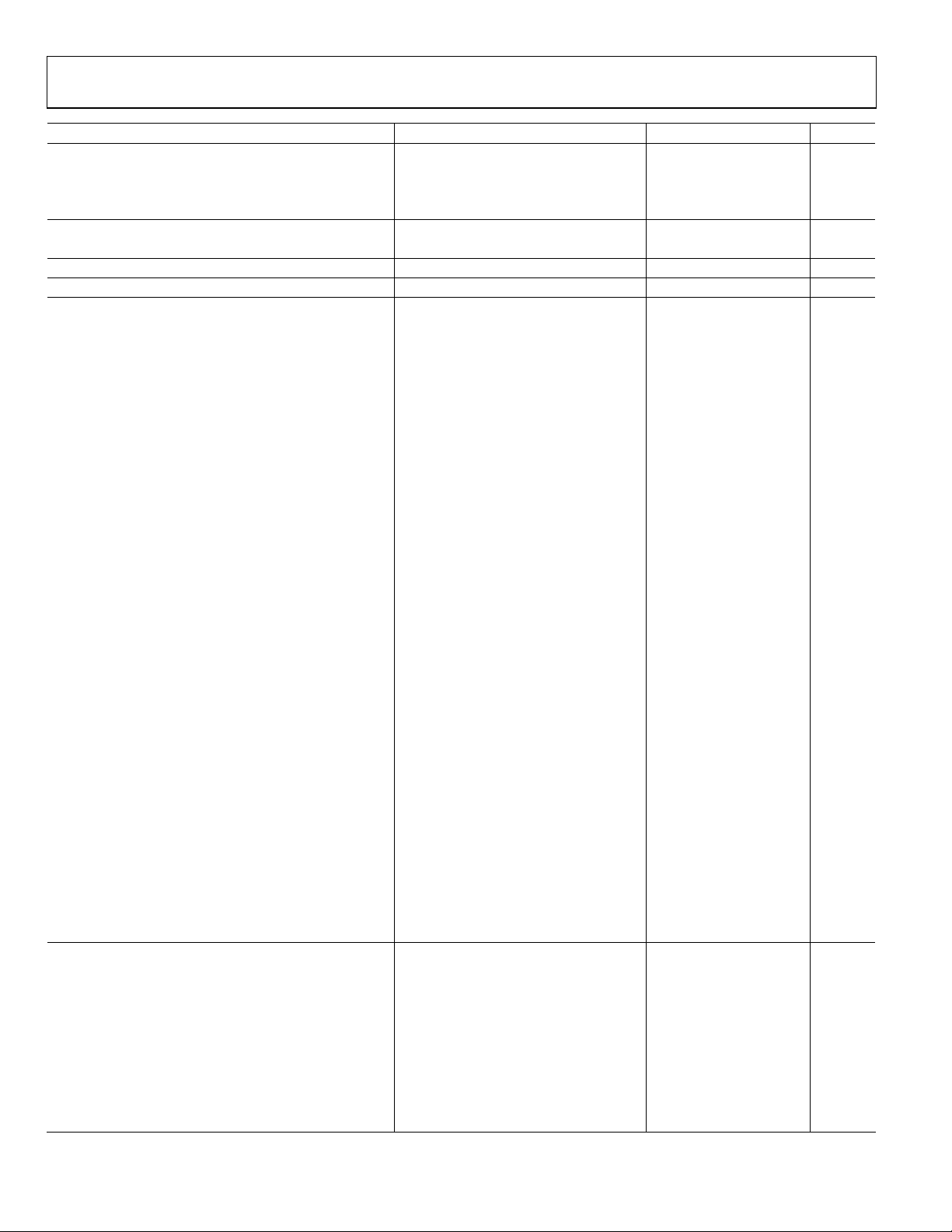

ADN2819

Parameter Conditions Min Typ Max Unit

Hysteresis (Electrical) (continued) OC-3, PRBS 27

R

R

R

LOSS OF LOCK DETECTOR (LOL)

Loss of Lock Response Time From f

POWER SUPPLY VOLTAGE 3.0 3.3 3.6 V

POWER SUPPLY CURRENT 150 164 215 mA

PHASE-LOCKED LOOP CHARACTERISTICS PIN–NIN = 10 mV p-p

Jitter Transfer BW OC-48 590 880 kHz

GbE 310 480 kHz

OC-12 140 200 kHz

OC-3 48 85 kHz

Jitter Peaking OC-48 0.025 dB

OC-12 0.004 dB

OC-3 0.002 dB

Jitter Generation OC-48, 12 kHz–20 MHz 0.003 UI rms

0.05 0.09 UI p-p

OC-12, 12 kHz–5 MHz 0.002 UI rms

0.02 0.04 UI p-p

OC-3, 12 kHz–1.3 MHz 0.002 UI rms

0.02 0.04 UI p-p

Jitter Tolerance OC-48 (See Figure 14)

600 Hz3 92 UI p-p

6 kHz3 20 UI p-p

100 kHz 5.5 UI p-p

1 MHz3 1.0 UI p-p

GbE (OC-24) (See Figure 14)

300 Hz3 16 UI p-p

3 kHz3 16 UI p-p

50 kHz 7.7 UI p-p

500 kHz3 2.2 UI p-p

OC-12 (See Figure 14)

30 Hz3 100 UI p-p

300 Hz 44 UI p-p

25 kHz 5.8 UI p-p

250 kHz3 1.0 UI p-p

OC-3 (See Figure 14)

30 Hz3 50 UI p-p

300 Hz3 23.5 UI p-p

6500 Hz 6.0 UI p-p

65 kHz3 1.0 UI p-p

CML OUTPUTS (CLKOUTP/N, DATAOUTP/N)

Single-Ended Output Swing VSE (See Figure 7) 300 455 600 mV

Differential Output Swing V

Output High Voltage VOH VCC V

Output Low Voltage VOL, referred to VCC –0.60 –0.30 V

Rise Time 20%–80% 150 ps

Fall Time 80%–20% 150 ps

= 2 kΩ 5.4 6.6 7.7 dB

THRESH

= 20 kΩ 4.6 6.4 8.2 dB

THRESH

= 90 kΩ 3.9 6.8 9.7 dB

THRESH

error > 1000 ppm 60 mV

VCO

(See Figure 7) 600 910 1200 mV

DIFF

Rev. B | Page 4 of 24

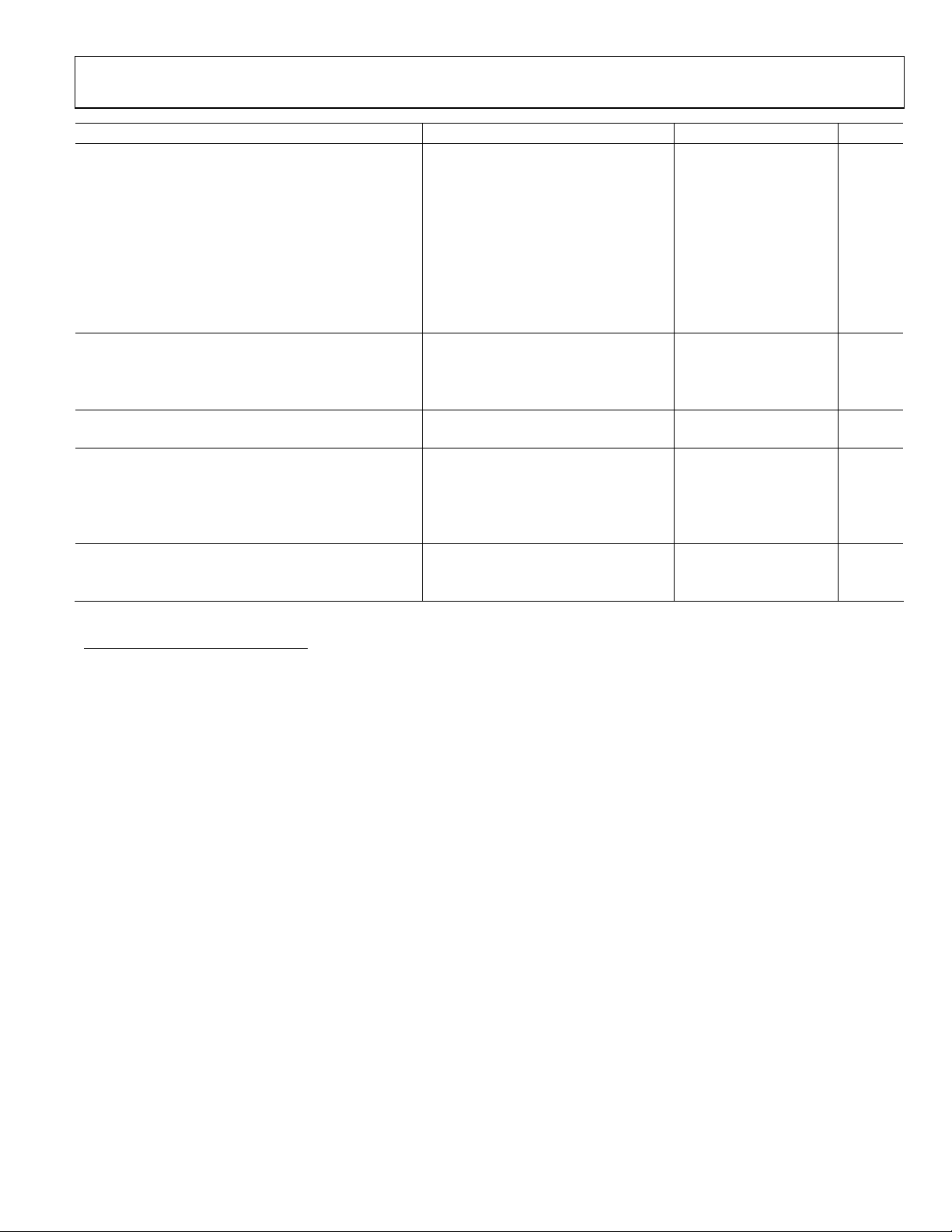

ADN2819

Parameter Conditions Min Typ Max Unit

Setup Time TS (See Figure 3)

OC-48 140 ps

GbE 350 ps

OC-12 750 ps

OC-3 3145 ps

Hold Time TH (See Figure 3)

OC-48 150 ps

GbE 350 ps

OC-12 750 ps

OC-3 3150 ps

REFCLK DC INPUT CHARACTERISTICS

Input Voltage Range @ REFCLKP or REFCLKN 0 VCC V

Peak-to-Peak Differential Input 100 mV

Common-Mode Level DC-coupled, single-ended VCC/2 V

TEST DATA DC INPUT CHARACTERISTICS4 (TDINP/N) CML inputs

Peak-to-Peak Differential Input Voltage 0.8 V

LVTTL DC INPUT CHARACTERISTICS

Input High Voltage VIH 2.0 V

Input Low Voltage VIL 0.8 V

Input Current VIN = 0.4 V or VIN = 2.4 V –5 +5 µA

Input Current (SEL0 and SEL1 Only)5 V

LVTTL DC OUTPUT CHARACTERISTICS

Output High Voltage VOH, IOH = –2.0 mA 2.4 V

Output Low Voltage VOL, IOL = +2.0 mA 0.4 V

= 0.4 V or VIN = 2.4 V –5 +50 µA

IN

1

PIN and NIN should be differentially driven, ac-coupled for optimum sensitivity.

2

PWD measurement made on quantizer outputs in bypass mode.

3

Jitter tolerance measurements are equipment limited.

4

TDINP/N are CML inputs. If the drivers to the TDINP/N inputs are anything other than CML, they must be ac-coupled.

5

SEL0 and SEL1 have internal pull-down resistors, causing higher IIH.

Rev. B | Page 5 of 24

ADN2819

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage (VCC) 5.5 V

Minimum Input Voltage (All Inputs) VEE – 0.4 V

Maximum Input Voltage (All Inputs) VCC + 0.4 V

Maximum Junction Temperature 165°C

Storage Temperature –65°C to +150°C

Lead Temperature (Soldering 10 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

THERMAL CHARACTERISTICS

Thermal Resistance

48-lead LFCSP, 4-layer board with exposed paddle soldered

to VCC

= 25°C/W

θ

JA

Rev. B | Page 6 of 24

ADN2819

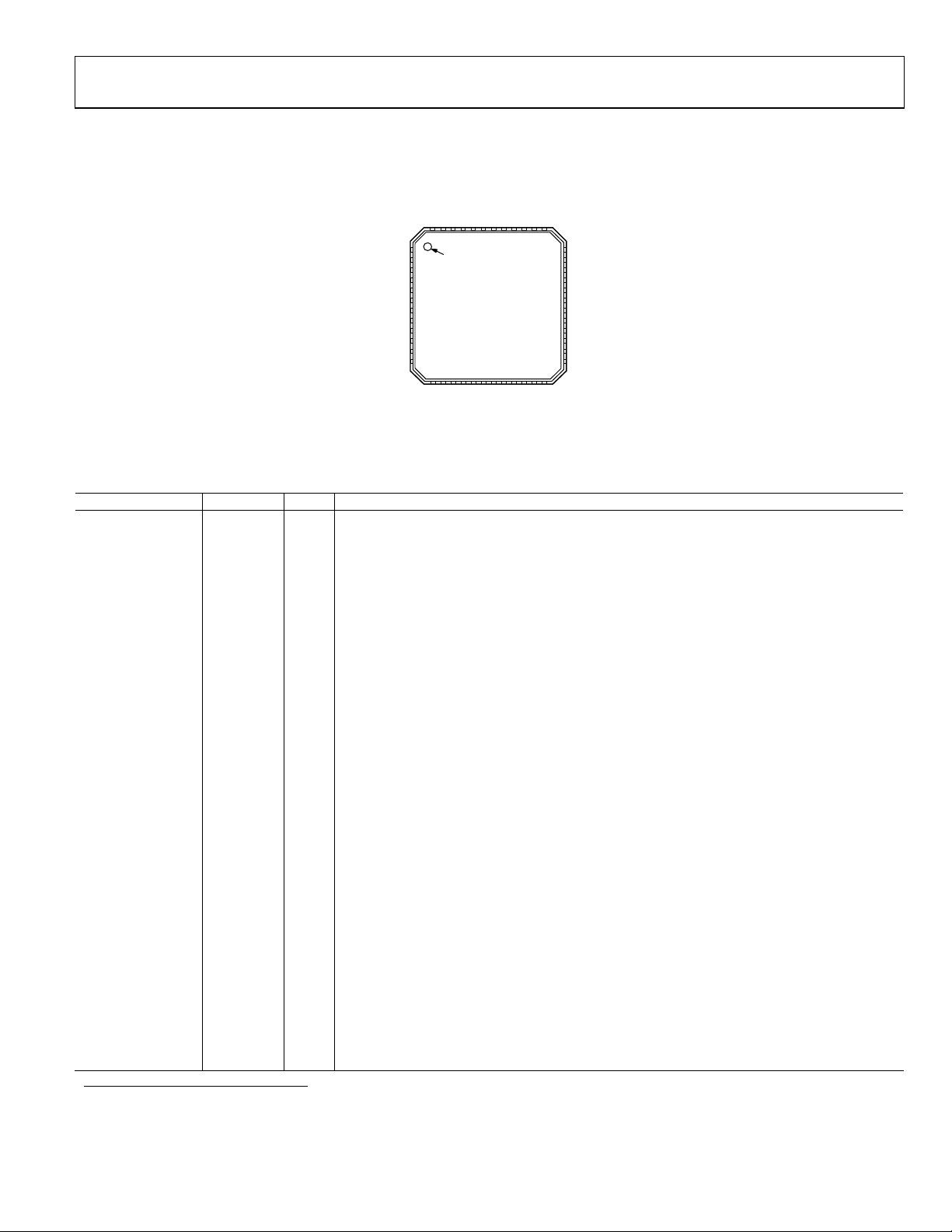

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

48 LOOPEN

47VCC

46VEE

45 SDOUT

44 BYPASS

43VEE

42VEE

41 CLKOUTP

40 CLKOUTN

39 SQUELCH

38 DATAOUTP

37 DATAOUTN

THRADJ 1

VCC 2

VEE 3

VREF 4

PIN 5

NIN 6

SLICEP 7

SLICEN 8

VEE 9

LOL 10

XO1 11

XO2 12

PIN 1

INDICATOR

ADN2819

TOPVIEW

VEE 16

REFSEL 15

REFCLKP 14

REFCLKN 13

VEE 19

TDINP 17

TDINN 18

CF1 21

VCC 20

VEE 22

REFSEL1 23

36VCC

35VCC

34VEE

33VEE

32 SEL0

31 SEL1

30 SEL2

29VEE

28VCC

27VEE

26VCC

25 CF2

REFSEL0 24

02999-B-002

Figure 2. 48-Lead LFCSP Pin Configuration

Table 3. Pin Function Descriptions

Pin Number Mnemonic Type1 Description

1 THRADJ AI LOS Threshold Setting Resistor.

2, 26, 28, Pad VCC P Analog Supply.

3, 9, 16, 19, 22, 27,

VEE P Ground.

29, 33, 34, 42, 43, 46

4 VREF AO Internal VREF Voltage. Decouple to GND with 0.1 µF capacitor.

5 PIN AI Differential Data Input.

6 NIN AI Differential Data Input.

7 SLICEP AI Differential Slice Level Adjust Input.

8 SLICEN AI Differential Slice Level Adjust Input.

10 LOL DO Loss of Lock Indicator. LVTTL active high.

11 XO1 AO Crystal Oscillator.

12 XO2 AO Crystal Oscillator.

13 REFCLKN DI Differential REFCLK Input. LVTTL, LVCMOS, LVPECL, LVDS (LVPECL, LVDS only at 155.52 MHz).

14 REFCLKP DI Differential REFCLK Input. LVTTL, LVCMOS, LVPECL, LVDS (LVPECL, LVDS only at 155.52 MHz).

15 REFSEL DI Reference Source Select. 0 = on-chip oscillator with external crystal; 1 = external clock source, LVTTL.

17 TDINP AI Differential Test Data Input. CML.

18 TDINN AI Differential Test Data Input. CML.

20, 47 VCC P Digital Supply.

21 CF1 AO Frequency Loop Capacitor.

23 REFSEL1 DI Reference Frequency Select (See Table 6) LVTTL.

24 REFSEL0 DI Reference Frequency Select (See Table 6) LVTTL.

25 CF2 AO Frequency Loop Capacitor.

30 SEL2 DI Data Rate Select (See Table 5) LVTTL.

31 SEL1 DI Data Rate Select (See Table 5) LVTTL.

32 SEL0 DI Data Rate Select (See Table 5) LVTTL.

35, 36 VCC P Output Driver Supply.

37 DATAOUTN DO Differential Retimed Data Output. CML.

38 DATAOUTP DO Differential Retimed Data Output. CML.

39 SQUELCH DI Disable Clock and Data Outputs. Active high. LVTTL.

40 CLKOUTN DO Differential Recovered Clock Output. CML.

41 CLKOUTP DO Differential Recovered Clock Output. CML.

44 BYPASS DI Bypass CDR Mode. Active high. LVTTL.

45 SDOUT DO Loss of Signal Detect Output. Active high. LVTTL.

48 LOOPEN DI Enable Test Data Inputs. Active high. LVTTL.

1

Type: P = Power, AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output.

Rev. B | Page 7 of 24

ADN2819

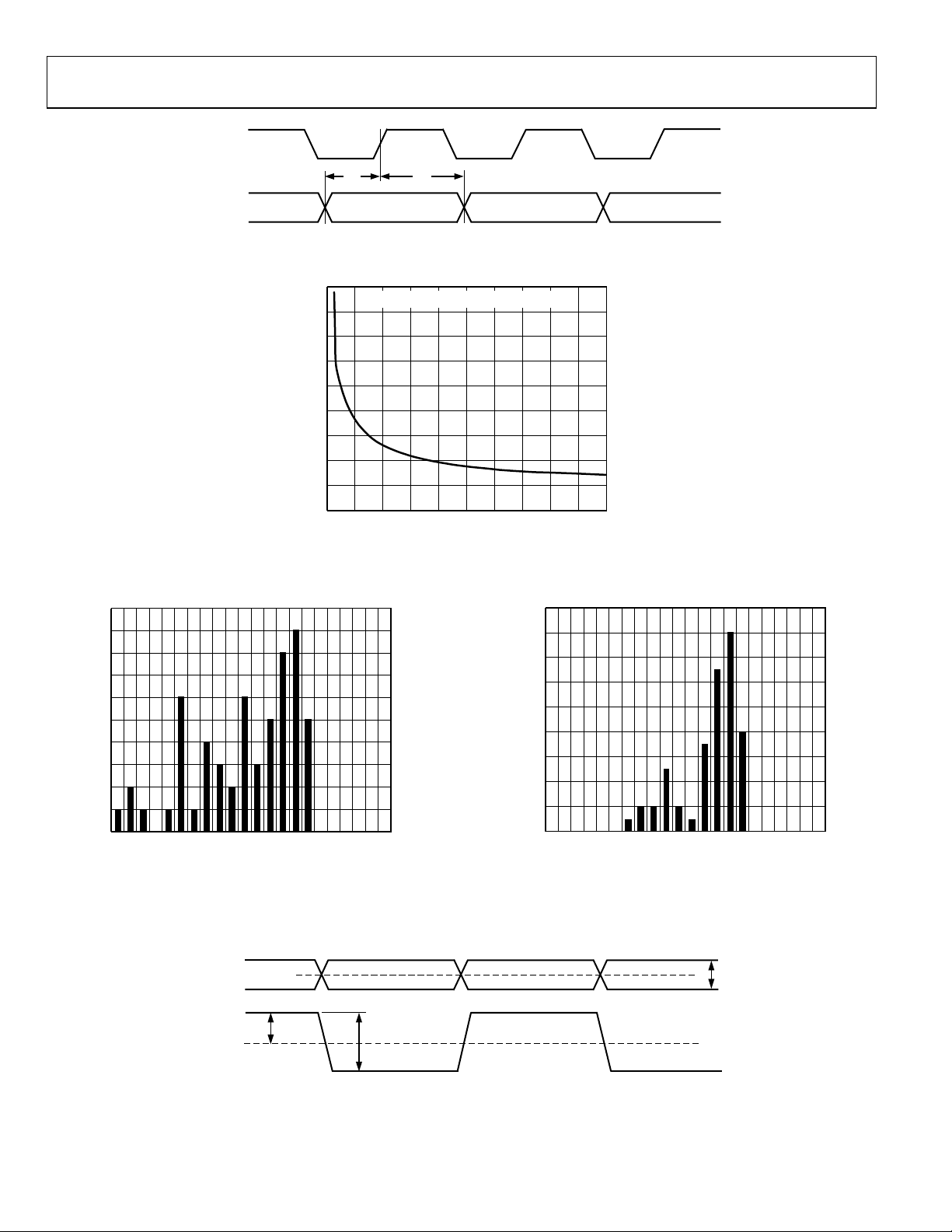

CLKOUTP

T

S

T

H

DATAOUTP/N

10

9

8

7

6

5

4

FREQUENCY

3

2

1

0

01123456789

Figure 5. LOS Hysteresis OC-3, –40°C, 3.6 V,

23

2

HYSTERESIS (dB)

– 1 PRBS Input Pattern, RTH = 90 kΩ

OUTP

OUTN

OUTP–OUTN

V

CML

V

0V

SE

Figure 3. Output Timing

18

16

14

12

10

mV

8

6

4

2

0

0 100

THRADJ RESISTOR VS. LOSTRIP POINT

10 20 30 40 50 60 70 80 90

RESISTANCE (kΩ)

Figure 4. LOS Comparator Trip Point Programming

18

16

14

12

10

8

FREQUENCY

6

4

2

0

0

02999-B-005

01123456789 0

Figure 6. LOS Hysteresis OC-12, –40°C, 3.6 V,

V

DIFF

Figure 7. Single-Ended vs. Differential Output Specifications

02999-B-003

02999-B-004

HYSTERESIS (dB)

23

– 1 PRBS Input Pattern, RTH = 90 kΩ

2

V

SE

02999-B-006

02999-B-007

Rev. B | Page 8 of 24

Loading...

Loading...