Mobile TV One-chip Receiver

Preliminary Technical Data

FEATURES

RF Tuner and Demodulator SoC for T-DMB/DAB/FM

Supports Triple-band: Band III, L-Band and FM

Wide Dynamic Range: −102dBm to +5dBm in 50Ω

Low Power Consumption

CSP_BGA Package: 75mW@TDMB_Video_544kbps

CSP Package: 65mW@TDMB_Video_544kbps

Reference Clock

CSP_BGA Package: 16.384/19.2MHz

CSP Package: 16.384MHz

1.2V Supply Voltage for Core and 1.8/2.8V Dual Supply

Voltage selectable for I/O

Supports JTAG I/O Boundary Scan

Fully Compliant to T-DMB Standards in Korea and ETSI

300 401 Physical Layer Definition

Satisfied TTAS.KO-07.0024 Specification of the data

Services for VHF Digital Multimedia Broadcasting

Supports ETSI EN 300 744 (204,188) Outer Coder

144-Ball

Chip Scale Package Ball Grid Array (CSP_BGA) and

92-Ball Chip Scale Package (CSP)

for T-DMB/DAB/FM

ADMTV315

CSP_BGA Package 7mm × 7mm × 1.0mm, 0.5mm pitch

CSP Package 5mm × 5mm × 0.75mm, 0.45mm pitch

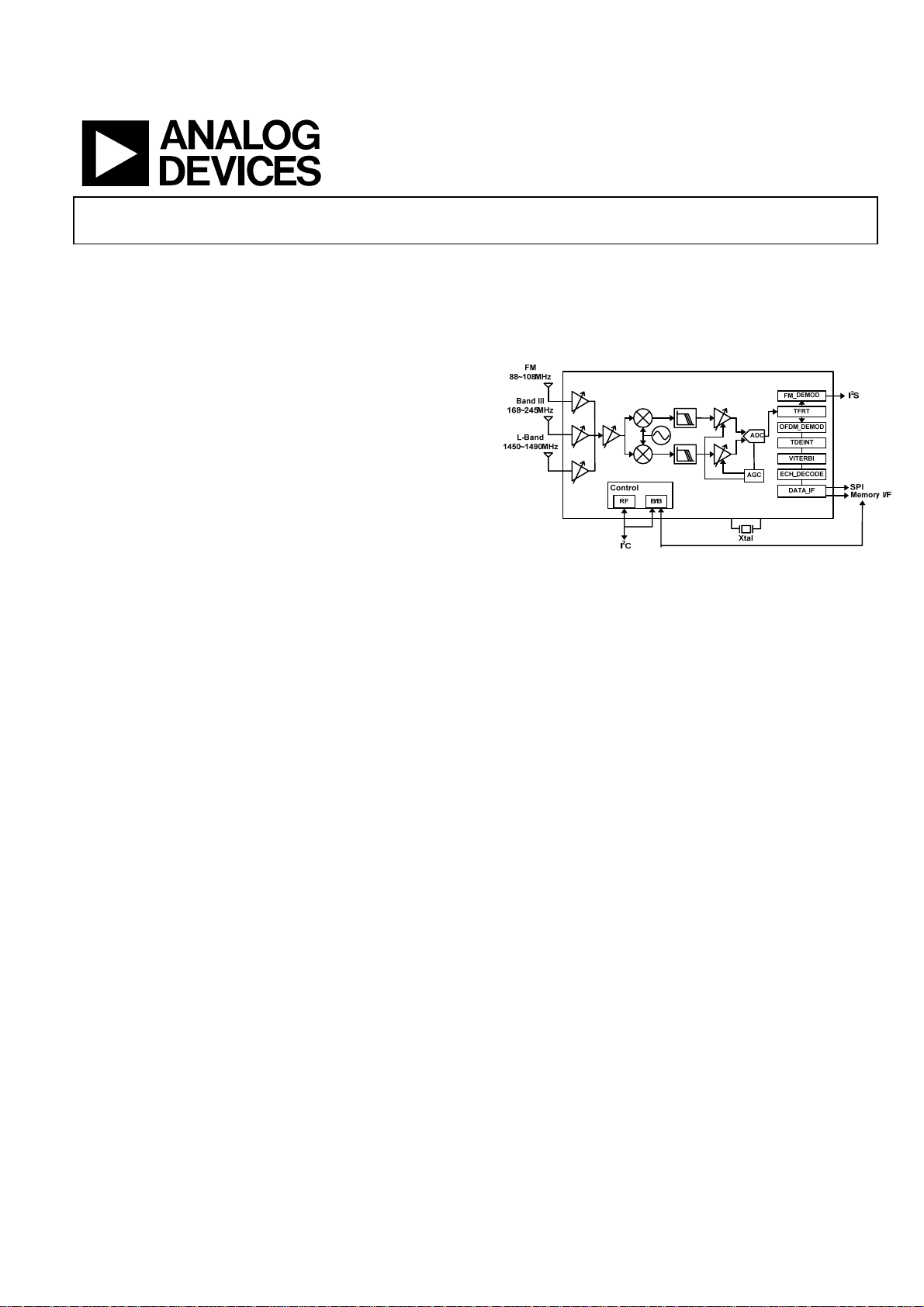

FUNCTIONAL BLOCK DIAGRAM

Figure 1. ADMTV315 Block diagram

GENERAL DESCRIPTION

ADMTV315 is a highly integrated SoC (System-on-Chip) TDMB/DAB receiver, which supports triple bands (Band III, LBand and FM). This device is composed of high performance

RF front-end tuner and OFDM (Orthogonal Frequency

Division Multiplex) demodulator in a small-size single package.

The zero-IF down-conversion RF front-end includes LNA, RF

PGA, mixer, high-resolution fractional-N PLL, on-chip low

phase noise VCO, BB PGA, and automatic cutoff frequencytuning LPF. The baseband of ADMTV315 includes 10bit ADC,

OFDM demodulator and FEC/audio/data decoders. This device

supports various serial interfaces such as I2C, I2S, and SPI to

make interface with external devices more flexible. With good

sensitivity and wide dynamic range, ADMTV315 is the best

solution for T-DMB/DAB application. It is designed to comply

with TTAS.KO-07.0024 specification of the data services for

VHF Digital Multimedia Broadcasting (T-DMB) and ETSI EN

300 401 (European DAB).

The additional features of ADMTV315 are as follows:

z Supports transmission mode 1, 2, 3 and 4

z Supports digital frequency control and timing control

z Supports simultaneous channel reception

- Maximum 64 sub-channels

- 4 enhanced channels (TDMB/ESM/EPM)

z Supports various AP (HOST) interfaces

- SRAM Base parallel interface (control + data)

2

- Serial interface (control: I

C, data: SPI)

- Single SPI interface at PIP mode

z Supports TII reception

z Supports FM reception

z Supports automatic setting with Multiplex Configuration

Information decoder

- CIF counter synchronization

- Multiplex configuration & reconfiguration

- Enhanced channel (TDMB/EPM)

z Supports full capacity channel decoding

z Minimized external components

- No external system memory

- Bit de-interleaver memory included

Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights o f Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

www.analog.com

ADMTV315 Preliminary Technical Data

TABLE OF CONTENTS

FEATURES........................................................................................ 1

GENERAL DESCRIPTION ............................................................ 1

REVISION HISTORY ..................................................................... 2

Specifications..................................................................................... 3

Operating Conditions.................................................................. 3

Electrical Charateristics............................................................... 3

Digital Timing Characteristics ................................................... 5

Electrostatic Charateristics.......................................................... 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Pin Map (BGA Package Type).................................................... 7

Pin Map (ADMTV315ACBZRL WLCSP Package Type)..... 12

Register map of RF part................................................................. 16

Theory of Operation ...................................................................... 23

RF Low Noise Amplifier (LNA), RF Programmable Gain

Amplifier (PGA) and Down-Converter.................................. 23

Local Oscillator (LO) .................................................................23

Phase Locked Loop (PLL) ......................................................... 23

Baseband Low-Pass FIlter (LPF) and Variable Gain Amplifier

(VGA) .......................................................................................... 24

Automatic Gain Control (AGC)............................................... 24

Power-Down Control ................................................................ 24

System Interface.............................................................................. 26

DATA Interface........................................................................... 26

APB Sub-System............................................................................. 43

System Architecture................................................................... 43

Address Map............................................................................... 43

APB Sub-System Components ................................................. 45

Applications..................................................................................... 50

BGA Package Type..................................................................... 50

WLCSP Package Type................................................................ 52

Outline Dimensions....................................................................... 54

BGA Package Type..................................................................... 54

WLCSP Package Type................................................................ 55

REVISION HISTORY

Rev.PrA | Page 2 of 57

Preliminary Technical Data ADMTV315

SPECIFICATIONS

OPERATING CONDITIONS

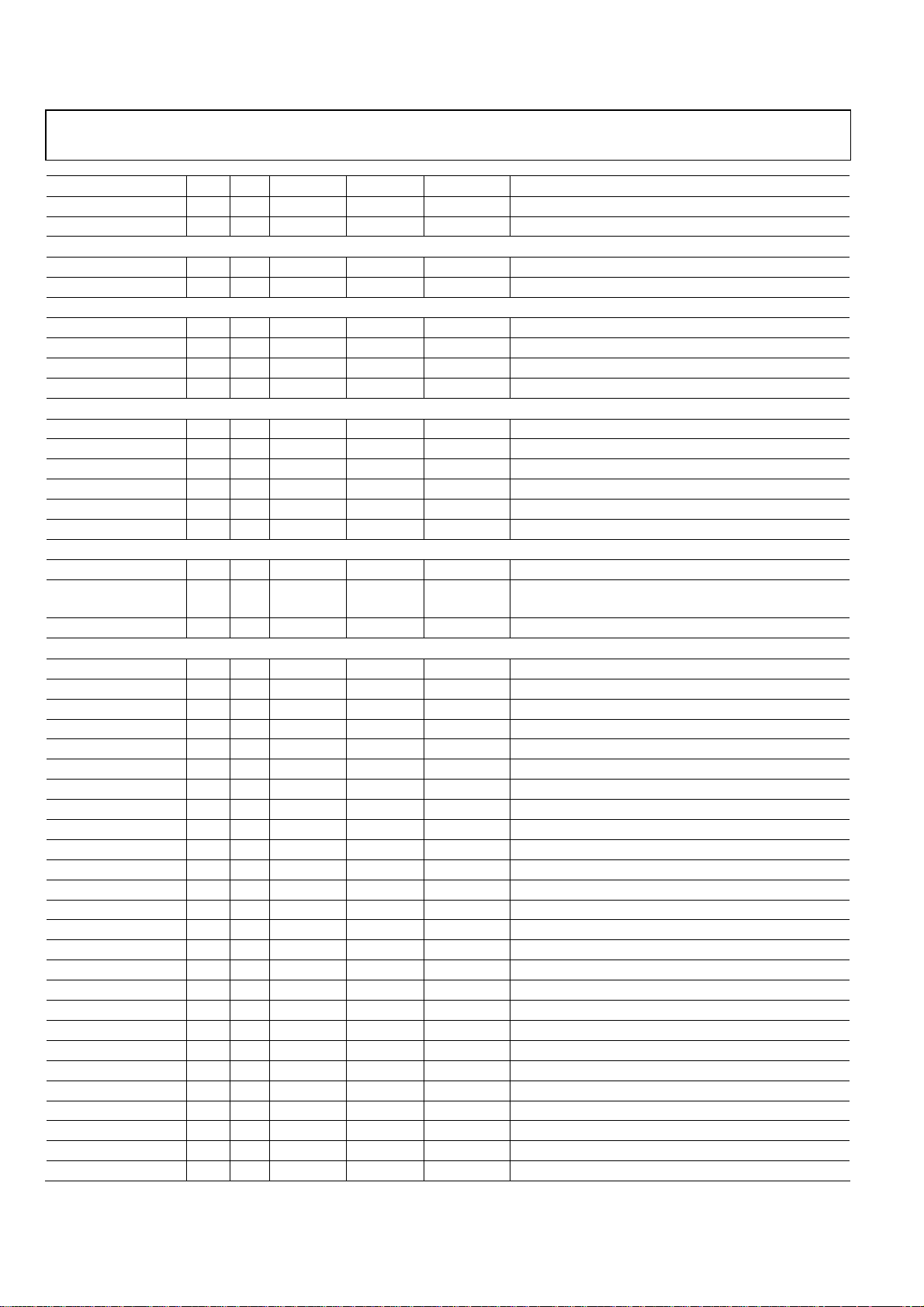

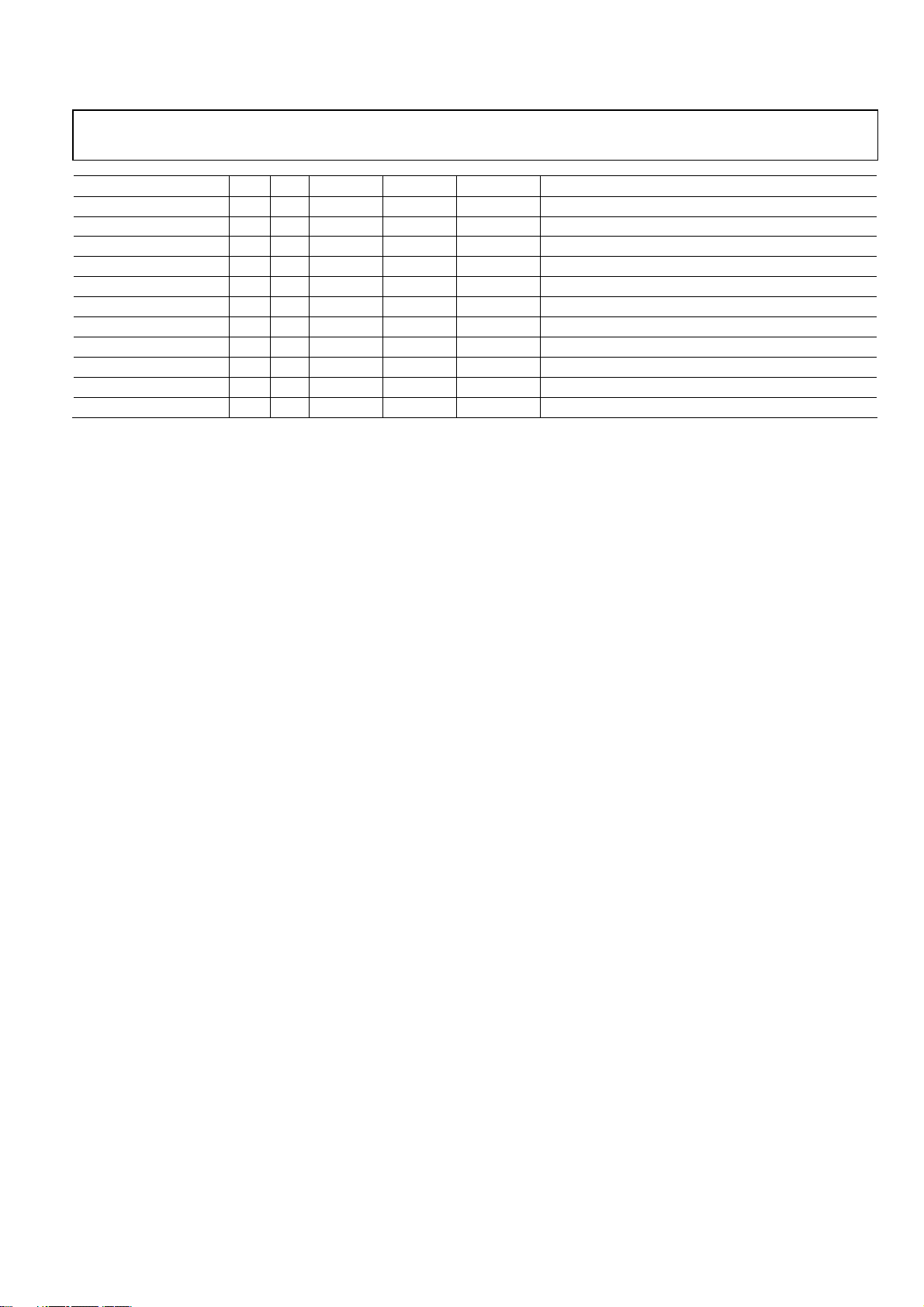

Table 1. Recommended Operating Conditions

Parameter Symbol Min Typ Max Unit

DC Supply Voltage

VDD (1.2 V)

VDD (1.8 V) 1.65 1.95 V

(2.8 V) 2.5 3.3 V

V

DD

V

IN/VOUT

Operating Ambient Temperature T

−40 85 °C

opr

ELECTRICAL CHARATERISTICS

TA = 25°C, all 1.8 V supplies = 1.65 V to 1.95 V, unless otherwise noted.

Table 2. 1.8 V DC Electrical Characteristics

Parameter Condition Symbol Min Typ Max Unit

Input High Current

Input Low Current

Input High Voltage CMOS

Input High Voltage SCMOS

Input Low Voltage CMOS

Input Low Voltage SCMOS

Output High Voltage

Output Low Voltage

Tri-state Output Leakage Current

Normal

V

= VDD

IN

Down Pull - Down

Normal

V

= VSS

IN

Up Pull - Up

= Drive Current VOH

I

OH

= Drive Current VOL

I

OL

= VDD of VSS I

V

OUT

1.1 1.3 V

1.65 1.95 V Input/Output Voltage

2.5 3.3 V

l

IH

−5 5 µA

1 30 µA

l

IL

−5 5 µA

−30 −1 µA

V

IH

V

T+

V

IL

V

T−

0.65×V

0.7×V

0.35×V

0.3×V

V

V

DD

V

DD

DD

V

DD

− 0.45 V

DD

0.45 V

OZ

−10 10 µA

V

T

= 25°C, all 2.8 V supplies = 2.5 V to 3.1 V, unless otherwise noted.

A

Table 3. 2.8 V DC Electrical Characteristics

Parameter Condition Symbol Min Typ Max Unit

Input High Current

VIN = VDD

Pull - Down Down

Input Low Current

VIN = VSS

Pull - Up Up

Input High Voltage CMOS

Input High Voltage SCMOS

Input Low Voltage CMOS

Input Low Voltage SCMOS

Output High Voltage

Output Low Voltage

Tri-state Output Leakage Current

= Drive Current VOH

I

OH

= Drive Current VOL

I

OL

= VDD of VSS I

V

OUT

Normal −5 5 µA

l

IH

5 60 µA

Normal −5 5 µA

l

IL

−60 −5 µA

V

IH

V

T+

V

IL

V

T−

0.65×V

0.7×V

0.35×V

0.3×V

V

V

DD

V

DD

V

DD

V

DD

− 0.45 V

DD

0.45 V

OZ

−10 10 µA

Rev.PrA | Page 3 of 57

ADMTV315 Preliminary Technical Data

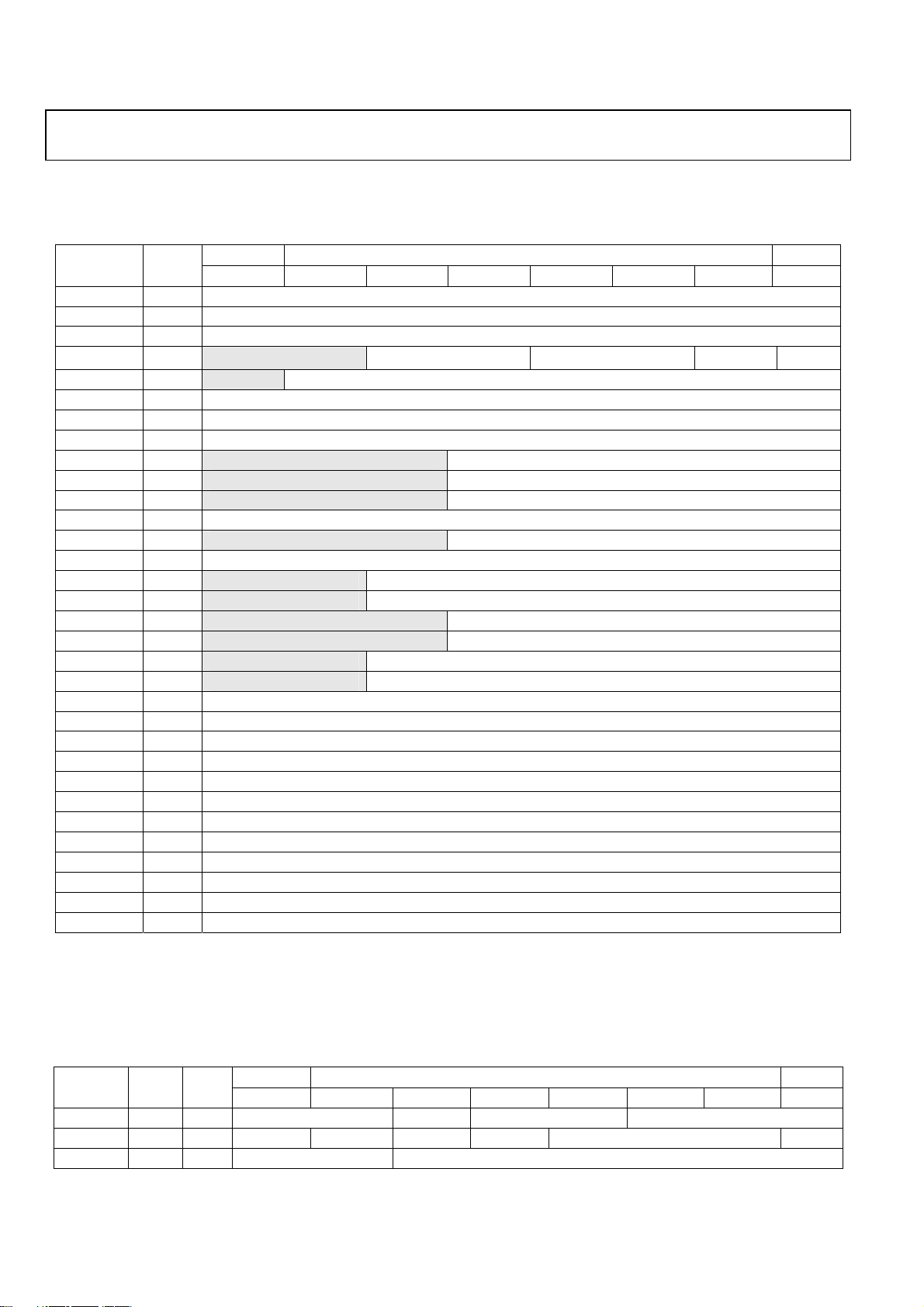

TA = 25°C, all 1.2 V supplies = 1.1 V to 1.3 V, 2.8 V supplies = 2.7 V to 2.9 V, unless otherwise noted.

Table 4. FM AC Electrical Characteristics

Parameter Symbol Min Typ Max Unit

FM RF frequency range f

FM

RF input impedance ZIN 50

Input VSWR VSWR 2:1 3:1

Sensitivity P

7 dBV

MIN

T

= 25°C, all 1.2 V supplies = 1.1 V to 1.3 V, 2.8 V supplies = 2.7 V to 2.9 V, unless otherwise noted.

A

Table 5. Band III AC Electrical Characteristics

Parameter Symbol Min Typ Max Unit

Band-III RF frequency range f

Band-III

RF input impedance ZIN 50

Input VSWR VSWR 2:1 3:1

Sensitivity @ BER P

Max Input Power @ BER P

Digital Adjacent Chanel Rejection (n+1) ACR

Digital Adjacent Chanel Rejection (n−1) ACR

Far-off (+5 MHz) FO

Far-off (−5 MHz) FO

−102 −97 dBm

MIN

+5 dBm

MAX

33 38 dBc

DN+1

33 38 dBc

DN−1

42 47 dBc

+5MHz

−5MHz

88 108 MHz

Ω

168 245 MHz

Ω

42 47 dBc

= 25°C, all 1.2 V supplies = 1.1 V to 1.3 V, 2.8 V supplies = 2.7 V to 2.9 V, unless otherwise noted.

T

A

Table 6. L-Band AC Electrical Characteristics

Parameter Symbol Min Typ Max Unit

L-Band RF frequency range f

L-Ba nd

RF input impedance ZIN 50

1450 1492 MHz

Ω

Input VSWR VSWR 2:1 3:1

Sensitivity P

Max Input Power P

Digital Adjacent Chanel Rejection (n+1) ACR

Digital Adjacent Chanel Rejection (n−1) ACR

Far-off (+5 MHz) FO

Far-off (−5 MHz) FO

−101 −97 dBm

MIN

0 dBm

MAX

30 33 dBc

DN+1

30 33 dBc

DN−1

40 47 dBc

+5MHz

−5MHz

40 47 dBc

Rev.PrA | Page 4 of 57

Preliminary Technical Data ADMTV315

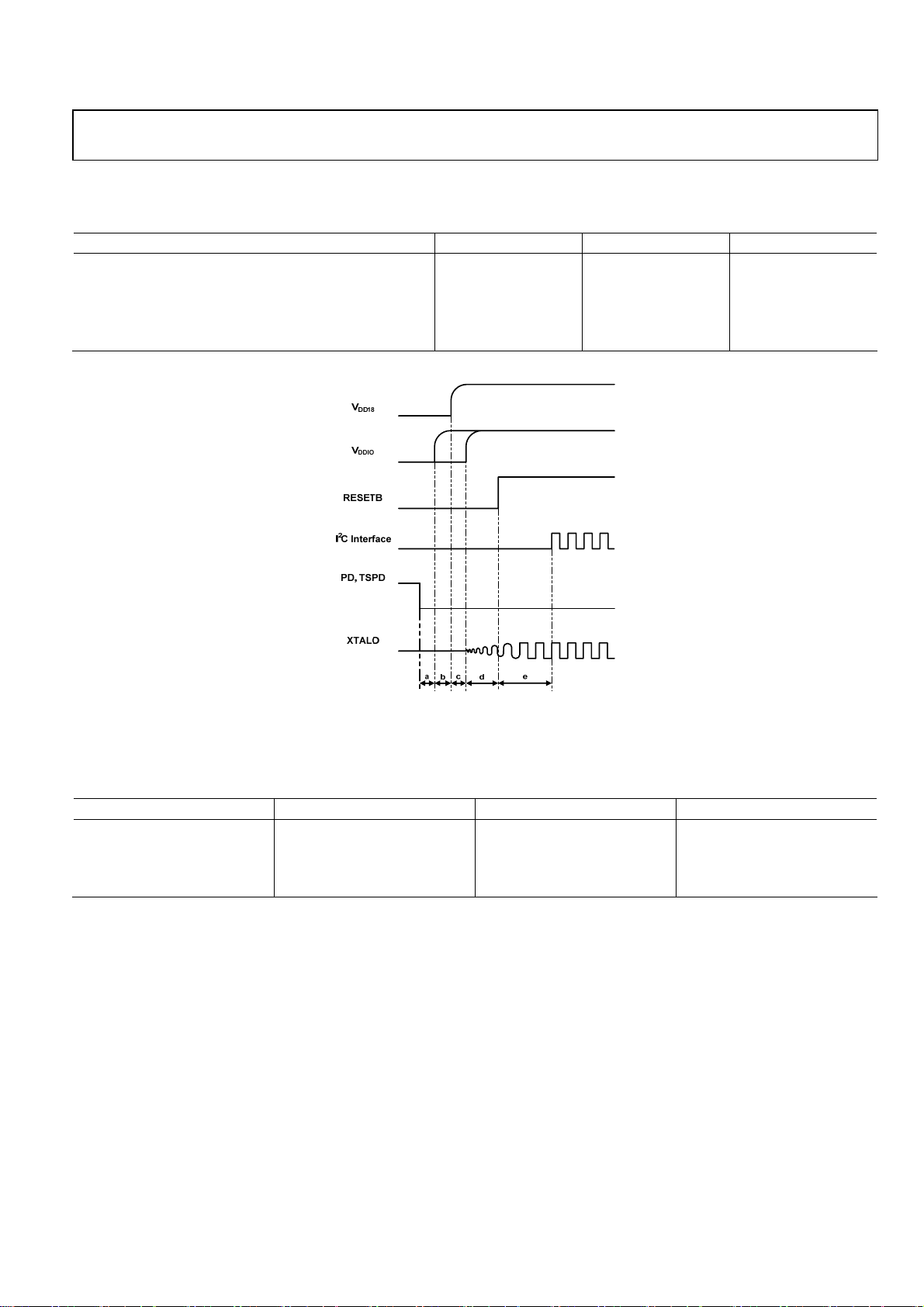

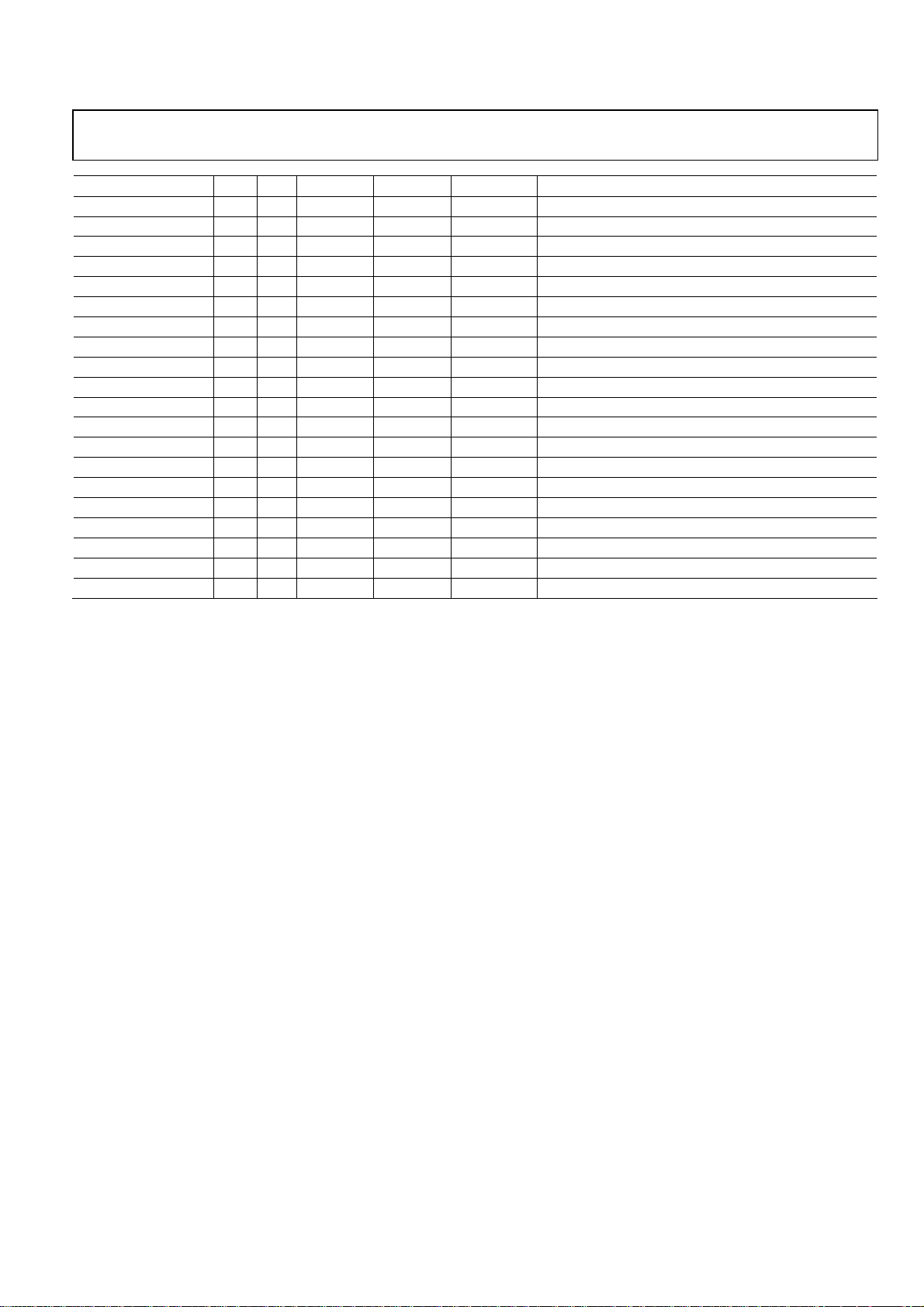

DIGITAL TIMING CHARACTERISTICS

Table 7.

Characteristic Symbol Min Unit

PD Set-up Margin a Don’t Care µs

Power up Set-up Margin for V

Power up Set-up Margin for V

RESETB Set-up Time for RESETB d 100 µs

Set-up Time for I2C Interface e 100 µs

b Don’t Care µs

DD18

c Don’t Care µs

DDIO

Figure 2. Digital Timing Diagram

ELECTROSTATIC CHARATERISTICS

Table 8.

Characteristic HBM MM Remarks

VDD positive > 1000 [V] >100 [V]

VDD negative > 1000 [V] >100 [V]

Vss positive > 1000 [V] >100 [V]

Vss negative > 1000 [V ] >100 [V ]

Rev.PrA | Page 5 of 57

ADMTV315 Preliminary Technical Data

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 9.

Parameter Symbol Rating

DC Supply Voltage

Input/Output Voltage

DC Input Current

Storage Temperature Tstg –65°C to +150°C

VDD (1.2V) 1.7 V

VDD (1.8V) 2.3 V

V

(2.8V) 3.3 V

DD

VIN/V

VIN/V

V

IN/VOUT

L

IN

OUT

OUT

(1.2V)

(1.8V)

(2.8V)

1.7 V

2.3 V

3.3 V

±200mA

Stresses above those listed under Absolute Maximum Ratings may

cause permanent damage to the device. This is a stress rating

only; functional operation of the device at these or any other

conditions above those indicated in the operational section of this

specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device

reliability.

Only one absolute maximum rating may be applied at any one

time.

ESD CAUTION

Rev.PrA | Page 6 of 57

Preliminary Technical Data ADMTV315

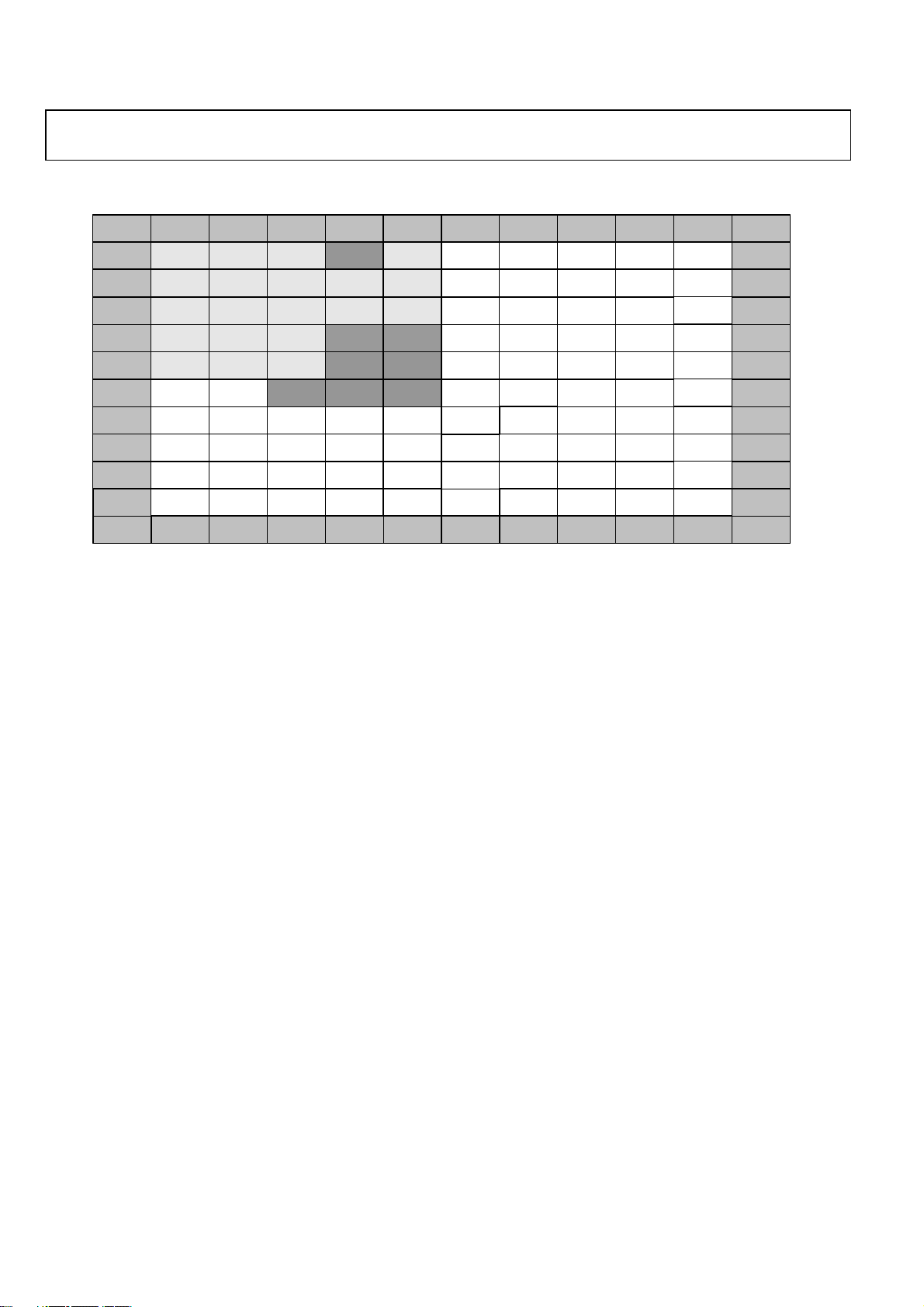

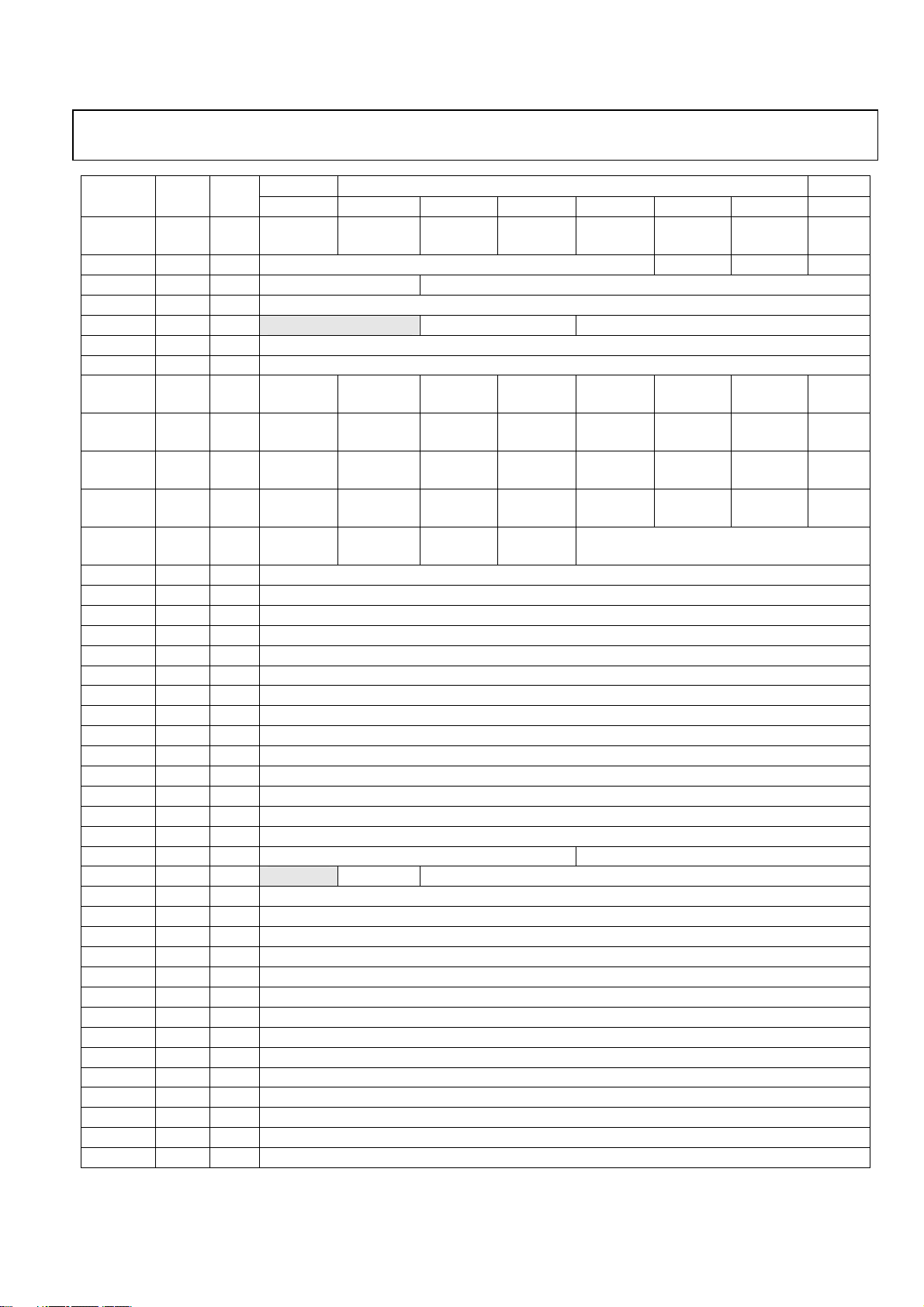

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

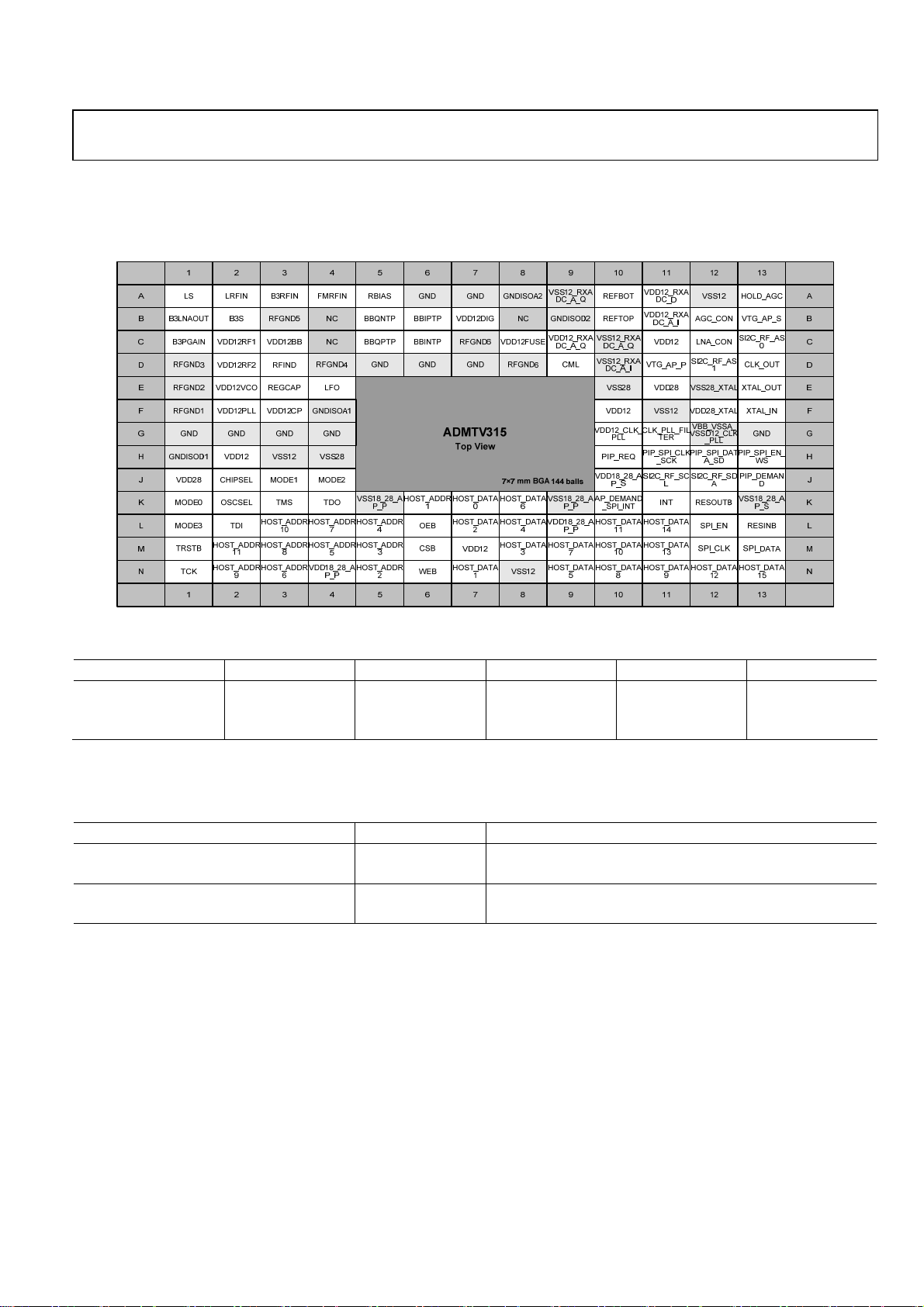

PIN MAP (BGA PACKAGE TYPE)

Figure 3. BGA Package Pin Map (Top View)

Table 10. Operation Mode

Operation Mode MODE3 MODE2 MODE1 MODE0 CHIPSEL

NORMAL 1 1 1 1 1 1

NORMAL 2 1 1 1 0 1

CHIP_DISABLE X X X X 0

Normal 1: Host Memory interface (Parallel I/F) used for DMB BB register access

2

Normal 2: I

Table 11. Dual Voltage Selection

Voltage Selection Pin Value Voltage Selection

Voltage source and IO list influenced by VTG_AP_P (Parallel I/F IO)

- Voltage source: VDD 18_28_AP_P

- IO: CSB, OEB, WEB, HOST_ VDD R (11:1), HOST_DATA (15:0)

Voltage source and IO list influenced by VTG_AP_S (Serial I/F IO and IO connected to AP)

- Voltage source: VDD 18_28_AP_S

- IO: INT, RESINB, RESOUTB, SI2C_RF_SCL, SI2C_RF_SDA, SPI_CLK, SPI_DATA, SPI_EN,

AP_DEMAND_SPI_INT, PIP_SPI_CLK_SCK, PIP_SPI_DATA_SD, PIP_SPI_EN_WS, PIP_DEMAND, PIP_REQ

C interface (Serial I/F) used for DMB BB register access (I2C is used for RF register access in normal 1 and 2.)

1 2.8 V (2.5 ~ 3.1 V) Interface Pin for Parallel Interface with AP VTG_AP_P

0 1.8 V (1.65 ~ 1.95 V) Interface Pin for Parallel Interface with AP

1 2.8 V (2.5 ~ 3.1 V) Interface Pin for Serial Interface with AP VTG_AP_S

0 1.8 V (1.65 ~ 1.95 V) Interface Pin for Serial Interface with AP

Rev.PrA | Page 7 of 57

ADMTV315 Preliminary Technical Data

Table 12. Pin Function Descriptions (BGA Package Type)

Mnemonic Ball Dir1 Voltage (V) Pad Type Drive (mA) Function

Clock, Reset, Mode, VTG, CHIPSEL (13 Pin)

MODE0 K1 I 2.8 IS-PU MODE selection 0

MODE1 J3 I 2.8 IS-PU MODE selection 1

MODE2 J4 I 2.8 IS-PU MODE selection 2

MODE3 L1 I 2.8 IS-PU MODE selection 3

XTAL_IN F13 I 2.8 IXA XTAL clock input

XTAL_OUT E13 O 2.8 OXA XTAL clock output

CLK_OUT D13 O 2.8 Z5 5 Clock output

OSCSEL K2 I 2.8 IS-PD Oscillator selection

0: 16.384 MHz

1: 19.2 MHz

RESINB L13 I 1.8/2.8 ISL Chip reset & AP I/F Hi-Z control

( when chip off, maintain RESINB=L )

RESOUTB K12 O 1.8/2.8 Z5 5 Reset output

VTG_AP_P D11 I 2.8 IS-PU AP IO voltage selection for parallel interface

VTG_AP_S B13 I 2.8 IS-PU AP IO voltage selection for serial interface

CHIPSEL J2 I 2.8 IS-PD Test chip selection in PiP test

RF Interface (3 Pin)

AGC_CON B12 O 2.8 Z5-PD 5 Automatic gain control signal

LNA_CON C12 O 2.8 Z5-PD 5 LNA step control signal

HOLD_AGC A13 O 2.8 Z5-PD 5 AGC hold control for null period

Application Processor Interface (31 Pin)

HOST_ADDR1 K6 I 1.8/2.8 IS-PD AP parallel interface address 1

HOST_ADDR2 N5 I 1.8/2.8 IS-PD AP parallel interface address 2

HOST_ADDR3 M5 I 1.8/2.8 IS-PD AP parallel interface address 3

HOST_ADDR4 L5 I 1.8/2.8 IS-PD AP parallel interface address 4

HOST_ADDR5 M4 I 1.8/2.8 IS-PD AP parallel interface address 5

HOST_ADDR6 N3 I 1.8/2.8 IS-PD AP parallel interface address 6

HOST_ADDR7 L4 I 1.8/2.8 IS-PD AP parallel interface address 7

HOST_ADDR8 M3 I 1.8/2.8 IS-PD AP parallel interface address 8

HOST_ADDR9 N2 I 1.8/2.8 IS-PD AP parallel interface address 9

HOST_ADDR10 L3 I 1.8/2.8 IS-PD AP parallel interface address 10

HOST_ADDR11 M2 I 1.8/2.8 IS-PD AP parallel interface address 11

CSB M6 I 1.8/2.8 ISL-PU Chip select

WEB N6 I 1.8/2.8 ISL-PU Write Enable

INT K11 O 1.8/2.8 O3 3 Interrupt

OEB L6 I 1.8/2.8 ISL-PU Out Enable

HOST_DATA0 K7 B 1.8/2.8 BX3-KP 3 AP parallel interface data 0

HOST_DATA1 N7 B 1.8/2.8 BX3-KP 3 AP parallel interface data 1

HOST_DATA2 L7 B 1.8/2.8 BX3-KP 3 AP parallel interface data 2

HOST_DATA3 M8 B 1.8/2.8 BX3-KP 3 AP parallel interface data 3

HOST_DATA4 L8 B 1.8/2.8 BX3-KP 3 AP parallel interface data 4

HOST_DATA5 N9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 5

HOST_DATA6 K8 B 1.8/2.8 BX3-KP 3 AP parallel interface data 6

HOST_DATA7 M9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 7

HOST_DATA8 N10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 8

HOST_DATA9 N11 B 1.8/2.8 BX3-KP 3 AP parallel interface data 9

HOST_DATA10 M10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 10

Rev.PrA | Page 8 of 57

Preliminary Technical Data ADMTV315

Mnemonic Ball Dir1 Voltage (V) Pad Type Drive (mA) Function

HOST_DATA11 L10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 11

HOST_DATA12 N12 B 1.8/2.8 BX3-KP 3 AP parallel interface data 12

HOST_DATA13 M11 B 1.8/2.8 BX3-KP 3 AP parallel interface data 13

HOST_DATA14 L11 B 1.8/2.8 BX3-KP 3 AP parallel interface data 14

HOST_DATA15 N13 B 1.8/2.8 BX3-KP 3 AP parallel interface data 15

SPI Interface (4 Pin)

SPI_CLK M12 B 1.8/2.8 BS3-PD 3 SPI interface clock signal

SPI_EN L12 B 1.8/2.8 BS3-PU 3 SPI interface enable signal

SPI_DATA M13 B 1.8/2.8 BS3-PD 3 SPI interface data signal

AP_DEMAND_SPI_INT K10 B 1.8/2.8 BS3-PU 3 SPI interface demand/interrupt

I2S Interface (3 Pin) / PiP Interface (5 Pin)

PIP_DEMAND J13 I 1.8/2.8 IS-PD PIP demand

PIP_REQ H10 O 1.8/2.8 O3 3 PIP request

PIP_SPI_CLK_SCK H11 B 1.8/2.8 BS3-PD 3 I2S Serial Clock/PIP SPI clock

PIP_SPI_EN_WS H13 B 1.8/2.8 BS3-PU 3 I2S Word Select/PIP SPI enable

PIP_SPI_DATA_SD H12 B 1.8/2.8 BS3-PD 3 I2S Serial Data/PIP SPI data

I2C Interface (4 Pin)

SI2C_RF_SCL J11 B 2.8

SI2C_RF_SDA J12 B 2.8

SI2C_RF_AS0 C13 I 2.8

SI2C_RF_AS1 D12 I 2.8

TCK N1 I 2.8 IS-PU JTAG port for clock

TDO K4 O 2.8 Z3 3 JTAG port for data output

TDI L2 I 2.8 IS-PU JTAG port for data input

TRSTB M1 I 2.8 ISL-PU JTAG port for reset

TMS K3 I 2.8 IS-PU JTAG port for mode select

CLK_PLL_FILTER G11 O AO Clock PLL Filter

REFTOP B10 O AO ADC reference top

REFBOT A10 O AO ADC reference bottom

CML D9 O AO ADC common mode level

VDD12_RXADC_A_I B11 1.2 P

VSS12_RXADC_A_I D10 1.2 G

VDD12_RXADC_A_Q C9 1.2 P

VSS12_RXADC_A_Q A9 1.2 G

VDD12_RXADC_D A11 1.2 P

VSS12_RXADC_D C10 1.2 G

VDD12 H2 1.2 P

VDD12 M7 1.2 P

VDD12 F10 1.2 P

VDD 12 C11 1.2 P

VSS12 H3 1.2 G

VSS12 N8 1.2 G

BS3-ODPUC

BS3-ODPUC

IS-PD

IS-PD

I2C interface serial clock

I2C interface serial data

I2C interface slave address 0

I2C interface slave address 1

JTAG Interface (5 Pin)

CLK64_PLL (1 Pin)

RX-ADC (3 Pin)

1.2 Analog RX-ADC Power/Ground (6 Pin)

1.2 V Digital Core Power/Ground (8 Pin)

Rev.PrA | Page 9 of 57

ADMTV315 Preliminary Technical Data

Mnemonic Ball Dir1 Voltage (V) Pad Type Drive (mA) Function

VSS12 F11 1.2 G

VSS12 A12 1.2 G

2.8 V XTAL I/O Power/Ground (2 Pin)

VDD 28_XTAL F12 2.8 P

VSS28_XTAL E12 2.8 G

2.8 V Digital I/O Power/Ground (4 Pin)

VDD 28 J1 2.8 P

VDD 28 E11 2.8 P

VSS28 H4 2.8 G

VSS28 E10 2.8 G

1.8/2.8 V Digital I/O Power/Ground (Dual Mode for Application Processor Interface) (6 Pin)

VDD 18_28_AP_P N4 1.8/2.8 P

VDD 18_28_AP_P L9 1.8/2.8 P

VSS18_28_AP_P K5 1.8/2.8 G

VSS18_28_AP_P K9 1.8/2.8 G

VDD 18_28_AP_S J10 1.8/2.8 P

VSS18_28_AP_S K13 1.8/2.8 G

1.2 V Analog CLK_PLL Power/Ground (3 Pin)

VDD 12_CLK_PLL G10 1.2 P

VBB_VSSA_VSSD12

_CLK_PLL

GND G13 1.2 G

LS A1 IO 1.2 PRF L-band LNA source

LRFIN A2 I 1.2 PRF L-band RF input

B3RFIN A3 I 1.2 PRF Band-III RF input

FMRFIN A4 I 1.2 PRF FM RF input

RBIAS A5 IO 1.2 PA Bias resistor

GND A6 G 1.2 G Ground

GND A7 G 1.2 G Ground

GNDIOA2 A8 G 1.2 G Ground

B3LNAOUT B1 O 1.2 PRF Band-III LNA output

B3S B2 IO 1.2 PRF Band-III LNA source

RFGND5 B3 G 1.2 G Ground

RFRSSI B4 O 1.2 PA RFRSSI test point

BBQNTP B5 IO 1.2 PA Baseband QN test point

BBIPTP B6 IO 1.2 PA Baseband IP test point

VDD 12DIG B7 P 1.2 PA Power supply for digital

NC B8 No connection

GNDISOD2 B9 G 1.2 G Ground

B3PGAIN C1 I 1.2 PRF Band-III PGA input

VDD 12RF1 C2 P 1.2 P Power supply for RF

VDD 12BB C3 P 1.2 P Power supply for analog baseband

BBAGC C4 I 1.2 PA Baseband AGC input (DC voltage)

BBQPTP C5 IO 1.2 PA Baseband QP test point

BBINTP C6 IO 1.2 PA Baseband IN test point

RFGND6 C7 G 1.2 G Ground

VDD 12FUSE C8 P 1.2 P Power supply for fuse

RFGND3 D1 G 1.2 G Ground

G12 1.2 G

RF Block (46 Pin)

Rev.PrA | Page 10 of 57

Preliminary Technical Data ADMTV315

Mnemonic Ball Dir1 Voltage (V) Pad Type Drive (mA) Function

VDD 12RF2 D2 P 1.2 P Power supply for RF

RFIND D3 IO 1.2 PRF RF inductor

RFGND4 D4 G 1.2 G Ground

GND D5 G 1.2 G Ground

GND D6 G 1.2 G Ground

GND D7 G 1.2 G Ground

RFGND6 D8 G 1.2 G Ground

RFGND2 E1 G 1.2 G Ground

VDD 12VCO E2 P 1.2 P Power supply for VCO

RFGCAP E3 IO 1.2 PA Regulator bypass capacitor

LFO E4 IO 1.2 PA Loop filter

RFGND1 F1 G 1.2 G Ground

VDD 12PLL F2 P 1.2 P Power supply for PLL

VDD 12CP F3 P 1.2 P Power supply for charge pump

GNDISOA1 F4 G 1.2 G Ground

GND G1 G 1.2 G Ground

GND G2 G 1.2 G Ground

GND G3 G 1.2 G Ground

GND G4 G 1.2 G Ground

GNDISOD1 H1 G 1.2 G Ground

1

P = power, G = ground, I = input, O = output, B = bi-direction, D = dual voltage, ZO = tri-state output, AI = analog input, AO = analog output, PU = pull-up, PD = pull-

down, S = Schmitt trigger, FS = fail safe IO, OD = open drain, KP = contains busholder, SI = TCXO input, XA = Xtal.

Rev.PrA | Page 11 of 57

ADMTV315 Preliminary Technical Data

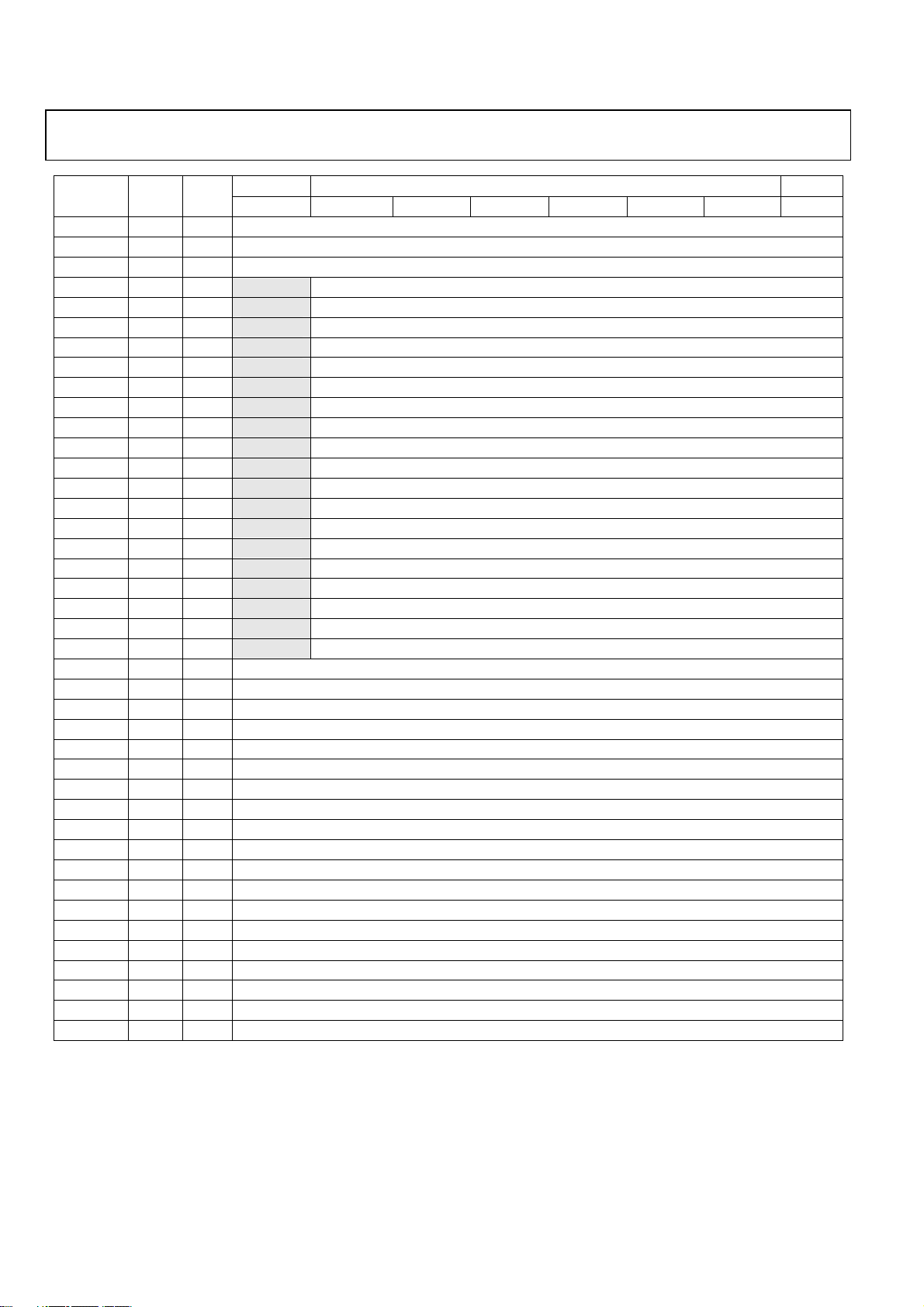

PIN MAP (ADMTV315ACBZRL WLCSP PACKAGE TYPE)

1

A

B

C

D

E

F

G

H

J

K K

NA

B3RFIN

RBIAS GND

BBIPTP BBQPTP

VDD12FUSE VDD12DIG

GND

VDD12_RX

ADC_A_Q

VDD12_RX

ADC_A_I

VDD12

VTG_AP_S

1 2 3 4 5 6 7

2 3

B3PGAIN

B3LNAOUT VDD12RF2 VDD12SYN LFO

GND

VDD12_RX

ADC_D

VTG_AP_P

SI2C_RF_

AS1

SI2C_RF_

AS0

RFIND

VDD12RF1

_BB

GND

GND

NC

GND

VDD28_

XTAL

VDD28

4 5 6 7

NC

GND

NC

NC

NC

GND GNDGND GND

VDD12

XTAL_OUT

XTAL_IN

VDD12CP

GND

VDD18_28

_AP_S

VDD12_

CLK_PLL

CLK_PLL

_FILTER

8 9

6

1

CSB

5

8

11

INT

8 9

HOST_ADDR

HOST_ADDR

HOST_ADDR

HOST_DATA

HO

HOST_DATA

HOST_DATA

HOST_DATA

SPI_DATA

GND

GND

MODE

NC

NC

NC

GND

GND

VDD12

HOST_DATA

15

SI2C_RF

_SCL

SI2C_RF_

SDA

VDD12

VDD28

VDD18_28_

AP_P

OEB

WEB

HOST_DATA

2

VDD18_28_A

P_P

HOST_DATA

14

AP_DEMAND_

SPI_INT

RESINB

CHIPSEL

HOST_ADDR9HOST_ADDR

HOST_ADDR

HOST_ADDR

HOST_DATA

HOST_DATA

HOST_DATA

SPI_EN

Figure 4.ADMTV315ACBZRL WLCSP Package Pin Map (Top View)

Table 13. Operation Mode

Operation Mode[Pin No.] MODE[C6] CHIPSEL[A8]

NORMAL 1 0 1

NORMAL2 1 1

CHIP_DISABLE X 0

Normal 1: I2C interface (Serial I/F) used for DMB Base-Band register and RF register access.

Normal 2: Host Memory interface (Parallel I/F) used for DMB Base-Band register access.

11

8

5

3

1

ST_DATA

4

7

10

13

10

HOST_ADDR

10

HOST_ADDR

7

HOST_ADDR

4

HOST_ADDR

2

HOST_DATA

0

HOST_DATA

3

HOST_DATA

6

HOST_DATA

9

HOST_DATA

12

SPI_CLK

10

A

B

C

D

E

F

G

H

J

Table 14. Dual Voltage Selection

Voltage Selection Pin [Pin No.] Value Voltage Selection

1 2.8 V (2.5 ~ 3.1 V) Interface Pin for Serial & Parallel Interface with AP VTG_AP_P[H2]

0 1.8 V (1.65 ~ 1.95 V) Interface Pin for Serial & Parallel Interface with AP

1 2.8 V (2.5 ~ 3.1 V) Interface Pin for Serial Interface with AP VTG_AP_S[K1]

0 1.8 V (1.65 ~ 1.95 V) Interface Pin for Serial Interface with AP

Voltage source and IO list influenced by VTG_AP_P (Parallel I/F IO)

- Voltage source: VDD 18_28_AP_P

- IO: CSB, OEB, WEB, HOST_ VDD R (11:1), HOST_DATA (15:0)

Voltage source and IO list influenced by VTG_AP_S (Serial I/F IO and IO connected to AP)

- Voltage source: VDD 18_28_AP_S

- IO: INT, RESINB, RESOUTB, SI2C_RF_SCL, SI2C_RF_SDA, SPI_CLK, SPI_DATA, SPI_EN,

AP_DEMAND_SPI_INT, PIP_SPI_CLK_SCK, PIP_SPI_DATA_SD, PIP_SPI_EN_WS, PIP_DEMAND, PIP_REQ

Rev.PrA | Page 12 of 57

Preliminary Technical Data ADMTV315

Table 15. Pin Function Descriptions (WLCSP Package Type)

Mnemonic Ball Dir1 Voltage (V) Pad Type Drive (mA) Function

Clock, Reset, Mode, VTG, CHIPSEL (7 Pin)

MODE C6 I 2.8 IS-PU MODE selection

XTAL_IN K4 I 2.8 IXA XTAL clock input

XTAL_OUT J4 O 2.8 OXA XTAL clock output

RESINB K7 I 1.8/2.8 ISL Chip reset & AP I/F Hi-Z control

( when chip off, maintain RESINB=L )

VTG_AP_P H2 I 2.8 IS-PU AP IO voltage selection for parallel interface

VTG_AP_S K1 I 2.8 IS-PU AP IO voltage selection for serial interface

CHIPSEL A8 I 2.8 IS-PD Test chip selection in PiP test

Application Processor Interface (31 Pin)

HOST_ADDR1 D8 I 1.8/2.8 IS-PD AP parallel interface address 1

HOST_ADDR2 D10 I 1.8/2.8 IS-PD AP parallel interface address 2

HOST_ADDR3 D9 I 1.8/2.8 IS-PD AP parallel interface address 3

HOST_ADDR4 C10 I 1.8/2.8 IS-PD AP parallel interface address 4

HOST_ADDR5 C9 I 1.8/2.8 IS-PD AP parallel interface address 5

HOST_ADDR6 C8 I 1.8/2.8 IS-PD AP parallel interface address 6

HOST_ADDR7 B10 I 1.8/2.8 IS-PD AP parallel interface address 7

HOST_ADDR8 B9 I 1.8/2.8 IS-PD AP parallel interface address 8

HOST_ADDR9 B8 I 1.8/2.8 IS-PD AP parallel interface address 9

HOST_ADDR10 A10 I 1.8/2.8 IS-PD AP parallel interface address 10

HOST_ADDR11 A9 I 1.8/2.8 IS-PD AP parallel interface address 11

CSB E8 I 1.8/2.8 ISL-PU Chip select

WEB E7 I 1.8/2.8 ISL-PU Write Enable

INT K8 O 1.8/2.8 O3 3 Interrupt

OEB D7 I 1.8/2.8 ISL-PU Out Enable

HOST_DATA0 E10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 0

HOST_DATA1 E9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 1

HOST_DATA2 F7 B 1.8/2.8 BX3-KP 3 AP parallel interface data 2

HOST_DATA3 F10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 3

HOST_DATA4 F9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 4

HOST_DATA5 F8 B 1.8/2.8 BX3-KP 3 AP parallel interface data 5

HOST_DATA6 G10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 6

HOST_DATA7 G9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 7

HOST_DATA8 G8 B 1.8/2.8 BX3-KP 3 AP parallel interface data 8

HOST_DATA9 H10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 9

HOST_DATA10 H9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 10

HOST_DATA11 H8 B 1.8/2.8 BX3-KP 3 AP parallel interface data 11

HOST_DATA12 J10 B 1.8/2.8 BX3-KP 3 AP parallel interface data 12

HOST_DATA13 J9 B 1.8/2.8 BX3-KP 3 AP parallel interface data 13

HOST_DATA14 H7 B 1.8/2.8 BX3-KP 3 AP parallel interface data 14

HOST_DATA15 H6 B 1.8/2.8 BX3-KP 3 AP parallel interface data 15

SPI Interface (4 Pin)

SPI_CLK K10 B 1.8/2.8 BS3-PD 3 SPI interface clock signal

SPI_EN J8 B 1.8/2.8 BS3-PU 3 SPI interface enable signal

SPI_DATA K9 B 1.8/2.8 BS3-PD 3 SPI interface data signal

AP_DEMAND_SPI_INT J7 B 1.8/2.8 BS3-PU 3 SPI interface demand/interrupt

I2C Interface (4 Pin)

SI2C_RF_SCL J6 B 2.8

BS3-OD-

I

Rev.PrA | Page 13 of 57

2

C interface serial clock

ADMTV315 Preliminary Technical Data

Mnemonic Ball Dir1Voltage (V) Pad Type Drive (mA) Function

PUC

SI2C_RF_SDA K6 B 2.8

SI2C_RF_AS0 K2 I 2.8

SI2C_RF_AS1 J2 I 2.8

CLK_PLL_FILTER K5 O AO Clock PLL Filter

VDD12_RXADC_A_I H1 1.2 P

VDD12_RXADC_A_Q G1 1.2 P

VDD12_RXADC_D G2 1.2 P

VDD12 A7 1.2 P

VDD12 F6 1.2 P

VDD12 H4 1.2 P

VDD 12 J1 1.2 P

VDD 28_XTAL J3 2.8 P

VDD28 B7 2.8 P

VDD28 K3 2.8 P

1.8/2.8 V Digital I/O Power/Ground (Dual Mode for Application Processor Interface) (3 Pin)

VDD18_28_AP_P C7 1.8/2.8 P

VDD18_28_AP_P G7 1.8/2.8 P

VDD18_28_AP_S H5 1.8/2.8 P

VDD12_CLK_PLL J5 1.2 P

GND A6 1.2 G

GND B6 1.2 G

GND D6 1.2 G

GND E6 1.2 G

GND F1 1.2 G

GND F2 1.2 G

GND G3 1.2 G

GND G4 1.2 G

GND G5 1.2 G

GND G6 1.2 G

GND H3 1.2 G

NA A1 Not assign

B3PGAIN A2 I 1.2 PRF Band-III PGA input

RFIND A3 IO 1.2 PRF RF inductor

VDD12CP A5 P 1.2 P Power supply for charge pump

B3RFIN B1 I 1.2 PRF Band-III RF input

B3LNAOUT B2 O 1.2 PRF Band-III LNA output

VDD12RF2 B3 P 1.2 P Power supply for RF

VDD12SYN B4 P 1.2 P Power supply for VCO, PLL, CP and REGCAP

LFO B5 IO 1.2 PA Loop filter

BS3-ODPUC

IS-PD

IS-PD

1.2 Analog RX-ADC Power(3 Pin)

1.2 V Digital Core Power (4 Pin)

2.8 V XTAL I/O Power (1 Pin)

2.8 V Digital I/O Power (2 Pin)

1.2 V Analog CLK_PLL Power (1 Pin)

BASE BAND Ground (11 Pin)

I

I

I

CLK64_PLL (1 Pin)

RF Block (20 Pin)

Rev.PrA | Page 14 of 57

2

C interface serial data

2

C interface slave address 0

2

C interface slave address 1

Preliminary Technical Data ADMTV315

Mnemonic Ball Dir1 Voltage (V) Pad Type Drive (mA) Function

RBIAS C1 IO 1.2 PA Bias resistor

GND C2 G 1.2 G Ground

VDD12RF1_BB C3 P 1.2 P Power supply for RF, analog baseband

GND C4 G 1.2 G Ground

GND C5 G 1.2 G Ground

BBIPTP D1 IO 1.2 PA Baseband IP test point

BBQPTP D2 IO 1.2 PA Baseband QP test point

GND D3 G 1.2 G Ground

VDD12FUSE E1 P 1.2 P Power supply for fuse

VDD 12DIG E2 P 1.2 P Power supply for digital

GND E3 G 1.2 G Ground

1

P = power, G = ground, I = input, O = output, B = bi-direction, D = dual voltage, ZO = tri-state output, AI = analog input, AO = analog output, PU = pull-up, PD = pull-

down, S = Schmitt trigger, FS = fail safe IO, OD = open drain, KP = contains busholder, SI = TCXO input, XA = Xtal.

Rev.PrA | Page 15 of 57

ADMTV315 Preliminary Technical Data

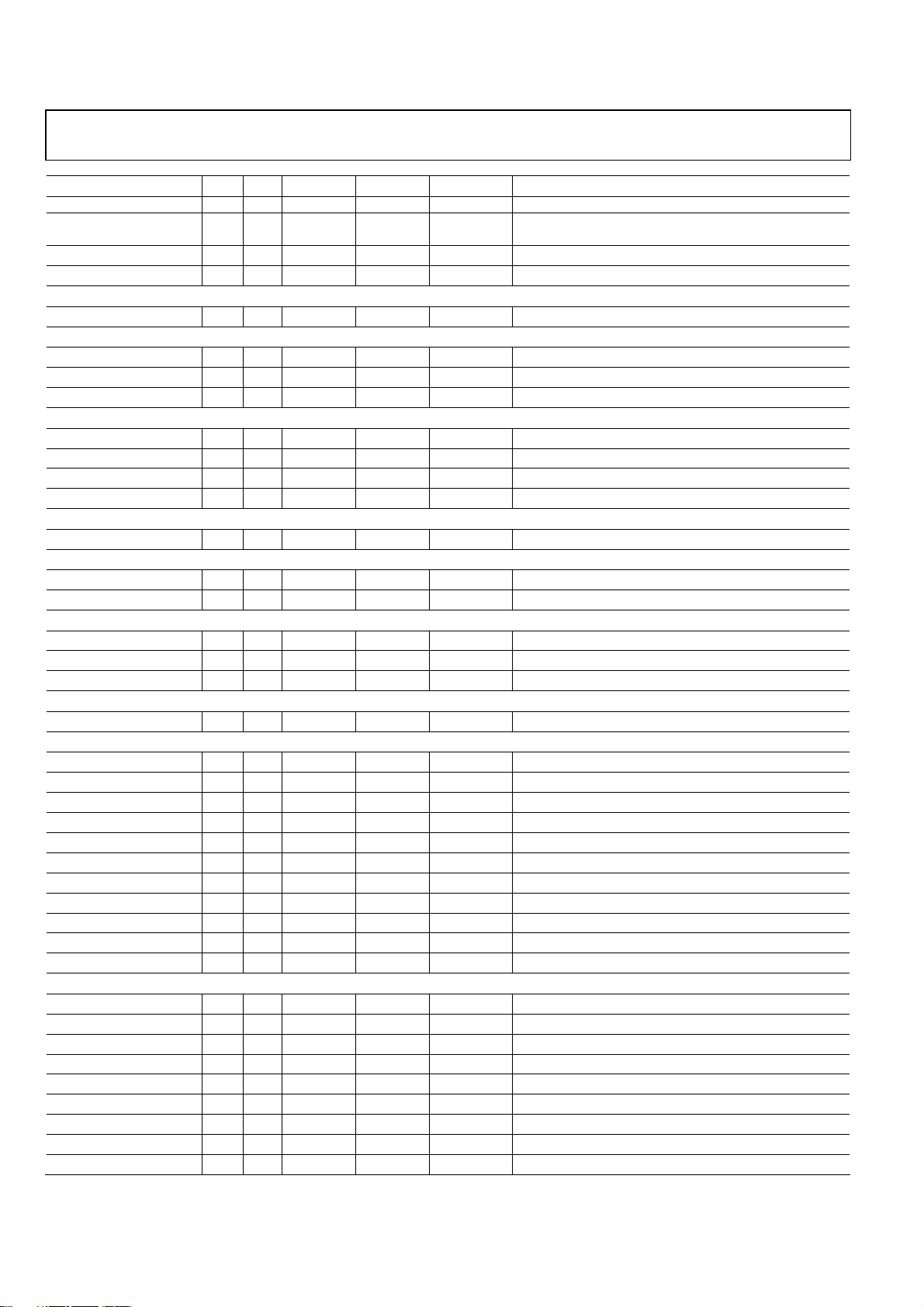

REGISTER MAP OF RF PART

Table 16. Read only Register table

Register

Name

RD00 R CHIPID1<7:0>

RD01 R CHIPID0<7:0>

RD02 R SPLITID<7:0>

RD03 R Blank Blank Blank Blank Blank

RD04 R Blank Blank

RD05 R GVBB<7:0>

RD06 R GVBBI<7:0>

RD07 R GVBBQ<7:0>

RD08 R Blank Blank

RD09 R Blank Blank

RD0A R Blank Blank

RD0B R IOFSCON<7:0>

RD0C R Blank Blank

RD0D R QOFSCON<7:0>

RD0E R Blank Blank

RD0F R Blank Blank

RD10 R Blank Blank

RD11 R Blank Blank

RD12 R Blank Blank

RD13 R Blank Blank

RD14 R READEFUSE<15:8>

RD15 R READEFUSE<7:0>

RD16 R BBAGCBBD<7:0>

RD17 R RFRSSID<7:0>

RD18 R ADJRSSID<7:0>

RD19 R RFPWRDETD<7:0>

RD1A R BBRSSID<7:0>

RD1B R BBAGCEXTD<7:0>

RD1C R TMPSNSD<7:0>

RD1D R VTUNED<7:0>

RD1E R Reserved

RD1F R Reserved

NOTES

Typ e

Reset values can be changeable without notice. Email Mobile_TV_support@analog.com to check the latest values.

MSB Address LSB

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Table 17. Read/Write Register table

Register

Name

WR20 0×6b R/W BAND<1:0> LPFBW ADJ<1:0> TOP<2:0>

WR21 0×72 R/W OB_EN EXT_EN INT_EN PDAAC CLKSEL<2:0> READEN

WR22 0×20 R/W DIVSEL<1:0> ICP<5:0>

Initial Type

MSB Address LSB

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Rev.PrA | Page 16 of 57

Preliminary Technical Data ADMTV315

Register

Name

WR23 0×b0 R/W

WR24 0×80 R/W ICP_OFS<4:0> ICP_EXT PC4 DTHEN

WR25 0×40 R/W BBPWR<1:0> N<13:8>

WR26 0×0b R/W N<7:0>

WR27 0×00 R/W Blank EXTGVBB<1:0> F<19:16>

WR28 0×00 R/W F<15:8>

WR29 0×00 R/W F<7:0>

WR2A 0×00 R/W

WR2B 0×00 R/W

WR2C 0×3f R/W

WR2D 0×ff R/W

WR2E 0×f5 R/W

WR2F 0×42 R/W Reserved

WR30 0×40 R/W Reserved

WR31 0×22 R/W Reserved

WR32 0×22 R/W Reserved

WR33 0×a4 R/W Reserved

WR34 0×64 R/W Reserved

WR35 0×8b R/W Reserved

WR36 0×40 R/W Reserved

WR37 0×3c R/W Reserved

WR38 0×bc R/W Reserved

WR39 0×6f R/W Reserved

WR3A 0×30 R/W Reserved

WR3B 0×d8 R/W Reserved

WR3C 0×00 R/W Reserved

WR3D 0×bb R/W Reserved CONBAND<4:1>

WR3E 0×7c R/W Blank CONBAND Reserved

WR3F 0×10 R/W Reserved

WR40 0×f0 R/W Reserved

WR41 0×33 R/W Reserved

WR42 0×04 R/W Reserved

WR43 0×f6 R/W Reserved

WR44 0×76 R/W Reserved

WR45 0×36 R/W Reserved

WR46 0×80 R/W Reserved

WR47 0×40 R/W Reserved

WR48 0×b0 R/W Reserved

WR49 0×40 R/W Reserved

WR4A 0×c0 R/W Reserved

WR4B 0×93 R/W Reserved

WR4C 0×40 R/W Reserved

Initial Type

MSB Address LSB

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

CTUNE_

ON

SWPD

LNA

SWPD

PLL

SWPD

LDO

TSPD

OUTBUF

TSPD

RTUNE

RTUNE_

ON

SWPD

RFPGA

SWPD

PWDET

SWPD

BGR

TSPD

VCO

TSPD

ADC

AAC_RN RN_PLL CAL_ON

SWPD

MIXER

SWPD

ADJRSSI

TSPD

LNA

TSPD

PLL

TSPD

LDO

SWPD

LPF

SWPD

RFRSSI

TSPD

RFPGA

TSPD

PWDET

TSPD

BGR

SWPD

CTUNE

SWPD

BBRSSI

TSPD

MIXER

TSPD

ADJRSSI

PCAL_

ON

SWPD

BBPGA

SWPD

TMPSNS

TSPD

LPF

TSPD

RFRSSI

Reserved

AAC_

EN

SWPD

OUTBUF

SWPD

RTUNE

TSPD

CTUNE

TSPD

BBRSSI

VCO

BIASSW

SWPD

VCO

SWPD

ADC

TSPD

BBPGA

TSPD

TMPSNS

Rev.PrA | Page 17 of 57

ADMTV315 Preliminary Technical Data

Register

Name

WR4D 0×8d R/W Reserved

WR4E 0×72 R/W Reserved

WR4F 0×d7 R/W Reserved

WR50 0×0a R/W Blank Reserved

WR51 0×7a R/W Blank Reserved

WR52 0×12 R/W Blank Reserved

WR53 0×72 R/W Blank Reserved

WR54 0×1a R/W Blank Reserved

WR55 0×56 R/W Blank Reserved

WR56 0×02 R/W Blank Reserved

WR57 0×3e R/W Blank Reserved

WR58 0×3c R/W Blank Reserved

WR59 0×2e R/W Blank Reserved

WR5A 0×4e R/W Blank Reserved

WR5B 0×36 R/W Blank Reserved

WR5C 0×32 R/W Blank Reserved

WR5D 0×3e R/W Blank Reserved

WR5E 0×1a R/W Blank Reserved

WR5F 0×3e R/W Blank Reserved

WR60 0×7f R/W Blank Reserved

WR61 0×00 R/W Blank Reserved

WR62 0×7f R/W Blank Reserved

WR63 0×8d R/W Reserved

WR64 0×72 R/W Reserved

WR65 0×c3 R/W Reserved

WR66 0×00 R/W Reserved

WR67 0×c3 R/W Reserved

WR68 0×d3 R/W Reserved

WR69 0×1a R/W Reserved

WR6A 0×2c R/W Reserved

WR6B 0×35 R/W Reserved

WR6C 0×00 R/W Reserved

WR6D 0×50 R/W Reserved

WR6E 0×00 R/W Reserved

WR6F 0×90 R/W Reserved

WR70 0×00 R/W Reserved

WR71 0×3e R/W Reserved

WR72 0×ff R/W Reserved

WR73 0×00 R/W Reserved

WR74 0×00 R/W Reserved

WR75 0×00 R/W Reserved

NOTES

Initial Type

Initial values can be changeable without notice. Email Mobile_TV_support@analog.com to check the latest values.

MSB Address LSB

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Rev.PrA | Page 18 of 57

Loading...

Loading...