Single Chip DSP

a

TARGET APPLICATIONS

Washing Machines, Refrigerator Compressors, Fans,

Pumps, Industrial Variable Speed Drives

FEATURES

26 MIPS Fixed-Point DSP Core

Single Cycle Instruction Execution (38.5 ns)

ADSP-2100 Family Code Compatible

Independent Computational Units

ALU

Multiplier/Accumulator

Barrel Shifter

Multifunction Instructions

Single Cycle Context Switch

Powerful Program Sequencer

Zero Overhead Looping

Conditional Instruction Execution

Two Independent Data Address Generator

Memory Configuration

2K 24-Bit Program Memory RAM

2K 24-Bit Program Memory ROM

1K 16-Bit Data Memory RAM

Three-Phase 16-Bit PWM Generator

16-Bit Center-Based PWM Generator

Programmable Deadtime and Narrow Pulse Deletion

Motor Controller

ADMC331

Edge Resolution to 38.5 ns

198 Hz Minimum Switching Frequency

Double/Single Duty Cycle Update Mode Control

Programmable PWM Pulsewidth

Suitable for AC Induction and Synchronous Motors

Special Signal Generation for Switched Reluctance

Motors

Special Crossover Function for Brushless DC Motors

Individual Enable and Disable for all PWM Outputs

High Frequency Chopping Mode for Transformer

Coupled Gate Drives

Hardwired Polarity Control

External PWMTRIP Pin

Seven Analog Input Channels

Acquisition Synchronized to PWM Switching

Frequency

Conversion Speed Control

24 Bits of Digital I/O Port

Bit Configurable as Input or Output

Change of State Interrupt Support

Two 8-Bit Auxiliary PWM Timers

Synchronized Analog Output

Programmable Frequency

0% to 100% Duty Cycle

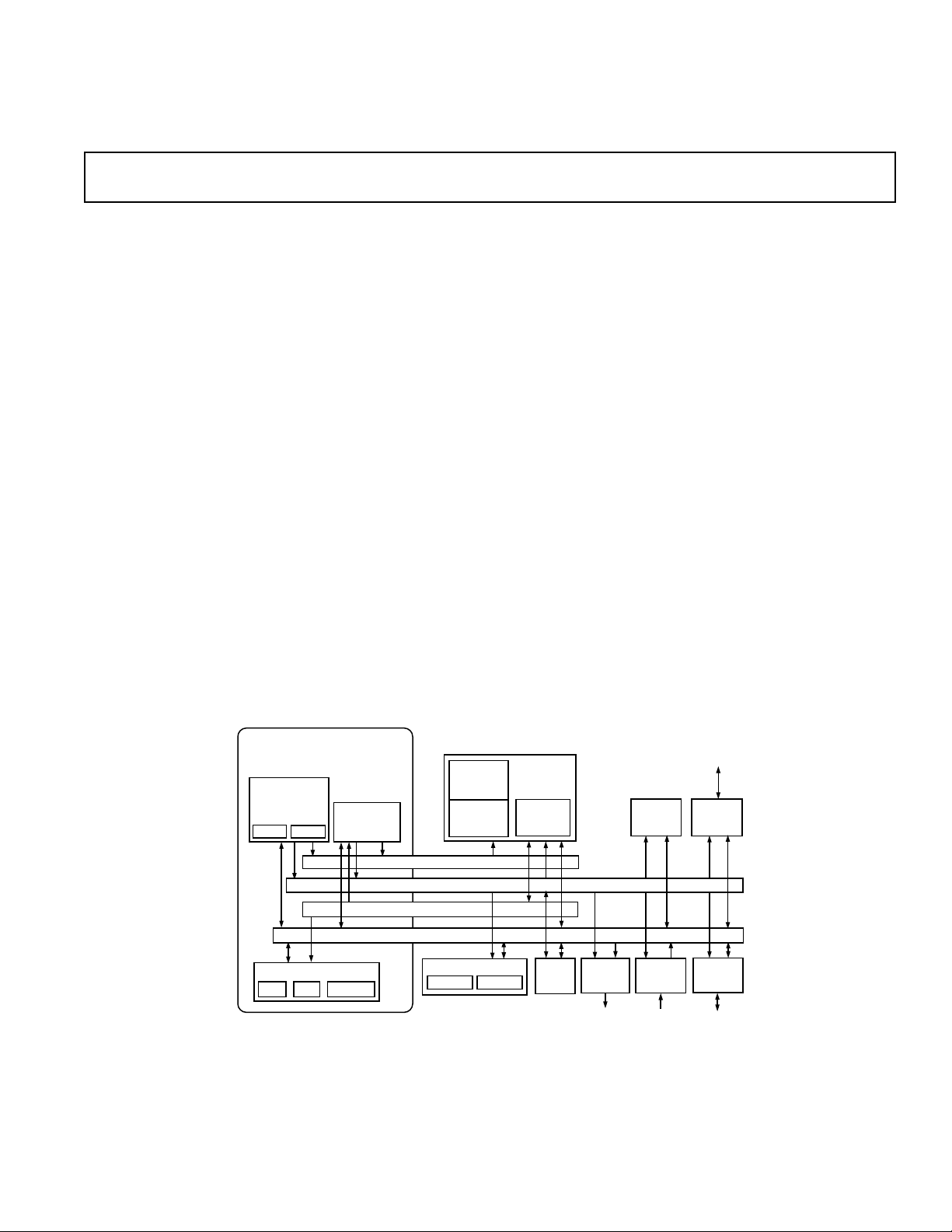

FUNCTIONAL BLOCK DIAGRAM

ADSP-2100 BASE

ARCHITECTURE

DATA

ADDRESS

GENERATORS

DAG 2

DAG 1

ARITHMETIC UNITS

MAC

ALU

PROGRAM

SEQUENCER

PROGRAM MEMORY ADDRESS

DATA MEMORY ADDRESS

PROGRAM MEMORY DATA

DATA MEMORY DATA

SHIFTER

PROGRAM

2K 24

PROGRAM

2K 24

SERIAL PORTS

SPORT 0

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

(Continued on page 7)

ROM

RAM

MEMORY

AUX

PWM

WATCH-

DOG

TIMER

7

ANALOG

INPUTS

24-BIT

PIO

16-BIT

3-PHASE

PWM

DATA

RAM

1K 16

2 8 BIT

SPORT 1

TIMER

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

ADMC331–SPECIFICATIONS

(VDD = +5 V 10%, GND = SGND = 0 V, TA = –40C to +85C, unless otherwise noted)

Parameter Min Typ Max Units Conditions/Comments

ANALOG-TO-DIGITAL CONVERTER Charging Capacitor = 1000 pF

2.5 kHz Sample Frequency

Signal Input 0.3 3.3

Resolution 12

1

2

V

Bits No Missing Codes

Converter Linearity 2 12 LSBs

Zero Offset 5 50 mV

Channel-to-Channel Comparator Match 22 mV

Comparator Delay 600 ns

Current Source 10.16 12.7 15.24 µA

Current Source Linearity 2 %

ELECTRICAL CHARACTERISTICS

V

Logic Low 0.8 V

IL

Logic High 2 V

V

IH

V

Low Level Output Voltage 0.4 V IOL = 2 mA

OL

V

Low Level Output Voltage (XTAL) 0.5 V IOL = 2 mA

OL

High Level Output Voltage 4 V I

V

OH

I

Low Level Input Current –10 µAV

IL

I

High Level Input Current 10 µAV

IH

I

Hi-Level PWMTRIP, PIO0–PIO23 Current 100 µA@ V

IH

I

Hi-Level PWMPOL/PWMSR Current 10 µA@ V

IH

I

Lo-Level PWMTRIP, PIO0–PIO23 Current 10 µA@ V

IL

Lo-Level PWMPOL/PWMSR Current 100 µA@ V

I

IL

I

Supply Current (Dynamic) 120 mA 13 MHz DSP Clock

DD

I

Supply Current (Idle) 60 mA 13 MHz DSP Clock

DD

= 0.5 mA

OH

= 0 V

IN

= V

IN

DD

= max, VIN = VDD max

DD

= max, VIN = VDD max

DD

= max, VIN = 0 V

DD

= max, VIN = 0 V

DD

REFERENCE VOLTAGE OUTPUT

Voltage Level 2.2 2.55 2.9 V 100 µA Load

Output Voltage Change T

MIN

to T

MAX

20 mV

16-BIT PWM TIMER

Counter Resolution 16 Bits

Edge Resolution (Single Update Mode) 76.9 ns 13 MHz CLKIN

Edge Resolution (Double Update Mode) 38.5 ns 13 MHz CLKIN

Programmable Deadtime Range 0 78 µs 13 MHz CLKIN

Programmable Deadtime Increments 76.9 ns 13 MHz CLKIN

Programmable Pulse Deletion Range 0 78 µs 13 MHz CLKIN

Programmable Pulse Deletion Increments 76.9 ns 13 MHz CLKIN

PWM Frequency Range 0.198 kHz 13 MHz CLKIN

PWMSYNC Pulsewidth (T

) 0.077 9.8 µs 13 MHz CLKIN

CRST

Gate Drive Chop Frequency Range 0.02 6.5 MHz 13 MHz CLKIN

AUXILIARY PWM TIMERS

Resolution 8 Bits

PWM Frequency 0.051 6.5 MHz 13 MHz CLKIN

NOTES

1

Signal input max V = 3.5 V if VDD = 5 V ± 5%.

2

Resolution varies with PWM switching frequency (13 MHz Clock in Double Update mode), 50.7 kHz = 9 bits, 6.3 kHz = 12 bits.

Specifications subject to change without notice.

–2–

REV. B

ADMC331

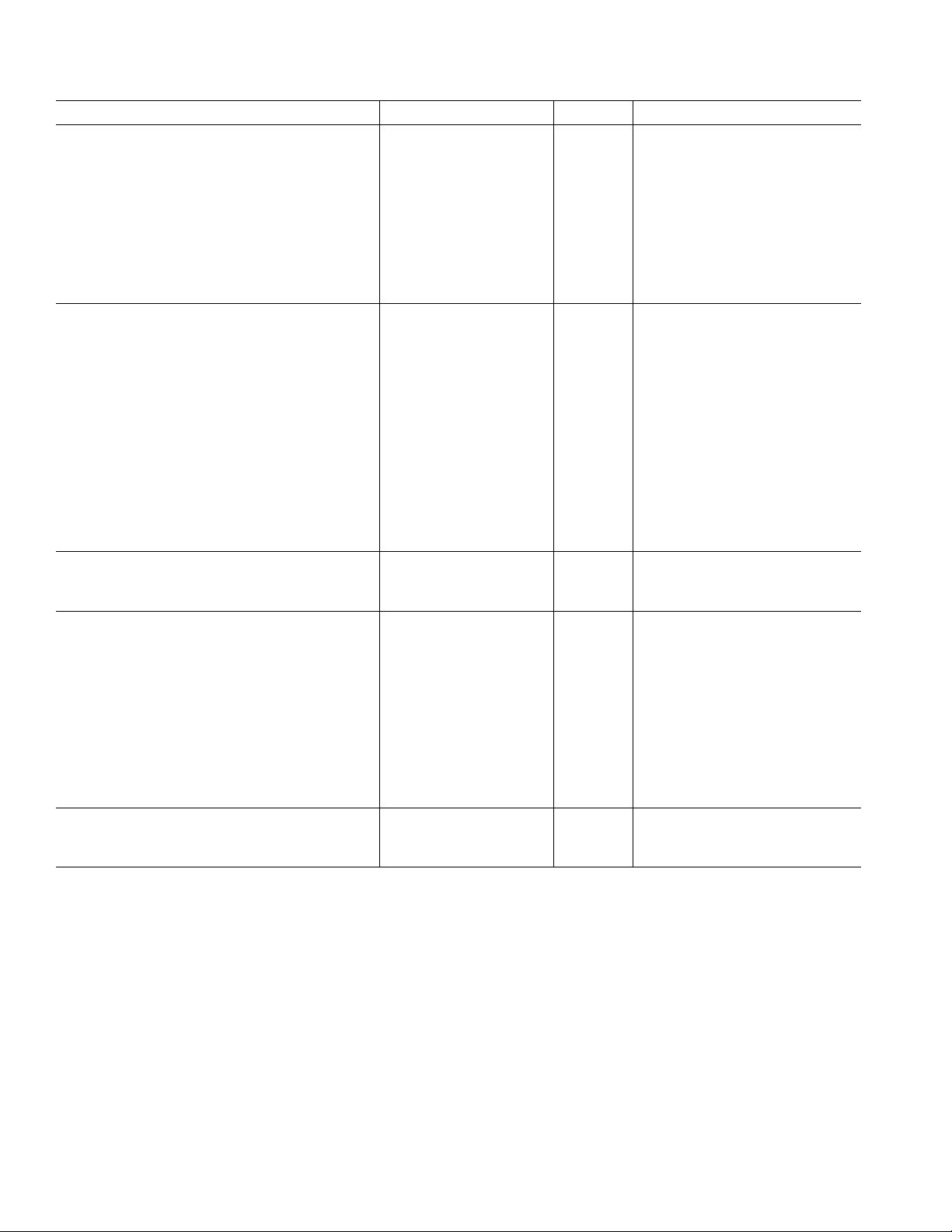

CLKIN

CLKOUT

t

CKOH

t

CKI

t

CKIH

t

CKH

t

CKL

t

CKIL

TIMING PARAMETERS

Parameter Min Max Unit

Clock Signals

tCK is defined as 0.5 t

to half the instruction rate; a 13 MHz input clock (which is equivalent to 76.9 ns)

yields a 38.5 ns processor cycle (equivalent to 26 MHz). t

of 0.5 t

period should be substituted for all relevant timing parameters to obtain

CKI

specification value.

Example: t

= 0.5 tCK – 10 ns = 0.5 (38.5 ns) – 10 ns = 9.25 ns.

CKH

Timing Requirements:

t

CKI

t

CKIL

t

CKIH

Switching Characteristics:

t

CKL

t

CKH

t

CKOH

Control Signals

Timing Requirement:

t

RSP

PWM Shutdown Signals

Timing Requirement:

t

PWMTPW

NOTE

1

Applies after power-up sequence is complete. Internal phase lock loop requires no more than 2000 CLKIN cycles assuming stable CLKIN (not including crystal

oscillator start-up time).

. The ADMC331 uses an input clock with a frequency equal

CKI

values within the range

CK

CLKIN Period 76.9 150 ns

CLKIN Width Low 20 ns

CLKIN Width High 20 ns

CLKOUT Width Low 0.5 tCK – 10 ns

CLKOUT Width High 0.5 tCK – 10 ns

CLKIN High to CLKOUT High 0 20 ns

RESET Width Low 5 t

PWMTRIP Width Low 2 t

CK

CK

1

ns

ns

Figure 1. Clock Signals

–3–REV. B

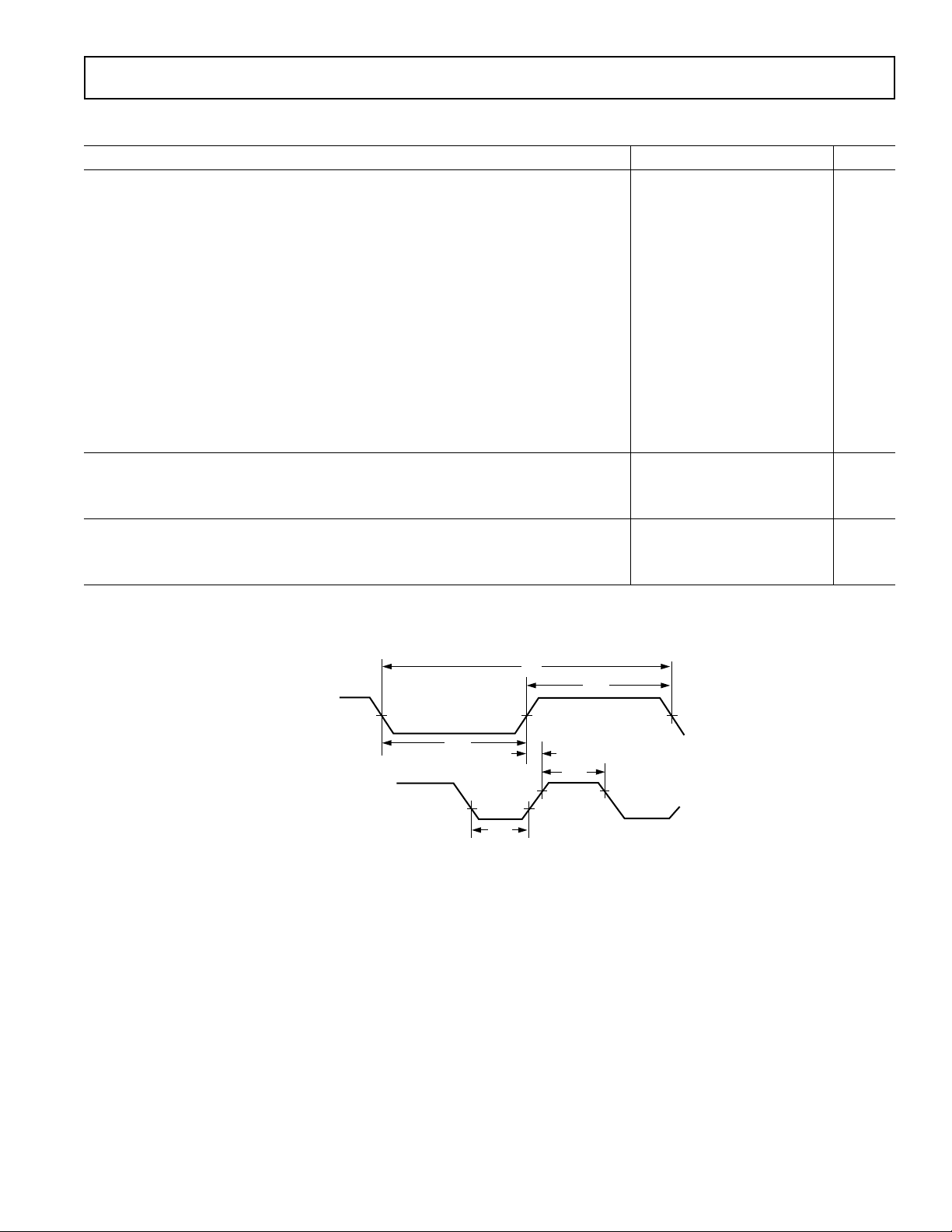

ADMC331

Parameter Min Max Unit

Serial Ports

Timing Requirements:

t

SCK

t

SCS

t

SCH

t

SCP

Switching Characteristics:

t

CC

t

SCDE

t

SCDV

t

RH

t

RD

t

SCDH

t

SCDD

t

TDE

t

TDV

t

RDV

SCLK Period 100 ns

DR/TFS/RFS Setup before SCLK Low 15 ns

DR/TFS/RFS Hold after SCLK Low 20 ns

SCLKIN Width 40 ns

CLKOUT High to SCLK

OUT

0.25 t

CK

0.25 tCK + 20 ns

SCLK High to DT Enable 0 ns

SCLK High to DT Valid 30 ns

TFS/RFS

TFS/RFS

Hold after SCLK High 0 ns

OUT

Delay from SCLK High 30 ns

OUT

DT Hold after SCLK High 0 ns

SCLK High to DT Disable 30 ns

TFS (Alt) to DT Enable 0 ns

TFS (Alt) to DT Valid 25 ns

RFS (Multichannel, Frame Delay Zero) to DT Valid 30 ns

CLKOUT

SCLK

DR

RFS

TFS

RFS

OUT

TFS

OUT

DT

TFS

(ALTERNATE

FRAME MODE)

(MULTICHANNEL MODE,

FRAME DELAY 0 [MFD = 0])

RFS

t

CC

IN

IN

t

t

RH

SCDE

t

t

TDE

t

RD

SCDV

t

t

TDV

RDV

t

CC

t

t

SCDD

t

t

SCH

SCS

t

SCDH

SCP

t

SCK

t

SCP

Figure 2. Serial Ports

–4–

REV. B

ADMC331

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage (VDD) . . . . . . . . . . . . . . . . . . –0.3 V to +7.0 V

Supply Voltage (AV

Input Voltage . . . . . . . . . . . . . . . . . . . . –0.3 V to V

Output Voltage Swing . . . . . . . . . . . . . .–0.3 V to V

) . . . . . . . . . . . . . . . . .–0.3 V to +7.0 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

*Stresses greater than those listed above may cause permanent damage to the

device. These are stress ratings only; functional operation of the device at these

or any other conditions greater than those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

Operating Temperature Range (Ambient) . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (5 sec) . . . . . . . . . . . . . . . . . . . . . .+280°C

ORDERING GUIDE

Temperature Instruction Package Package

Model Range Rate Description Option

ADMC331BST –40°C to +85°C 26 MHz 80-Lead Plastic Thin Quad Flatpack (TQFP) ST-80

ADMC331-ADVEVALKIT Development Tool Kit

ADMC331-PB Evaluation/Processor Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the ADMC331 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–5–REV. B

ADMC331

PIN FUNCTION DESCRIPTIONS

Pin Pin Pin

No. Type Name

1 O/P VREF

2 SUP AV

DD

3 GND GND

4 BIDIR PIO9

5 BIDIR PIO8

6 BIDIR PIO7

7 BIDIR PIO6

8 BIDIR PIO5

9 BIDIR PIO4

10 BIDIR PIO3

11 BIDIR PIO2

12 BIDIR PIO1

13 BIDIR PIO0

14 O/P AUX1

15 O/P AUX0

16 BIDIR PIO10

17 BIDIR PIO11

18 SUP V

DD

19 I/P PWMTRIP

20 GND GND

Pin Pin Pin

No. Type Name

21 SUP V

DD

22 GND GND

23 BIDIR PIO12

24 BIDIR PIO13

25 O/P PWMSYNC

26 O/P CL

27 O/P CH

28 O/P BL

29 O/P BH

30 O/P AL

31 O/P AH

32 BIDIR PIO14

33 BIDIR PIO15

34 BIDIR PIO16

35 SUP V

DD

36 GND GND

37 BIDIR PIO17

38 GND GND

39 BIDIR PIO18

40 GND GND

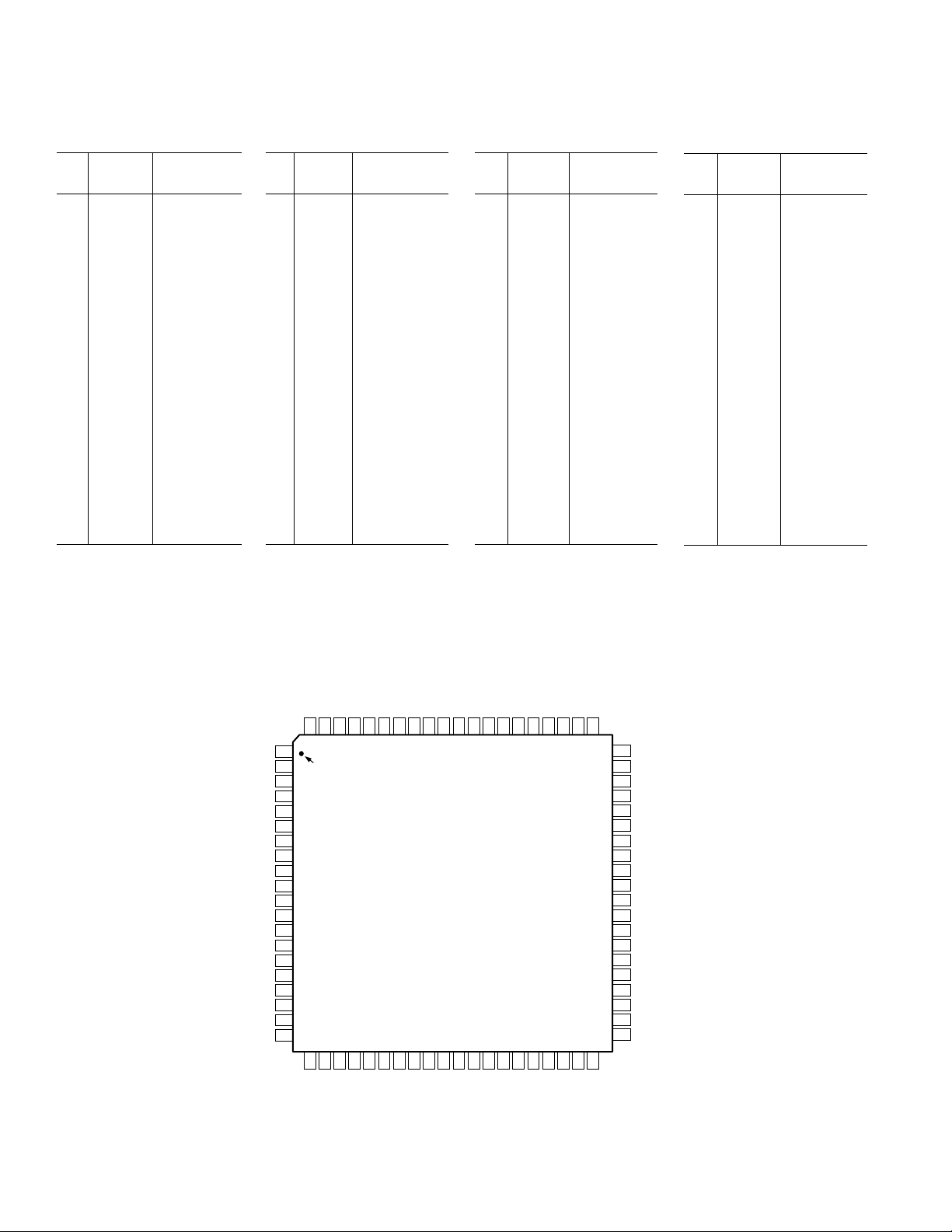

PIN CONFIGURATION

80-Lead Plastic Thin Quad Flatpack (TQFP)

Pin Pin Pin

No. Type Name

41 GND GND

42 GND GND

43 O/P XTAL

44 I/P CLKIN

45 I/P PWMPOL

46 I/P RESET

47 GND GND

48 SUP V

49 BIDIR PIO19

50 BIDIR PIO20

51 O/P CLKOUT

52 GND GND

53 O/P DT1

54 BIDIR TFS1

55 BIDIR RFS1/SROM

56 I/P DR1A

57 I/P DR1B

58 BIDIR SCLK1

59 O/P DT0

60 I/P PWMSR

(ST-80)

DD

Pin Pin Pin

No. Type Name

61 BIDIR TFS0

62 BIDIR RFS0

63 I/P DR0

64 BIDIR SCLK0

65 BIDIR PIO21

66 BIDIR PIO22

67 BIDIR PIO23

68 SUP V

DD

69 GND GND

70 GND AGND

71 I/P CAPIN

72 O/P ICONST

73 GND SGND

74 I/P V1

75 I/P V2

76 I/P V3

77 I/P VAUX0

78 I/P VAUX1

79 I/P VAUX2

80 I/P VAUX3

VREF

AV

GND

PIO9

PIO8

PIO7

PIO6

PIO5

PIO4

PIO3

PIO2

PIO1

PIO0

AUX1

AUX0

PIO10

PIO11

V

PWMTRIP

GND

VAUX3

80

7978777675

1

PIN 1

2

DD

DD

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

DD

V

GND

PIO12

25

24

PIO13

PWMSYNC

V2

26

CL

V1

74

27

CH

CAPIN

ICONST

SGND

73

727170

ADMC331

TOP VIEW

(Not to Scale)

30

28

29

AL

BL

BH

V3

VAUX0

VAUX1

VAUX2

DD

V

GND

AGND

31

AH

PIO22

PIO23

69686766656463

32

35

33

34

DD

V

PIO16

PIO15

PIO14

PIO21

36

GND

SCLK0

37

38

GND

PIO17

DR0

RFS0

62

39

GND

PIO18

TFS0

61

40

60

PWMSR

DT0

59

SCLK1

58

DR1B

57

DR1A

56

55

RFS1/ SROM

TFS1

54

53

DT1

GND

52

51

CLKOUT

50

PIO20

PIO19

49

V

48

DD

GND

47

46

RESET

45

PWMPOL

CLKIN

44

XTAL

43

GND

42

GND

41

–6–

REV. B

ADMC331

(Continued from page 1)

Two Programmable Operational Modes

Independent Mode

Offset Mode

16-Bit Watchdog Timer

Programmable 16-Bit Internal Timer with Prescaler

Two Double Buffered Synchronous Serial Ports

Four Boot Load Protocols via SPORT1

2

PROM/SROM Booting

E

UART Booting (SCI Compatible) with Autobaud

Feature

Synchronous Master Booting with Autobaud Feature

Synchronous Slave Booting with Autobaud Feature

Debugger Interface via SPORT1 with Autobaud (UART

and Synchronous Supported)

ROM Utilities

Full Debugger for Program Development

Preprogrammed Math Functions

Preprogrammed Motor Control Functions—Vector

Transformations

80-Lead TQFP Package

Industrial Temperature Range –40C to +85C

GENERAL DESCRIPTION

The ADMC331 is a low cost, single-chip DSP-based controller,

suitable for ac induction motors, permanent magnet synchronous motors, brushless dc motors, and switched reluctance

motors. The ADMC331 integrates a 26 MIPS, fixed-point DSP

core with a complete set of motor control peripherals that permits fast, efficient development of motor controllers.

The DSP core of the ADMC331 is the ADSP-2171, which is

completely code compatible with the ADSP-2100 DSP family

and combines three computational units, data address generators and a program sequencer. The computational units comprise an ALU, a multiplier/accumulator (MAC) and a barrel

shifter. The ADSP-2171 adds new instructions for bit manipulation, multiplication (X squared), biased rounding and global

interrupt masking. In addition, two flexible, double-buffered,

bidirectional, synchronous serial ports are included in the

ADMC331.

The ADMC331 provides 2K × 24-bit program memory RAM,

2K × 24-bit program memory ROM and 1K × 16-bit data

memory RAM. The program and data memory RAM can be

boot loaded through the serial port from a Serial ROM (SROM),

E2PROM, asynchronous (UART) connection or synchronous

connection. The program memory ROM includes a monitor

that adds software debugging features through the serial port. In

addition, a number of preprogrammed mathematical and motor

control functions are included in the program memory ROM.

The motor control peripherals of the ADMC331 include a

16-bit center-based PWM generation unit that can be used to

produce high accuracy PWM signals with minimal processor

overhead and seven analog input channels. The device also

contains two auxiliary 8-bit PWM channels, a 16-bit watchdog timer and expanded capability through the serial ports

and 24-bit digital I/O ports.

–7–REV. B

ADMC331

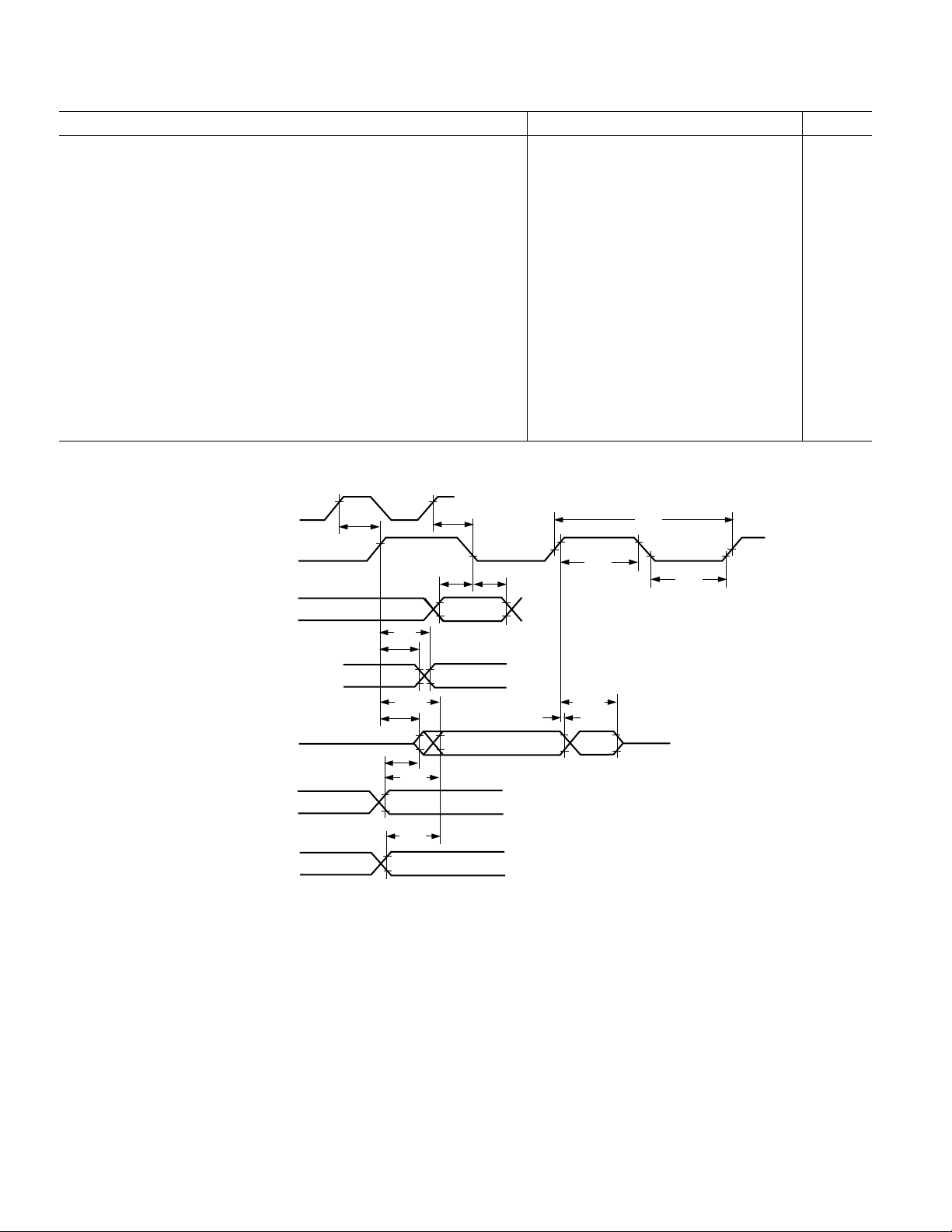

DATA

ADDRESS

GENERATOR

#1

INPUT REGS

ALU

OUTPUT REGS

DATA

ADDRESS

GENERATOR

#2

INPUT REGS

OUTPUT REGS

MAC

INSTRUCTION

PROGRAM

SEQUENCER

16

R BUS

REGISTER

OUTPUT REGS

14

14

24

BUS

EXCHANGE

16

INPUT REGS

SHIFTER

PM ROM

2K 24

PM RAM

2K 24

CONTROL

LOGIC

PMA BUS

DMA BUS

PMD BUS

DMD BUS

TRANSMIT REG

RECEIVE REG

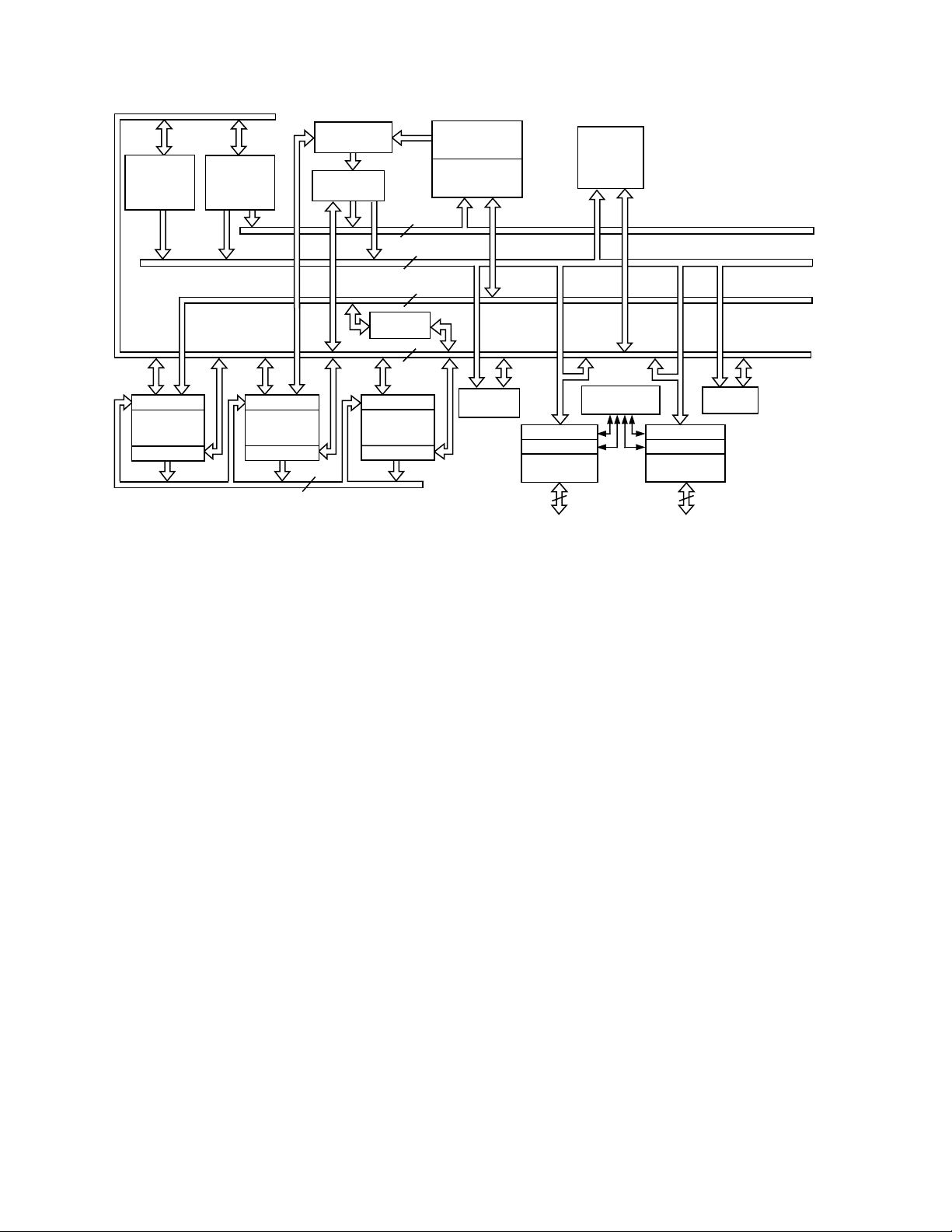

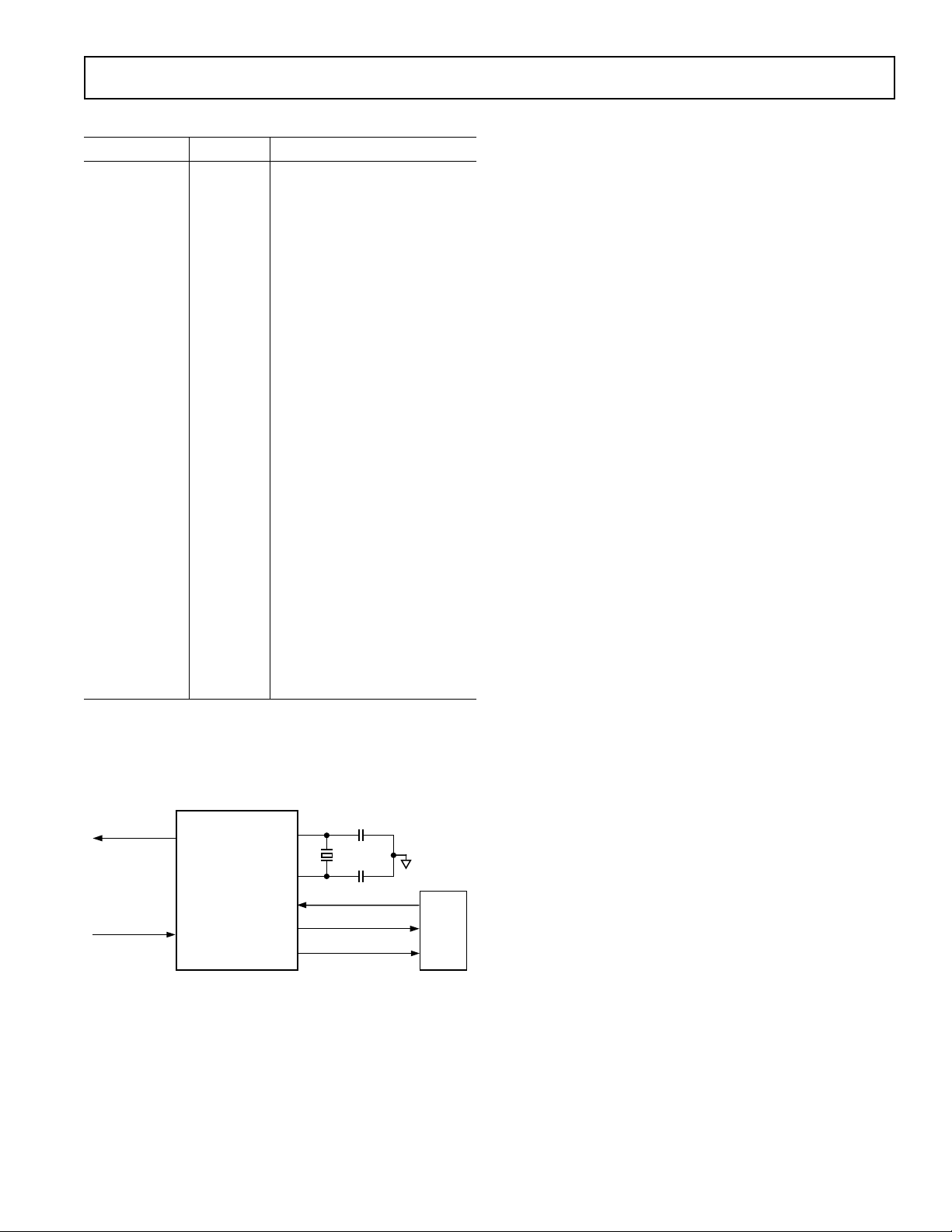

Figure 3. DSP Core Block Diagram

SERIAL

PORT 0

5

DM RAM

1K 16

COMPANDING

CIRCUITRY

TRANSMIT REG

RECEIVE REG

SERIAL

PORT 1

6

TIMER

DSP CORE ARCHITECTURE OVERVIEW

Figure 3 is an overall block diagram of the DSP core of the

ADMC331, which is based on the fixed-point ADSP-2171. The

flexible architecture and comprehensive instruction set of the

ADSP-2171 allows the processor to perform multiple operations

in parallel. In one processor cycle (38.5 ns with a 13 MHz

CLKIN) the DSP core can:

• Generate the next program address.

• Fetch the next instruction.

• Perform one or two data moves.

• Update one or two data address pointers.

• Perform a computational operation.

This all takes place while the processor continues to:

• Receive and transmit through the serial ports.

• Decrement the interval timer.

• Generate three-phase PWM waveforms for a power inverter.

• Generate two signals using the 8-bit auxiliary PWM timers.

• Acquire four analog signals.

• Decrement the watchdog timer.

The processor contains three independent computational units:

the arithmetic and logic unit (ALU), the multiplier/accumulator

(MAC) and the shifter. The computational units process 16-bit

data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and

logic operations; division primitives are also supported. The

MAC performs single-cycle multiply, multiply/add, multiply/

subtract operations with 40 bits of accumulation. The shifter

performs logical and arithmetic shifts, normalization, denormalization

and derive exponent operations. The shifter can be used to efficiently implement numeric format control including floatingpoint representations.

The internal result (R) bus directly connects the computational

units so that the output of any unit may be the input of any unit

on the next cycle.

A powerful program sequencer and two dedicated data address

generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps and

subroutine calls and returns in a single cycle. With internal loop

counters and loop stacks, the ADMC331 executes looped code

with zero overhead; no explicit jump instructions are required

to maintain the loop.

Two data address generators (DAGs) provide addresses for

simultaneous dual operand fetches from data memory and

program memory. Each DAG maintains and updates four address pointers (I registers). Whenever the pointer is used to

access data (indirect addressing), it is post-modified by the

value in one of four modify (M registers). A length value may

be associated with each pointer (L registers) to implement automatic modulo addressing for circular buffers. The circular buffering feature is also used by the serial ports for automatic data

transfers to and from on-chip memory. DAG1 generates only

data memory address but provides an optional bit-reversal

capability. DAG2 may generate either program or data memory

addresses, but has no bit-reversal capability.

Efficient data transfer is achieved with the use of five internal

buses:

• Program Memory Address (PMA) Bus

• Program Memory Data (PMD) Bus

• Data Memory Address (DMA) Bus

• Data Memory Data (DMD) Bus

• Result (R) Bus

–8–

REV. B

ADMC331

Program memory can store both instructions and data, permitting the ADMC331 to fetch two operands in a single cycle—

one from program memory and one from data memory. The

ADMC331 can fetch an operand from on-chip program memory

and the next instruction in the same cycle.

The ADMC331 writes data from its 16-bit registers to the 24-bit

program memory using the PX register to provide the lower

eight bits. When it reads data (not instructions) from 24-bit

program memory to a 16-bit data register, the lower eight bits

are placed in the PX register.

The ADMC331 can respond to a number of distinct DSP core

and peripheral interrupts. The DSP core interrupts include

serial port receive and transmit interrupts, timer interrupts,

software interrupts and external interrupts. The motor control

peripherals also produce interrupts to the DSP core.

The two serial ports (SPORTs) provide a complete synchronous

serial interface with optional companding in hardware and a

wide variety of framed and unframed data transmit and receive

modes of operation. Each SPORT can generate an internal

programmable serial clock or accept an external serial clock.

Boot loading of both the program and data memory RAM of the

ADMC331 is through the serial port SPORT1.

A programmable interval counter is also included in the DSP

core and can be used to generate periodic interrupts. A 16-bit

count register (TCOUNT) is decremented every n processor

cycle, where n–1 is a scaling value stored in the 8-bit TSCALE

register. When the value of the counter reaches zero, an interrupt is

generated and the count register is reloaded from a 16-bit period register (TPERIOD).

The ADMC331 instruction set provides flexible data moves and

multifunction (one or two data moves with a computation) instructions. Each instruction is executed in a single 38.5 ns processor

cycle (for a 13 MHz CLKIN). The ADMC331 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools support program

development. For further information on the DSP core, refer to

the ADSP-2100 Family User’s Manual, Third Edition, with par-

ticular reference to the ADSP-2171.

Serial Ports

The ADMC331 incorporates two complete synchronous serial

ports (SPORT0 and SPORT1) for serial communication and

multiprocessor communication. Following is a brief list of capabilities of the ADMC331 SPORTs. Refer to the ADSP-2100

Family User’s Manual, Third Edition, for further details.

• SPORTs are bidirectional and have a separate, double-buffered

transmit and receive section.

• SPORTs can use an external serial clock or generate their

own serial clock internally.

• SPORTs have independent framing for the receive and transmit sections. Sections run in a frameless mode or with frame

synchronization signals internally or externally generated. Frame

synchronization signals are active high or inverted, with either of

two pulsewidths and timings.

• SPORTs support serial data word lengths from 3 bits to 16

bits and provide optional A-law and µ-law companding ac-

cording to ITU (formerly CCITT) recommendation G.711.

• SPORT receive and transmit sections can generate unique

interrupts on completing a data word transfer.

• SPORTs can receive and transmit an entire circular buffer of

data with only one overhead cycle per data word. An interrupt

is generated after a data buffer transfer.

• SPORT0 has a multichannel interface to selectively receive

and transmit a 24-word or 32-word, time-division multiplexed, serial bitstream.

• SPORT1 can be configured to have two external interrupts

(IRQ0 and IRQ1), and the Flag In and Flag Out signals. The

internally generated serial clock may still be used in this configuration.

• SPORT1 is the default input for program and data memory

boot loading. The RFS1 pin can be configured internal to the

ADMC331 as an SROM/E

• SPORT1 has two data receive pins (DR1A and DR1B). The

DR1A pin is intended for synchronous boot loading from the

external SROM/E

data receive pin for boot loading from an external asynchronous (UART) connection (SCI compatible), an external

synchronous connection as the data receive pin for an external

device communicating over the debugger interface, or as the

data receive pin for a general purpose SPORT after booting.

These two pins are internally multiplexed onto the one DR1

port of the SPORT. The particular data receive pin selected is

determined by a bit in the MODECTRL register.

2

PROM. The DR1B pin can be used as the

2

PROM reset signal.

–9–REV. B

ADMC331

PIN FUNCTION DESCRIPTION

The ADMC331 is available in an 80-lead TQFP package. Table I

contains the pin descriptions.

Table I. Pin List

Pin #

Group of Input/

Name Pins Output Function

RESET 1 I/P Processor Reset Input.

SPORT0 5 I/P, O/P Serial Port 0 Pins (TFS0, RFS0,

DT0, DR0, SCLK0).

SPORT1 6 I/P, O/P Serial Port 1 Pins (TFS1, RFS1,

DT1, DR1A, DR1B, SCLK1).

CLKOUT 1 O/P Processor Clock Output.

CLKIN, XTAL 2 I/P, O/P External Clock or Quartz Crystal

Connection Point.

PIO0–PIO23 24 I/P, O/P Digital I/O Port Pins.

AUX0–AUX1 2 O/P Auxiliary PWM Outputs.

AH–CL 6 O/P PWM Outputs.

PWMTRIP 1 I/P PWM Trip Signal.

PWMPOL 1 I/P PWM Polarity Pin.

PWMSYNC 1 O/P PWM Synchronization Pin.

PWMSR 1 I/P Switch Reluctance Mode Pin.

V1–V3, 3 I/P Analog Inputs.

VAUX0–VAUX3 4 I/P Auxiliary Analog Input

CAPIN 1 I/P ADC Capacitor Input.

ICONST 1 O/P ADC Constant Current Source.

VREF 1 O/P Voltage Reference Output.

AV

DD

AGND 1 Analog Ground.

SGND 1 Analog Signal Ground

V

DD

GND 11

INTERRUPT OVERVIEW

1 Analog Power Supply.

5 Digital Power Supply.

Digital Ground.

The ADMC331 can respond to 34 different interrupt sources

with minimal overhead, 8 of which are internal DSP core

interrupts and 26 interrupts from the motor control peripherals.

The 8 DSP core interrupts are SPORT0 receive and transmit,

SPORT1 receive (or IRQ0) and transmit (or IRQ1), the internal

timer and two software interrupts. The motor control peripheral

interrupts are the 24 peripheral I/Os and two from the PWM

(PWMSYNC pulse and PWMTRIP). All motor control interrupts are multiplexed into the DSP core through the peripheral

IRQ2 interrupt. The interrupts are internally prioritized and individually maskable. A detailed description of the entire interrupt system of the ADMC331 is given later, following a more

detailed description of each peripheral block.

Memory Map

The ADMC331 has two distinct memory types: program

memory and data memory. In general, program memory contains

user code and coefficients, while the data memory is used to store

variables and data during program execution. Both program

memory RAM and ROM are provided on the ADMC331. Program memory RAM is arranged as one contiguous 2K × 24-bit

block, starting at address 0x0000. Program memory ROM is

located at address 0x0800. Data memory is arranged as a 1K ×

16-bit block starting at address 0x3800. The motor control

peripherals are memory mapped into a region of the data

memory space starting at 0x2000. The complete program and

data memory maps are given in Tables II and III, respectively.

Table II. Program Memory Map

Memory

Address Range Type Function

0x0000–0x002F RAM Interrupt Vector Table

0x0030–0x071F RAM User Program Space

0x0720–0x07EC RAM Reserved by Debugger

0x07ED–0x07FF RAM Reserved by Monitor

0x0800–0x0DEC ROM ROM Monitor

0x0DED–0x0FEA ROM ROM Math and Motor

Control Utilities

0x0FEB–0x0FFF ROM Reserved

Table III. Data Memory Map

Memory

Address Range Type Function

0x0000–0x1FFF Reserved

0x2000–0x20FF Memory Mapped Registers

0x2100–0x37FF Reserved

0x3800–0x3B5F RAM User Data Space

0x3B60–0x3BFF RAM Reserved by Monitor

0x3C00–0x3FFF Memory Mapped Registers

ROM Code

The 2K × 24-bit block of program memory ROM starting at address 0x0800 contains a monitor function that is used to download

and execute user programs via the serial port. In addition, the

monitor function supports an interactive mode in which commands

are received and processed from a host. An example of such a host

is the Windows

®

-based Motion Control Debugger, which is part of

the software development system for the ADMC331. In the interactive mode, the host can access both the internal DSP and peripheral motor control registers of the ADMC331, read and write to

both program and data memory, implement breakpoints and perform single-step and run/halt operation as part of the program

debugging cycle.

In addition to the monitor function, the program memory ROM

contains a number of useful mathematical and motor control utilities that can be called as subroutines from the user code. A complete list of these ROM functions is given in Table IV. The start

address of the function in the program memory ROM is also given.

Refer to the ADMC331 DSP Motor Controller Developer’s Reference

Manual for more details of the ROM functions.

Windows is a registered trademark of Microsoft Corporation.

–10–

REV. B

ADMC331

Table IV. ROM Utilities

Utility Address Function

PER_RST 0x07F1 Reset Peripherals.

UMASK 0x0DED Limits Unsigned Value to

Given Range.

PUT_VECTOR 0x0DF4 Facilitates User Setup of

Vector Table.

SMASK 0x0E06 Limits Signed Value to Given

Range.

ADMC_COS 0x0E26 Cosine Function.

ADMC_SIN 0x0E2D Sine Function.

ARCTAN 0x0E43 Arctangent Function.

RECIPROCAL 0x0E65 Reciprocal (1/×) Function.

SQRT 0x0E7B Square Root Function.

LN 0x0EB5 Natural Logarithm Function.

LOG 0x0EB8 Logarithm (Base 10) Function.

FLTONE 0x0ED4 Fixed Pt. to Float Conversion.

FIXONE 0x0ED9 Float to Fixed Pt. Conversion.

FPA 0x0EDD Floating Pt. Addition.

FPS 0x0EEC Floating Pt. Subtraction.

FPM 0x0EFC Floating Pt. Multiplication.

FPD 0x0F05 Floating Pt. Division.

FPMACC 0x0F26 Floating Pt. Multiply/Accumulate.

PARK 0x0F48 Forward/Reverse Park

Transformation.

REV_CLARK 0x0F5C Reverse Clark Transformation.

FOR_CLARK 0x0F72 Forward Clark Transformation.

COS64 0x0F80 64 Pt. COS Table.

ONE_BY_X 0x0FCO 16 Pt. 1/× Table.

SDIVQINT 0x0FD0 Unsigned Single Precision

Division (Integer).

SDIVQ 0x0FD9 Unsigned Single Precision

Division (Fractional).

SYSTEM INTERFACE

Figure 4 shows a basic system configuration for the ADMC331,

with an external crystal and serial E

2

PROM for boot loading of

program and data memory RAM.

CLKOUT

ADMC331

RESET

XTAL

CLKIN

DR1A

SCLK1

RFS1/ SROM

13 MHz

DATA

CLK

RESET

SERIAL

2

E

PROM

Figure 4. Basic System Configuration

Clock Signals

The ADMC331 can be clocked by either a crystal or a TTLcompatible clock signal. The CLKIN input cannot be halted,

changed during operation nor operated below the specified

minimum frequency during normal operation. If an external

clock is used, it should be a TTL-compatible signal running at

half the instruction rate. The signal is connected to the CLKIN

pin of the ADMC331. In this mode, with an external clock

signal, the XTAL pin must be left unconnected. The ADMC331

uses an input clock with a frequency equal to half the instruction rate; a 13 MHz input clock yields a 38.5 ns processor cycle

(which is equivalent to 26 MHz). Normally, instructions are

executed in a single processor cycle. All device timing is

relative to the internal instruction rate, which is indicated by

the CLKOUT signal.

Because the ADMC331 includes an on-chip oscillator feedback

circuit, an external crystal may be used instead of a clock

source, as shown in Figure 4. The crystal should be connected

across the CLKIN and XTAL pins, with two capacitors as

shown in Figure 4. A parallel-resonant, fundamental frequency,

microprocessor-grade crystal should be used. A clock output

signal (CLKOUT) is generated by the processor at the processor’s

cycle rate of twice the input frequency. This output can be

enabled and disabled by the CLKODIS bit of the SPORT0

Autobuffer Control Register, DM[0x3FF3]. However, extreme

care must be exercised when using this bit since disabling

CLKOUT effectively disables all motor control peripherals,

except the watchdog timer.

Reset

The RESET signal initiates a master reset of the ADMC331.

The RESET signal must be asserted during the power-up sequence to assure proper initialization. RESET during initial

power-up must be held long enough to allow the internal clock

to stabilize. If RESET is activated any time after power-up, the

clock continues to run and does not require stabilization time.

The power-up sequence is defined as the total time required for

the crystal oscillator circuit to stabilize after a valid V

DD

is applied to the processor, and for the internal phase-locked loop

(PLL) to lock onto the specific crystal frequency. A minimum

of 2000 CLKIN cycles ensures that the PLL has locked, but

does not include the crystal oscillator start-up time. During this

power-up sequence, the RESET signal should be held low. On

any subsequent resets, the RESET signal must meet the minimum pulsewidth specification, t

RSP

.

If an RC circuit is used to generate the RESET signal, the use of

an external Schmitt trigger is recommended.

The master reset sets all internal stack pointers to the empty

stack condition, masks all interrupts, initializes DSP core registers and performs a full reset of all of the motor control peripherals. When the RESET line is released, the first instruction is

fetched from internal program memory ROM at location 0x0800.

The internal monitor code at this location then commences the

boot-loading sequence over the serial port, SPORT1. A software controlled full peripheral reset is achieved by toggling the

DSP FL2 flag from 1 to 0 to 1 again.

–11–REV. B

Loading...

Loading...