Analog Devices ADM483EAR, ADM483EAN Datasheet

615 kV ESD Protected, EMC Compliant

D

R

A

B

DI

DE

RE

RO

ADM483E

a

FEATURES

Robust RS-485 Transceiver

15 kV ESD Protection Using HBM

2 kV EFT Protection Meets IEC1000-4-4

High EM Immunity Meets IEC1000-4-3

Reduced Slew Rate for Low EM Interference

250 kbps Data Rate

Single +5 V 6 10% Supply

–7 V to +12 V Bus Common-Mode Range

12 kV Input Impedance

Short Circuit Protection

Excellent Noise Immunity

36 mA Supply Current

0.1 mA Shutdown Current

APPLICATIONS

Low Power RS-485 Systems

Electrically Harsh Environments

EMI Sensitive Applications

DTE-DCE Interface

Packet Switching

Local Area Networks

Slew Rate Limited, EIA RS-485 Transceiver

ADM483E

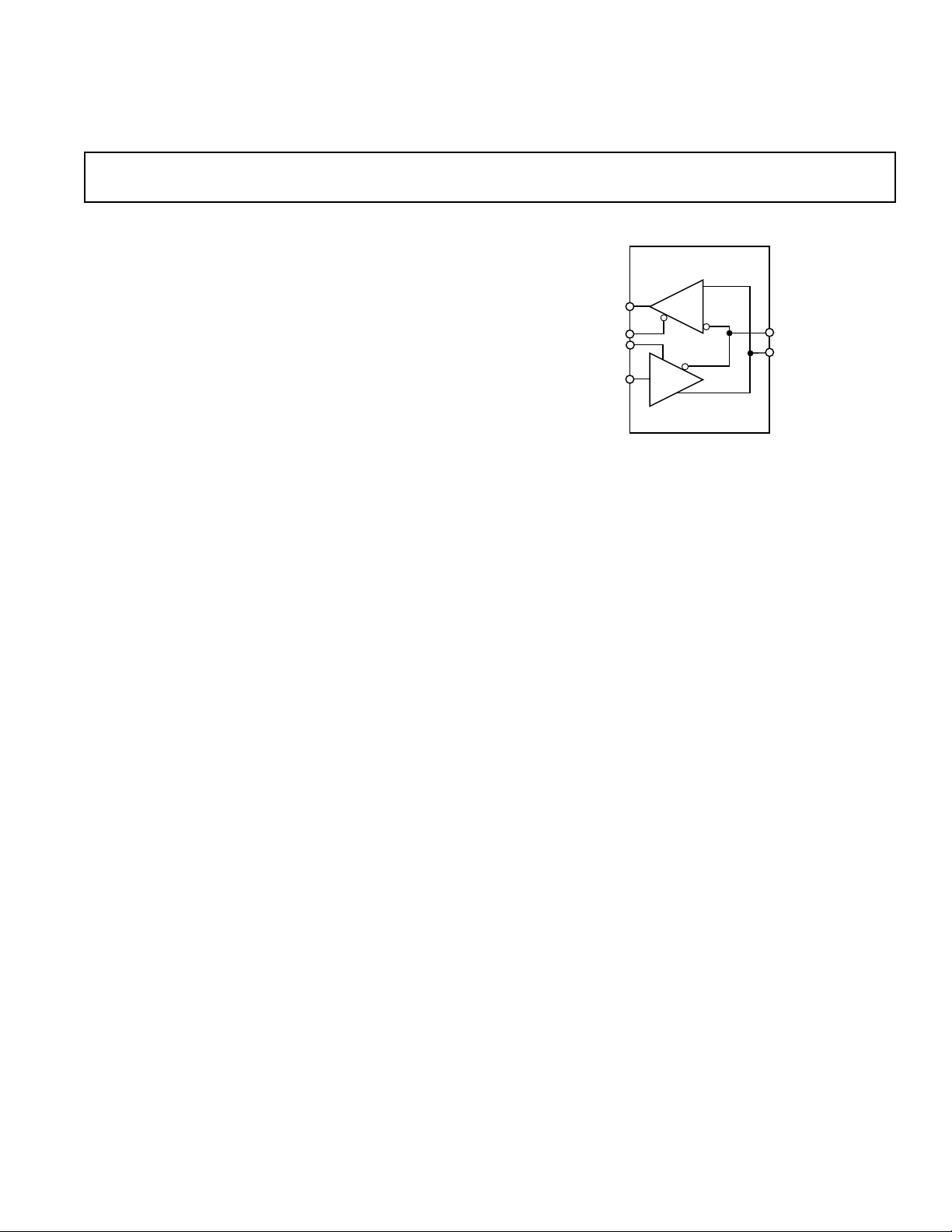

FUNCTIONAL BLOCK DIAGRAM

GENERAL DESCRIPTION

The ADM483E is a robust, low power differential line transceiver suitable for communication on multipoint bus transmission lines. Internal protection against electrostatic discharge

(ESD), electrical fast transient (EFT) and electromagnetic

immunity (EMI) allows operation in electrically harsh environments. ESD protection on the I-O lines meets ±15 kV when

tested using the Human Body Model. EFT protection meets

± 2 kV in accordance with IEC1000-4-4, while EMI immunity is

in excess of 10 V/m meeting IEC1000-4-3.

The level of unwanted emissions is also carefully controlled

using slew limiting on the driver outputs. This reduces reflections with improperly terminated cables and also minimizes

electromagnetic interference. The controlled slew rate limits the

data rate to 250 kbps.

The ADM483E is intended for balanced data transmission and

complies with both EIA Standards RS-485 and RS-422. It

contains a differential line driver and a differential line receiver

and is suitable for half duplex data transmission, as the driver

and receiver share the same differential pins.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

The input impedance on the ADM483E is 12 kΩ, allowing up

to 32 transceivers on the bus.

The ADM483E operates from a single +5 V ± 10% power supply. Excessive power dissipation caused by bus contention or by

output shorting is prevented by a thermal shutdown circuit. This

feature forces the driver output into a high impedance state if,

during fault conditions, a significant temperature increase is

detected in the internal driver circuitry.

The receiver contains a fail-safe feature that results in a logic

high output state if the inputs are unconnected (floating).

The ADM483E is fabricated on BiCMOS, an advanced mixed

technology process combining low power CMOS with robust

bipolar technology.

It is fully specified over the industrial temperature range and is

available in 8-lead DIP and SOIC packages.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1997

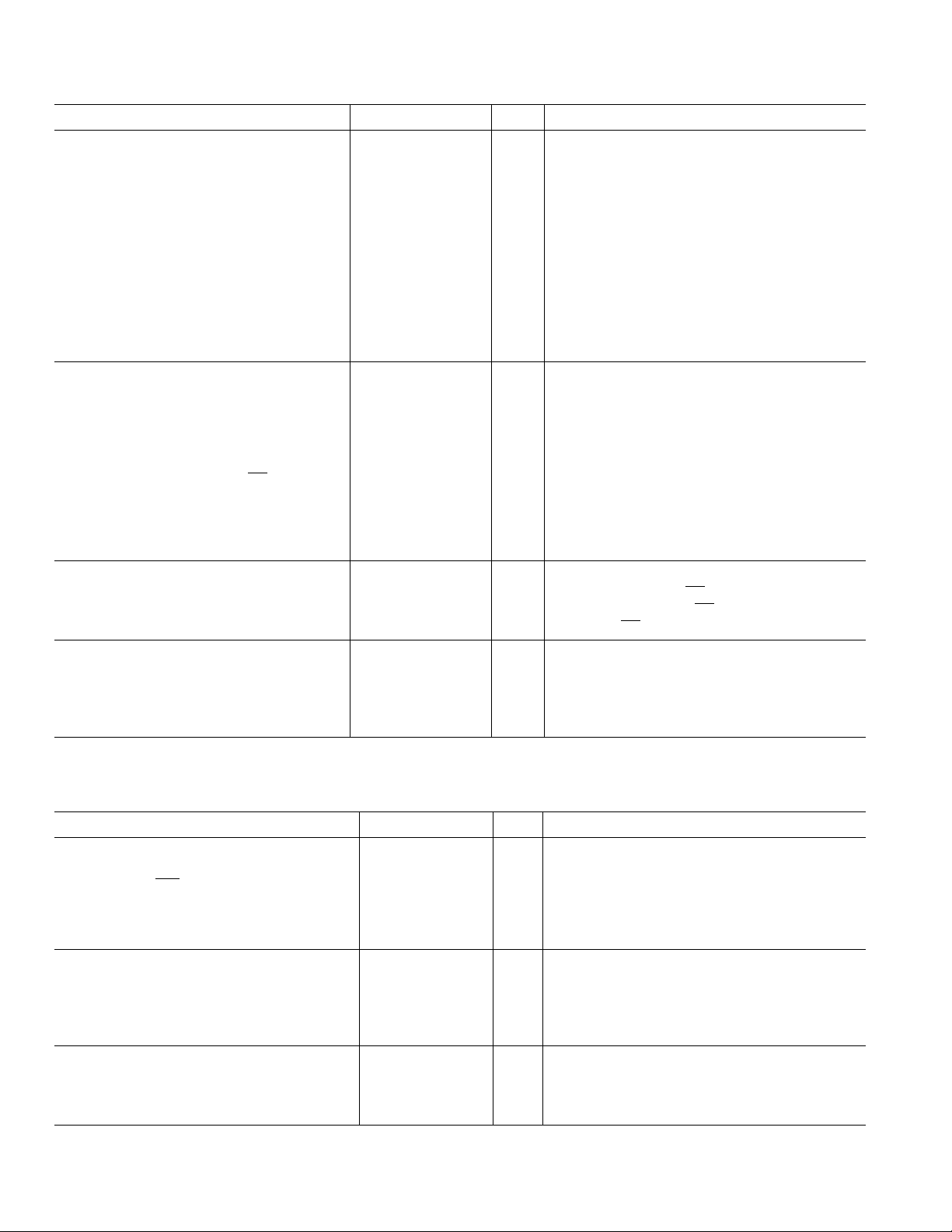

ADM483E–SPECIFICATIONS

(VCC = +5 V 6 10%. All specifications T

MIN

to T

unless otherwise noted)

MAX

Parameter Min Typ Max Units Test Conditions/Comments

DRIVER

Differential Output Voltage, V

OD

5.0 V V

= 5.25 V. R = ∞, Figure 1

CC

2.0 5.0 V R = 50 Ω (RS-422), Figure 1

1.5 5.0 V R = 27 Ω (RS-485), Figure 1

1.5 5.0 V V

∆|V

| for Complementary Output States 0.2 V R = 27 Ω or 50 Ω, Figure 1

OD

Common-Mode Output Voltage V

∆|V

| for Complementary Output States 0.2 V R = 27 Ω or 50 Ω

OC

Output Short Circuit Current (V

Output Short Circuit Current (V

CMOS Input Logic Threshold Low, V

CMOS Input Logic Threshold High, V

OC

= High) 250 mA –7 V ≤ VO ≤ +12 V

OUT

= Low) 250 mA –7 V ≤ VO ≤ +12 V

OUT

INL

INH

2.0 1.4 V

3 V R = 27 Ω or 50 Ω, Figure 1

1.4 0.8 V

= –7 V to +12 V, Figure 2, V

TST

≥ 4.75 V

CC

Logic Input Current (DE, DI) ±1.0 µA

RECEIVER

Differential Input Threshold Voltage, V

Input Voltage Hysteresis, ∆V

TH

TH

Input Resistance 12 kΩ –7 V ≤ V

Input Current (A, B) +1 mA V

Logic Enable Input Current (

CMOS Output Voltage Low, V

CMOS Output Voltage High, V

RE) ±1 µA

OL

OH

Short Circuit Output Current 7 85 mA V

Three-State Output Leakage Current ±1.0 µA 0.4 V ≤ V

–0.2 +0.2 V –7 V ≤ VCM ≤ +12 V

70 mV VCM = 0 V

≤ +12 V

CM

= 12 V

–0.8 mA V

0.4 V I

4.0 V I

IN

= –7 V

IN

= +4.0 mA

OUT

= –4.0 mA

OUT

= GND or V

OUT

≤ +2.4 V

OUT

CC

POWER SUPPLY CURRENT Outputs Unloaded, Receivers Enabled

I

(ADM483E) 36 60 µA DE = 0 V (Disabled) RE = 0 V

CC

Supply Current in Shutdown 0.1 10 µA DE = 0 V, RE = V

270 360 µA DE = 5 V (Enabled) =

CC

RE = 0 V

ESD/EFT IMMUNITY

ESD Protection ±15 kV HBM Air Discharge. A, B Pins

±3.5 kV HBM 3015.7 Contact Discharge. All Pins

EFT Protection ±2 kV IEC1000-4-4, A, B Pins

EMI Immunity 10 V/m IEC1000-4-3

Specifications subject to change without notice.

TIMING SPECIFICATIONS

(VCC = +5 V 6 10%. All specifications T

MIN

to T

unless otherwise noted.)

MAX

Parameter Min Typ Max Units Test Conditions/Comments

DRIVER

Propagation Delay Input to Output T

Driver O/P to

Driver Rise/Fall Time T

O/P T

SKEW

R

, T

F

Driver Enable to Output Valid 250 2000 ns R

Driver Disable Timing 300 3000 ns R

PLH

, T

250 2000 ns R

PHL

100 800 ns R

250 2000 ns R

Diff = 54 Ω C

L

Diff = 54 Ω C

L

Diff = 54 Ω C

L

= 500 Ω, C

L

= 500 Ω, C

L

= CL2 = 100 pF, Figure 5

L1

= CL2 = 100 pF, Figure 5

L1

= CL2 = 100 pF, Figure 5

L1

= 100 pF, Figure 3

L

= 15 pF, Figure 3

L

RECEIVER

Propagation Delay Input to Output T

Skew |T

PLH–TPHL

Receiver Enable T

Receiver Disable T

| 200 ns

EN1

EN2

PLH

, T

250 2000 ns CL = 15 pF, Figure 5

PHL

10 50 ns R

10 50 ns R

= 1 kΩ, C

L

= 1 kΩ, C

L

= 15 pF, Figure 4

L

= 15 pF, Figure 4

L

SHUTDOWN

Time to Shutdown 50 200 600 ns

Driver Enable from Shutdown 2000 ns R

Receiver Enable from Shutdown 2500 ns R

Specifications subject to change without notice.

= 500 Ω, C

L

= 1 kΩ, C

L

= 100 pF, Figure 3

L

= 15 pF, Figure 4

L

–2– REV. 0

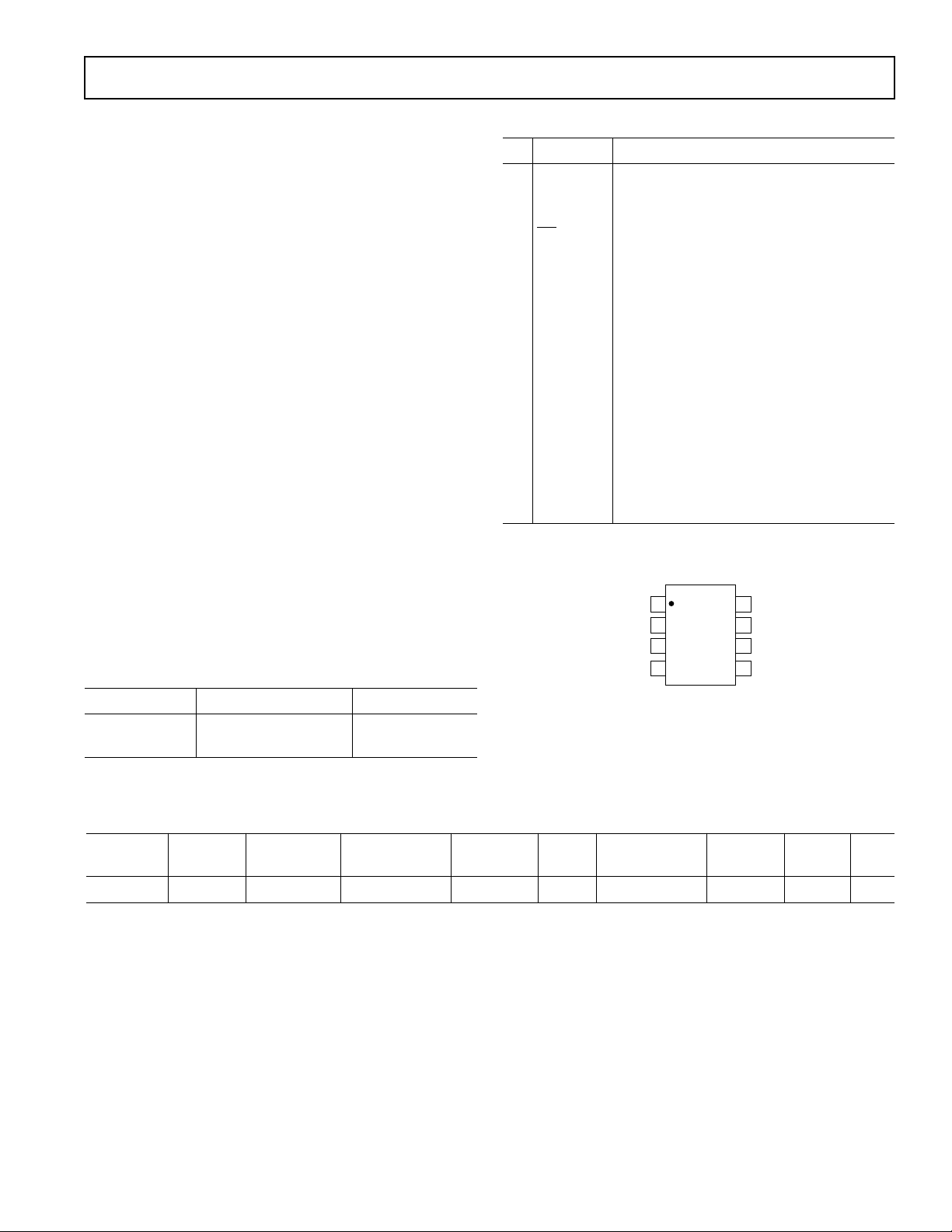

ADM483E

RE

DE

DI

V

CC

B

A

GND

1

2

3

4

8

7

6

5

TOP VIEW

(Not to Scale)

ADM483E

RO

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted)

VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+7 V

Inputs

Driver Input (DI) . . . . . . . . . . . . . . . . –0.5 V to V

Control Inputs (DE, RE) . . . . . . . . . . –0.5 V to V

+ 0.5 V

CC

+ 0.5 V

CC

Receiver Inputs (A, B) . . . . . . . . . . . . . . . . . –14 V to +14 V

Outputs

Driver Outputs . . . . . . . . . . . . . . . . . . . . –12.5 V to +12.5 V

Receiver Output . . . . . . . . . . . . . . . . . –0.5 V to V

+0.5 V

CC

ESD Rating: Air (Human Body Model) (A, B Pins) . . ± 15 kV

ESD Rating: Contact (Human Body Model)

(A, B Pins) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±8 kV

ESD Rating MIL-STD-883B Method 3015

(Except A, B) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±3.5 kV

EFT Rating (IEC1000-4-4) (A, B Pins) . . . . . . . . . . . . ±2 kV

EMI Immunity (IEC1000-4-3) . . . . . . . . . . . . . . . . . . 10 V/m

Power Dissipation 8-Pin DIP . . . . . . . . . . . . . . . . . . . 727 mW

θ

, Thermal Impedance . . . . . . . . . . . . . . . . . . +135°C/W

JA

Power Dissipation 8-Pin SOIC . . . . . . . . . . . . . . . . . 470 mW

θ

, Thermal Impedance . . . . . . . . . . . . . . . . . . +110°C/W

JA

Operating Temperature Range

Industrial (A Version) . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . +300°C

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute

maximum ratings for extended periods may affect device reliability.

PIN FUNCTION DESCRIPTION

Pin Mnemonic Function

1 RO Receiver Output. When enabled if A > B by

200 mV, then RO = High. If A < B by

200 mV, then RO = Low.

2

RE Receiver Output Enable. A low level enables

the receiver output, RO. A high level places it

in a high impedance state.

3 DE Driver Output Enable. A high level enables

the driver differential outputs, A and B. A

low level places it in a high impedance state.

4 DI Driver Input. When the driver is enabled a

logic Low on DI forces A low and B high

while a logic High on DI forces A high and B

low.

5 GND Ground Connection, 0 V.

6 A Noninverting Receiver Input A/Driver

Output A.

7 B Inverting Receiver Input B/Driver Output B.

8V

CC

Power Supply, 5 V ± 10%.

PIN CONFIGURATION

ORDERING GUIDE

Model Temperature Range Package Option

ADM483EAN –40°C to +85°C N-8

ADM483EAR –40°C to +85°C SO-8

Table I. Selection Table

Part No. Duplex Data Rate Low Power Tx/Rx I

No of Tx/Rx ESD EFT EMI

CC

kb/s Shutdown Enable mA On Bus kV kV V/m

ADM483E Half 250 Yes Yes 36 32 ±15 ±210

REV. 0

–3–

ADM483E

T

ZH

1.5VDE

1.5V

3V

0V

2.3V

T

HZ

V

OH

VOH – 0.5V

0V

A, B

V

OL

+ 0.5V

T

ZL

2.3V

T

LZ

V

OL

A, B

T

ZH

1.5V 1.5V

3V

0V

1.5V

T

HZ

V

OH

VOH – 0.5V

0V

R

V

OL

+ 0.5V

T

ZL

1.5V

T

LZ

V

OL

R

RE

O/P LOW

O/P HIGH

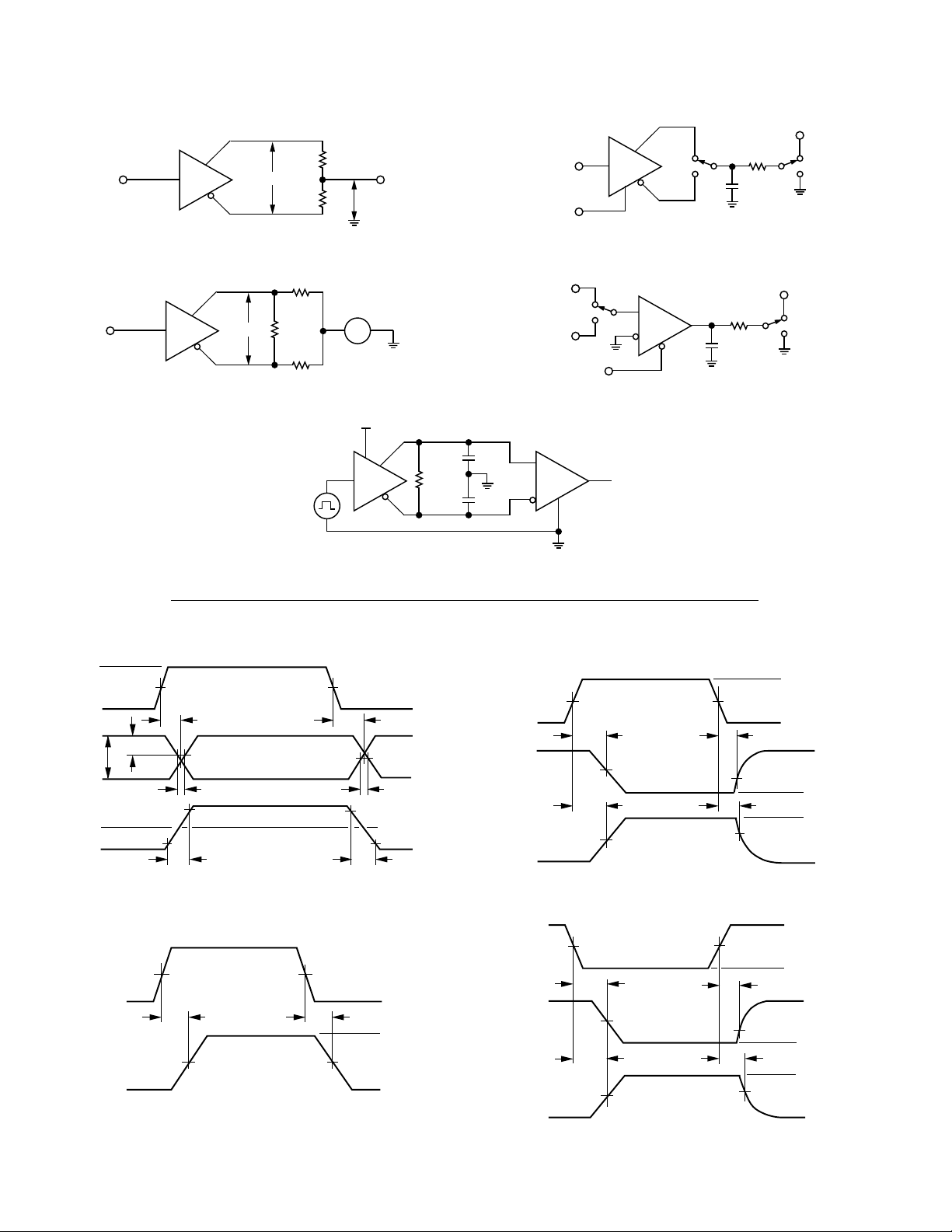

Test Circuits

V

CC

R

V

OD

R

V

OC

0V OR 3V

DE IN

A

DE

S1 S2

B

R

L

C

L

V

OUT

Figure 1. Driver Voltage Measurement Test Circuit

375Ω

V

OD3

60Ω

375Ω

V

TST

Figure 2. Driver Voltage Measurement Test Circuit 2

DI

D

Figure 5. Receiver Propagation Delay Test Circuit

Switching Characteristics

3V

VO

–VO

0V

B

VO

A

0V

1/2VO

90% POINT

10% POINT

T

1.5V

PLH

T

T

SKEW

R

1.5V

T

PHL

90% POINT

10% POINT

T

F

T

SKEW

Figure 3. Driver Enable/Disable Test Circuit

V

+15V

–15V

S1

RE IN

RE

R

C

L

V

OUT

CC

L

S2

Figure 4. Receiver Enable/Disable Test Circuit

A

C

L1

RL

DIFF

B

C

L2

RO

R

RE

Figure 6. Driver Propagation Delay, Rise/Fall Timing

0V

T

PHL

V

OH

V

OL

–4–

T

PLH

0V

1.5V 1.5V

A–B

RO

Figure 8. Receiver Propagation Delay

Figure 7. Driver Enable/Disable Timing

Figure 9. Receiver Enable/Disable Timing

REV. 0

Loading...

Loading...