ANALOG DEVICES ADM4210 Service Manual

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

Hot Swap Controller

FEATURES

Controls supply rails from 2.7 V to 16.5 V

Allows protected board removal and insertion to a live

backplane

External sense resistor provides adjustable analog current

limit with circuit breaker

Peak fault current limited with fast response

Charge pumped gate drive for external N-FET switch

Automatic retry or latch-off during current fault

Undervoltage lockout

Low profile (1 mm), 6-lead, TSOT package

Pin compatible with LTC4210-1 and LTC4210-2

APPLICATIONS

Hot swap board insertion: line cards, raid systems

Industrial high-side switches/circuit breakers

Electronic circuit breakers

GENERAL DESCRIPTION

The ADM4210 is a hot swap controller that safely enables a

printed circuit board to be removed and inserted to a live

backplane. This is achieved using an external N-channel power

MOSFET with a current control loop that monitors the load

current through a sense resistor. An internal charge pump is

used to enhance the gate of the N-channel FET. When an

overcurrent condition is detected, the gate voltage of the FET is

reduced to limit the current flowing through the sense resistor.

During an overcurrent condition, the TIMER cap determines

the amount of time the FET remains at a current limiting mode

CLR

of operation until it is shut down. The ON (ONenable input for the device and can be used to monitor the

input supply voltage. The ADM4210 operates with a supply

voltage ranging from 2.7 V to 16.5 V.

) pin is the

in 6-Lead TSOT Package

ADM4210

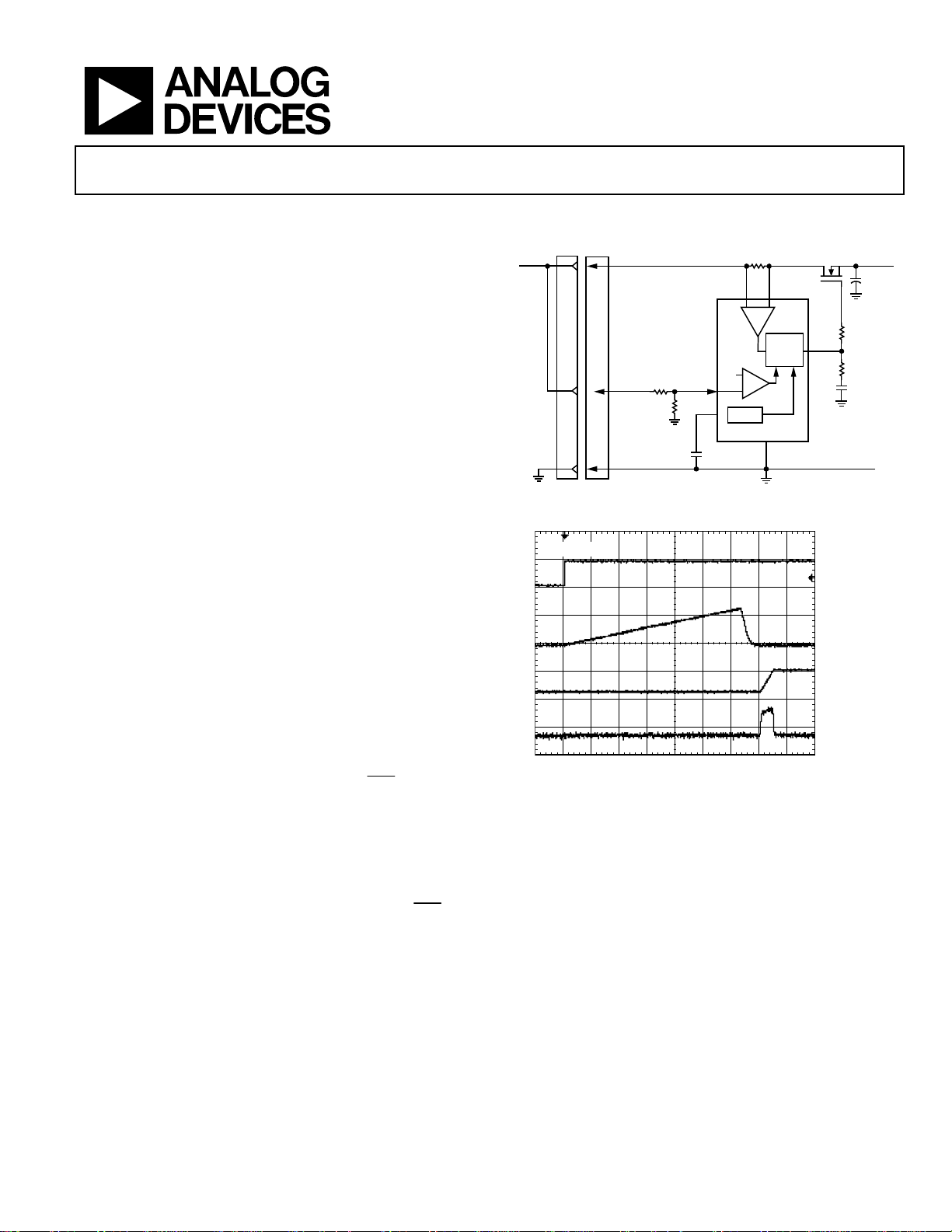

FUNCTIONAL BLOCK DIAGRAM

R

ON

C

TIMER

0.22µF

V

1.3V

CC

TIMER

SENSE

0.01Ω

SENSE

GATE

DRIVE/

LOGIC

ADM4210

GND

Q

GATE

V

ON

(2V/DIV)

V

TIMER

(1V/DIV)

V

OUT

(5V/DIV)

I

OUT

(0.5A/ DIV)

1

VIN = 5V V

GND GND

LONG

SHORT

LONG

R

ON1

20kΩ

R

ON2

10kΩ

C

TIMER

Figure 1.

C

= 470µF

LOAD

10ms/DIV

Figure 2. Start-Up Sequence

OUT

+

R

G

100Ω

R

C

100Ω

C

0.01µF

C

470µF

C

= 5V

LOAD

05132-050

05132-001

The ADM4210 is available in two options: the ADM4210-1 with

automatic retry for overcurrent fault and the ADM4210-2 with

CLR

latch off for an overcurrent fault. Toggling the ON (ON-

)

pin resets a latched fault. The ADM4210 is packaged in a

6-lead TSOT.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

ADM4210

TABLE OF CONTENTS

Features.............................................................................................. 1

UVLO........................................................................................... 11

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

Thermal Characteristics .............................................................. 4

ESD Caution.................................................................................. 4

Pin Configurations and Function Descriptions ........................... 5

Typical Performance Characteristics ............................................. 6

Theory of Operation ...................................................................... 11

Overview...................................................................................... 11

REVISION HISTORY

7/06—Revision 0: Initial Version

ON (ON-

GATE ........................................................................................... 11

Current Limit Function............................................................. 11

Calculating the Current Limit.................................................. 11

Circuit Breaker Function........................................................... 12

Timer Function........................................................................... 12

Power-Up Timing Cycle............................................................ 12

Circuit Breaker Timing Cycle................................................... 13

Automatic Retry or Latched Off............................................... 13

Outline Dimensions....................................................................... 14

Ordering Guide .......................................................................... 14

CLR

) Pin..................................................................... 11

Rev. 0 | Page 2 of 16

ADM4210

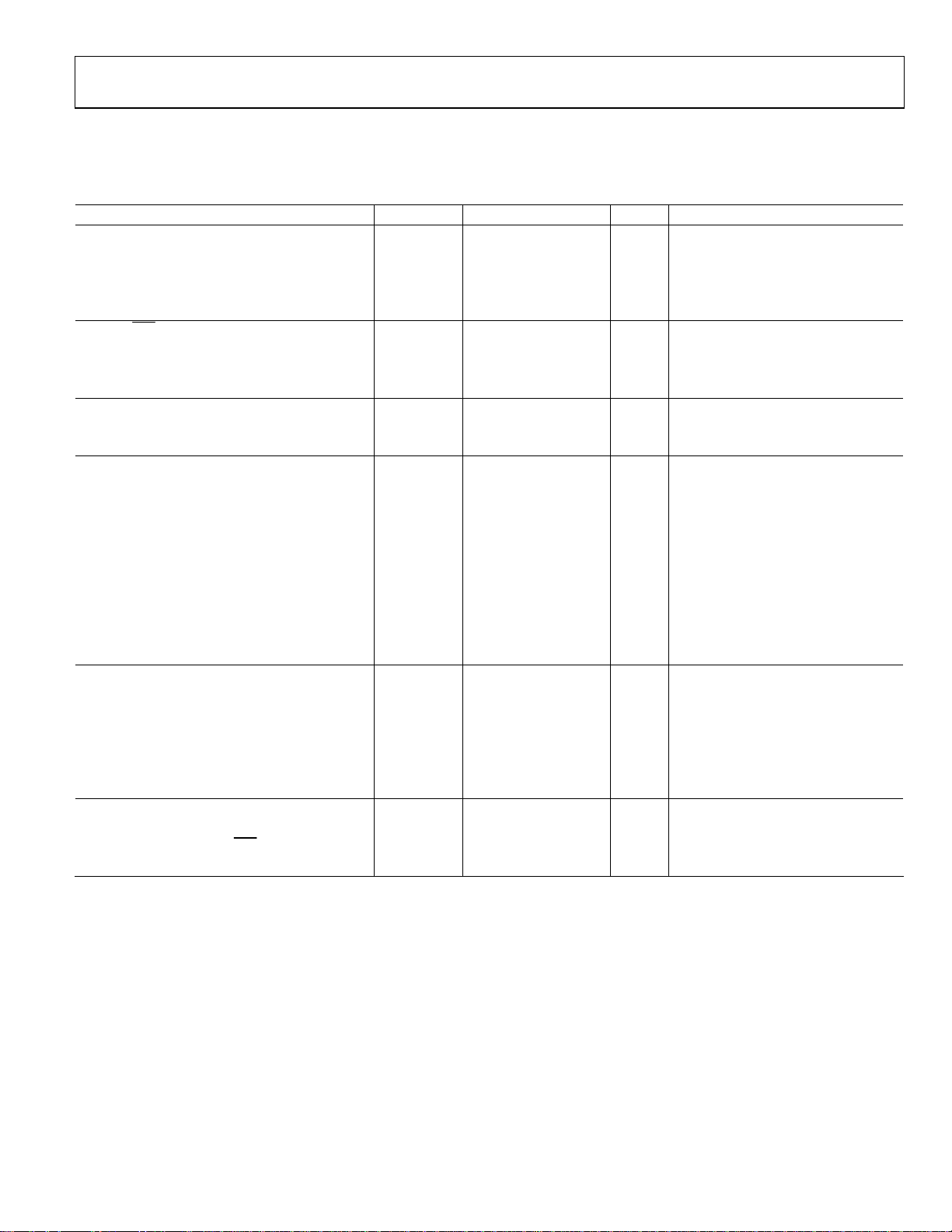

SPECIFICATIONS

VCC = 2.7 V to 16.5 V, TA = −40°C to +85°C, typical values at TA = 25°C, unless otherwise noted.

Table 1.

Parameter Symbol Min Typ Max Unit Conditions

VCC PIN

Operating Voltage Range VCC 2.7 16.5 V

Supply Current ICC 0.65 3.5 mA

Undervoltage Lockout V

Undervoltage Lockout Hysteresis V

ON (ON-CLR) PIN

Input Current

Threshold VON 1.22 1.3 1.38 V ON rising

Threshold Hysteresis V

SENSE PIN

Input Current

Circuit Breaker Limit Voltage VCB 44 50 56 mV VCB = (VCC− V

GATE PIN

Pull-Up Current I

Pull-Down Current I

V

V

Gate Drive Voltage

4.5 7.5 10 V V

5.0 8.5 12 V V

8.75 12 16 V V

7.6 12 16 V V

6.0 11 18 V V

TIMER PIN

Pull-Up Current I

−25 −60 −100 µA During current fault, V

Pull-Down Current

100 µA Normal operation, V

Threshold High V

Threshold Low V

t

OFF

Turn-Off Time (TIMER Rise to GATE Fall)

Turn-Off Time (ON (ON-CLR) Fall to GATE Fall)

Turn-Off Time (VCC Rise to IC Reset) t

2.2 2.5 2.65 V VCC rising

UVLO

100 mV

UVLOHYS

I

−10 0 +10 µA

INON

80 mV

ONHYST

I

−10 +5 +10 µA V

INSENSE

−5 −10 −15 µA V

GATEUP

25 mA V

GATEDN

V

GATE

−2 −5 −8.5 µA Initial cycle, V

TIMERUP

I

2 3.5 µA After current fault, V

TIMERDN

1.22 1.3 1.38 V TIMER rising

TIMERH

0.15 0.2 0.25 V TIMER falling

TIMERL

t

OFF(TMRHIGH)

t

OFF(ONLOW)

OFF(VCCLOW)

1 µs V

30 µs VON = 5 V to 0 V step, VCC = 5 V

30 µs VCC = 0 V to 2 V step, VON = 5 V

= VCC

SENSE

= 0 V

GATE

= 1.5 V, V

TIMER

= 0 V, V

ON

− V

CC

SENSE

− VCC, VCC = 3 V

GATE

− VCC, VCC = 3.3 V

GATE

− VCC, VCC = 5 V

GATE

− VCC, VCC = 12 V

GATE

− VCC, VCC = 15 V

GATE

= 0 V to 2 V step, VCC = VON = 5 V

TIMER

)

SENSE

= 3 V or

GATE

= 3 V or

GATE

= 100 mV, V

= 1 V

TIMER

TIMER

TIMER

GATE

TIMER

= 1 V

= 1 V

= 3 V

= 1 V

Rev. 0 | Page 3 of 16

ADM4210

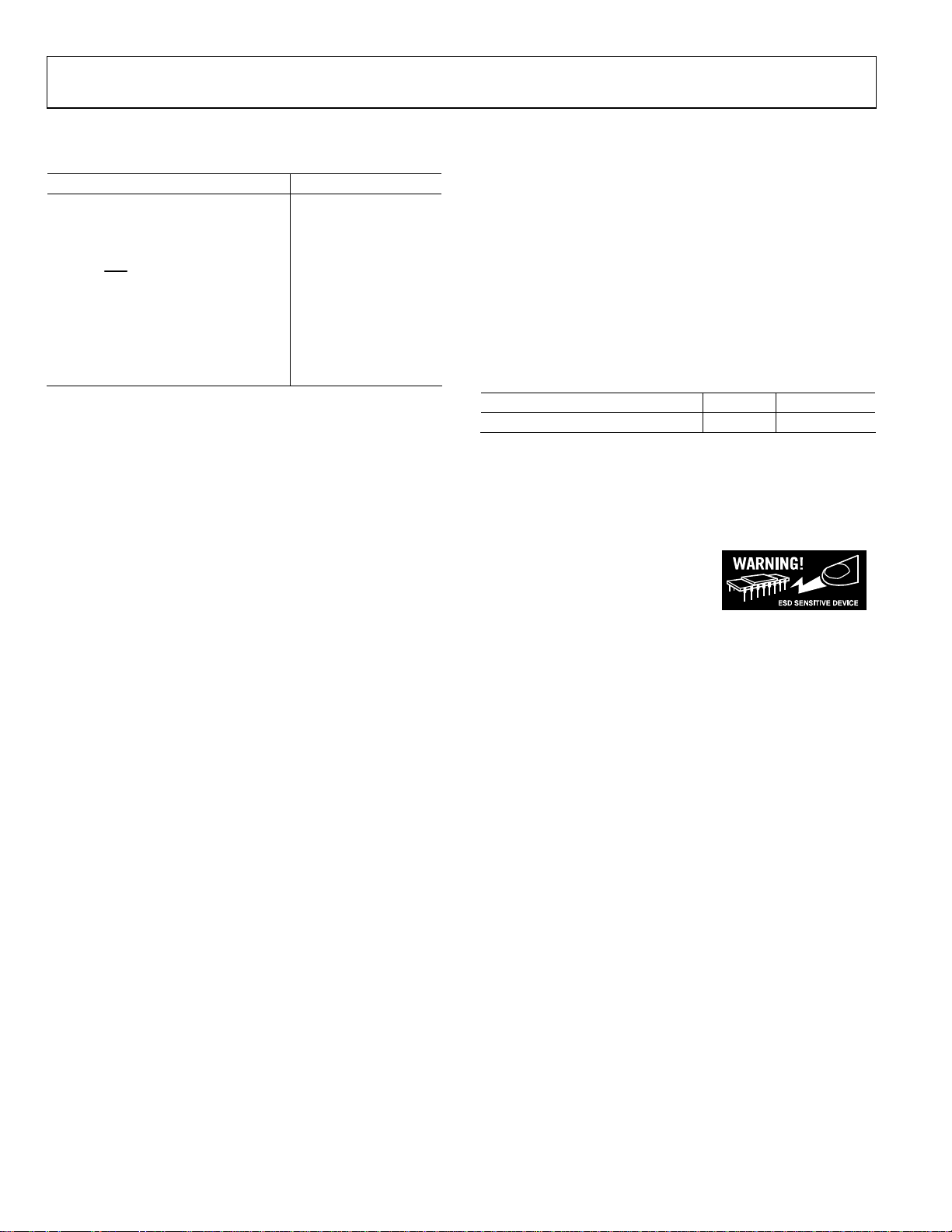

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VCC Pin −0.3 V to +20 V

SENSE Pin −0.3 V to +20 V

VCC − SENSE ±5 V

TIMER Pin −0.3 V to (VCC + 0.3 V)

ON (ON-CLR) Pin

GATE Pin −0.3 V to (VCC + 11 V)

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature (10 sec) 300°C

Junction Temperature 150°C

−0.3 V to +20 V

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type θJA Unit

6-Lead TSOT 169.5 °C/W

Rev. 0 | Page 4 of 16

ADM4210

A

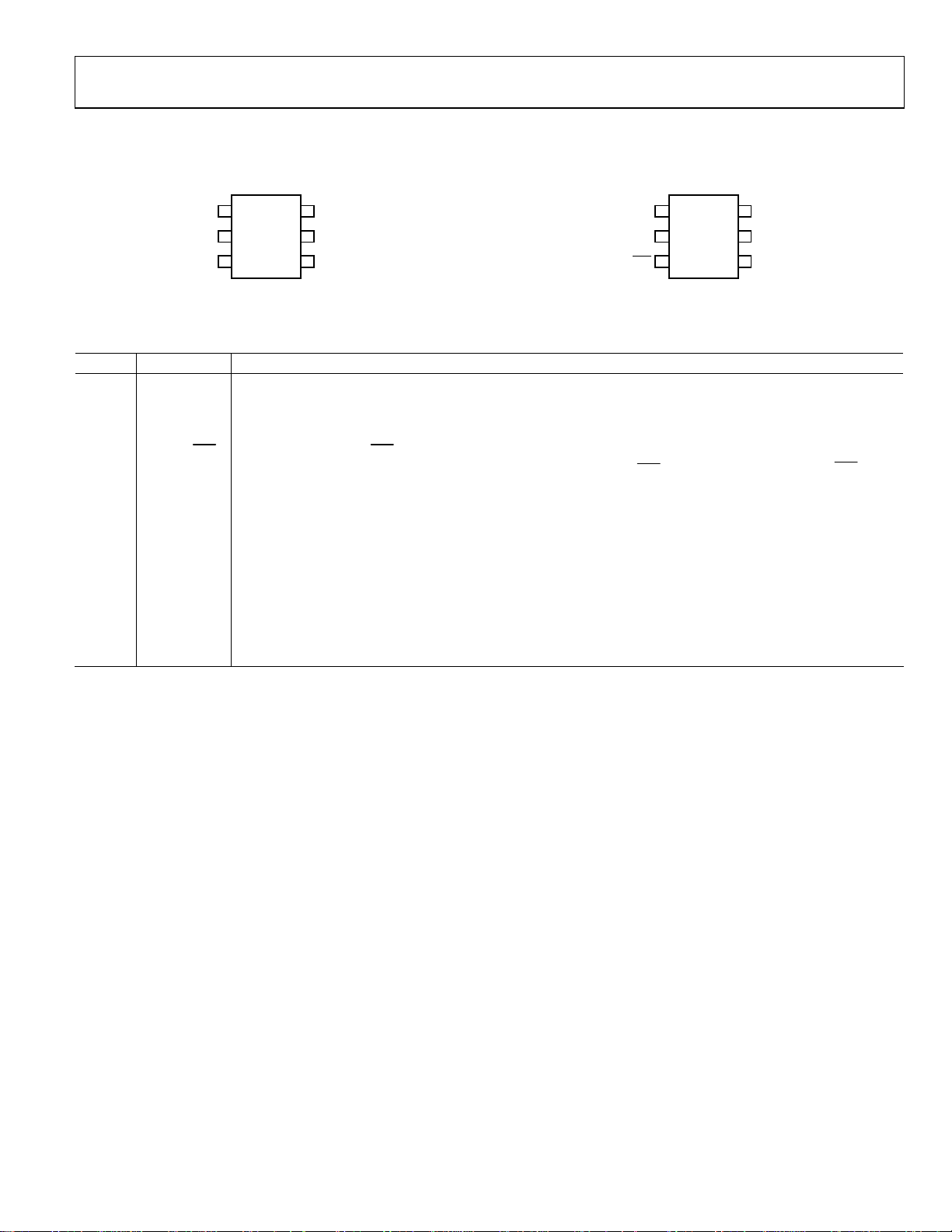

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

ADM4210-1AUJ

TIMER

GND

ON

1

TOP VIEW

2

(Not to Scale)

3

6

5

4

V

CC

SENSE

GATE

Figure 3. Pin Configuration, 1AUJ Model

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 TIMER

Timer Input Pin. The initial and circuit breaker timing cycles are set by this external capacitor. The initial timing

delay is 272.9 ms/F, and 21.7 ms/µF for a circuit breaker delay. When the TIMER pin is pulled beyond the upper

threshold, the GATE turns off.

2 GND Chip Ground Pin.

3

ON (ON-

CLR) Input Pin. The ON (ON-CLR) pin is an input to a comparator that has a low-to-high threshold of 1.3 V with 80 mV

hysteresis and a glitch filter. The ADM4210 is reset when the ON (ON-

high, the ADM4210 is enabled. A rising edge on this pin has the added function of clearing a fault and restarting

the device on the latched off model, the ADM4210-2.

4 GATE

Gate Output Pin. An internal charge pump provides a 12 µA pull-up current to drive the gate of an N-channel

MOSFET. In an overcurrent condition, the ADM4210 controls the external FET to maintain a constant load

current.

5 SENSE

Current Limit Sense Input Pin. The current limit is set via a sense resistor between the V

overcurrent condition, the gate of the FET is controlled to maintain the SENSE voltage at 50 mV. When this limit is

reached, the TIMER circuit breaker mode is activated. The circuit breaker limit can be disabled by connecting the

pin and SENSE pin together.

V

CC

6 VCC

Positive Supply Input Pin. The ADM4210 operates between 2.7 V to 16.5 V. An undervoltage lockout (UVLO)

circuit with a glitch filter resets the ADM4210 when the supply voltage drops below the specified UVLO limit.

DM4210-2AUJ

1

TIMER

GND 2

05132-006

ON-CLR

TOP VIEW

(Not to Scal e)

3

6

V

CC

SENSE5

GATE4

05132-007

Figure 4. Pin Configuration, 2AUJ Model

CLR) pin is low. When the ON (ON-

and SENSE pins. In an

CC

CLR

) pin is

Rev. 0 | Page 5 of 16

Loading...

Loading...