Analog Devices ADM1034 Datasheet

Thermal Monitor and

FEATURES

1 local and 2 remote temperature channels

±1°C accuracy on local and remote channels

Automatic remote temperature channels, up to 1 kΩ

Fast (up to 64 measurements per second)

SMBus 2.0, 1.1, and 1.0 compliant

SMBus address input/LOCATION input to UDID

Programmable over-/undertemperature limits

Programmable fault queue

SMBusALERT

Fail-safe overtemperature comparator output

Fan speed (RPM) controller

DRIVE1

DRIVE2

output

ADM1034

1

3

FAN SPEED

CONTROLLER

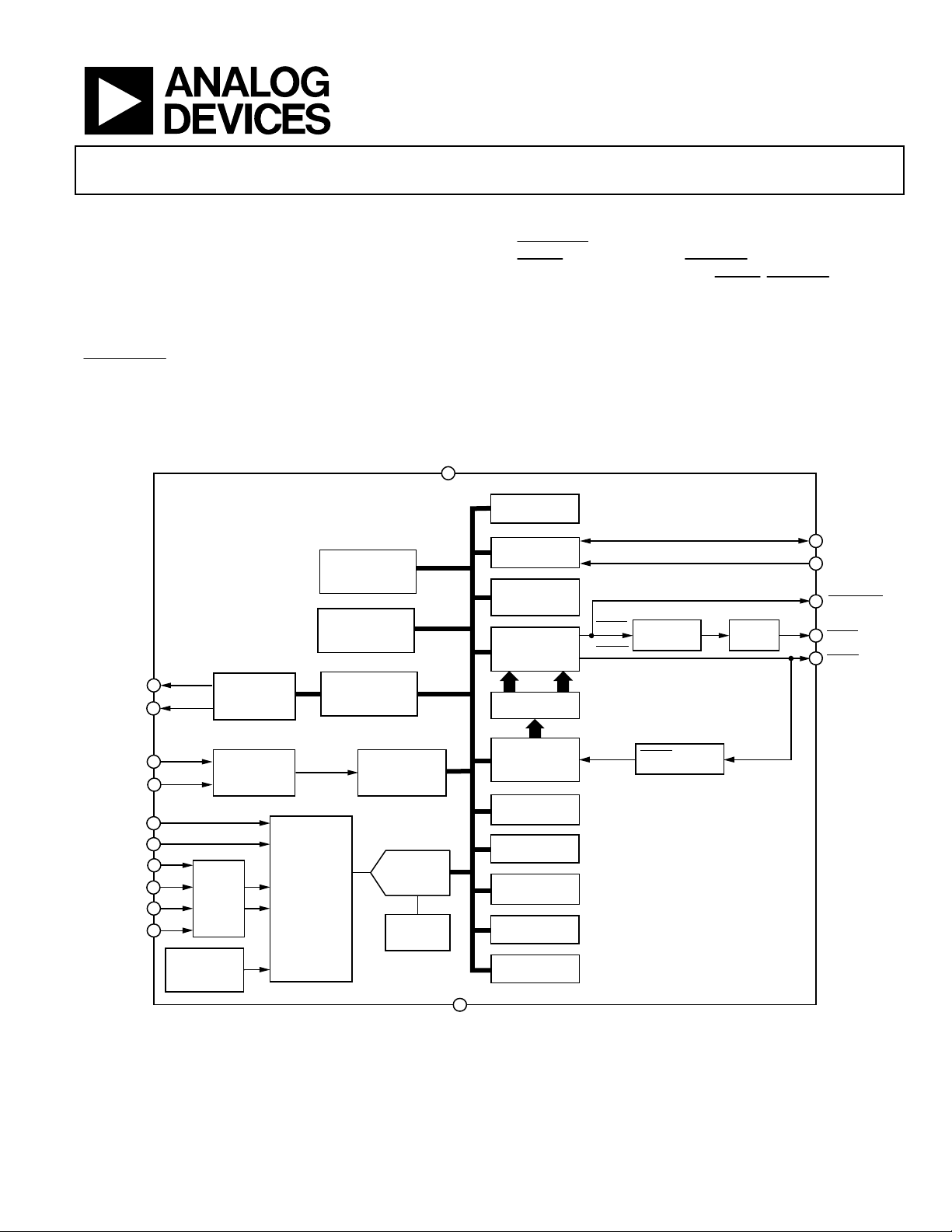

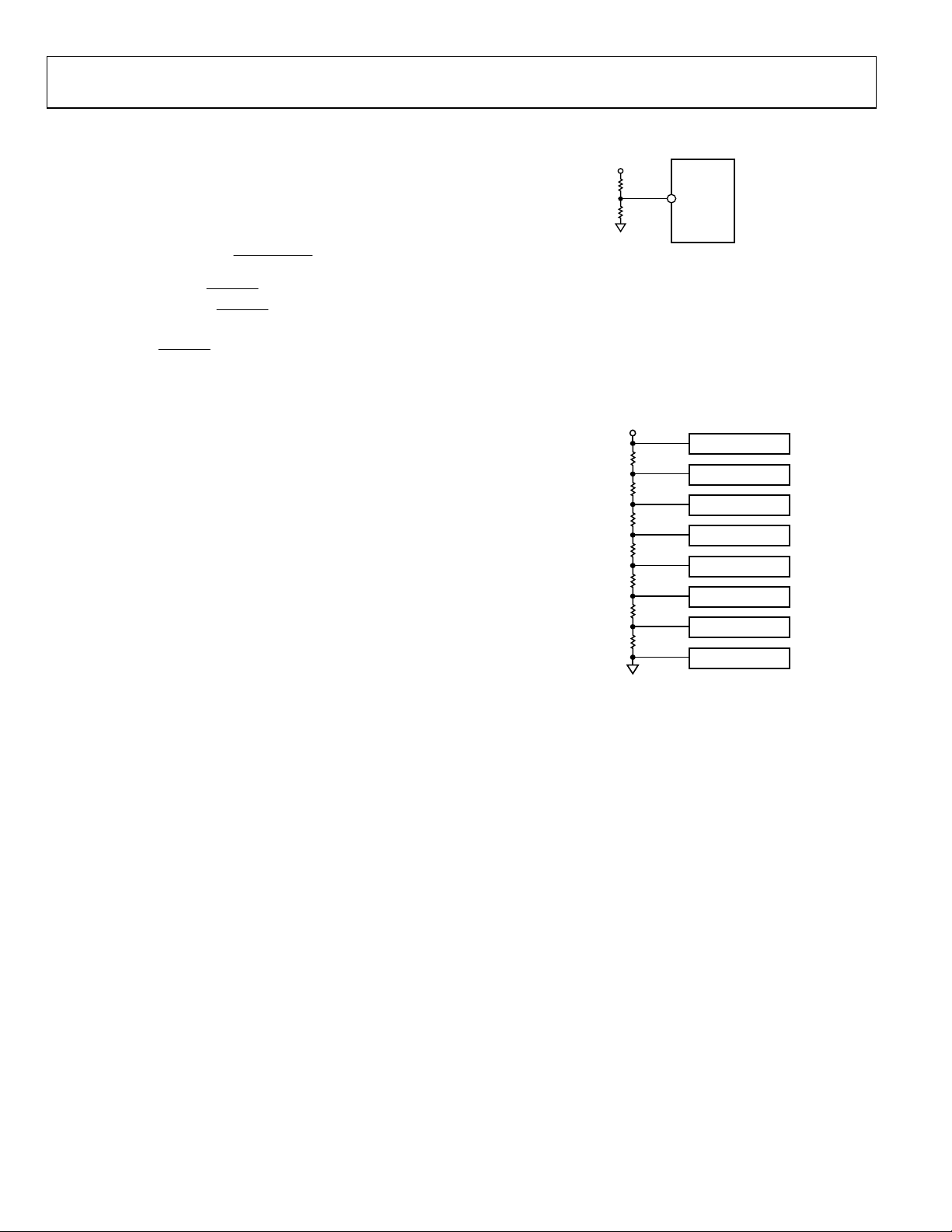

FUNCTIONAL BLOCK DIAGRAM

MANUAL FAN

SPEED CONTROL

REGISTERS

TEMPERATURE-TO-

FAN-SPEED

LOOK-UP TABLE

FAN RESPONSE

Fan Speed (RPM) Controller

ADM1034

Look-up table for temperature-to-fan-speed control

Linear and discrete options for look-up table

FAN _FA ULT

THERM

REF input, used as reference for

3 V to 5.5 V supply

Small 16-lead QSOP package

APPLICATIONS

Desktop and notebook PCs

Embedded systems

Telecommunications equipment

LCD projectors

V

CC

6

SMBUS

ADDRESS

SERIAL BUS

INTERFACE

ADDRESS

POINTER

REGISTER

STATUS

REGISTER

LIMIT

COMPARATOR

output

input, used to time

ALERT

THERM

MASK

REGISTERS

PROCHOT

assertions

THERM (PROCHOT

FAULT

QUEUE

)

16

SCL

15

SDA

8

FAN_FAULT

14

ALERT

7

THERM

2

TACH1

4

TACH2

8

REF

D1–

D1+

D2–

D2+

13

9

10

11

12

TEMPERATURE

LOCATION

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective owners.

SRC

BLOCK

BAND GAP

SENSOR

TACH SIGNAL

CONDITIONING

ANALOG

MULTIPLEXER

FAN

SPEED

COUNTER

ADC

BAND GAP

REFERENCE

GND

5

Figure 1.

VALUE AND

LIMIT

REGISTERS

FAULT

QUEUE

HYSTERESIS

REGISTERS

OFFSET

REGISTERS

CONVERSION

RATE REGISTER

CONFIGURATION

REGISTERS

THERM PERCENT

TIMER

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

04918-0-001

ADM1034

TABLE OF CONTENTS

Specifications..................................................................................... 4

Interrupt Behavior ....................................................... 21

ALERT

Absolute Maximum Ratings............................................................ 6

Thermal Characteristics .............................................................. 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Typical Performance Characteristics............................................. 8

Functional Description ..................................................................10

Internal Registers ........................................................................ 10

Serial Bus Interface..................................................................... 10

Location Input.............................................................................10

SMBus 2.0 ARP-Capable Mode................................................ 10

SMBus 2.0 Fixed-and-Discoverable Mode.............................. 12

SMBus 2.0 Read and Write Operations ...................................12

Register Addresses for Single/Block Byte Modes ...................14

Write Operations ........................................................................ 14

Read Operations ......................................................................... 15

SMBus Timeout ..........................................................................15

Packet Error Checking (PEC)................................................... 15

Alert Response Address (ARA)................................................ 15

Temperature Measurement System.............................................. 16

Internal Temperature Measurement........................................ 16

Remote Temperature Measurement......................................... 16

Additional Functions ................................................................. 18

Handling

Interrupt Masking Register ....................................................... 22

FAN_ FAULT

Fault Queue ................................................................................. 23

Conversion Rate Register.......................................................... 23

THERM

THERM

Fan Drive Signal ......................................................................... 25

Synchronous Speed Control ..................................................... 25

Fan Inputs .................................................................................... 26

Fan Speed Measurement ........................................................... 26

Fan Speed Measurement Registers........................................... 27

Reading Fan Speed ..................................................................... 27

Calculating Fan Speed ............................................................... 27

Alarm Speed................................................................................ 27

Look-Up Table: Modes of Operation....................................... 28

Setting Up the Size of the Look-Up Table............................... 29

Setting Up the Look-Up Table in Linear Mode...................... 29

Setting Which Temperature Channel Controls a Fan ........... 29

Look-Up Table Hysteresis ......................................................... 29

Programming the

Channel

SMBUSALERT

Output ................................................................. 23

I/O Timer and Limits ................................................ 23

% Limit Register ......................................................... 24

........................................................................................ 30

Interrupts ....................................... 22

THERM

Limit for Each Temperature

Layout Considerations................................................................... 19

Limits, Status Registers, and Interrupts ....................................... 20

8-Bit Limits.................................................................................. 20

Out-of-Limit Comparisons .......................................................20

Analog Monitoring Cycle Time................................................ 20

Status Registers ........................................................................... 20

REVISION HISTORY

8/04—Revision 0: Initial Version

Rev. 0 | Page 2 of 40

XOR Tree Test Mode .................................................................. 30

Lock Bit........................................................................................ 30

SW Reset...................................................................................... 30

Outline Dimensions....................................................................... 40

Ordering Guide .......................................................................... 40

ADM1034

GENERAL DESCRIPTION

The ADM1034 is a dual-channel remote- and local-temperature

sensor and fan controller. The remote channels monitor the

temperature of two remote thermal diodes, which may be

discrete 2N3904/6s or may be located on a microprocessor die.

The device also monitors its own ambient temperature.

The ADM1034 can monitor and control the speed of two

cooling fans. The user can program a target fan speed, or else

use the look-up table to input a temperature-to-fan-speed

profile. The look-up table can be configured to run the fans at

discrete speeds (discrete mode) or to ramp the fan speed with

temperature (linear mode).

The ADM1034 communicates over a 2-wire SMBus 2.0

interface. An 8-level LOCATION input allows the user to

choose between SMBus 1.1 and SMBus 2.0. An

indicates error conditions. The

temperature as an output and times

an input. Pin 8 can be configured as a reference for the

THERM (PROCHOT

) input.

THERM

I/O signals over-

THERM

assertions as

ALERT

output

Rev. 0 | Page 3 of 40

ADM1034

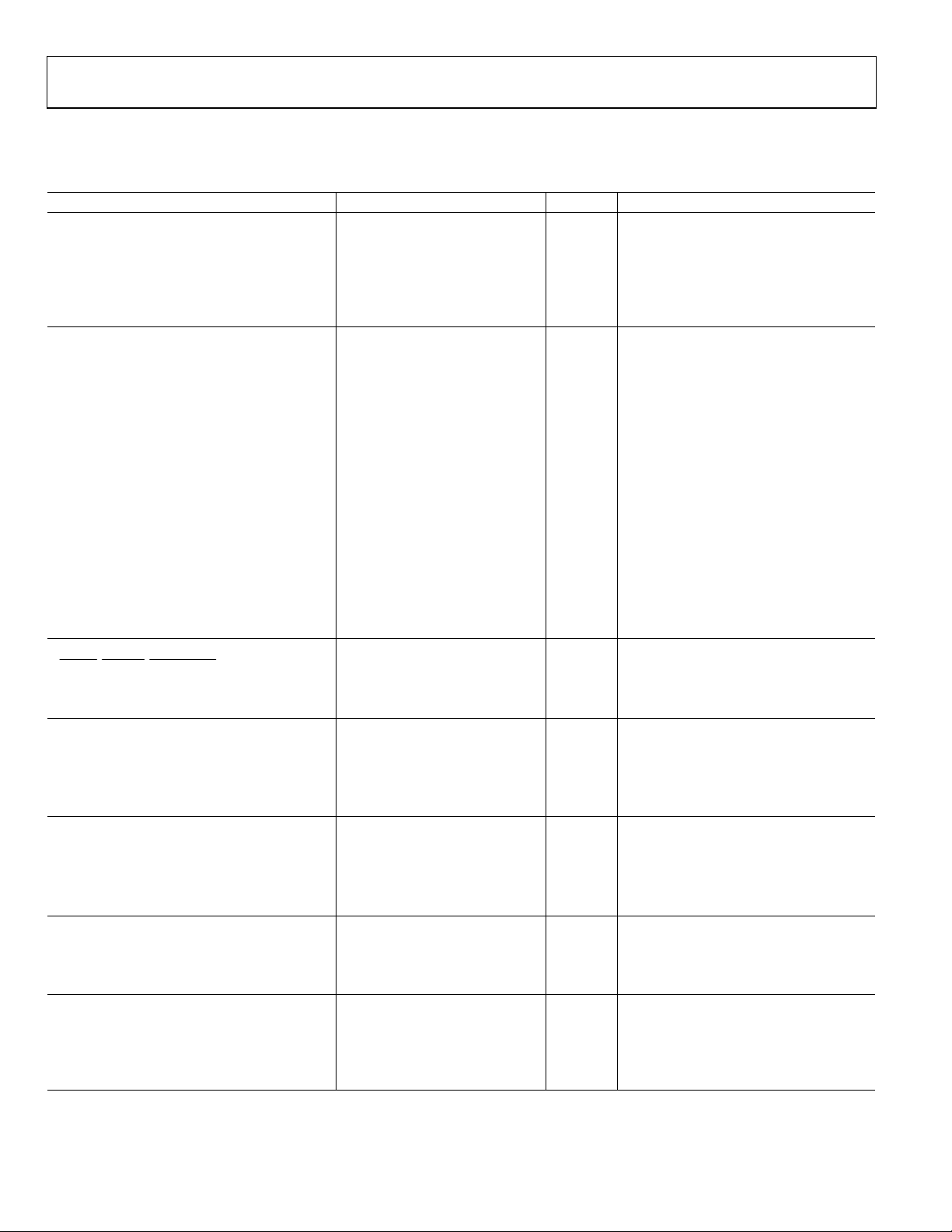

SPECIFICATIONS

TA = T

MIN

to T

, VCC = V

MAX

MIN

to V

, unless otherwise noted.

MAX

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

POWER SUPPLY

Supply Voltage, V

Supply Current, I

2

CC

CC

3.0 3.30 3.6 V

3 mA Interface inactive, ADC active

900 µA Standby mode

Undervoltage Lockout Threshold 2.5 V

Power-On Reset Threshold 1 2.4 V

TEMPERATURE-TO-DIGITAL CONVERTER

Internal Sensor Accuracy ±1 ±2 °C 20°C ≤ TA ≤ 60°C

−4

Resolution 0.03125 °C

External Diode Sensor Accuracy ±0.5 ±1 °C

±1 °C

−3

Resolution 0.03125 °C

Remote Sensor Source Current 85 µA High level

34 µΑ Mid level

5 µΑ Low level

Series Resistance Cancellation 1000 Ω

Power Supply Sensitivity ±1 %/V

Conversion Time (Local Temperature) 11 ms Averaging enabled

Conversion Time (Remote Temperature) 32 ms Averaging enabled

Total Conversion Time 75 ms Averaging enabled

OPEN-DRAIN DIGITAL OUTPUTS

3

(ALERT, THERM, FAN _ FAU LT, DRIVE1, DRIVE2)

Output Low Voltage, V

High Level Output Leakage Current, I

OL

OH

0.4 V

0.1 1 µA V

DIGITAL INPUT LEAKAGE CURRENT

(TACH1, TACH2)

Input High Current, I

Input Low Current, I

Input Capacitance, C

IH

IL

IN

−1

1 µA VIN = 0

7 pF

DIGITAL INPUT LOGIC LEVELS

(TACH1, TACH2)

Input High Voltage, V

Input Low Voltage, V

IH

IL

2.0 5.5 V

−0.3

Hysteresis 500

OPEN-DRAIN SERIAL DATA

BUS OUTPUT (SDA)

Output Low Voltage, V

OL

High Level Output Leakage Current, I

OH

0.4 V

0.1 1 µA V

SERIAL BUS DIGITAL INPUTS

(SCL, SDA)

Input High Voltage, V

Input Low Voltage, V

IH

IL

2.1 V

0.8 V

Hysteresis 500 mV

1

+2 °C

+2 °C

µA

−40°C ≤ T

−40°C ≤ T

−40°C ≤ T

−40°C ≤ T

I

OUT

OUT

−VIN = V

A

D

D

D

= −6.0 mA; VCC = +3 V

= VCC; VCC = 3 V

CC

+0.8 V

mV p−p

I

= −6.0 mA; V

OUT

= V

OUT

CC

≤ +100°C

≤ +100°C; TA = +40°C

≤ +100°C; +20°C ≤ TA ≤ +60°C

≤ +100°C; −40°C ≤ TA ≤ +100°C

CC

Rev. 0 | Page 4 of 40

ADM1034

A

Parameter Min Typ Max Unit Test Conditions/Comments

ANALOG INPUTS

(LOCATION, REF)

Input Resistance 80 125 160 kΩ

AGTL + INPUT

(THERM)

Input High Level

0.75 ×

REF

Input Low Level 0.4 V

TACHOMETER ACCURACY

Fan Speed Measurement Accuracy ±4 %

BUF

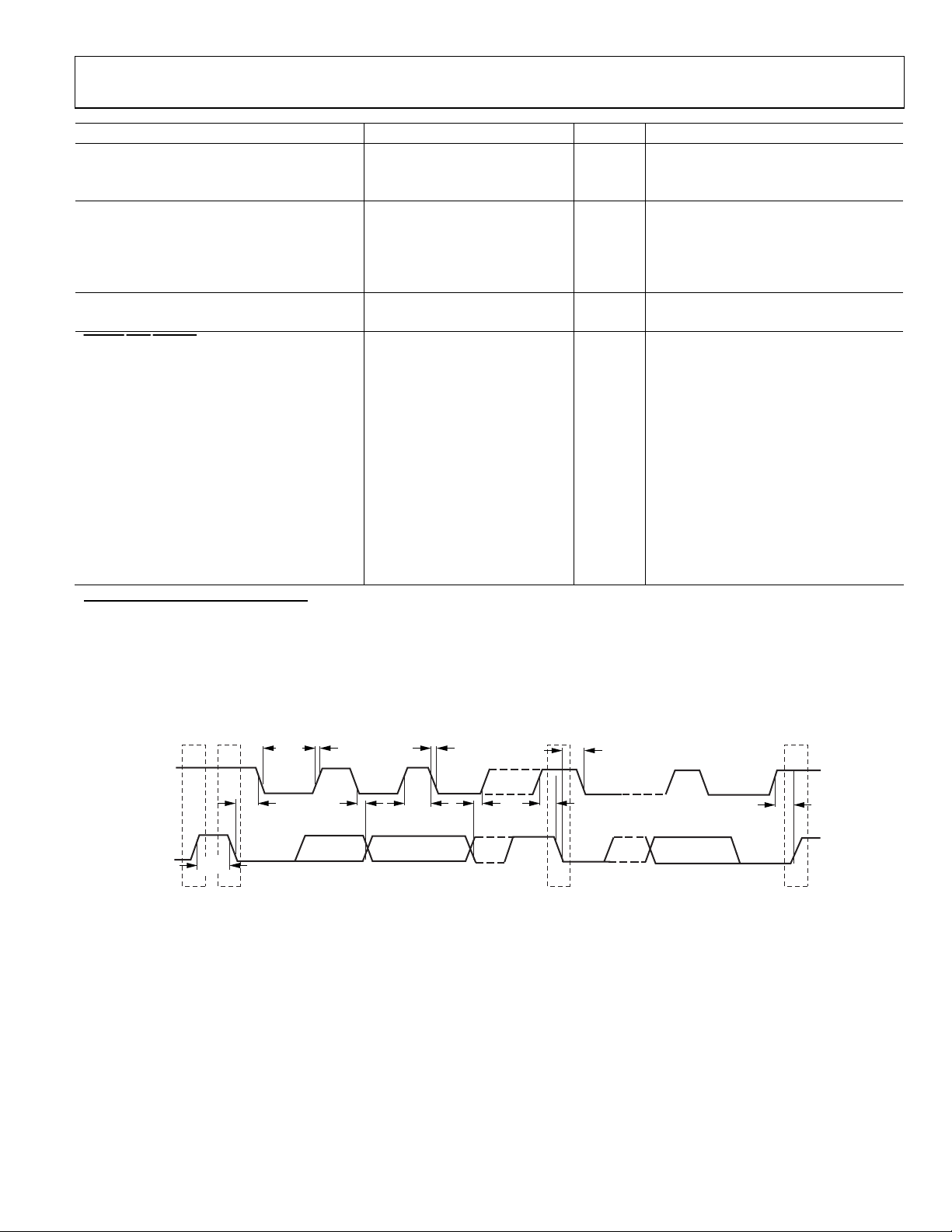

LOW

HIGH

4

SCLK

SW

SU:STA

HD:STA

SU:DAT

1.3

0.6

0.6

SU:STO

0.6

1.3

0.6

r

f

100

TIMEOUT

25

50

SERIAL BUS TIMING

Clock Frequency, f

Glitch Immunity, t

Bus Free Time, t

Start Setup Time, t

Start Hold Time, t

Stop Condition Setup Time t

SCL Low Time, t

SCL High Time, t

SCL, SDA Rise Time, t

SCL, SDA Fall Time, t

Data Setup Time, t

Detect Clock Low Timeout, t

1

Typicals are at TA = 25°C and represent most likely parametric norm. Standby current typ is measured with VCC = 3.3 V. Timing specifications are tested at logic levels of

= 0.8 V for a falling edge and VIH = 2.1 V for a rising edge.

V

IL

2

Operation at 5.5 V is guaranteed by design, not production tested.

3

Recommend use of 100 kΩ pull-up resistors for all open-drain outputs from the ADM1034.

4

Guaranteed by design, not production tested.

5

SMBus timeout disabled by default. See the section for more information. SMBUS

V

400 kHz See Figure 2

ns See Figure 2

µs See Figure 2

µs See Figure 2

µs See Figure 2

µs See Figure 2

µs See Figure 2

µs See Figure 2

1000 ns See Figure 2

300 ns See Figure 2

ns See Figure 2

35 ms See Note 5

SCL

SD

t

t

BUF

PS

HD:STA

t

LOW

t

R

t

HD:DAT

t

HIGH

t

F

t

SU:DAT

t

HD:STA

t

SU:STA

S

t

SU:STO

P

04918-0-002

Figure 2. Serial Bus Timing Diagram

Rev. 0 | Page 5 of 40

ADM1034

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Positive Supply Voltage (VCC)

Voltage on Any Input or Output Pin except

FA N_ FAU LT and LOCATION

Voltage on FA N_ FAU LT

Voltage on LOCATION VCC + 0.3 V

Input Current at Any Pin ±20 mA

Maximum Junction Temperature (TJ max) 150°C

Storage Temperature Range

Lead Temperature, Soldering (10 s) 300°C

IR Reflow Peak Temperature 220°C

ESD Rating—All Pins 1500 V

1

−0.3 V to +6.5 V

−0.3 V to +6.5 V

V

CC

−65°C to +150°C

1

During power-up the voltage on

FAN _ FAU LT

should not be higher than VCC.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to Absolute

Maximum Rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

16-Lead QSOP Package:

= 150°C/W, θJC = 39°C/W

θ

JA

Rev. 0 | Page 6 of 40

ADM1034

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

DRIVE1

2

TACH1

3

DRIVE2

TACH2

GND

V

CC

THERM

FAN_FAULT/REF D1–

ADM1034

TOP VIEW

4

(Not to Scale)

5

6

7

8

16

SCL

15

SDA

14

ALERT

13

LOCATION

12

D2+

11

D2–

10

D1+

9

04918-0-003

Figure 3. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 DRIVE1 DRIVE1 Pin Drives Fan 1. Open-drain output. Requires a pull-up resistor.

2 TACH1 Fan 1 Fan Speed Measurement Input. Connects to the fan’s TACH output to measure the fan speed.

3 DRIVE2 DRIVE2 Pin Drives Fan 2. Open-drain output. Requires a pull-up resistor.

4 TACH2 Fan 2 Fan Speed Measurement Input. Connects to the fan’s TACH output to measure the fan speed.

5 GND Ground for Analog and Digital Circuitry.

6 V

7

8

CC

THERM Can be configured as an overtemperature interrupt output, or as an input (to monitor PROCHOT output of

FA N_ FAU LT/REF FA N_ FAU LT: Open-Drain Output. Asserted low when one or both fans stall. Requires a pull-up resistor to V

Power. Can be powered by 3.3 V standby power if monitoring in low power states is required.

an INTEL CPU). A timer measures assertion times on the

REF: Analog Input Reference for the

THERM Input.

THERM pin (either input or output).

9 D1− Cathode Connection for the First Thermal Diode or Diode-Connected Transistor.

10 D1+ Anode Connection for the First Thermal Diode or Diode-Connected Transistor.

11 D2− Cathode Connection for the Second Thermal Diode or Diode-Connected Transistor.

12 D2+ Anode Connection for the Second Thermal Diode or Diode-Connected Transistor.

13 LOCATION 8-Level Analog Input. Used to determine the correct SMBus version and the SMBus address (in

fixed-and-discoverable mode) and to set the LLL bits in the UDID (in ARP-capable mode).

14

ALERT Open-Drain Output. SMBusALERT pin. Alerts the system in the case of out-of-limit events, such as over

temperature. Can be configured as sticky SMBus mode or comparator mode.

15 SDA

Serial Bus Bidirectional Data. Connects to the SMBus master’s data line. Requires pull-up resistor if not

provided elsewhere in the system.

16 SCL

Serial SMBus Clock Input. Connects to the SMBus master’s clock line. Requires pull-up resistor if not already

provided in the system.

.

CC

Rev. 0 | Page 7 of 40

ADM1034

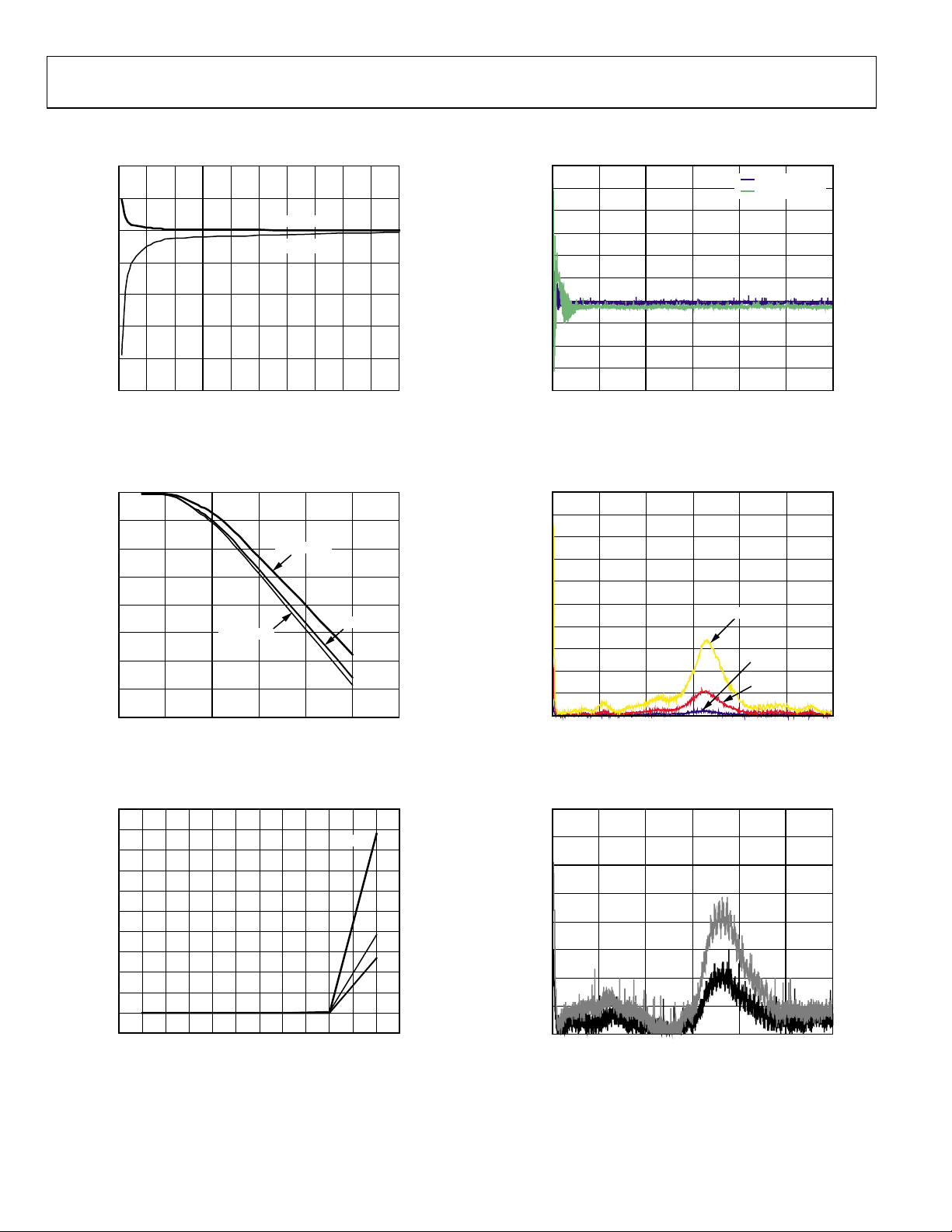

TYPICAL PERFORMANCE CHARACTERISTICS

40

20

0

–20

–40

–60

TEMPERATURE ERROR (°C)

–80

D+ TO GND

D+ TO V

CC

20

15

10

5

0

TEMPERATURE ERROR (°C)

–5

EXT 100mVpp

EXT 250mVpp

–100

0 10203040 5060708090100

LEAKAGE RESISTANCE (MΩ)

Figure 4. Temperature Error vs. PCB Track Resistance DXP to GND and V

0

–10

–20

–30

–40

–50

–60

TEMPERATURE ERROR (°C)

–70

–80

0426810

DEV 32 (°C)

CAPACITANCE (nF)

DEV 33 (°C)

DEV 31 (°C)

12

Figure 5. Remote Temperature Error vs. D+, D− Capacitance

100

90

80

70

60

50

40

30

20

TEMPERATURE ERROR (°C)

10

0

–10

12 3 4 65

SERIES RESISTANCE IN D+/D– LINES (kΩ)

DEV 33

DEV 31

DEV 32

Figure 6. Remote Temperature Error vs. Series Resistance on D+ and D−

04918-0-004

CC

04918-0-005

04918-0-006

–10

01M2M3M4M 65M

04918-0-007

M

Figure 7. Remote Temperature Error vs. Power Supply Noise Frequency

50

45

40

35

30

25

20

15

TEMPERATURE ERROR (°C)

10

5

00

01M2M 4M3M 5M 6M

NOISE FREQUENCY (Hz)

100mV

20mV

50mV

04918-0-008

Figure 8. Remote Temperature Error vs. Common-Mode Noise Frequency

Coupled on D+ and D−

4.0

3.5

3.0

2.5

2.0

1.5

1.0

TEMPERATURE ERROR (°C)

0.5

0

01M 3M2M 5M4M 6M

NOISE FREQUENCY

20mV

10mV

04918-0-009

Figure 9. Remote Temperature Error vs. Differential Mode Noise Frequency

Coupled on D+ and D−

Rev. 0 | Page 8 of 40

ADM1034

2

1

0

–1

–2

–3

ERROR (°C)

–4

–5

–6

–7

S1

S2

S3

S4

S5

–60 –40 –20 0 80 100 12040 6020 140

V1

V2

V3

V4

V5

TEMPERATURE (

MEAN

°

C)

HIGH 4 SIGMA

LOW 4 SIGMA

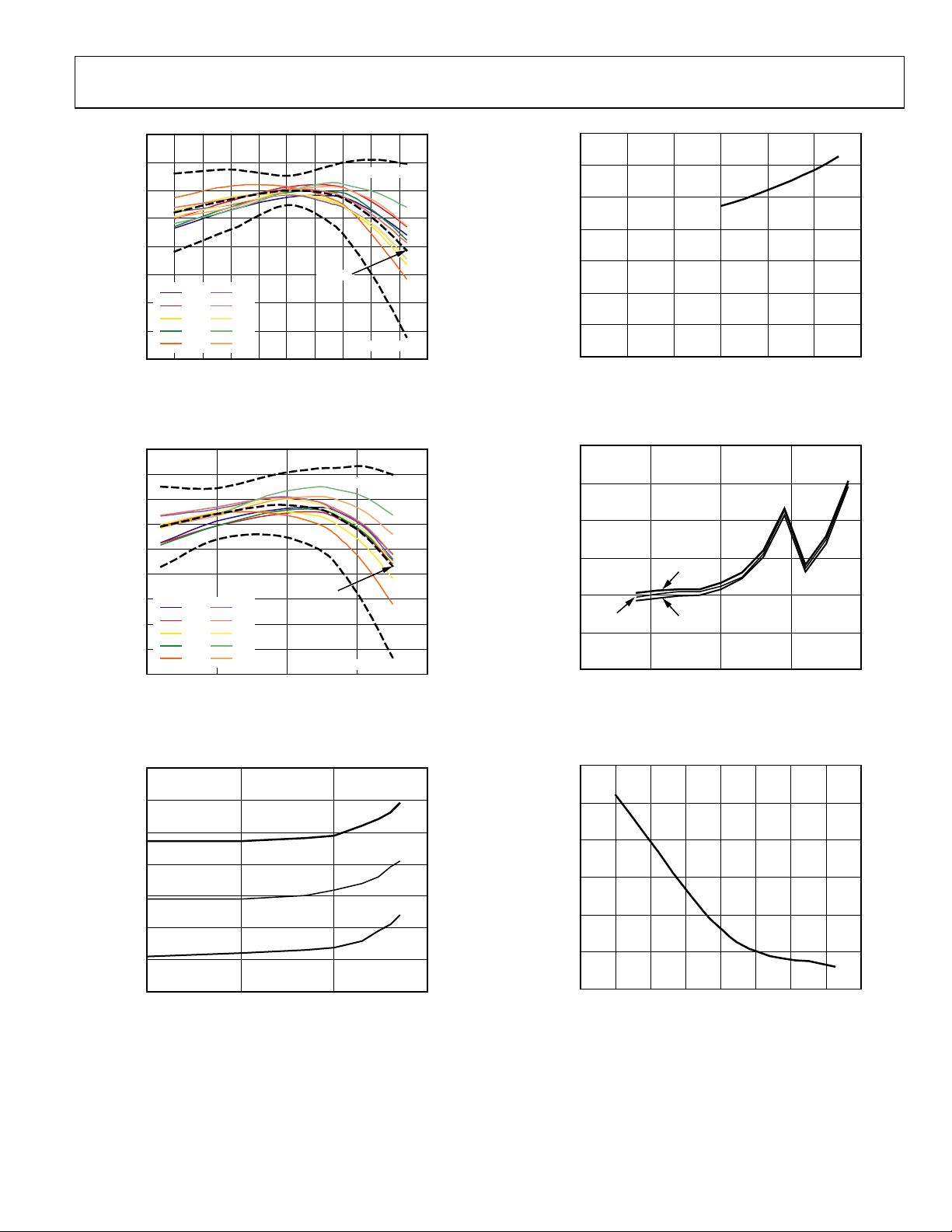

Figure 10. Remote Temperature Error vs. Actual Diode Temperature

2

1

0

–1

–2

–3

ERROR (°C)

–4

–5

–6

–7

S1

S2

S3

S4

S5

–50 0 10050 150

V1

V2

V3

V4

V5

TEMPERATURE (°C)

HIGH 4 SIGMA

MEAN

LOW 4 SIGMA

Figure 11. Local Temperature Error vs. Actual Temperature

430

04918-0-010

04918-0-011

0.7

0.6

0.5

0.4

0.3

0.2

STANDBY SUPPLY CURRENT

0.1

0

024531

SUPPLY VOLTAGE (V)

Figure 13. Standby Supply Current vs. Supply Voltage

1200

1000

800

(µA)

600

CC

I

400

DEV 33

200

0

0.01 0.1 1 10010

DEV 31

DEV 32

CONVERSION RATE (Hz)

Figure 14. Supply Current vs. Conversion Rate

1.55

04918-0-013

6

04918-0-014

420

410

400

(µA)

CC

I

390

380

370

360

1 10 1000100

FSCL (kHz)

Figure 12. Standby Supply Current vs. SCLK Frequency

DEV 31

DEV 33

DEV 32

04918-0-012

1.50

1.45

1.40

1.35

SUPPLY CURRENT

1.30

1.25

–60 –40 –20 0 10040 60 8020

TEMPERATURE (°C)

Figure 15. Supply Current vs. ADM1034 Temperature

04918-0-015

Rev. 0 | Page 9 of 40

ADM1034

0

0

FUNCTIONAL DESCRIPTION

The ADM1034 is a local- and remote-temperature monitor and

fan controller for use in a variety of applications, including

microprocessor-based systems. The device accurately monitors

remote and ambient temperature and uses that information to

quietly control the speed of a cooling fan. Whenever one of the

fans stalls, the device asserts a

The ADM1034 features a

measures assertions on the

FAN_ FAULT

THERM

THERM

I/O. As an input, this

a low signal to indicate when the measured temperature exceeds

the programmed

THERM

temperature. The ADM1034

communicates over an SMBus 2.0 interface. Its LOCATION

input determines which version of SMBus to use, as well as the

SMBus address (in fixed-and-discoverable mode) and the

LOCATION bits in the UDID (in ARP-capable mode).

INTERNAL REGISTERS

Table 4 gives a brief description of the ADM1034’s principal

internal registers. For more detailed information on the

function of each register, refer to Table 34.

SERIAL BUS INTERFACE

The ADM1034 communicates with the master via the 2-wire

SMBus 2.0 interface. It supports two versions of SMBus 2.0,

determined by the value of the LOCATION input’s resistors.

The first version is fully ARP-capable. This means that it

supports address resolution protocol (ARP), allowing the

master to dynamically address the device on power-up. It

responds to ARP commands such as “Prepare to ARP.”

The second SMBus version, fixed-and-discoverable, is

backwards-compatible with SMBus 1.0 and 1.1. In this mode,

the ADM1034 powers up with a fixed address, which is

determined by the state of the LOCATION pin on power-up.

Note: When using the ADM1034, Addresses 0xC2 and 0xCA

should not be used by any other device on the bus.

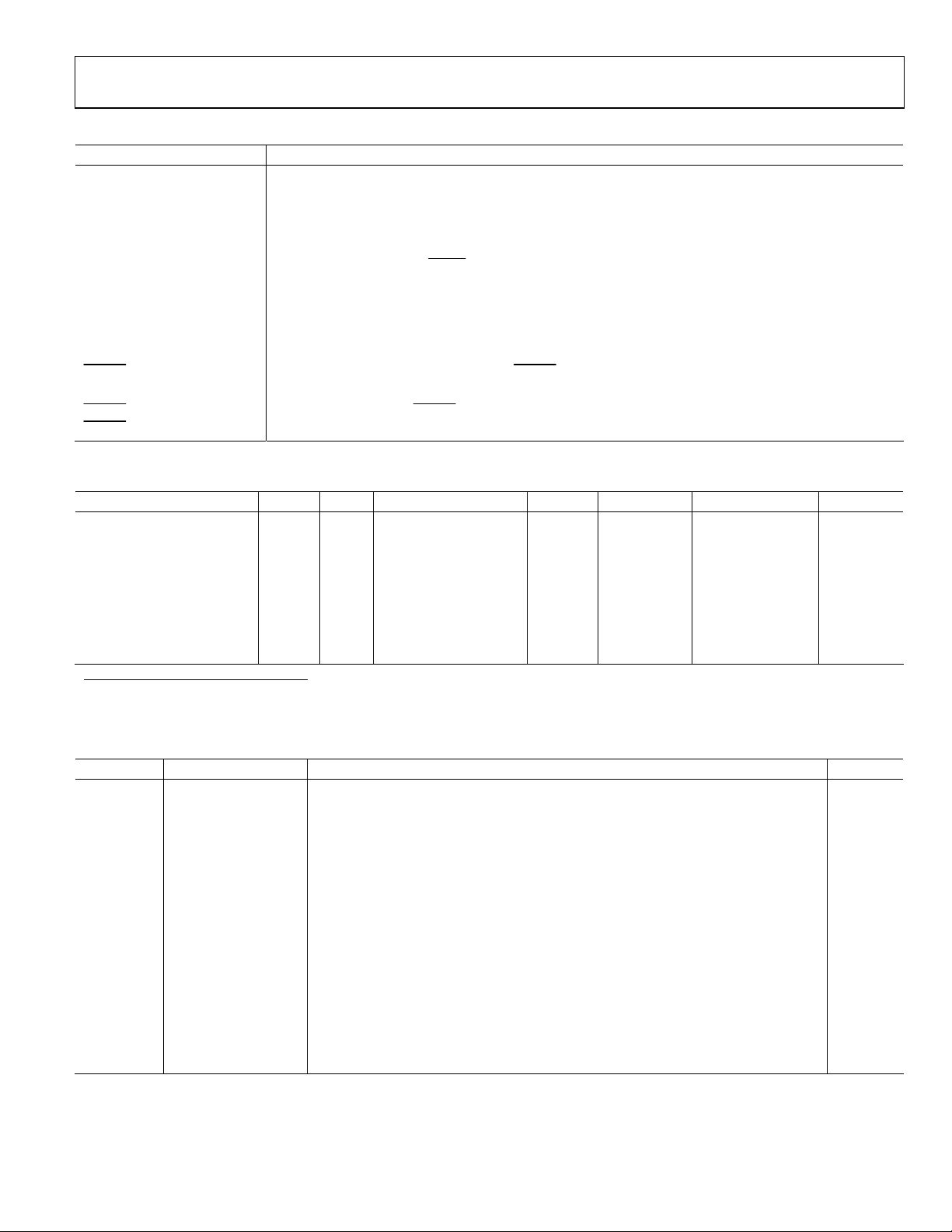

LOCATION INPUT

The LOCATION input is a resistor divider input. It has multiple

functions and can specify the SMBus version (in fixed-anddiscoverable or ARP-capable modes); the SMBus address (in

fixed-and-discoverable mode); and the LLL bits (in UDID in

ARP-capable mode).

The voltage of this 8-level input is set by a potential divider. The

voltage on LOCATION is sampled on power-up and digitized

by the on-chip ADC to determine the LOCATION input value.

Because the LOCATION input is sampled only at power-up,

changes made while power is applied have no effect.

output.

pin. As an output, it asserts

V

CC

R1

R2

GND

Figure 16. Bootstrapping the LOCATION Input

PIN 13

ADM1034

LOCATION

04918-0-016

SMBus 2.0 ARP-CAPABLE MODE

In ARP-capable mode, the ADM1034 supports features such as

address resolution protocol (ARP) and unique device identifier

(UDID). The UDID is a 128-bit message that describes the

ADM1034’s capabilities to the master. The UDID also includes a

vendor-specific ID for functionally equivalent devices.

V

CC

LOCATION = 111

LOCATION = 11

LOCATION = 101

LOCATION = 10

ADDRESS = 53h

ADDRESS = 52h

ADDRESS = 51h

ADDRESS = 50h

Figure 17. Setting Up Multiple ADM1034 Addresses in

ARP

1.5kΩ

ARP

1kΩ

ARP

1kΩ

ARP

1kΩ

FD

1kΩ

FD

1kΩ

FD

1.5kΩ

FD

GND

SMBus 2.0 ARP-Capable Mode

In SMBus 2.0 mode, this vendor-specific ID is generated by an

on-chip random number generator. This should enable two

adjacent ADM1034s in the same system to power up with a

different vendor-specific ID, allowing the master to identify the

two separate ADM1034s and assign a different address to each.

The state of the LOCATION input on power-up is also reflected

in the UDID. This is useful when there is more than one

ADM1034 in the system, so the master knows which one it is

communicating with. The complete UDID is listed in Table 6.

The SMBus 2.0 master issues both general and directed ARP

commands. A general command is directed at all ARP devices.

A directed command is targeted at a single device once an

address has been established. The PEC byte must be used for

ARP commands. (Refer to the Packet Error Checking (PEC)

section.) The ADM1034 responds to the following commands:

• Prepare to ARP (general)

• Reset device (general and directed)

• Get UDID (general and directed)

• Assign address (general)

ADM1034 NO. 1

ADM1034 NO. 2

ADM1034 NO. 3

ADM1034 NO. 4

ADM1034 NO. 5

ADM1034 NO. 6

ADM1034 NO. 7

ADM1034 NO. 8

04918-0-017

Rev. 0 | Page 10 of 40

ADM1034

Table 4. Internal Register Descriptions

Register Description

Configuration Provides control and configuration of various functions on the device.

Conversion Rate Determines the number of measurements per second completed by the ADM1034.

Address Pointer

Status Provides the status of each limit comparison.

Interrupt Mask

Value and Limit Stores the results of temperature and fan speed measurements, along with their limit values.

Offset

THERM Limit and Hysteresis Contains the temperature value at which THERM is asserted and indicates the level of hysteresis.

Look-Up Table Used to program the look-up table for the fan-speed-to-temperature profile.

THERM % Ontime and

THERM % Limit

Table 5. Resistor Ratios for Setting LOCATION Bits

Ideal Ratio R2/(R1 + R2) R1 kΩ R2 Ω Actual R2/(R1 + R2) Error % SMBus Ver SMBus Address UDID LLL

N/A 0 O/C 1 0 ARP

0.8125 18 82 0.82 +0.75 ARP1 N/A 110

0.6875 22 47 0.6812 −0.63 ARP1 N/A 101

0.5625 12 15 0.5556 −0.69 ARP1 N/A 100

0.4375 15 12 0.4444 +0.69 FD1 0x53 N/A

0.3125 47 22 0.3188 +0.63 FD1 0x52 N/A

0.1875 82 18 0.18 −0.75 FD1 0x51 N/A

N/A O/C 0 0 0 FD1 0x50 N/A

1

FD denotes fixed-and-discoverable mode, ARP denotes ARP-capable mode.

Table 6. UDID Values

Bit No. Name Function Value

<127:120> Device Capabilities

<119:112> Version/Revision UDID version number (Version 1) and silicon revision identification 00001010

<111:96> Vendor ID

<95:80> Device ID Device ID.

<79:64> Interface

<63:48> Subsystem Vendor ID Subsystem Vendor ID = 0 (subsystem fields are unsupported).

<47:32> Subsystem Device ID Subsystem Device ID = 0 (subsystem fields are unsupported).

<31:0> Vendor Specific ID

Contains the address that selects one of the other internal registers. When writing to the ADM1034, the

first byte of data is always a register address, written to the address pointer register.

Allows the option to mask

ALERTs due to particular out-of-limit conditions.

Allows the local and remote temperature channel readings to be offset by a twos complement value

written to them. These values are automatically added to the temperature values (or subtracted from them

if negative). This allows the systems designer to optimize the system if required, by adding or subtracting

up to 15.875°C from a temperature reading.

Reflects the state of the

THERM input and monitors the duration of the assertion time of the signal as a

percentage of a time window. The user can program the length of the time window.

1

Describes the ADM1034’s capabilities (for instance, that it supports PEC and uses a

N/A 111

11000001

random number address device).

Analog Devices vendor ID number, as assigned by the SBS Implementer’s Forum or

the PCI SIG.

00010001

11010100

00010000

00110100

Identifies the protocol layer interfaces supported by the ADM1034. This represents

SMBus 2.0 as the Interface version..

00000000

00000100

00000000

00000000

00000000

00000000

A unique number per device. Contains LOCATION information (LL) and a 16-bit

random number (x). See Table 5 for information on setting the LLL bits.

00000000

00000LLL

xxxxxxxx

xxxxxxxx

Rev. 0 | Page 11 of 40

ADM1034

SMBus 2.0 FIXED-AND-DISCOVERABLE MODE

The ADM1034 also supports fixed-and-discoverable mode,

which is backwards-compatible with SMBus 1.0 and 1.1. Fixedand-discoverable mode supports all the same functionality as

ARP-capable mode, except for assign address—in which case it

powers up with a fixed address and is not changed by the assign

address call. The fixed address is determined by the state of the

LOCATION pin on power-up.

SMBus 2.0 READ AND WRITE OPERATIONS

The master initiates data transfer by establishing a start

condition, defined as a high-to-low transition on the serial data

line (SDA) while the serial clock line (SCL) remains high. This

indicates that an address/data stream is to follow. All slave

peripherals connected to the serial bus respond to the start

condition and shift in the next 8 bits, which consist of a 7-bit

address (MSB first) plus an R/

direction of the data transfer (whether data is written to or read

from the slave device).

1. The peripheral that corresponds to the transmitted address

responds by pulling the data line low during the low period

before the 9th clock pulse, which is known as the

acknowledge bit. All other devices on the bus remain idle

while the selected device waits for data to be read from or

written to it. If the R/

slave device. If the R/

2. Data is sent over the serial bus in sequences of 9 clock

pulses—8 bits of data followed by an acknowledge bit from

the slave device. Transitions on the data line must occur

during the low period of the clock signal and remain stable

during the high period, because a low-to-high transition

when the clock is high may be interpreted as a stop signal.

The number of data bytes that can be transmitted over the

serial bus in a single read or write operation is limited only

by what the master and slave devices can handle.

bit. This last bit determines the

W

bit is a 0, the master writes to the

W

bit is a 1, the master reads from it.

W

It is not possible to mix read and write in one operation,

because the type of operation is determined at the beginning

and cannot be changed without starting a new operation.

To write data to one of the device data registers or to read data

from it, the address pointer register (APR) must be set so that

the correct data register is addressed; then data can be written

into that register or read from it. The first byte of a write

operation always contains an address that is stored in the APR.

If data is to be written to the device, then the write operation

contains a second data byte, which is written to the register

selected by the APR.

As illustrated in Figure 18, the device address is sent over the

bus, followed by R/

bytes. The first data byte is the address of the internal data

register to be written to, which is stored in the APR. The second

data byte is the data to be written to the internal data register.

When reading data from a register there are two possibilities.

If the ADM1034’s APR value is unknown or incorrect, it must

be set to the correct value before data can be read from the

desired data register. To do this, perform a write to the ADM1034

as before, but send only the data byte containing the register.

(See Figure 19.) A read operation is then performed, using the

serial bus address and the R/

byte read from the data register. (See Figure 20.)

However, if the APR is already at the desired address, data can

be read from the corresponding data register without first

writing to the APR. In this case, Figure 19 can be omitted.

In Figure 18 to Figure 20, the serial bus address is determined

by the state of the LOCATION pin on power-up.

set to 0. This is followed by two data

W

bit set to 1, followed by the data

W

3. When all data bytes have been read or written, stop

conditions are established. In write mode, the master pulls

the data line high during the 10th clock pulse to assert a

stop condition. In read mode, the master device overrides

the acknowledge bit by pulling the data line high during

the low period before the 9th clock pulse. This is known as

no acknowledge. The master takes the data line low during

the low period before the 10th clock pulse, then high

during the 10th clock pulse to assert a stop condition.

Rev. 0 | Page 12 of 40

Loading...

Loading...