REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

ADM1020

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

8-Lead, Low-Cost, System

Temperature Monitor

FUNCTIONAL BLOCK DIAGRAM

LOCAL TEMPERATURE

LOW LIMIT COMPARATOR

LOCAL TEMPERATURE

HIGH LIMIT COMPARATOR

REMOTE TEMPERATURE

LOW LIMIT COMPARATOR

REMOTE TEMPERATURE

HIGH LIMIT COMPARATOR

REMOTE TEMPERATURE

VALUE REGISTER

LOCAL TEMPERATURE

VALUE REGISTER

RUN/STANDBY

8-BIT A-TO-D

CONVERTER

BUSY

ANALOG

MUX

ON-CHIP TEMP.

SENSOR

D+

D–

STATUS REGISTER

LOCAL TEMPERATURE

LOW LIMIT REGISTER

LOCAL TEMPERATURE

HIGH LIMIT REGISTER

REMOTE TEMPERATURE

LOW LIMIT REGISTER

REMOTE TEMPERATURE

HIGH LIMIT REGISTER

CONFIGURATION

REGISTER

CONVERSION RATE

REGISTER

ONE-SHOT

REGISTER

ADDRESS POINTER

REGISTER

INTERRUPT

MASKING

ALERT

ADM1020

SMBUS INTERFACE

EXTERNAL DIODE OPEN-CIRCUIT

V

DD

GND SDATA SCLK ADD

PRODUCT DESCRIPTION

The ADM1020 is a two-channel digital thermometer and

under/over temperature alarm, intended for use in personal

computers and other systems requiring thermal monitoring and

management. The device can measure the temperature of a

microprocessor using a diode-connected NPN or PNP transistor, which may be provided on-chip in the case of the Pentium

®

II or similar processors, or can be a low-cost discrete device

such as the 2N3904. A novel measurement technique cancels

out the absolute value of the transistor’s base emitter voltage, so

that no calibration is required. The second measurement channel measures the output of an on-chip temperature sensor, to

monitor the temperature of the device and its environment.

The ADM1020 communicates over a two-wire serial interface

compatible with System Management Bus (SMBus) standards.

Under and over temperature limits can be programmed into the

devices over the serial bus, and an ALERT output signals when

the on-chip or remote temperature is out of range. This output

can be used as an interrupt, or as an SMBus alert.

SMBus is a trademark of Intel Corporation.

Pentium is a registered trademark of Intel Corporation.

FEATURES

On-Chip and Remote Temperature Sensing

No Calibration Necessary

1ⴗC Accuracy for On-Chip Sensor

3ⴗC Accuracy for Remote Sensor

Programmable Over/Under Temperature Limits

Programmable Conversion Rate

2-Wire SMBus™ Serial Interface

Supports SMBus Alert

70 A Max Operating Current

3 A Standby Current

+3 V to +5.5 V Supply

8-Lead SOIC Package

APPLICATIONS

Desktop Computers

Notebook Computers

Smart Batteries

Industrial Controllers

Telecommunication Equipment

Instrumentation

REV. 0–2–

ADM1020–SPECIFICATIONS

(TA = T

MIN

to T

MAX

, VDD = 3.0 V to 3.6 V, unless otherwise noted)

Parameter Min Typ Max Units Test Conditions/Comments

POWER SUPPLY AND ADC

Temperature Resolution 1 °C Guaranteed No Missed Codes

Temperature Error, Local Sensor ±1 °C

–3 +3 °C

Temperature Error, Remote Sensor –3 +3 °CT

A

= +60°C to +100°C

–5 +5 °C

Supply Voltage Range 3 3.6 V Note 1

Undervoltage Lockout Threshold 2.5 2.7 2.95 V V

DD

Input, Disables ADC,

Rising Edge

Undervoltage Lockout Hysteresis 25 mV

Power-On Reset Threshold 0.9 1.7 2.2 V V

DD

, Falling Edge

2

POR Threshold Hysteresis 50 mV

Standby Supply Current 3 10 µAV

DD

= 3.3 V, No SMBus Activity

4 µA SCLK at 10 kHz

Average Operating Supply Current 70 190 µA 0.25 Conversions/Sec Rate

Auto-Convert Mode, Averaged Over 4 Seconds 160 290 µA 2 Conversions/Sec Rate

Conversion Time 65 115 170 ms From Stop Bit to Conversion

Complete (Both Channels)

Remote Sensor Source Current D+ Forced to D– + 0.65 V

90 µA High Level

5.5 µA Low Level

D– Source Voltage 0.7 V

Address Pin Bias Current 50 µA Momentary at Power-On Reset

SMBUS INTERFACE

Logic Input High Voltage, V

IH

STBY, SCLK, SDATA 2.2 V VDD = 3 V to 5.5 V

Logic Input Low Voltage, V

IL

STBY, SCLK, SDATA 0.8 V VDD = 3 V to 5.5 V

SMBus Output Low Sink Current 6 mA SDATA Forced to 0.6 V

ALERT Output Low Sink Current 1 mA ALERT Forced to 0.4 V

Logic Input Current, I

IH

, I

IL

–1 +1 µA

SMBus Input Capacitance, SCLK, SDATA 5 pF

SMBus Clock Frequency 0 100 kHz

SMBus Clock Low Time, t

LOW

4.7 µst

LOW

Between 10% Points

SMBus Clock High Time, t

HIGH

4 µst

HIGH

Between 90% Points

SMBus Start Condition Setup Time, t

SU:STA

4.7 µs

SMBus Repeat Start Condition 250 ns Between 90% and 90% Points

Setup Time, t

SU:STA

SMBus Start Condition Hold Time, t

HD:STA

4 µs Time from 10% of SDATA to

90% of SCLK

SMBus Stop Condition Setup Time, t

SU:STO

4 µs Time from 90% of SCLK to 10%

of SDATA

SMBus Data Valid to SCLK 250 ns Time from 10% or 90% of

Rising Edge Time, t

SU:DAT

SDATA to 10% of SCLK

SMBus Data Hold Time, t

HD:DAT

0 µs

SMBus Bus Free Time, t

BUF

4.7 µs Between Start/Stop Condition

SCLK Falling Edge to SDATA

Valid Time, t

VD,DAT

1 µs Master Clocking in Data

NOTES

1

Operation at VDD = +5 V guaranteed by design, not production tested.

2

Guaranteed by design, not production tested.

Specifications subject to change without notice.

REV. 0

ADM1020

–3–

ABSOLUTE MAXIMUM RATINGS*

Positive Supply Voltage (VDD) to GND . . . . . . . . –0.3 V, +6 V

D+, ADD . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, V

DD

+ 0.3 V

D– to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V, +0.6 V

SCLK, SDATA, ALERT . . . . . . . . . . . . . . . . . . . . . –0.3 V, +6 V

Input Current, SDATA . . . . . . . . . . . . . . . . . . . . . –1, ±50 mA

Input Current, D– . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±1 mA

ESD Rating, all Pins (Human Body Model) . . . . . . . . 4000 V

Continuous Power Dissipation

Up to +70°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 650 mW

Derating above +70°C . . . . . . . . . . . . . . . . . . . . 6.7 mW/°C

Operating Temperature Range . . . . . . . . . . –55°C to +125°C

Maximum Junction Temperature (T

J

max) . . . . . . . . . +150°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature, Soldering

Vapor Phase 60 sec . . . . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared 15 sec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +200°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

THERMAL CHARACTERISTICS

8-Lead SOIC Package: θ

JA

= 150°C/Watt.

PIN FUNCTION DESCRIPTION

Pin

No. Mnemonic Description

1V

DD

Positive Supply, +3 V to +5.5 V

2 D+ Positive Connection to Emitter of Remote

Temperature Sensor.

3 D– Negative Connection to Base of Remote

Temperature Sensor.

4 ADD Address Select Three-State Logic Input.

5 GND Supply 0 V Connection.

6 ALERT Open-Drain Logic Output Used as

Interrupt or SMBus Alert.

7 SDATA Logic Input/Output, SMBus Serial Data.

Open-Drain Output.

8 SCLK Logic Input, SMBus Serial Clock.

PIN CONFIGURATION

TOP VIEW

(Not to Scale)

8

7

6

5

1

2

3

4

V

DD

D+

D–

ADD

SCLK

SDATA

ALERT

GND

ADM1020

ORDERING GUIDE

Temperature Package Package

Model* Range Description Option

ADM1020AR-REEL 0°C to +85°C 8-Lead Small Outline (SOIC) SO-8

ADM1020AR-REEL7

*REEL contains 2500 pieces; REEL7 contains 1000 pieces.

REV. 0

ADM1020

–4–

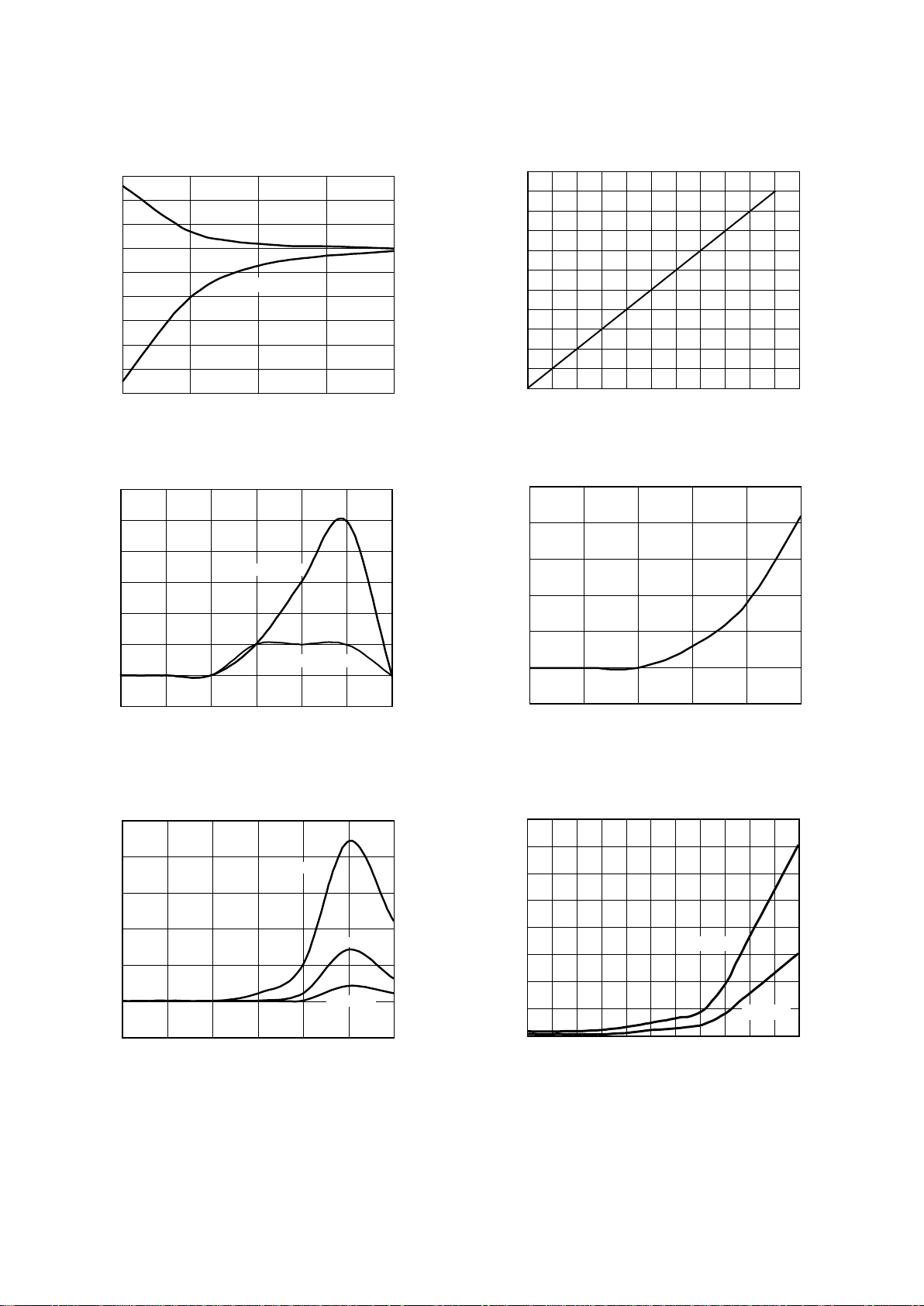

LEAKAGE RESISTANCE – MV

30

20

–60

1.0 1003.3

TEMPERATURE ERROR – 8C

10 30

–10

–30

–40

–50

10

0

–20

D+ TO GND

D+ TO VCC (5V)

Figure 1. Temperature Error vs. PC Board Track Resistance

FREQUENCY – Hz

6

–1

50 50M500

TEMPERATURE ERROR – 8C

5k

50k

500k 5M

5

4

3

1

0

2

250mV p-p REMOTE

100mV p-p REMOTE

Figure 2. Temperature Error vs. Power Supply Noise

Frequency

FREQUENCY – Hz

–5

50 50M500

TEMPERATURE ERROR – 8C

5k 50k 500k 5M

25

20

15

5

0

10

25mV p-p

50mV p-p

100mV p-p

Figure 3. Temperature Error vs. Common-Mode Noise

Frequency

MEASURED TEMPERATURE

0 11010

READING

20 30 40 50

120

20

30

0

10

40

50

60

70

80

90

100

60 70 80 90 100

Figure 4. Pentium II Temperature Measurement vs.

ADM1020 Reading

D+ AND D– CAPACITANCE – nF

25

20

–5

1.0 102.2

TEMPERATURE ERROR – 8C

3.2 4.7 7

15

10

5

0

Figure 5. Temperature Error vs. Capacitance Between

D+ and D–

SCLK FREQUENCY – Hz

80

30

0

0

1M1k

SUPPLY CURRENT – mA

5k 10k 25k 50k 75k 100k 250k 500k 750k

70

40

20

10

60

50

VCC = +5V

VCC = +3V

Figure 6. Standby Supply Current vs. Clock Frequency

–Typical Performance Characteristics

REV. 0

ADM1020

–5–

FREQUENCY – Hz

10

0

50 50M500

TEMPERATURE ERROR – 8C

5k 50k 500k 5M

6

5

4

2

1

3

10mV SQ. WAVE

9

8

7

100k 25M

Figure 7. Temperature Error vs. Differential-Mode Noise

Frequency

CONVERSION RATE – Hz

200

0

0.0625 80.125

SUPPLY CURRENT – mA

0.25 0.5 1 2 4

180

80

60

40

20

140

100

160

120

VCC = +5V

VCC = +3.3V

Figure 8. Operating Supply Current vs. Conversion

Rate

SUPPLY VOLTAGE – Volts

100

40

–20

0

1.1

SUPPLY CURRENT – mA

1.3 1.5 1.7 1.9 2.1 2.3 2.5 2.7 2.9 3.5 4.5

80

60

20

0

ADDX = HI-Z

ADDX = GND

Figure 9. Standby Supply Current vs. Supply Voltage

TIME – Sec

125

100

0

T = 0 T = 10T = 2

TEMPERATURE – 8C

T = 4 T = 6 T = 8

75

50

25

IMMERSED

IN +1158C

FLUORINERT BATH

Figure 10. Response to Thermal Shock

FUNCTIONAL DESCRIPTION

The ADM1020 contains a two-channel A-to-D converter with

special input-signal conditioning to enable operation with

remote and on-chip diode temperature sensors. When the

ADM1020 is operating normally, the A-to-D converter operates

in a free-running mode. The analog input multiplexer alternately

selects either the on-chip temperature sensor to measure its local

temperature, or the remote temperature sensor. These signals

are digitized by the ADC and the results stored in the local and

remote temperature value registers as 8-bit, twos complement

words.

The measurement results are compared with local and remote,

high and low temperature limits, stored in four on-chip registers. Out of limit comparisons generate flags that are stored in

the Status Register, and one or more out-of-limit results will

cause the ALERT output to pull low.

The limit registers can be programmed, and the device controlled and configured, via the serial System Management Bus

(SMBus). The contents of any register can also be read back via

the SMBus.

Control and configuration functions consist of:

– switching the device between normal operation and standby

mode.

– masking or enabling the ALERT output.

– selecting the conversion rate.

MEASUREMENT METHOD

A simple method of measuring temperature is to exploit the

negative temperature coefficient of a diode, or the base-emitter

voltage of a transistor, operated at constant current. Unfortunately, this technique requires calibration to null out the effect

of the absolute value of V

BE

, which varies from device to device.

The technique used in the ADM1020 is to measure the change

in V

BE

when the device is operated at two different currents.

This is given by:

∆

VBE = KT/q × ln (N)

where:

K is Boltzmann’s constant.

q is charge on the electron (1.6 × 10

–19

Coulombs).

T is absolute temperature in Kelvins.

N is ratio of the two currents.

REV. 0

ADM1020

–6–

Figure 11 shows the input signal conditioning used to measure

the output of an external temperature sensor. This figure shows

the external sensor as a substrate transistor, provided for temperature monitoring on some microprocessors, but it could

equally well be a discrete transistor. If a discrete transistor is

used, the collector will not be grounded, and should be linked to

the base. To prevent ground noise interfering with the measurement, the more negative terminal of the sensor is not referenced

to ground, but is biased above ground by an internal diode at

the D– input. If the sensor is operating in a noisy environment,

C1 may optionally be added as a noise filter. Its value is typically 2200 pF but should be no more than 3000 pF. See the

section on Layout Considerations for more information on C1.

To measure ∆V

BE

, the sensor is switched between operating

currents of I and N × I. The resulting waveform is passed

through a 65 kHz low-pass filter to remove noise, hence to a

chopper-stabilized amplifier that performs the functions of amplification and rectification of the waveform to produce a dc

voltage proportional to ∆V

BE

. This voltage is measured by the

ADC to give a temperature output in 8-bit twos complement

format. To further reduce the effects of noise, digital filtering is

performed by averaging the results of 16 measurement cycles.

Signal conditioning and measurement of the internal temperature sensor is performed in a similar manner.

TEMPERATURE DATA FORMAT

One LSB of the ADC corresponds to 1°C, so the ADC can

theoretically measure from –128°C to +127°C, although the

practical lowest value is limited to –65°C due to device maxi-

mum ratings. The temperature data format is shown in Table I.

The results of the local and remote temperature measurements

are stored in the local and remote temperature value registers,

and are compared with limits programmed into the local and

remote high and low limit registers.

C1*

D+

D–

REMOTE

SENSING

TRANSISTOR

IN 3 I I

BIAS

V

DD

V

OUT+

TO ADC

V

OUT–

BIAS

DIODE

*CAPACITOR C1 IS OPTIONAL.

IT IS ONLY NECESSARY IN NOISY ENVIRONMENTS.

C1 = 2.2nF TYPICAL, 3nF MAX.

LOWPASS FILTER

f

C

= 65kHz

Figure 11. Input Signal Conditioning

Table I. Temperature Data Format

Temperature Digital Output

–128°C 1 000 0000

–125°C 1 000 0011

–100°C 1 001 1100

–75°C 1 011 0101

–50°C 1 100 1110

–25°C 1 110 0111

–1°C 1 111 1111

0°C 0 000 0000

+1°C 0 000 0001

+10°C 0 000 1010

+25°C 0 001 1001

+50°C 0 011 0010

+75°C 0 100 1011

+100°C 0 110 0100

+125°C 0 111 1101

+127°C 0 111 1111

ADM1020 REGISTERS

The ADM1020 contains nine registers that are used to store the

results of remote and local temperature measurements, high and

low temperature limits, and to configure and control the device.

A description of these registers follows, and further details are

given in Tables II to IV. It should be noted that the ADM1020’s

registers are dual port, and have different addresses for read and

write operations. Attempting to write to a read address, or to

read from a write address, will produce an invalid result. Register addresses above 0F are reserved for future use or used for

factory test purposes and should not be written to.

Address Pointer Register

The Address Pointer Register itself does not have, or require, an

address, as it is the register to which the first data byte of every

write operation is automatically written. This data byte is an

address pointer that sets up one of the other registers for the

second byte of the write operation, or for a subsequent read

operation.

REV. 0

ADM1020

–7–

The power-on default value of the Address Pointer Register is

00h, so if a read operation is performed immediately after poweron, without first writing to the address pointer, the value of the

local temperature will be returned, since its register address is

00h.

Value Registers

The ADM1020 has two registers to store the results of local and

remote temperature measurements. These registers are written

to by the ADC and can only be read over the SMBus.

Status Register

Bit 7 of the Status Register indicates that the ADC is busy converting when it is high. Bits 5 to 3 are flags that indicate the

results of the limit comparisons.

If the local and/or remote temperature measurement is above

the corresponding high temperature limit or below the corresponding low temperature limit, then one or more of these flags

will be set. Bit 2 is a flag that is set if the remote temperature

sensor is open-circuit. These five flags are NOR’d together, so

that if any of them are high, the ALERT interrupt latch will be

set and the ALERT output will go low. Reading the Status

Register will clear the five flag bits, provided the error conditions that caused the flags to be set have gone away. While a

limit comparator is tripped due to a value register containing an

out-of-limit measurement, or the sensor is open-circuit, the

corresponding flag bit cannot be reset. A flag bit can only be

reset if the corresponding value register contains an in-limit

measurement, or the sensor is good.

The ALERT interrupt latch is not reset by reading the Status

Register, but will be reset when the ALERT output has been

serviced by the master reading the device address, provided the

error condition has gone away and the Status Register flag bits

have been reset.

Table II. Status Register Bit Assignments

Bit Name Function

7 BUSY 1 When ADC Converting

6 LHIGH* 1 When Local High-Temp Limit Tripped

5 LLOW* 1 When Local Low-Temp Limit Tripped

4 RHIGH* 1 When Remote High-Temp Limit Tripped

3 RLOW* 1 When Remote Low-Temp Limit Tripped

2 OPEN* 1 When Remote Sensor Open-Circuit

1–0 Reserved

*These flags stay high until the Status Register is read or they are reset by POR.

Configuration Register

Two bits of the Configuration Register are used. If Bit 6 is 0,

which is the power-on default, the device is in operating mode

with the ADC converting. If Bit 6 is set to 1, the device is in

standby mode and the ADC does not convert. Standby mode

can also be selected by taking the STBY pin low.

Bit 7 of the configuration register is used to mask the ALERT

output. If Bit 7 is 0, which is the power-on default, the ALERT

output is enabled. If Bit 7 is set to 1, the ALERT output is

disabled.

Table III. List of Registers

Read Address (Hex) Write Address (Hex) Name Power-On Default

Not Applicable Not Applicable Address Pointer Undefined

00 Not Applicable Local Temperature Value 0000 0000 (00h)

01 Not Applicable Remote Temperature Value 0000 0000 (00h)

02 Not Applicable Status Undefined

03 09 Configuration 0000 0000 (00h)

04 0A Conversion Rate 0000 0010 (02h)

05 0B Local Temperature High Limit 0111 1111 (7Fh) (127°C)

06 0C Local Temperature Low Limit 1100 1001 (C9h) (–55°C)

07 0D Remote Temperature High Limit 0111 1111 (7Fh) (127°C)

08 0E Remote Temperature Low Limit 1100 1001 (C9h) (–55°C)

Not Applicable 0F One-Shot See Note 1

10 Not Applicable Reserved Undefined (Note 2)

11 13 Reserved Undefined (Note 2)

12 14 Reserved Undefined (Note 2)

15 16 Reserved 1000 0000 (Note 2)

17 18 Reserved Undefined (Note 2)

19 Not Applicable Reserved 0000 0000 (Note 2)

20 21 Reserved Undefined

FE Not Applicable Manufacturer ID 0100 0001 (41h)

FF Not Applicable Die Revision Code Undefined

NOTES

1

Writing to address 0F causes the ADM1020 to perform a single measurement. It is not a data register as such and it does not matter what data is written to it.

2

These registers are reserved for future versions of the device.

REV. 0

ADM1020

–8–

Table IV. Configuration Register Bit Assignments

Power-On

Bit Name Function Default

7 MASK1 0 = ALERT Enabled 0

1 = ALERT Masked

6 RUN/STOP 0 = Run; 1 = Standby 0

5–0 Reserved 0

Conversion Rate Register

The lowest three bits of this register are used to program the

conversion rate by dividing the ADC clock by 1, 2, 4, 8, 16, 32,

64 or 128, to give conversion times from 125 ms (code 07h) to

16 seconds (code 00h). This register can be written to and read

back over the SMBus. The higher five bits of this register are

unused and must be set to zero. Use of slower conversion times

greatly reduces the device power consumption, as shown in

Table V.

Table V. Conversion Rate Register Codes

Average Supply Current

Data Conversion/Sec A Typ at V

CC

= 3.3 V

00h 0.0625 42

01h 0.125 42

02h 0.25 42

03h 0.5 48

04h 1 60

05h 2 82

06h 4 118

07h 8 170

08h to FFh Reserved

Limit Registers

The ADM1020 has four Limit Registers to store local and remote, high and low temperature limits. These registers can be

written to and read back, over the SMBus. The high limit registers perform a > comparison while the low limit registers perform a < comparison. For example, if the high limit register is

programmed with 80°C, then measuring 81°C will result in an

alarm condition.

One-Shot Register

The One-Shot Register is used to initiate a single conversion

and comparison cycle when the ADM1020 is in standby mode,

after which the device returns to standby. This is not a data

register as such and it is the write operation that causes the oneshot conversion. The data written to this address is irrelevant

and is not stored.

SERIAL BUS INTERFACE

Control of the ADM1020 is carried out via the serial bus. The

ADM1020 is connected to this bus as a slave device, under the

control of a master device, e.g., the PIIX4

ADDRESS PIN

In general, every SMBus device has a 7-bit device address (except

for some devices that have extended, 10-bit addresses). When

the master device sends a device address over the bus, the slave

device with that address will respond. The ADM1020 has an

address select pin, ADD to allow selection of the device address, so that more than one ADM1020 can be used on the

same bus, and/or to avoid conflict with other devices. Although

only one address pins is provided, it is a three-level input, and

can be grounded, left unconnected, or tied to V

DD

, so that a

total of three different addresses are possible, as shown in

Table VI.

It should be noted that the state of the address pin is only

sampled at power-up, so changing it after power-up will have

no effect.

Table VI. Device Addresses

ADD Device Address

0 1001 100

NC 1001 101

1 1001 110

NOTE: ADD is sampled at power-up only.

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a START

condition, defined as a high-to-low transition on the serial

data line SDATA, while the serial clock line SCLK remains

high. This indicates that an address/data stream will follow.

All slave peripherals connected to the serial bus respond to

the START condition, and shift in the next eight bits, consisting of a 7-bit address (MSB first) plus a R/W bit, which

determines the direction of the data transfer, i.e., whether

data will be written to or read from the slave device.

The peripheral whose address corresponds to the transmitted

address responds by pulling the data line low during the low

period before the ninth clock pulse, known as the Acknowledge Bit. All other devices on the bus now remain idle while

the selected device waits for data to be read from or written

to it. If the R/W bit is a 0, the master will write to the slave

device. If the R/W bit is a 1, the master will read from the

slave device.

2. Data is sent over the serial bus in sequences of nine clock

pulses, eight bits of data followed by an Acknowledge Bit from

the slave device. Transitions on the data line must occur

during the low period of the clock signal and remain stable

during the high period, as a low-to-high transition when the

clock is high may be interpreted as a STOP signal. The number of data bytes that can be transmitted over the serial bus

in a single READ or WRITE operation is limited only by

what the master and slave devices can handle.

3. When all data bytes have been read or written, stop condi-

tions are established. In WRITE mode, the master will pull

the data line high during the 10th clock pulse to assert a

STOP condition. In READ mode, the master device will

override the acknowledge bit by pulling the data line high

during the low period before the 9th clock pulse. This is

known as no acknowledge. The master will then take the

data line low during the low period before the 10th clock

pulse, then high during the 10th clock pulse to assert a

STOP condition.

Any number of bytes of data may be transferred over the

serial bus in one operation, but it is not possible to mix read

and write in one operation, because the type of operation is

determined at the beginning and cannot subsequently be

changed without starting a new operation.

REV. 0

ADM1020

–9–

In the case of the ADM1020, write operations contain either one or two bytes, while read operations contain one

byte, and perform the following functions:

To write data to one of the device data registers or read data

from it, the Address Pointer Register must be set so that the

correct data register is addressed, then data can be written

into that register or read from it. The first byte of a write

operation always contains a valid address that is stored in

the Address Pointer Register. If data is to be written to the

device, then the write operation contains a second data byte

that is written to the register selected by the address pointer

register.

This is

illustrated in Figure 12a. The device address is sent over

the bus followed by R/W set to 0. This is followed by two data

bytes. The first data byte is the address of the internal data

register to be written to, which is stored in the Address Pointer

Register. The second data byte is the data to be written to the

internal data register.

When reading data from a register there are two possibilities:

1. If the ADM1020's Address Pointer Register value is unknown or not the desired value, it is first necessary to set it

to the correct value before data can be read from the desired

data register. This is done by performing a write to the

ADM1020 as before, but only the data byte containing the

register read address is sent, as data is not to be written to

the register. This is shown in Figure 12b.

A read operation is then performed consisting of the serial bus

address, R/W bit set to 1, followed by the data byte read from

the data register. This is shown in Figure 12c.

2. If the Address Pointer Register is known to be already at the

desired address, data can be read from the corresponding

data register without first writing to the Address Pointer

Register, so Figure 12b can be omitted.

NOTES

1. Although it is possible to read a data byte from a data register

without first writing to the Address Pointer Register, if the

Address Pointer Register is already at the correct value, it is

not possible to write data to a register without writing to the

Address Pointer Register, because the first data byte of a

write is always written to the Address Pointer Register.

2. Don't forget that the ADM1020 registers have different addresses for read and write operations. The write address of a

register must be written to the address pointer if data is to be

written to that register, but it is not possible to read data

from that address. The read address of a register must be

written to the address pointer before data can be read from

that register.

R/W

A6

SCLK

SDATA

A5 A4 A3 A2 A1 A0 D7

D6

D5 D4 D3 D2 D1

D0

ACK. BY

ADM1020

START BY

MASTER

191

ACK. BY

ADM1020

9

D7 D6

D5 D4 D3 D2 D1

D0

ACK. BY

ADM1020

STOP BY

MASTER

1

9

SCL (CONTINUED)

SDA (CONTINUED)

FRAME 1

SERIAL BUS ADDRESS BYTE

FRAME 3

DATA BYTE

FRAME 2

ADDRESS POINTER REGISTER BYTE

Figure 12a. Writing a Register Address to the Address Point Register, then Writing Data to the Selected Register

R/W

A6

SCLK

SDATA A5 A4

A3 A2

A1 A0

D7 D6

D5

D4

D3

D2

D1

D0

ACK. BY

ADM1020

STOP BY

MASTER

START BY

MASTER

191

ACK. BY

ADM1020

9

FRAME 1

SERIAL BUS ADDRESS BYTE

FRAME 2

ADDRESS POINTER REGISTER BYTE

Figure 12b. Writing to the Address Pointer Register Only

R/W

A6

SCLK

SDATA

A5 A4 A3 A2 A1 A0 D7

D6

D5

D4 D3

D2

D1 D0

NO ACK.

BY MASTER

STOP BY

MASTER

START BY

MASTER

19

1

ACK. BY

ADM1020

9

FRAME 1

SERIAL BUS ADDRESS BYTE

FRAME 2

DATA BYTE FROM ADM1020

Figure 12c. Reading Data from a Previously Selected Register

REV. 0

ADM1020

–10–

ALERT OUTPUT

The ALERT output goes low whenever an out-of limit measurement is detected, or if the remote temperature sensor is opencircuit. It is an open-drain and requires a 10 kΩ pull-up to V

DD

.

Several ALERT outputs can be wire-ANDED together, so that

the common line will go low if one or more of the ALERT outputs goes low.

The ALERT output can be used as an interrupt signal to a

processor, or it may be used as an SMBALERT. Slave devices

on the SMBus can not normally signal to the master that they

want to talk, but the SMBALERT function allows them to do so.

One or more ALERT outputs are connected to a common

SMBALERT line connected to the master. When the

SMBALERT line is pulled low by one of the devices, the

following procedure occurs as illustrated in Figure 13.

MASTER

RECEIVES

SMBALERT

START

ALERT

RESPONSE ADDRESS

RD ACK

DEVICE

ADDRESS

NO

ACK

STOP

DEVICE SENDS

ITS ADDRESS

MASTER SENDS

ARA AND READ

COMMAND

Figure 13 Use of

SMBALERT

1. SMBALERT pulled low.

2. Master initiates a read operation and sends the Alert Response Address (ARA = 0001 100). This is a general call

address that must not be used as a specific device address.

3. The device whose ALERT output is low responds to the

Alert Response Address and the master reads its device address. The address of the device is now known and it can be

interrogated in the usual way.

4. If more than one device’s ALERT output is low, the one with

the lowest device address will have priority, in accordance

with normal SMBus arbitration.

5. Once the ADM1020 has responded to the Alert Response

Address, it will reset its ALERT output, provided that the

error condition that caused the ALERT no longer exists. If

the SMBALERT line remains low, the master will send ARA

again, and so on until all devices whose ALERT outputs were

low have responded.

LOW POWER STANDBY MODES

The ADM1020 can be put into a low power standby mode by

setting Bit 6 of the Configuration Register. With Bit 6 low the

ADM1020 operates normally. When Bit 6 is high, the ADC is

inhibited, any conversion in progress is terminated without

writing the result to the corresponding value register.

The SMBus is still enabled. Power consumption in the standby

mode is reduced to less than 10 µA if there is no SMBus activity, or 100 µA if there are clock and data signals on the bus.

When Bit 6 is set , a one-shot conversion of both channels can

be initiated by writing XXh to the One-Shot Register (address

0Fh).

SENSOR FAULT DETECTION

The ADM1020 has a fault detector at the D+ input that detects

if the external sensor diode is open-circuit. This is a simple

voltage comparator that trips if the voltage at D+ exceeds

V

CC

– 1 V (typical). The output of this comparator is checked

when a conversion is initiated, and sets Bit 2 of the Status Register if a fault is detected.

If the remote sensor voltage falls below the normal measuring

range, for example due to the diode being short-circuited, the

ADC will output –128 (1000 0000). Since the normal operating

temperature range of the device only extends down to –55°C,

this output code should never be seen in normal operation, so it

can be interpreted as a fault condition. Since it will be outside

the power-on default low temperature limit (–55°C) and any

low limit that would normally be programmed, a short-circuit

sensor will cause an SMBus alert.

In this respect the ADM1020 differs from and improves upon,

competitive devices that output zero if the external sensor goes

short-circuit. These devices can misinterpret a genuine 0°C

measurement as a fault condition.

If the external diode channel is not being used and it is shorted

out, the resulting ALERT may be cleared by writing 80h

(–128°C) to the low limit register.

APPLICATIONS INFORMATION

FACTORS AFFECTING ACCURACY

Remote Sensing Diode

The ADM1020 is designed to work with substrate transistors

built into processors, or with discrete transistors. Substrate

transistors will generally be PNP types with the collector connected to the substrate. Discrete types can be either PNP or

NPN, connected as a diode (base shorted to collector). If an

NPN transistor is used then the collector and base are connected

to D+ and the emitter to D–. If a PNP transistor is used then

the collector and base are connected to D– and the emitter

to D+.

The user has no choice in the case of substrate transistors but if

a discrete transistor is used the best accuracy will be obtained by

choosing devices according to the following criteria:

1. Base-emitter voltage greater than 0.25 V at 6 µA, at the high-

est operating temperature.

2. Base-emitter voltage less than 0.95 V at 100 µA, at the lowest

operating temperature.

3. Base resistance less than 100 Ω.

4. Small variation in h

FE

(say 50 to 150) which indicates tight

control of V

BE

characteristics.

Transistors such as 2N3904, 2N3906 or equivalents in SOT-23

package are suitable devices to use.

REV. 0

ADM1020

–11–

LAYOUT CONSIDERATIONS

Digital boards can be electrically noisy environments, and the

ADM1020 is measuring very small voltages from the remote

sensor, so care must be taken to minimize noise induced at the

sensor inputs. The following precautions should be taken:

1. Place the ADM1020 as close as possible to the remote sensing diode. Provided that the worst noise sources such as clock

generators, data/address buses and CRTs are avoided, this

distance can be 4 to 8 inches.

2. Route the D+ and D– tracks close together, in parallel, with

grounded guard tracks on each side. Provide a ground plane

under the tracks if possible.

3. Use wide tracks to minimize inductance and reduce noise

pickup. 10 mil track minimum width and spacing is

recommended.

10mil

GND

D+

D–

GND

10mil

10mil

10mil

10mil

10mil

10mil

Figure 14. Arrangement of Signal Tracks

4. Try to minimize the number of copper/solder joints, which

can cause thermocouple effects. Where copper/solder joints

are used, make sure that they are in both the D+ and D–

path and at the same temperature.

Thermocouple effects should not be should not be a major

problem as 1°C corresponds to about 200 mV, and thermocouple voltages are about 3 mV/°C of temperature difference.

Unless there are two thermocouples with a big temperature

differential between them, thermocouple voltages should be

much less than 200 mV.

5. Place a 0.1 µF bypass capacitor close to the V

DD

pin and

2200 pF input filter capacitors across D+, D– close to the

ADM1020.

6. If the distance to the remote sensor is more than 8 inches, the

use of twisted pair cable is recommended. This will work up

to about 6 to 12 feet.

7. For really long distances (up to 100 feet) use shielded twisted

pair such as Belden #8451 microphone cable. Connect the

twisted pair to D+ and D– and the shield to GND close to

the ADM1020. Leave the remote end of the shield unconnected to avoid ground loops.

Because the measurement technique uses switched current

sources, excessive cable and/or filter capacitance can affect the

measurement. When using long cables, the filter capacitor may

be reduced or removed.

Cable resistance can also introduce errors. 1 Ω series resistance

introduces about 0.5°C error.

APPLICATION CIRCUITS

Figure 15 shows a typical application circuit for the ADM1020,

using a discrete sensor transistor connected via a shielded,

twisted pair cable. The pull-ups on SCLK, SDATA and ALERT

are required only if they are not already provided elsewhere in

the system.

SCLK

SDATA

ALERT

ADD

GND

D+

D–

0.1mF

10kV

+3.3V

SET TO REQUIRED

ADDRESS

C1*

SHIELD2N3904

*C1 IS OPTIONAL

ADM1020

V

DD

10kV

10kV

TO

PIIX4

CHIP

IN

OUT

I/O

Figure 15. Typical ADM1020 Application Circuit

REV. 0

ADM1020

–12–

C3445–4–4/99

PRINTED IN U.S.A.

8-Lead SOIC

(SO-8)

85

41

0.1 968 (5.00)

0.1 890 (4.80)

0.2440 (6.20)

0.2284 (5.80)

PIN 1

0.1574 (4.00)

0.1497 (3.80)

0.0500 (1.27)

BSC

0.0688 (1.75)

0.0532 (1.35)

SEATING

PLANE

0.0098 (0.25)

0.0040 (0.10)

0.0192 (0.49)

0.0138 (0.35)

0.0098 (0.25)

0.0075 (0.19)

0.0500 (1.27)

0.0160 (0.41)

88

08

0.0196 (0.50)

0.0099 (0.25)

3 458

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

BUILT-IN

SENSOR

PROCESSOR

HOST BUS

SECOND LEVEL

CACHE

HOST-TO-PCI

BRIDGE

MAIN MEMORY

(DRAM)

PCI BUS (3.3V OR 5V 30/33MHz)

PCI SLOTS

D– D+

ADM1020

ALERT

SCLK SDATA

CD ROM

HARD

DISK

BMI IDE

ULTRA DMA/33

8237 1AB

(PIIX4)

HARD

DISK

GPI [I,O] (30+)

AUDIO

SERIAL PORT

PARALLEL PORT

FLOPPY DISK

CONTROLLER

INFRARED

SMBUS

KEYBOARD

BIOS

ISA/EIO BUS

(3.3V, 5V TOLERANT)

USB PORT 1

USB PORT 2

Figure 16. Typical System Using ADM1020

The SCLK, and SDATA pins of the ADM1020 can be interfaced directly to the SMBus of an I/O controller such as the

Intel PCI ISA IDE Xcelerator (PIIX4) chip type 82371AB.

Figure 16 shows how the ADM1020 might be integrated into a

system using this type of I/O controller.

Loading...

Loading...