ANALOG DEVICES ADL5811 Service Manual

High IP3, 700 MHz to 2800 MHz, Double Balanced,

Passive Mixer, IF Amplifier, and Wideband LO Amplifier

FEATURES

RF frequency: 700 MHz to 2800 MHz continuous

LO frequency: 250 MHz to 2800 MHz, high-side or

low-side inject

IF range: 30 MHz to 450 MHz

Power conversion gain of 7.5 dB at 1900 MHz

SSB noise figure of 10.7 dB at 1900 MHz

Input IP3 of 27.5 dBm at 1900 MHz

Input P1dB of 12.7 dBm at 1900 MHz

Typical LO drive of 0 dBm

Single-ended, 50 Ω RF port

Single-ended or balanced LO input port

Single-supply operation: 3.6 V to 5.0 V

Serial port interface control on all functions

Exposed paddle 5 mm × 5 mm, 32-lead LFCSP package

APPLICATIONS

Multiband/multistandard cellular base station receivers

Wideband radio link diversity downconverters

Multimode cellular extenders and broadband receivers

ADL5811

FUNCTIONAL BLOCK DIAGRAM

VPIF

IFGMNCIFOP

30 29 28 27 26 2532 31

1

NC

2

RFCT

3

NC

4

RFIN

5

NC

6

NC

BIAS

7

NC

NC

GEN

8

11 12 13 14 15 169 10

VLO4

COMM

VLO3

COMM

Figure 1.

IFONNCIFGD

ADL5811

SERIAL

PORT

INTERFACE

VLO2

COMM

COMM

24

NC

23

NC

22

NC

21

LOIP

20

LOIN

19

LE

18

DATA

17

CLK

VLO1

COMM

09912-001

GENERAL DESCRIPTION

The ADL5811 uses revolutionary new broadband, square

wave limiting, local oscillator (LO) amplifiers to achieve an

unprecedented radio frequency (RF) bandwidth of 700 MHz

to 2800 MHz. Unlike conventional narrow-band sine wave LO

amplifier solutions, this permits the LO to be applied either

above or below the RF input over an extremely wide bandwidth.

Because energy storage elements are not used, the dc current

consumption also decreases with decreasing LO frequency.

The ADL5811 uses highly linear, doubly balanced, passive

mixer cores along with integrated RF and LO balancing circuits

to allow single-ended operation. The ADL5811 incorporates

programmable RF baluns, allowing optimal performance over a

700 MHz to 2800 MHz RF input frequency. The balanced passive

mixer arrangement provides outstanding LO-to-RF and LO-toIF leakages, excellent RF-to-IF isolation, and excellent

intermodulation performance over the full RF bandwidth.

The balanced mixer cores also provide extremely high input

linearity, allowing the device to be used in demanding

wideband applications where in-band blocking signals may

otherwise result in the degradation of dynamic range. Blocker

noise figure performance is comparable to narrow-band passive

mixer designs. High linearity IF buffer amplifiers follow the

passive mixer cores, yielding typical power conversion gains of

7.5 dB, and can be used with a wide range of output

impedances. For low voltage applications, the ADL5811 is

capable of operation at voltages down to 3.6 V with

substantially reduced current. Two logic bits are provided to

power down (<1.5 mA) the circuit when desired.

All features of the ADL5811 are controlled via a 3-wire serial

port interface, resulting in optimum performance and

minimum external components.

The ADL5811 is fabricated using a BiCMOS high performance

IC process. The device is available in a 32-lead, 5mm × 5mm,

LFCSP package and operates over a −40°C to +85°C

temperature range. An evaluation board is also available.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADL5811

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Characteristics ................................................................ 4

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics ............................................. 7

3.6 V Performance...................................................................... 16

Spurious Performance................................................................ 17

Circuit Description......................................................................... 20

RF Subsystem.............................................................................. 20

LO Subsystem ............................................................................. 21

Applications Information.............................................................. 22

Basic Connections...................................................................... 22

IF Port.......................................................................................... 22

Bias Resistor Selection ............................................................... 22

VGS Programming.................................................................... 22

Low-Pass Filter Programming.................................................. 23

RF Balun Programming ............................................................ 23

Register Structure........................................................................... 24

Evaluation Board............................................................................ 25

Outline Dimensions....................................................................... 28

Ordering Guide .......................................................................... 28

REVISION HISTORY

7/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

ADL5811

SPECIFICATIONS

VS = 5 V, TA = 25°C, fRF = 1900 MHz, fLO = 1697 MHz, RF power = −10 dBm, LO power = 0 dBm, R1 = 910 Ω, ZO = 50 Ω, optimum SPI settings,

unless otherwise noted.

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

RF INPUT INTERFACE

Return Loss Tunable to >20 dB broadband via serial port 15 dB

Input Impedance 50 Ω

RF Frequency Range 700 2800 MHz

OUTPUT INTERFACE

Output Impedance Differential impedance, f = 200 MHz 260||1.0 Ω||pF

IF Frequency Range 30 450 MHz

DC Bias Voltage1 Externally generated VS V

LO INTERFACE

LO Power −6 0 +10 dBm

Return Loss 13 dB

Input Impedance 50 Ω

LO Frequency Range Low-side or high-side LO 250 2800 MHz

DYNAMIC PERFORMANCE

Power Conversion Gain Including 4:1 IF port transformer and PCB loss 7.5 dB

Voltage Conversion Gain Z

SSB Noise Figure 10.7 dB

SSB Noise Figure Under Blocking

Input Third-Order Intercept

Input Second-Order Intercept

Input 1 dB Compression Point 12.7 dBm

LO-to-IF Output Leakage Unfiltered IF output −40 dBm

LO-to-RF Input Leakage −25 dBm

RF-to-IF Output Isolation 26 dB

IF/2 Spurious −10 dBm input power −73 dBc

IF/3 Spurious −10 dBm input power −75 dBc

POWER INTERFACE

Supply Voltage, VS 3.6 5 5.5 V

Quiescent Current Resistor programmable IF current 185 mA

Power-Down Current 1.4 mA

1

Supply voltage must be applied from external circuit through choke inductors.

= 50 Ω, differential Z

SOURCE

= 200 Ω differential 13.9 dB

LOAD

5 dBm blocker present ±10 MHz from wanted RF input,

LO source filtered

= 1900 MHz, f

f

RF1

= 1901 MHz, fLO = 1697 MHz,

RF2

each RF tone at −10 dBm

= 1900 MHz, f

f

RF1

= 2000 MHz, fLO = 1697 MHz,

RF2

each RF tone at −10 dBm

20.7 dB

27.5 dBm

62 dBm

Rev. 0 | Page 3 of 28

ADL5811

A

TIMING CHARACTERISTICS

Low logic level ≤ 0.4 V, and high logic level ≥ 1.4 V.

Table 2. Serial Interface Timing

Parameter Limit Unit Test Conditions/Comments

t1 20 ns minimum LE setup time

t2 10 ns minimum DATA-to-CLK setup time

t3 10 ns minimum DATA-to-CLK hold time

t4 25 ns minimum CLK high duration

t5 25 ns minimum CLK low duration

t6 10 ns minimum CLK-to-LE setup time

t7 20 ns minimum LE pulse width

Timing Diagram

CLK

t

4

t

5

t

2

D

DB23 (MSB) DB22

TA

LE

t

3

DB2 DB1

(CONTROL BIT C2)(CONTROL BIT C3)

DB0 ( LSB)

(CONTROL BIT C1)

t

t

t

7

6

1

09912-002

Figure 2. Timing Diagram

Rev. 0 | Page 4 of 28

ADL5811

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage, V

CLK, DATA, LE 5.5 V

IF Output Bias 6.0 V

RF Input Power 20 dBm

LO Input Power 13 dBm

Internal Power Dissipation 1.1 W

θJA (Exposed Paddle Soldered Down) 25°C/W

Maximum Junction Temperature 150°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

5.5 V

POS

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 28

ADL5811

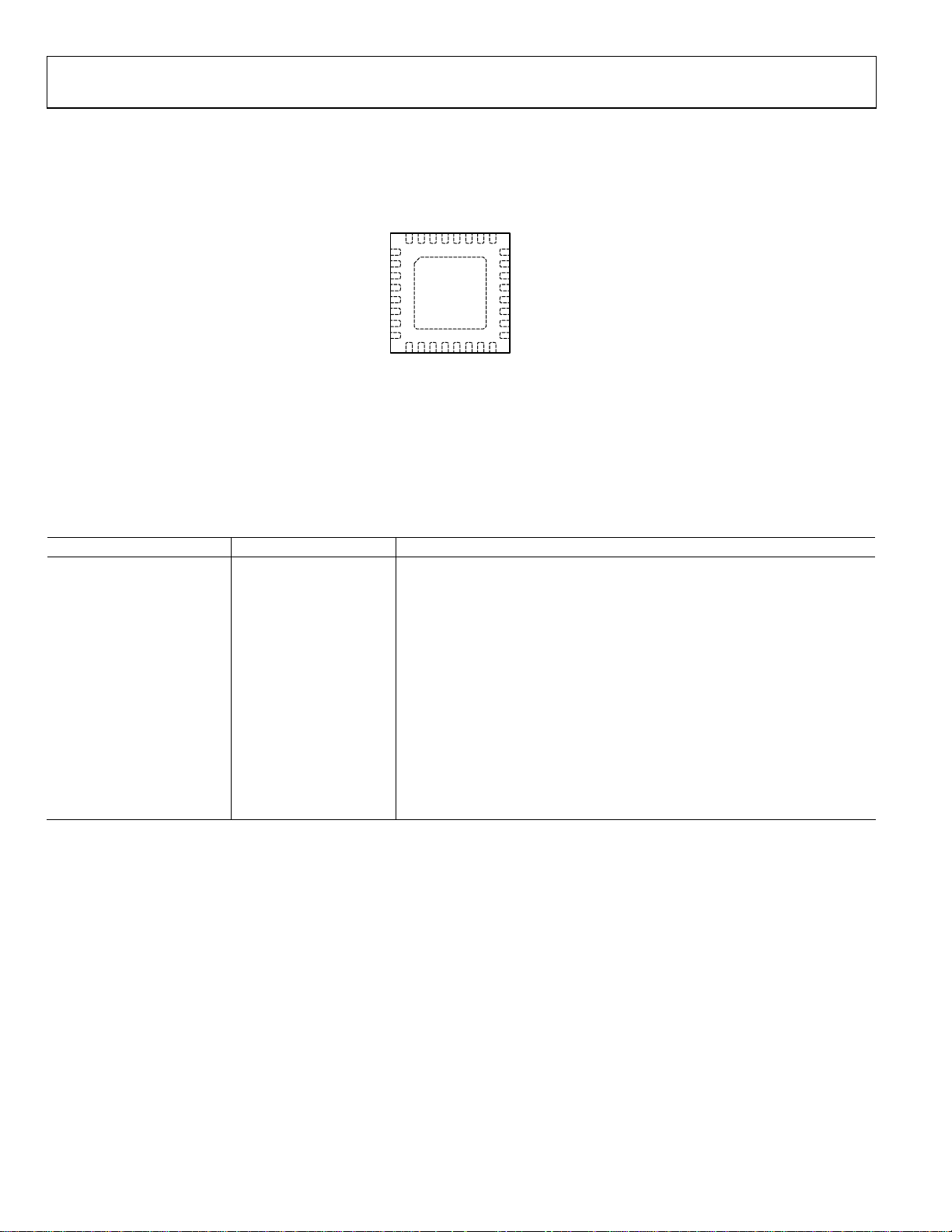

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VPIF

IFGMNCIFOP

IFONNCIFGD

32313029282726

1

NC

2

RFCT

NC

3

4

5

6

7

8

ADL5811

TOP VIEW

(Not to Scale)

9

10111213141516

VLO4

VLO3

COMM

COMM

RFIN

NC

NC

NC

NC

NOTES

1. NC = NO CO NNECT. CAN BE GROUNDED.

2. EXPOSED PAD MUST BE CONNECTED

TO GROUND.

Figure 3. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1, 3, 5 to 8, 22 to 24, 27, 30 NC No Connect. Can be grounded.

2 RFCT RF Balun Center Tap (AC Ground).

4 RFIN RF Input. Should be ac-coupled.

9, 11, 13, 15 VLO4, VLO3, VLO2, VLO1 Positive Supply Voltages for LO Amplifier.

10, 12, 14, 16, 25 COMM Ground.

17, 18, 19 CLK, DATA, LE Serial Port Interface Control.

20 LOIN Ground Return for LO Input.

21 LOIP LO Input. Should be ac-coupled.

26 IFGD Supply Return for IF Amplifier. Must be grounded.

28, 29 IFOP, IFON

IF Differential Open-Collector Outputs. Should be pulled up to V

external inductors.

31 IFGM IF Amplifier Bias Control.

32 VPIF Supply Voltage for IF Amplifier.

EPAD Exposed pad must be connected to ground.

COMM

25

NC

24

23

NC

NC

22

LOIP

21

20

LOIN

19

LE

18

DATA

CLK

17

VLO2

VLO1

COMM

COMM

09912-003

using

CC

Rev. 0 | Page 6 of 28

ADL5811

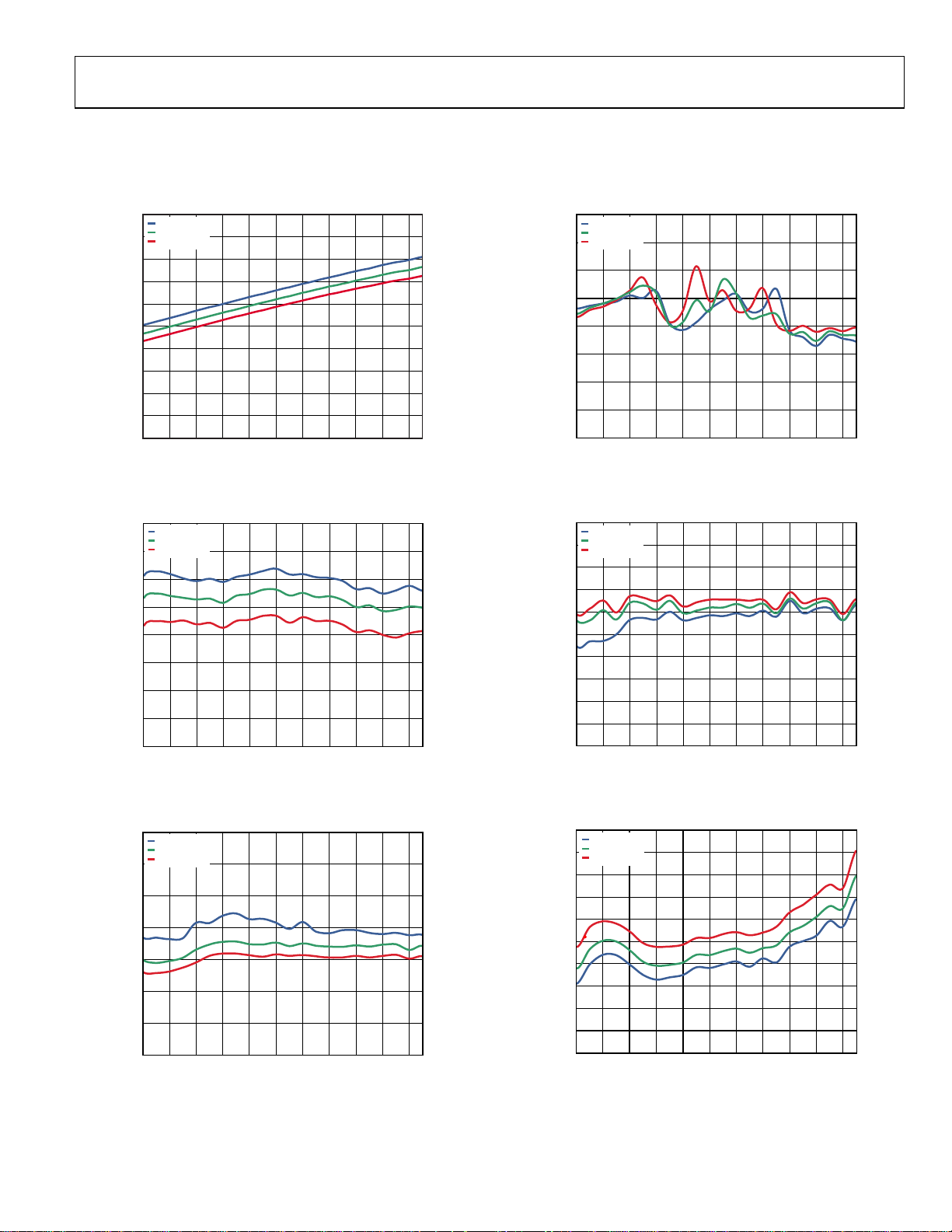

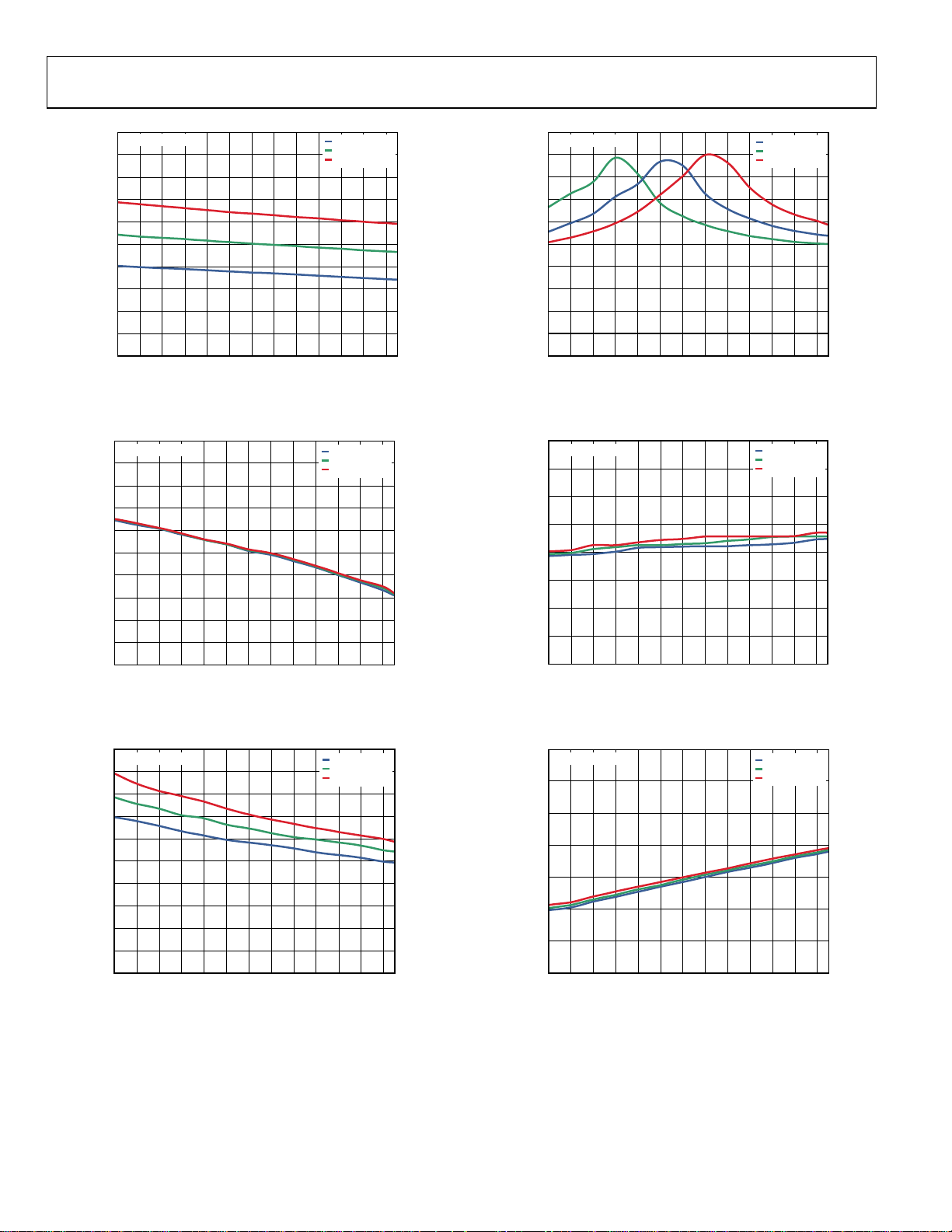

TYPICAL PERFORMANCE CHARACTERISTICS

VS = 5 V, TA = 25°C, fRF = 1900 MHz, fLO = 1697 MHz, RF power = −10 dBm, LO power = 0 dBm, R1 = 910 Ω, ZO = 50 Ω, optimum SPI settings,

unless otherwise noted.

220

TA = –40°C

= +25°C

T

A

210

200

190

180

170

160

150

SUPPLY CURRENT (mA)

140

130

120

= +85°C

T

A

700 900 1100 1300 1500 1700 1900 2100 2300 2500 2700

RF FREQUE NCY (MHz)

Figure 4. Supply Current vs. RF Frequency

10

TA = –40°C

T

= +25°C

A

T

= +85°C

9

A

8

7

6

5

CONVERSIO N GAIN (dB)

4

3

2

700 900 1100 1300 1500 1700 1900 2100 2300 2500 2700

RF FREQUE NCY (MHz)

Figure 5. Power Conversion Gain vs. RF Frequency

45

TA = –40°C

T

= +25°C

A

T

= +85°C

A

40

35

30

25

INPUT IP3 (dBm)

20

15

10

700 900 1100 1300 1500 1700 1900 2100 2300 2500 2700

RF FREQUENCY (MHz)

Figure 6. Input IP3 vs. RF Frequency

09912-004

09912-005

09912-006

90

TA = –40°C

T

= +25°C

A

T

= +85°C

80

A

70

60

50

40

INPUT IP2 (dBm)

30

20

10

700 900 1100 1300 1500 1700 1900 2100 2300 2500 2700

RF FREQUE NCY (MHz)

Figure 7. Input IP2 vs. RF Frequency

20

TA = –40°C

T

= +25°C

A

18

T

= +85°C

A

16

14

12

10

8

INPUT P1dB (dBm)

6

4

2

0

700 900 1100 1300 1500 1700 1900 2100 2300 2500 2700

RF FREQUENCY (MHz)

Figure 8. Input P1dB vs. RF Frequency

16

TA = –40°C

= +25°C

T

A

15

= +85°C

T

A

14

13

12

11

10

NOISE FIGURE (dB)

9

8

7

6

700 900 1100 1300 1500 1700 1900 2100 2300 2500 2700

RF FREQ UENCY (MHz)

Figure 9. SSB Noise Figure vs. RF Frequency

09912-007

09912-008

09912-009

Rev. 0 | Page 7 of 28

ADL5811

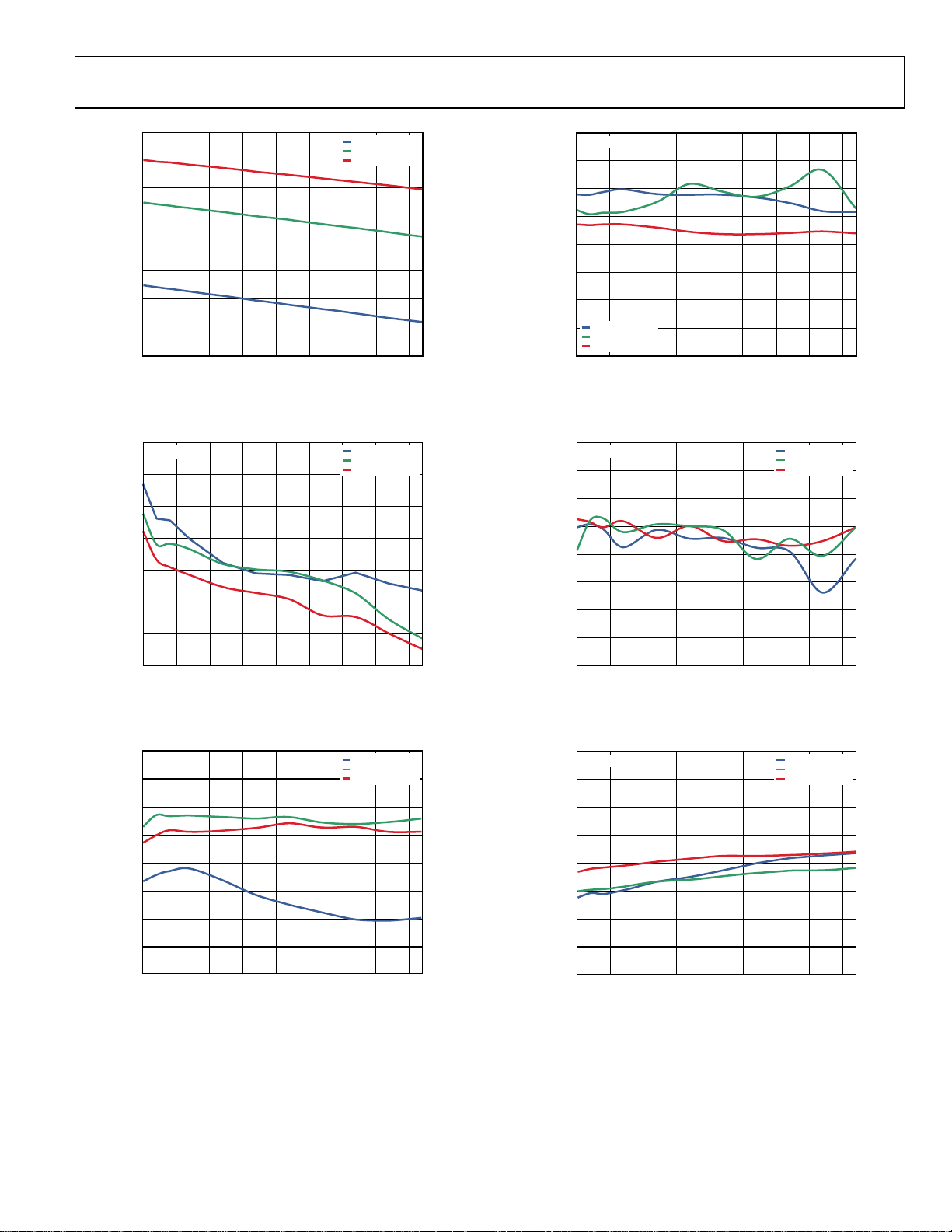

235

RF = 1900MHz

225

215

205

195

185

175

165

SUPPLY CURRENT (mA)

155

145

135

–40 –30 –20 –10 01020304050607080

TEMPERAT URE (°C)

V

POS

V

POS

V

POS

Figure 10. Supply Current vs. Temperature

10.0

RF = 1900MHz

9.5

9.0

8.5

8.0

7.5

7.0

6.5

CONVERSION GAIN (dB)

6.0

5.5

5.0

–40 –30 –20 –10 0 1020304050607080

TEMPERATURE (°C)

V

POS

V

POS

V

POS

Figure 11. Power Conversion Gain vs. Temperature

35

RF = 1900MHz

33

31

29

27

25

23

INPUT IP3 (dBm)

21

19

17

15

–40 –30 –20 –10 0 1020304050607080

TEMPERATURE (°C)

V

POS

V

POS

V

POS

Figure 12. Input IP3 vs. Temperature

= 4.75V

= 5.00V

= 5.25V

= 4.75V

= 5.00V

= 5.25V

= 4.75V

= 5.00V

= 5.25V

09912-010

09912-011

09912-012

80

RF = 1900MHz

75

70

65

60

55

50

INPUT IP2 (dBm)

45

40

35

30

–40 –30 –20 –10 0 1020304050607080

TEMPERATURE (°C)

V

POS

V

POS

V

POS

Figure 13. Input IP2 vs. Temperature

20

RF = 1900MHz

18

16

14

12

10

INPUT P1dB (dBm)

8

6

4

–40 –30 –20 –10 0 1020304050607080

TEMPERATURE (°C)

V

POS

V

POS

V

POS

Figure 14. Input P1dB vs. Temperature

15

RF = 1900MHz

14

13

12

11

10

SSB NOISE FIGURE ( dB)

9

8

–40 –30 –20 –10 0 1020304050607080

TEMPERATURE (°C)

V

POS

V

POS

V

POS

Figure 15. SSB Noise Figure vs. Temperature

= 4.75V

= 5.00V

= 5.25V

= 4.75V

= 5.00V

= 5.25V

= 4.75V

= 5.00V

= 5.25V

09912-013

09912-014

09912-015

Rev. 0 | Page 8 of 28

ADL5811

200

195

TA = 25°C

RF = 900MHz

RF = 1900MHz

RF = 2500MHz

80

70

TA = 25°C

190

185

180

175

SUPPLY CURRENT (mA)

170

165

160

30 80 130 180 230 280 330 380 430

IF FREQUENCY (MHz)

Figure 16. Supply Current vs. IF Frequency

11

TA = 25°C

10

9

8

7

6

CONVERSION GAIN (dB)

5

RF = 900MHz

RF = 1900MHz

RF = 2500MHz

60

50

40

30

INPUT IP2 (dBm)

20

RF = 900MHz

10

RF = 1900MHz

RF = 2500MHz

0

30 80 130 180 230 280 330 380 430

09912-016

IF FREQUENCY (MHz)

09912-019

Figure 19. Input IP2 vs. IF Frequency

18

TA = 25°C

16

14

12

10

8

INPUT P1dB (dBm)

6

4

RF = 900MHz

RF = 1900MHz

RF = 2500MHz

4

30 80 130 180 230 280 330 380 430

IF FREQUENCY (MHz)

Figure 17. Power Conversion Gain vs. IF Frequency

30

TA = 25°C

39

28

27

26

25

INPUT IP3 (dBm)

24

23

22

30 80 130 180 230 280 330 380 430

IF FREQUENCY (MHz)

RF = 900MHz

RF = 1900MHz

RF = 2500MHz

Figure 18. Input IP3 vs. IF Frequency

2

30 80 130 180 230 280 330 380 430

09912-017

IF FREQ UENCY (MHz)

09912-020

Figure 20. Input P1dB vs. IF Frequency

20

TA = 25°C

18

16

14

12

10

SSB NOISE FIGURE (dB)

8

6

4

30 80 130 180 230 280 330 380 430

09912-018

IF FREQ UENCY (MHz)

RF = 900MHz

RF = 1900MHz

RF = 2500MHz

09912-021

Figure 21. SSB Noise Figure vs. IF Frequency

Rev. 0 | Page 9 of 28

Loading...

Loading...