400 MHz to 4000 MHz

FEATURES

Operation from 400 MHz to 4000 MHz

Noise figure of 0.8 dB at 900 MHz

Requires few external components

Integrated active bias control circuit

Integrated dc blocking capacitors

Adjustable bias for low power applications

Single-supply operation from 3 V to 5 V

Gain of 20.8 dB at 900 MHz

OIP3 of 37.0 dBm at 900 MHz

P1dB of 21.8 dBm at 900 MHz

Small footprint LFCSP

Pin-compatible version with 21.5 dB gain available

GENERAL DESCRIPTION

The ADL5521 is a high performance GaAs pHEMT low noise

amplifier. It provides high gain and low noise figure for singledownconversion IF sampling receiver architectures as well as

direct-downconversion receivers.

The ADL5521 provides a high level of integration by incorporating

the active bias and dc blocking capacitors, making it very easy

to use while not sacrificing design flexibility.

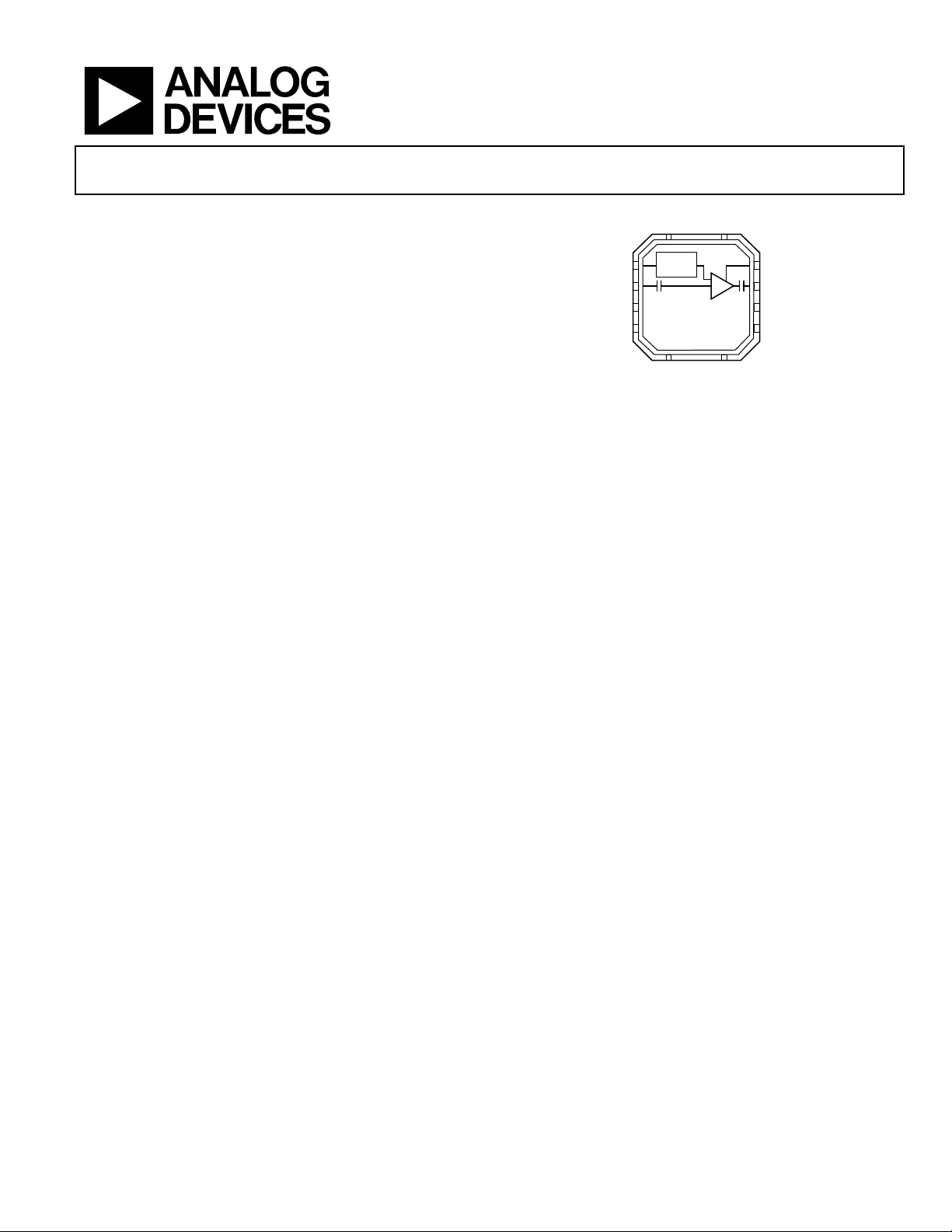

Low Noise Amplifier

ADL5521

FUNCTIONAL BLOCK DIAGRAM

ACTIVE

1VBIAS

BIAS

2RFIN

3NC

ADL5521

4NC

NC = NO CONNECT

Figure 1.

The ADL5521 is easy to tune, requiring only a few external

components. The device can support operation from 3 V to 5 V,

and the current draw can be adjusted with the external bias

resistor for applications requiring low power consumption.

The ADL5521 comes in a compact, thermally enhanced, 3 mm ×

3 mm LFCSP and operates over the temperature range of

−40°C to +85°C.

A fully populated evaluation board is also available.

8 VPOS

7RFOUT

6NC

5NC

06828-001

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008–2009 Analog Devices, Inc. All rights reserved.

ADL5521

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

AC Specifications .......................................................................... 3

DC Specifications ......................................................................... 4

De-Embedded S-Parameters, VPOS = 3 V to 5 V, RFIN =

Port 1, VPOS = Port 2, RFOUT = Port 3 .................................. 4

Absolute Maximum Ratings ............................................................ 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

Typical Performance Characteristics ............................................. 7

900 MHz, VPOS = 5 V ................................................................. 7

1950 MHz, VPOS = 5 V .............................................................. 8

2600 MHz, VPOS = 5 V .............................................................. 9

3500 MHz, VPOS = 5 V ............................................................ 10

900 MHz, VPOS = 3 V .............................................................. 11

1950 MHz, VPOS = 3 V ............................................................ 12

2600 MHz, VPOS = 3 V ............................................................ 13

3500 MHz, VPOS = 3 V ............................................................ 14

DC Characteristics ..................................................................... 15

Basic Connections .......................................................................... 16

Evaluation Board ............................................................................ 17

Soldering Information and Recommended PCB

Land Pattern ................................................................................ 17

Tuning the ADL5521 for Optimal Noise Figure ........................ 18

Tuning S22 ................................................................................... 18

Tuning the LNA Input for Optimal Gain ................................ 19

Tuning the LNA Input for Optimal Noise Figure .................. 19

S11 of the LNA with S22 Matched ........................................... 20

Outline Dimensions ....................................................................... 21

Ordering Guide .......................................................................... 21

REVISION HISTORY

9/09—Rev. 0 to Rev. A

Updated Maximum Junction Temperature Unit (Table 4) ......... 5

10/08—Revision 0: Initial Version

Rev. A | Page 2 of 24

ADL5521

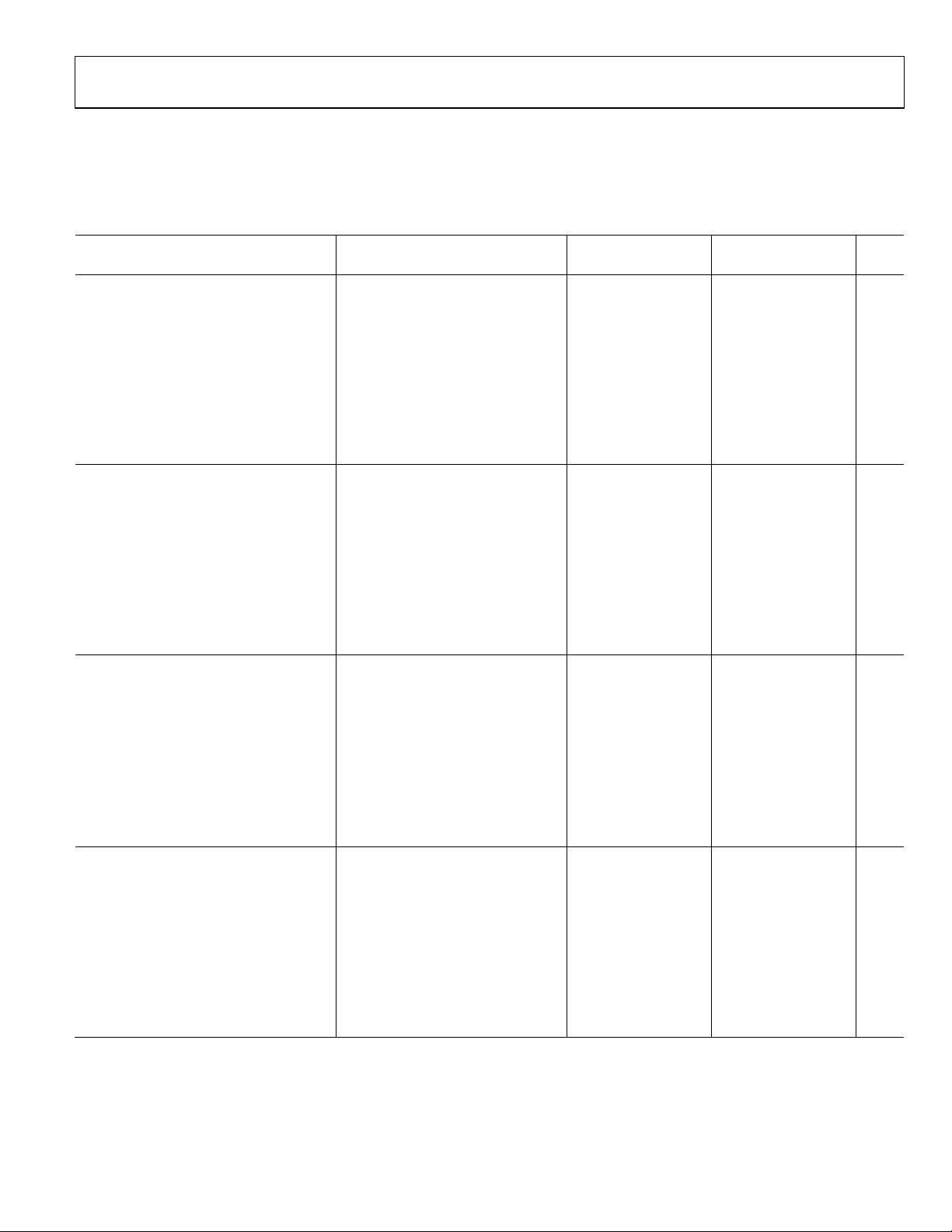

SPECIFICATIONS

AC SPECIFICATIONS

TA = 25°C, R1 = 1.3 kΩ; parameters include matching circuit, matched for optimal noise, unless otherwise noted.

Table 1.

3 V 5 V

Parameter Conditions Min Typ Max Min Typ Max Unit

FREQUENCY = 900 MHz

Gain (S21) 20.3 20.8 dB

vs. Frequency ±50 MHz ±0.28 ±0.33 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.53 ±0.46 dB

Noise Figure1 0.8 0.9 dB

Output Third-Order Intercept (OIP3) Δf = 1 MHz, P

Output 1 dB Compression Point (P1dB) 17.8 21.8 dBm

Input Return Loss (S11) −8.0 −9.0 dB

Output Return Loss (S22) −14.7 −15.3 dB

Isolation (S12) −23.8 −25.0 dB

FREQUENCY = 1950 MHz

Gain (S21) 15.4 14.7 15.8 17.0 dB

vs. Frequency ±30 MHz ±0.04 ±0.06 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.43 ±0.40 dB

Noise Figure1 1.0 1.0 dB

Output Third-Order Intercept (OIP3) Δf = MHz, P

Output 1 dB Compression Point (P1dB) 17.6 21.8 dBm

Input Return Loss (S11) −10.5 −12.5 dB

Output Return Loss (S22) −25.5 −25.5 dB

Isolation (S12) −20.2 −21.0 dB

FREQUENCY = 2600 MHz

Gain (S21) 12.4 12.8 dB

vs. Frequency ±100 MHz ±0.35 ±0.35 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.46 ±0.45 dB

Noise Figure1 0.9 1.0 dB

Output Third-Order Intercept (OIP3) Δf = 1 MHz, P

Output 1 dB Compression Point (P1dB) 17.1 21.5 dBm

Input Return Loss (S11) −7.1 −7.7 dB

Output Return Loss (S22) −14.1 −13.5 dB

Isolation (S12) −20.0 −20.5 dB

FREQUENCY = 3500 MHz

Gain (S21) 10.0 10.3 dB

vs. Frequency ±100 MHz ±0.56 ±0.59 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.66 ±0.63 dB

Noise Figure1 1.0 1.1 dB

Output Third-Order Intercept (OIP3) Δf = 1 MHz, P

Output 1 dB Compression Point (P1dB) 17.0 20.9 dBm

Input Return Loss (S11) −18.0 −18.3 dB

Output Return Loss (S22) −10.5 −11.0 dB

Isolation (S12) −17.8 −18.1 dB

1

Noise figure de-embedded to first matching component on input side.

= 0 dBm per tone 28.0 37.0 dBm

OUT

= 0 dBm per tone 29.0 35.0 dBm

OUT

= 0 dBm per tone 30.5 35.5 dBm

OUT

= 0 dBm per tone 31.0 36.0 dBm

OUT

Rev. A | Page 3 of 24

ADL5521

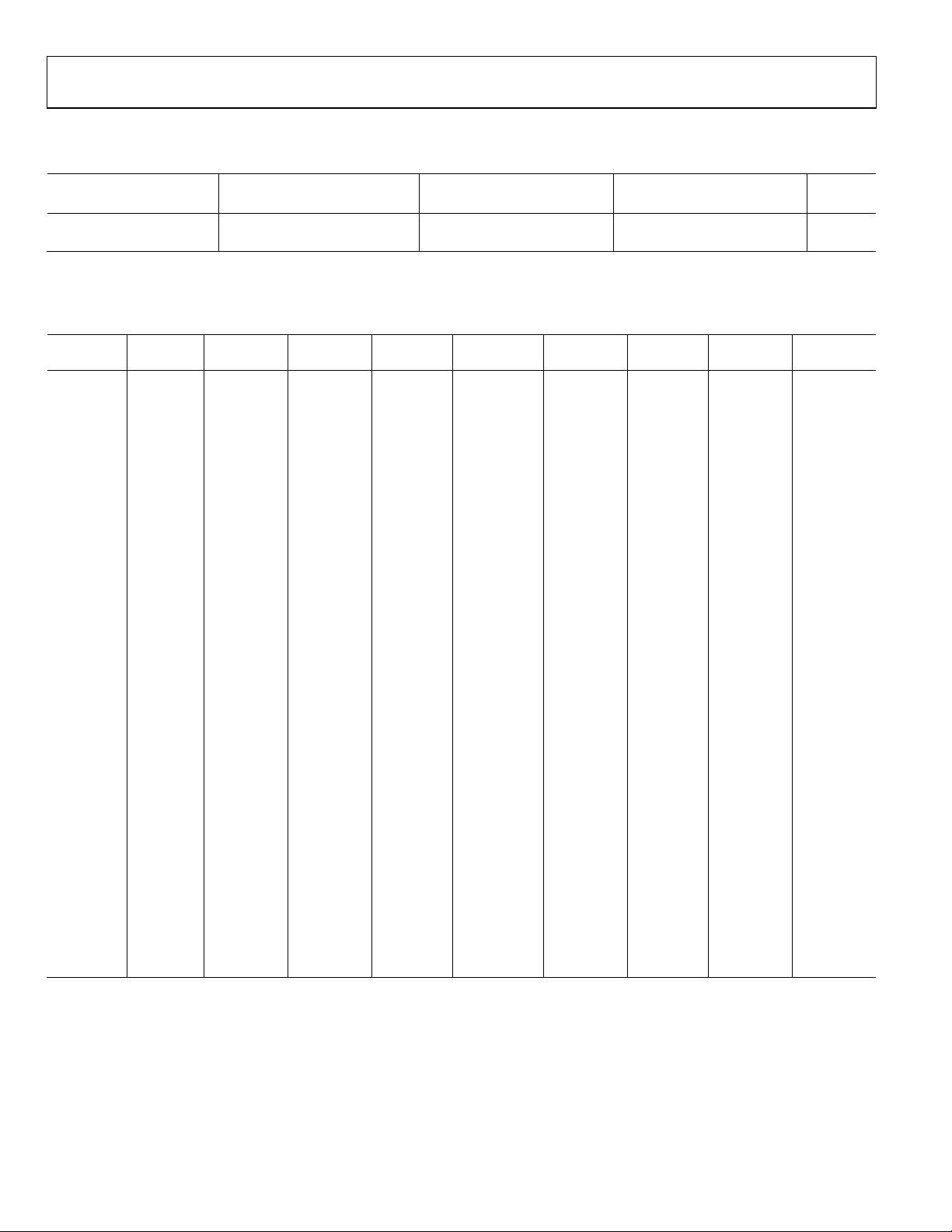

DC SPECIFICATIONS

Table 2.

3 V 5 V

Parameter Conditions

Supply Current 30 60 mA

vs. Temperature −40°C ≤ TA ≤ +85°C ±4 ±7 mA

DE-EMBEDDED S-PARAMETERS, VPOS = 3 V TO 5 V, RFIN = PORT 1, VPOS = PORT 2, RFOUT = PORT 3

Table 3.

Frequency

(GHz)

0.125 −3.8/−11.3 −34.5/+8.9 −37.2/+51.8 +21.5/+161 −11.4/−133 −4.4/+32 +18.8/−155 +4.3/+32 −4.8/−80.9

0.25 −3.8/−24.5 −34.4/+26.6 −35.0/+50.5 +20.2/+158 −10.4/−153 −3.5/+19.8 +19.5/−178 −3.4/+20.1 −8.0/−111

0.375 −4.0/−37.1 −33.3/+39.6 −33.3/+54.2 +19.5/+154 −9.5/−158 −3.5/+16.5 +19.4/+170 −3.4/+17.0 −9.2/−126

0.5 −4.4/−48.9 −32.2/+48.9 −31.9/+57.7 +18.7/+150 −8.7/−158 −3.6/+16.2 +19.0/+161 −3.5/+16.7 −9.7/−133

0.625 −4.7/−60.0 −31.2/+55.8 −30.7/+60.2 +18.0/+146 −7.9/−155 −3.8/+17.2 +18.5/+153 −3.7/+17.7 −9.7/−137

0.75 −5.0/−70.2 −30.4/+61.3 −29.7/+61.9 +17.2/+143 −7.2/−150 −4.1/+19.1 +18.0/+147 −3.9/+19.5 −9.5/−139

0.875 −5.3/−79.1 −29.7/+66.6 −28.9/+63.5 +16.4/+141 −6.8/−144 −4.3/+21.6 +17.3/+141 −4.2/+22.1 −9.3/−139

1.0 −5.5/−86.9 −29.0/+71.2 −28.2/+64.7 +15.7/+140 −6.4/−137 −4.6/+24.8 +16.7/+137 −4.4/+25.1 −9.0/−138

1.125 −5.6/−93.3 −28.4/+75.6 −27.6/+65.6 +14.9/+138 −6.2/−129 −4.8/+28.0 +16.0/+132 −4.6/+28.3 −8.6/−137

1.25 −5.7/−98.0 −27.9/+79.8 −27.2/+66.9 +14.3/+138 −6.1/−121 −4.9/+31.9 +15.3/+129 −4.7/+32.1 −8.2/−135

1.375 −5.7/−102 −27.3/+84.0 −26.8/+68.0 +13.7/+138 −6.3/−113 −4.9/+35.7 +14.5/+126 −4.8/+35.8 −7.9/−133

1.5 −5.8/−104 −26.8/+87.8 −26.5/+69.4 +13.1/+138 −6.6/−105 −5.0/+39.4 +13.7/+123 −4.8/+39.4 −7.5/−131

1.625 −5.9/−104 −26.2/+91.6 −26.3/+71.5 +12.6/+138 −7.2/−97.2 −5.0/+43.5 +12.9/+122 −4.8/+43.5 −7.2/−129

1.75 −5.8/−104 −25.7/+94.8 −26.2/+73.9 +12.2/+138 −8.0/−91.0 −4.9/+47.0 +12.1/+121 −4.7/+47.0 −6.9/−127

1.875 −5.8/−103 −25.1/+98.2 −26.0/+76.8 +11.8/+139 −9.2/−86.4 −4.7/+50.5 +11.3/+122 −4.5/+50.5 −6.7/−126

2.0 −5.6/−101 −24.6/+101 −26.0/+80.1 +11.5/+139 −10.7/−85.8 −4.5/+53.6 +10.5/+123 −4.4/+53.6 −6.6/−125

2.125 −5.5/−99.3 −24.0/+104 −25.9/+85.1 +11.2/+139 −12.4/−92.3 −4.4/+56.6 +9.8/+125 −4.2/+56.6 −6.5/−125

2.25 −5.3/−97.2 −23.6/+106 −25.7/+91.0 +10.8/+139 −13.4/−110 −4.3/+59.1 +9.3/+129 −4.1/+59.1 −6.6/−125

2.375 −5.1/−95.9 −23.2/+109 −25.3/+96.7 +10.4/+139 −12.0/−129 −4.3/+61.6 +8.9/+132 −4.1/+61.7 −6.9/−127

2.5 −4.9/−94.8 −23.0/+111 −24.6/+103 +9.9/+140 −9.4/−136 −4.4/+64.3 +8.9/+136 −4.2/+64.4 −7.4/−128

2.625 −4.8/−94.4 −22.9/+114 −23.8/+108 +9.2/+141 −6.9/−135 −4.6/+67.3 +9.0/+139 −4.4/+67.4 −8.2/−130

2.75 −4.8/−94.8 −23.0/+118 −22.8/+111 +8.4/+143 −4.9/−127 −5.1/+70.9 +9.3/+140 −4.9/+71.0 −9.2/−132

2.875 −4.9/−95.4 −23.3/+122 −21.8/+114 +7.5/+146 −3.4/−117 −5.7/+75.0 +9.6/+141 −5.5/+75.2 −10.5/−133

3.0 −5.2/−96.9 −23.8/+127 −20.9/+114 +6.4/+149 −2.2/−104 −6.4/+79.7 +9.9/+140 −6.2/+79.8 −12.2/−133

3.125 −5.6/−98.9 −24.5/+133 −20.0/+114 +5.1/+153 −1.4/−89.0 −7.5/+85.2 +10.2/+138 −7.2/+85.0 −14.2/−132

3.25 −6.1/−102 −25.4/+139 −19.2/+114 +3.5/+157 −0.89/−73.4 −8.8/+90.4 +10.3/+136 −8.5/+90.4 −16.2/−126

3.375 −6.6/−105 −26.4/+144 −18.6/+112 +1.9/+162 −0.59/−57.8 −10.2/+95.5 +10.4/+133 −9.9/+95.4 −177/−116

3.5 −7.2/−110 −27.5/+149 −18.0/+111 +0.27/+165 −0.41/−42.6 −11.6/+100 +10.3/+130 −11.4/+99.7 −18.1/−104

3.625 −7.7/−115 −28.6/+154 −17.6/+109 −1.3/+169 −0.23/−27.6 −13.1/+104 +10.2/+127 −12.7/+104 −17.1/−93.5

3.75 −8.1/−123 −29.4/+158 −17.3/+106 −2.7/+172 +0.035/−12.8 −14.3/+109 +10.0/+124 −14.0/+108 −15.7/−88.0

3.875 −8.3/−132 −30.1/+163 −17.0/+103 −3.9/+175 +0.45/+2.3 −15.4/+114 +9.7/+119 −15.1/+113 −14.0/−87.7

4.0 −8.2/−140 −30.6/+168 −16.9/+99.8 −4.8/−180 +1.0/+18.9 −16.3/+120 +9.4/+115 −16.0/+120 −12.5/−89.2

S11

(dB/Ang)

S12

(dB/Ang)

S13

(dB/Ang)

S21

(dB/Ang)

Min Typ Max Min Typ Max Unit

S22

(dB/Ang)

S23

(dB/Ang)

S31

(dB/Ang)

S32

(dB/Ang)

S33

(dB/Ang)

Rev. A | Page 4 of 24

ADL5521

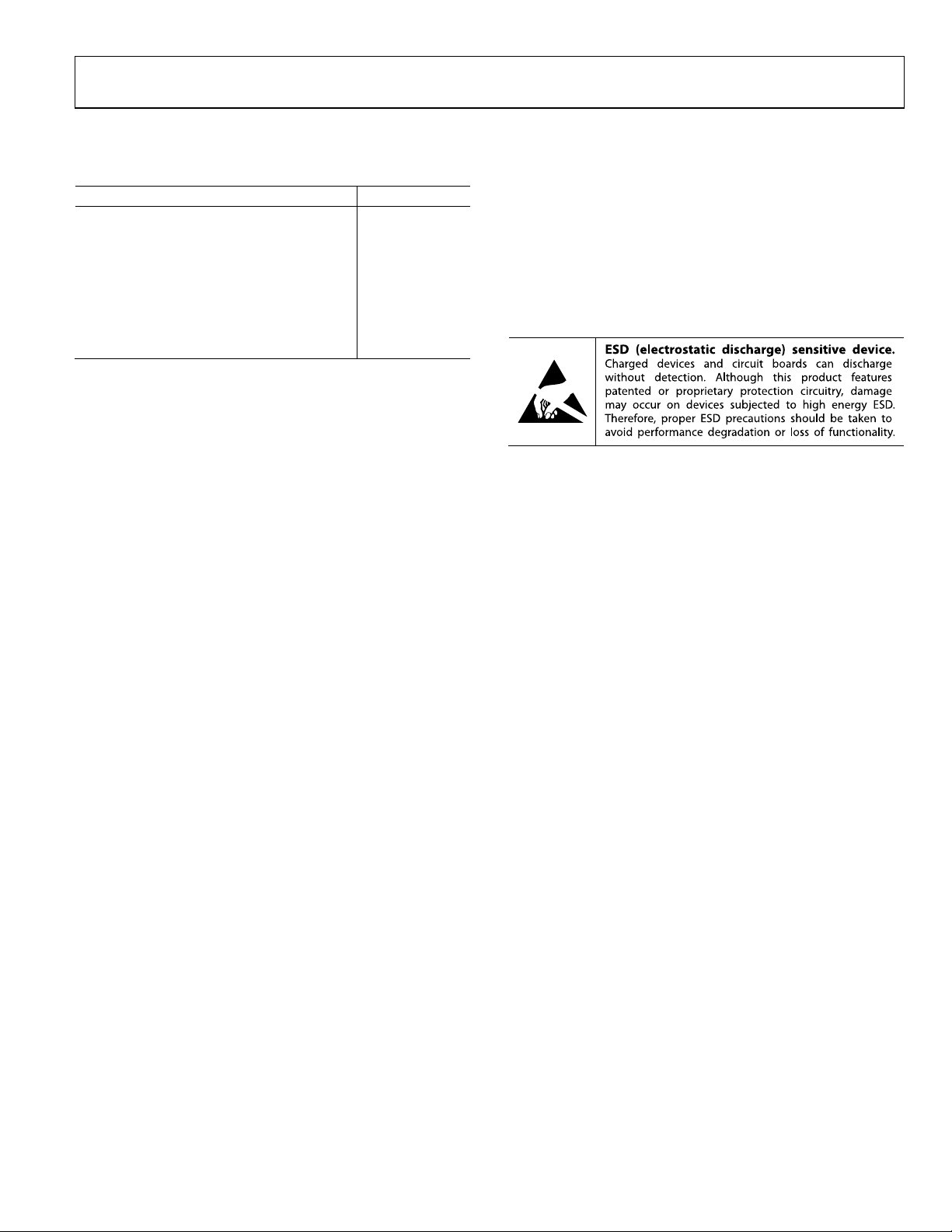

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage, VPOS 5.5 V

RF Input Level 7 dBm

RF Input Level (with 8 Ω Series Resistor on VPOS) 20 dBm

Internal Power Dissipation 500 mW

θJA (Junction to Air) 50°C/W

Maximum Junction Temperature 150°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. A | Page 5 of 24

ADL5521

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1VBIAS

ADL5521

2RFIN

3NC

4NC

NOTES

1. NC = NO CONNEC T.

2. CONNECT THE EXPOSED PAD TO A LOW

IMPEDANCE GROUND PL ANE .

TOP VIEW

(Not to S cale)

EXPOSED PAD

8 VPOS

7RFOUT

6NC

5NC

06828-002

Figure 2. Pin Configuration

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

1 VBIAS Internal DC Bias. This pin should be connected to VPOS through the R1 resistor.

2 RFIN RF Input. This is the input to the LNA.

3, 4, 5, 6 NC No Connection. No internal connection.

7 RFOUT RF Output.

8 VPOS

Supply Voltage. DC bias needs to be bypassed to ground using a low inductance capacitor. This pin is

also used for output matching. See the Basic Connections section.

9 (EPAD) Exposed Pad (EPAD) GND. Connect the exposed pad to a low impedance ground plane.

Rev. A | Page 6 of 24

ADL5521

TYPICAL PERFORMANCE CHARACTERISTICS

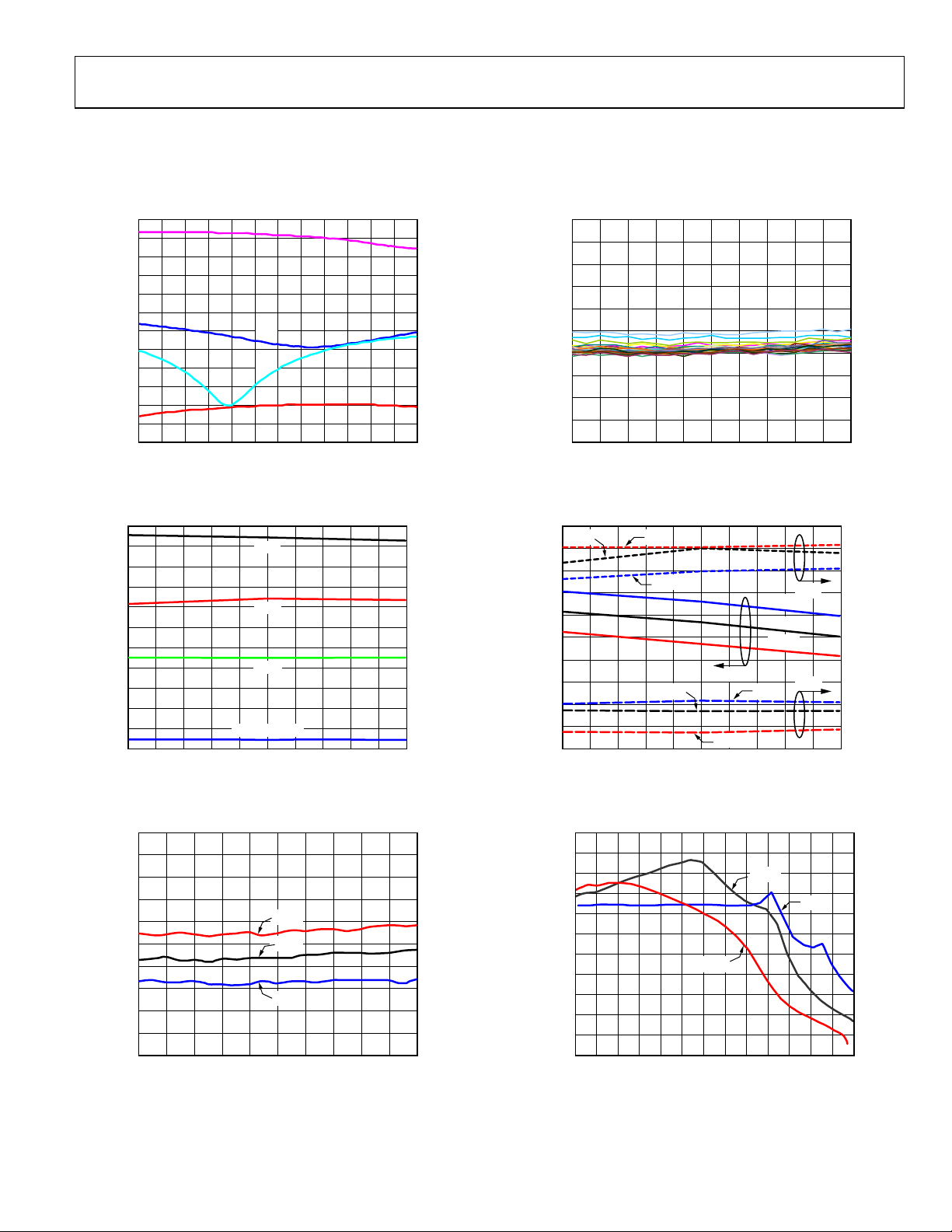

900 MHz, VPOS = 5 V

Matched for optimal noise figure, external matching circuit included.

25

20

15

10

5

0

–5

–10

–15

S-PARAMETERS ( dB)

–20

–25

–30

–35

600 650 700 750 800 850 900 950 1000 1050 1100 1150 1200

S21

S11

S22

S12

FREQUENCY (MHz)

Figure 3. Typical S-Parameters, Log Magnitude

22

20

18

16

14

12

10

8

6

NOISE FI GURE AND GAIN (d B)

4

2

0

850 860 870 880 890 900 910 920 930 940 950

GAIN

OIP3

P1dB

NOISE FI GURE

FREQUENCY (MHz)

Figure 4. Noise Figure, Gain, OIP3, and P1dB vs. Frequency

2.0

1.8

1.6

1.4

+85°C

+25°C

–40°C

FREQUENCY (MHz)

NOISE FIGURE (dB)

1.2

1.0

0.8

0.6

0.4

0.2

0

800 1000980960940920900880860840820

Figure 5. Noise Figure vs. Temperature

06828-003

55

50

45

40

35

30

25

20

OIP3 AND P1dB ( dBm)

15

10

5

0

06828-004

06828-005

2.0

1.8

1.6

1.4

1.2

1.0

0.8

NOISE FIGURE (dB)

0.6

0.4

0.2

0

800 820 840 860 880 900 920 940 960 1000980

FREQUENCY (MHz)

Figure 6. Noise Figure vs. Frequency at 25°C, Multiple Devices

23.0

+25°C

22.5

22.0

21.5

21.0

20.5

GAIN (dB)

20.0

19.5

19.0

18.5

18.0

850 860 870 880 890 900 910 920 930 940 950

+85°C

–40°C

+25°C

FREQUENCY (MHz)

–40°C

+25°C

+85°C

GAIN

–40°C

+85°C

Figure 7. Gain, OIP3, and P1dB vs. Temperature

42

40

38

36

34

32

30

OIP3 (dBm)

28

26

24

22

20

–4 –2 2220181614121086420

P

OUT

Figure 8. OIP3 vs. Output Power (P

+85°C

PER TONE (dBm)

+25°C

) and Temperature

OUT

OIP3

P1dB

–40°C

06828-006

39

37

35

33

31

29

27

25

OIP3 AND P1dB ( dBm)

23

21

19

06828-008

06828-007

Rev. A | Page 7 of 24

ADL5521

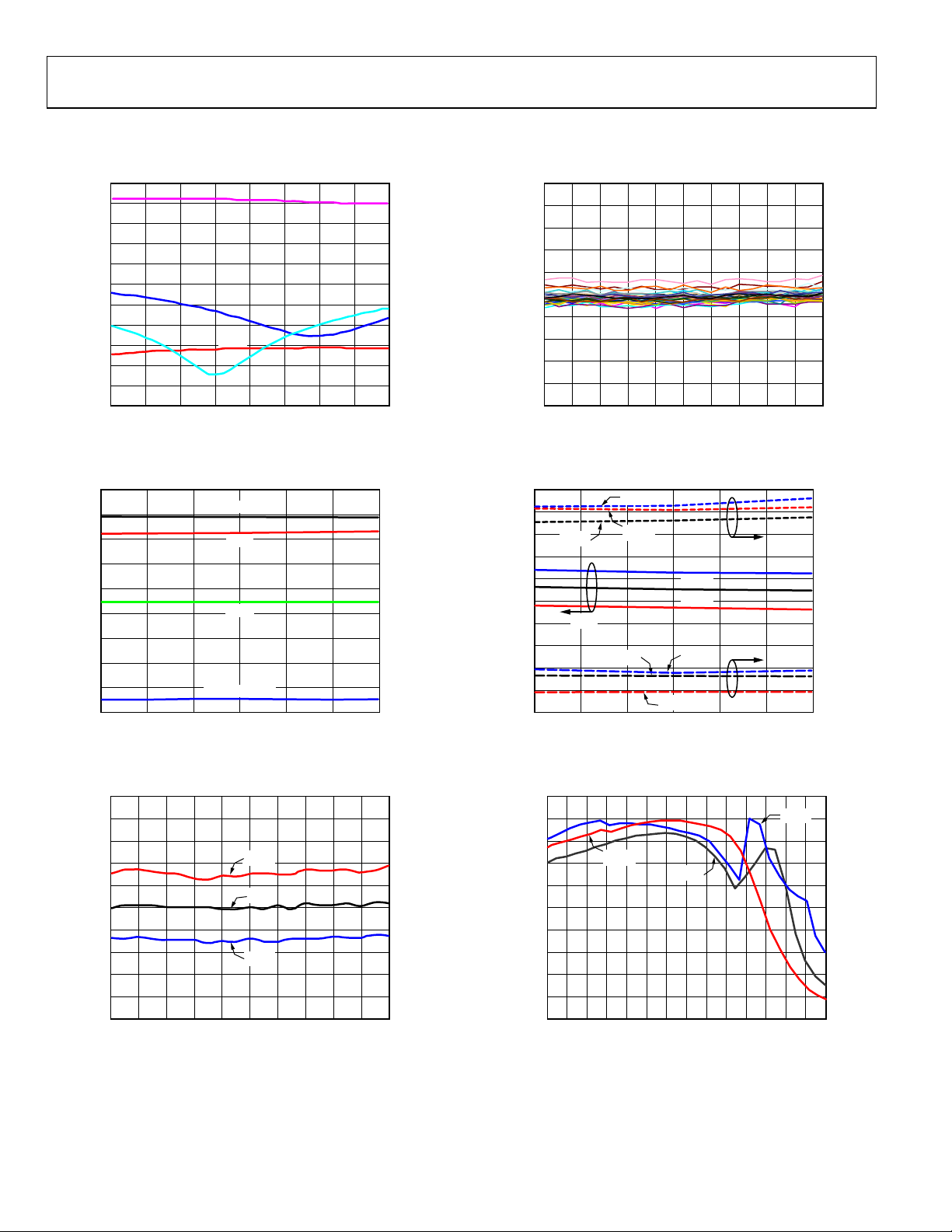

1950 MHz, VPOS = 5 V

Matched for optimal noise figure, external matching circuit included.

20

15

10

5

0

–5

–10

–15

S-PARAMETERS ( dB)

–20

–25

–30

–35

1800 1850 1900 1950 2000 2050 2100 2150 2200

S11

Figure 9. Typical S-Parameters, Log Magnitude

18

16

14

12

10

8

6

4

NOISE FI GURE AND GAIN (d B)

2

0

1920 1930 1940 1950 1960 1970 1980

Figure 10. Noise Figure, Gain, OIP3, and P1dB vs. Frequency

2.0

1.8

1.6

1.4

1.2

1.0

0.8

NOISE FI G URE (dB)

0.6

0.4

0.2

0

1800 2000198019601940192019001880186018401820

Figure 11. Noise Figure vs. Temperature

S21

S12

S22

FREQUENCY (MHz)

GAIN

OIP3

P1dB

NOISE FI GURE

FREQUENCY (MHz)

+85°C

+25°C

–40°C

FREQUENCY (MHz)

06828-009

45

40

35

30

25

20

15

OIP3 AND P1dB (dBm)

10

5

0

06828-010

06828-011

2.0

1.8

1.6

1.4

1.2

1.0

0.8

NOISE FI G URE (dB)

0.6

0.4

0.2

0

1800 1820 1840 1860 1880 1900 1920 1940 1960 20001980

FREQUENCY (MHz)

Figure 12. Noise Figure vs. Frequency at 25°C, Multiple Devices

18.0

17.5

17.0

16.5

16.0

15.5

GAIN (dB)

15.0

14.5

14.0

13.5

13.0

+25°C

GAIN

1920 1930 1940 1950 1960 1970 1980

–40°C

+85°C

+25°C

+85°C

FREQUENCY (MHz)

–40°C

+25°C

+85°C

–40°C

OIP3

P1dB

Figure 13. Gain, OIP3, and P1dB vs. Temperature

40

38

36

34

32

30

28

OIP3 (dBm)

26

24

22

20

–8 –4–6 –2 20181614121086420

Figure 14. OIP3 vs. Output Power (P

+85°C

+25°C

P

PER TONE (dBm)

OUT

) and Temperature

OUT

–40°C

06828-012

39

37

35

33

31

29

27

25

OIP3 AND P1dB (dBm)

23

21

19

06828-013

06828-014

Rev. A | Page 8 of 24

Loading...

Loading...