50 MHz to 2200 MHz Quadrature Modulator

FEATURES

Output frequency range: 50 MHz to 2200 MHz

1 dB output compression: 11 dBm @ 350 MHz

Noise floor: −160 dBm/Hz @ 350 MHz

Sideband suppression: −46 dBc @ 350 MHz

Carrier feedthrough: −38 dBm @ 350 MHz

30 dB of linear AGC dynamic range @ 350 MHz

Single supply: 4.75 V to 5.5 V

40-lead, Pb-free LFCSP_VQ with exposed paddle

APPLICATIONS

Radio-link infrastructures

Cable modem termination systems

Wireless/cellular infrastructure systems

Wireless local loops

WiMAX/broadband wireless access systems

GENERAL DESCRIPTION

The ADL5386 is a quadrature modulator with unmatched

integration levels for low intermediate frequency (IF) and radio

frequency (RF) transmitters within broadband wireless access

systems, microwave radio links, cable modem termination

systems, and cellular infrastructure equipment. The ADL5386

operates over a frequency range of 50 MHz to 2200 MHz. Its

excellent phase accuracy and amplitude balance supports high data

rate, complex modulation for next-generation communication

infrastructure equipment.

with Integrated Detector and VVA

ADL5386

In addition, the ADL5386 incorporates a standalone

logarithmic power detector, as well as a voltage variable

attenuator (VVA). The attenuator has its own separate input and

output pins for easy cascading with filters and buffer amplifiers.

The wide dynamic range of the power detector and VVA provides

flexibility in the choice of the signal monitoring point in the

transmitter system.

The wide baseband input bandwidth of 700 MHz allows for

either baseband drive or a drive from a complex IF signal.

Typical applications are in IF or direct-to-RF radio-link

transmitters, cable modem termination systems, broadband

wireless access systems, and cellular infrastructure equipment.

The ADL5386 takes signals from two differential baseband inputs

and modulates them onto two carriers in quadrature with each

other. The two internal carriers are derived from a single-ended,

external local oscillator (LO) input signal at twice the frequency

as the desired output. The output amplifier is designed to drive

a 50 load.

The ADL5386 consists of two die, one fabricated using the

Analog Devices, Inc., advanced SiGe bipolar process, and the other

using an external GaAs process. The ADL5386 is packaged in a

40-lead, Pb-free LFCSP_VQ with an exposed paddle. Performance

is specified over the −40°C to +85°C range. A Pb-free evaluation

board is also available.

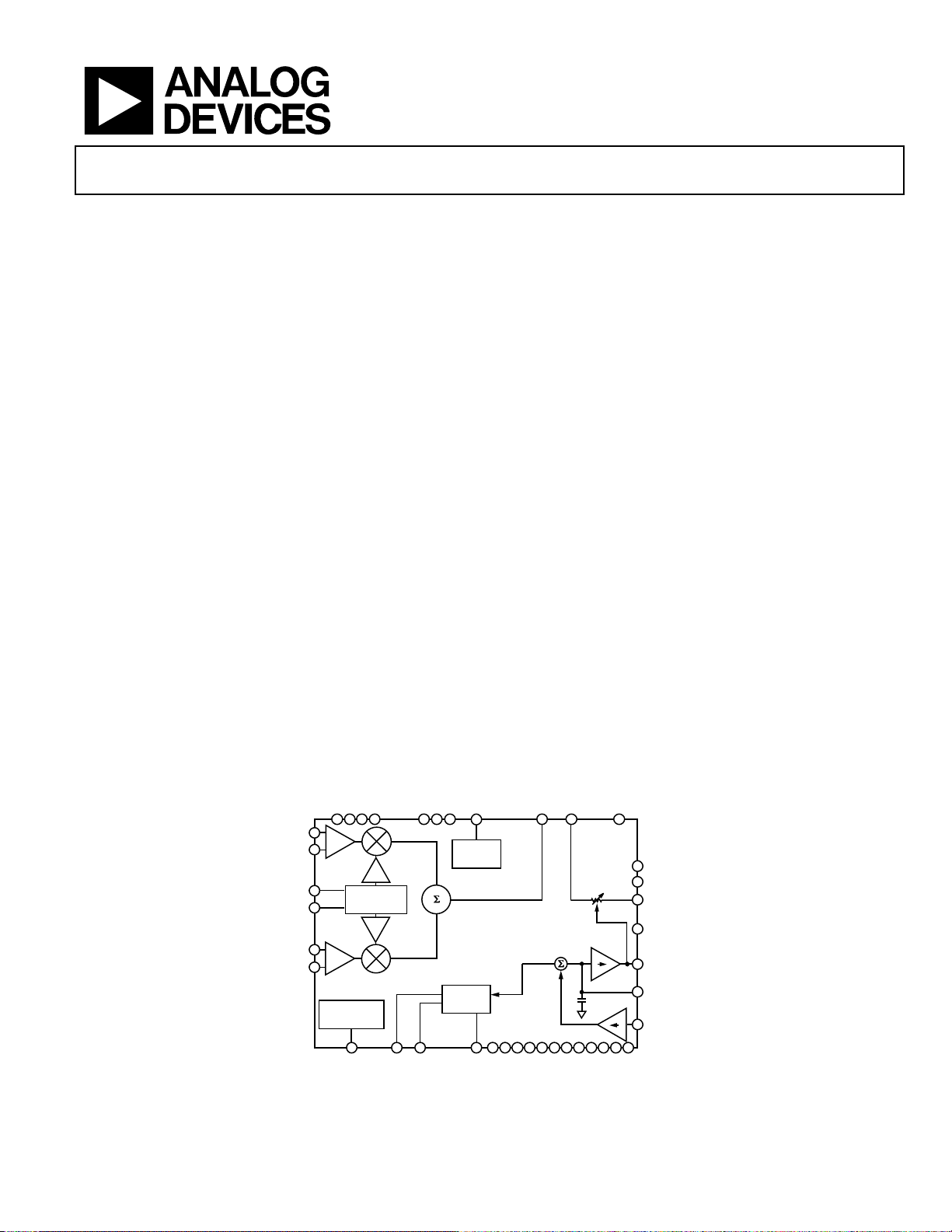

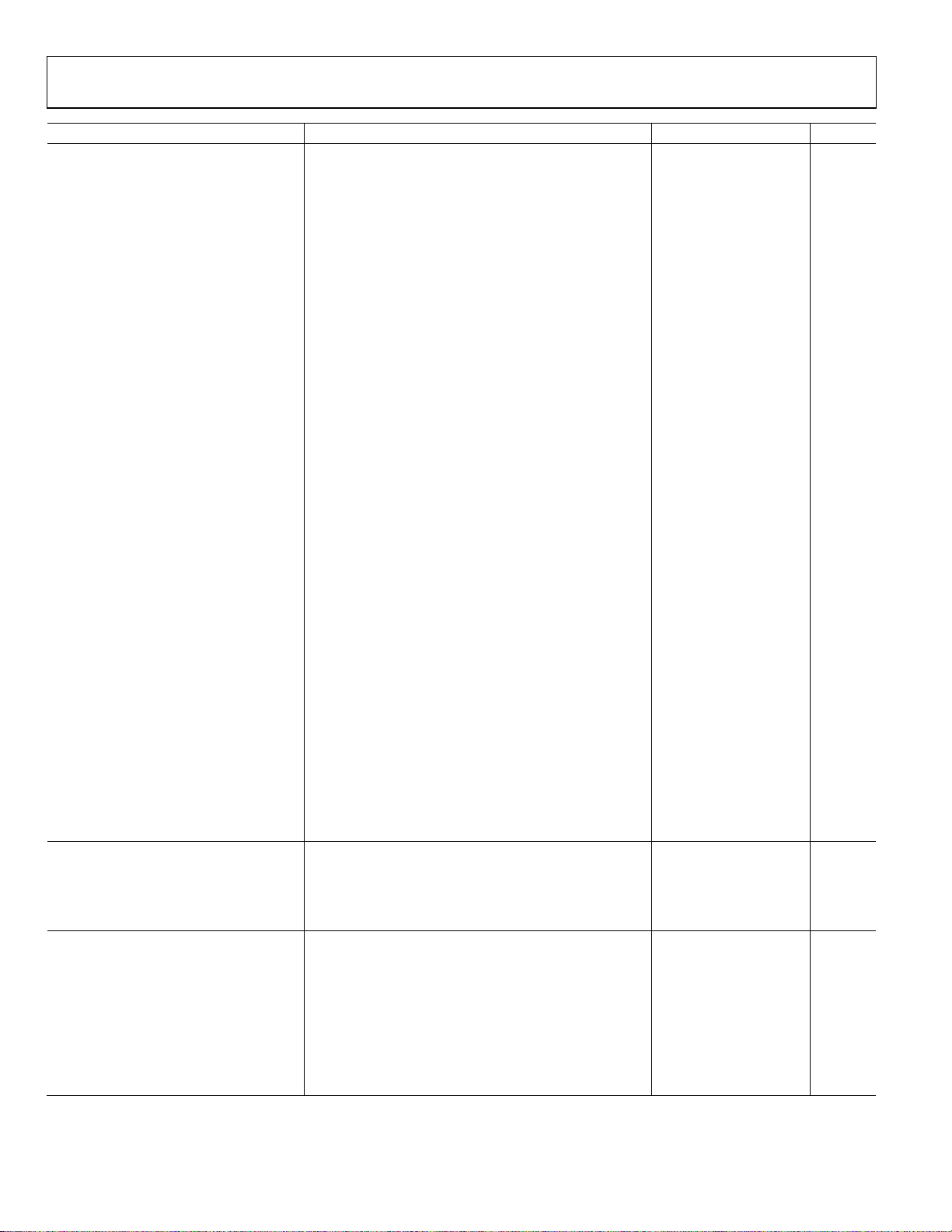

FUNCTIONAL BLOCK DIAGRAM

VPOS

25

IBBP

26

IBBN

33

LOIP

34

LOIN

29

QBBN

30

QBBP

TEMPERATURE

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

35 233638 37

QUADRATURE

PHASE

SPLITTER

SENSOR

8

TEMP INHIINLO

VPOS

12

22 21

DETECTOR

ENBL

24

IQ MOD

BIAS

LOG

39

Figure 1.

MODO UT

10

ADL5386

13511 161815 2819 27 3231 40

COMMTADJ

ATTI

NC

12

15dB

IV

9

ATTCM

17

14

ATTCM

20

ATTO

VREF

6

7

VDET/VCTL

4

CLPF

VSET

3

V

I

07664-001

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

ADL5386

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Typical Input and Output Impedances ...................................... 8

Absolute Maximum Ratings ............................................................ 9

ESD Caution .................................................................................. 9

Pin Configuration and Function Descriptions ........................... 10

Typical Performance Characteristics ........................................... 12

Modulator .................................................................................... 12

Voltage Variable Attentuator ..................................................... 16

Detector ....................................................................................... 17

Closed-Loop AGC Mode........................................................... 18

Circuit Description ......................................................................... 19

Overview ...................................................................................... 19

Quadrature Modulator Section ................................................ 19

Logarithmic Detector ................................................................. 20

Voltage Variable Attenuator (VVA) ......................................... 20

Basic Connections .......................................................................... 21

Open-Loop Power Control Mode ............................................ 21

Power Supply and Grounding .................................................. 22

Device Enable and Disable ........................................................ 22

Baseband Inputs ......................................................................... 22

LO Input ...................................................................................... 22

AGC Mode .................................................................................. 22

Setting the TADJ Resistor .......................................................... 24

Using the Detector in Standalone Measurement Mode ........ 25

DAC Modulator Interfacing ..................................................... 25

Spectral Products from Harmonic Mixing ............................. 27

LO Generation Using PLLs ....................................................... 27

Transmit DAC Options ............................................................. 28

Modulator/Demodulator Options ........................................... 28

Evaluation Board ............................................................................ 29

Characterization Setup .................................................................. 31

SSB Setup ..................................................................................... 31

Detector Setup ............................................................................ 31

VVA S-Paramters Setup ............................................................. 32

VVA Intermodulation Test Setup ............................................. 32

Outline Dimensions ....................................................................... 33

Ordering Guide .......................................................................... 33

REVISION HISTORY

1/09—Revision 0: Initial Version

Rev. 0 | Page 2 of 36

ADL5386

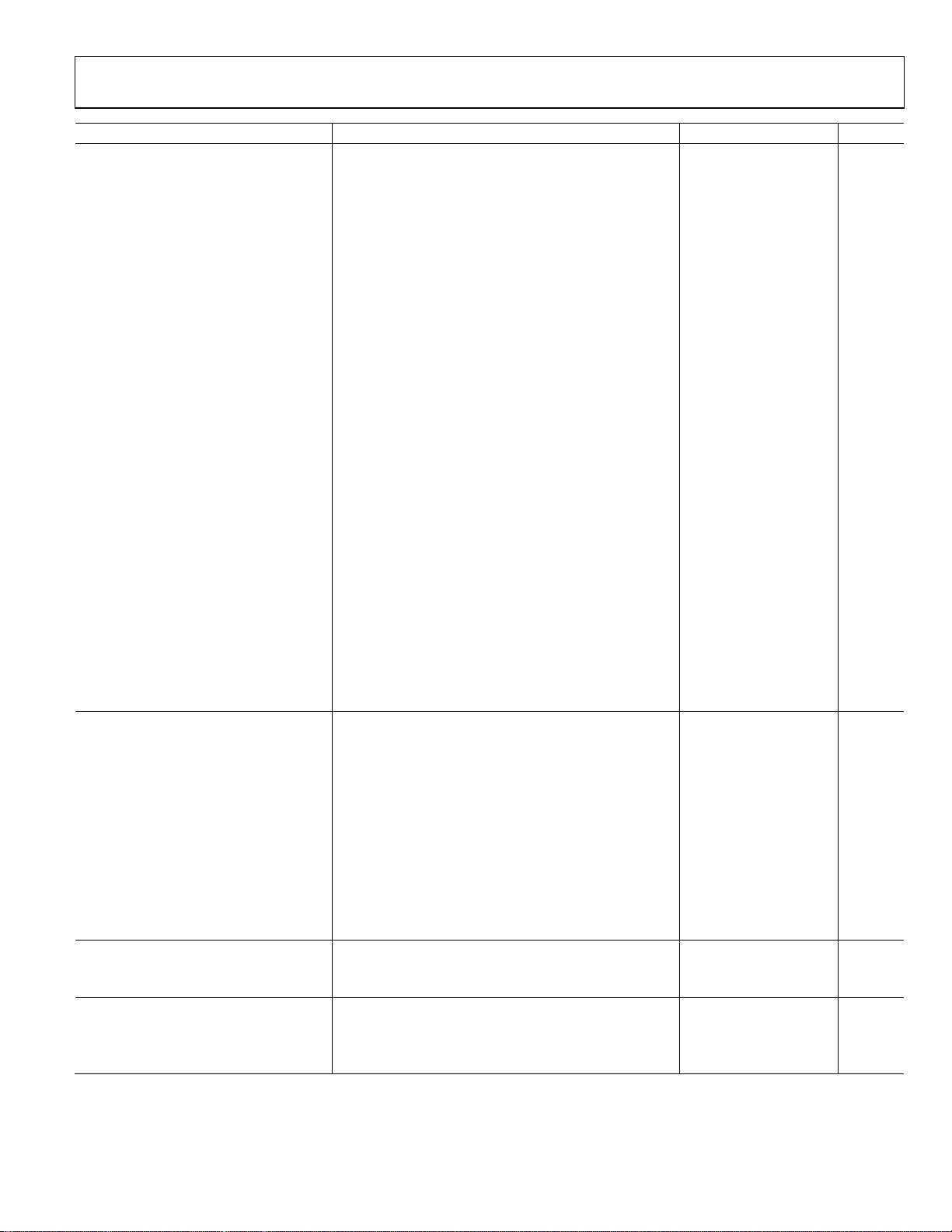

SPECIFICATIONS

Unless otherwise noted, VS = 5 V, TA = 25°C, LO = −7 dBm, I/Q inputs = 1.4 V p-p differential sine waves in quadrature on a 500 mV dc

bias, baseband frequency = 1 MHz, LO source and RF output load impedances are 50 Ω.

Table 1.

Parameter Conditions Min Typ Max Unit

MODULATOR DYNAMIC CHARACTERISTICS

Operating Frequency Range 50 2200 MHz

External LO Frequency Range External LO frequency is twice output frequency 100 4400 MHz

Output Frequency = 50 MHz

Output Power Single (lower) sideband output 5.6 dBm

Modulator Voltage Gain −1.3 dB

Output P1dB 10.8 dBm

Output Return Loss −21 dB

Carrier Leakage Unadjusted (nominal drive level) −43 dBm

At 85°C after optimization at 25°C −63 dBm

At −40°C after optimization at +25°C −63 dBm

Sideband Suppression Unadjusted (nominal drive level) −48 dBc

At 85°C after optimization at 25°C −60 dBc

At −40°C after optimization at +25°C −60 dBc

Quadrature Error −0.2 Degrees

I/Q Amplitude Balance 0.05 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −159 dBm/Hz

Output Frequency = 140 MHz

Output Power Single (lower) sideband output 5.7 dBm

Modulator Voltage Gain −1.2 dB

Output P1dB 11.1 dBm

Output Return Loss −21 dB

Carrier Leakage Unadjusted (nominal drive level) −42 dBm

At 85°C after optimization at 25°C −62 dBm

At −40°C after optimization at +25°C −62 dBm

Sideband Suppression Unadjusted (nominal drive level) −57 dBc

At 85°C after optimization at 25°C −60 dBc

At −40°C after optimization at +25°C −60 dBc

Quadrature Error −0.2 Degrees

I/Q Amplitude Balance 0.05 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −160 dBm/Hz

Output Frequency = 350 MHz

Output Power Single (lower) sideband output 4 5.5 7 dBm

Modulator Voltage Gain −1.4 dB

Output P1dB 11.1 dBm

Output Return Loss −19 dB

Carrier Leakage Unadjusted (nominal drive level) −38 dBm

At 85°C after optimization at 25°C −58 dBm

At −40°C after optimization at +25°C −58 dBm

= 5 dBm −80 dBc

OUT

= 5 dBm −58 dBc

OUT

= −3 dBm per tone 76 dBm

OUT

= −3 dBm per tone 26 dBm

OUT

= 5 dBm −79 dBc

OUT

= 5 dBm −56 dBc

OUT

= −3 dBm per tone 75 dBm

OUT

= −3 dBm per tone 25 dBm

OUT

Rev. 0 | Page 3 of 36

ADL5386

Parameter Conditions Min Typ Max Unit

Sideband Suppression Unadjusted (nominal drive level) −46 dBc

At 85°C after optimization at 25°C −57 dBc

At −40°C after optimization at +25°C −57 dBc

Quadrature Error −0.5 Degrees

I/Q Amplitude Balance 0.05 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −160 dBm/Hz

20 MHz offset from LO, output power = −5 dBm −156 dBm/Hz

Output Frequency = 860 MHz

Output Power Single (lower) sideband output 3.8 5.3 6.8 dBm

Modulator Voltage Gain −1.6 dB

Output P1dB 11.4 dBm

Output Return Loss −15 dB

Carrier Leakage Unadjusted (nominal drive level) −37 dBm

At 85°C after optimization at 25°C −56 dBm

At −40°C after optimization at +25°C −56 dBm

Sideband Suppression Unadjusted (nominal drive level) −39 dBc

At 85°C after optimization at 25°C −55 dBc

At −40°C after optimization at +25°C −55 dBc

Quadrature Error −0.9 Degrees

I/Q Amplitude Balance 0.05 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −160 dBm/Hz

20 MHz offset from LO, output power = −5 dBm −157 dBm/Hz

Output Frequency = 1450 MHz

Output Power Single (lower) sideband output 4.3 dBm

Modulator Voltage Gain −2.6 dB

Output P1dB 10.6 dBm

Output Return Loss −15 dB

Carrier Leakage Unadjusted (nominal drive level) −35 dBm

At 85°C after optimization at 25°C −50 dBm

At −40°C after optimization at +25°C −50 dBm

Sideband Suppression Unadjusted (nominal drive level) −43 dBc

At 85°C after optimization at 25°C −45 dBc

At −40°C after optimization at +25°C −45 dBc

Quadrature Error −0.2 Degrees

I/Q Amplitude Balance 0.03 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −160 dBm/Hz

= 5 dBm −76 dBc

OUT

= 5 dBm −53 dBc

OUT

= −3 dBm per tone 74 dBm

OUT

= −3 dBm per tone 25 dBm

OUT

= 5 dBm −72 dBc

OUT

= 5 dBm −49 dBc

OUT

= −3 dBm per tone 73 dBm

OUT

= −3 dBm per tone 25 dBm

OUT

= 5 dBm −67 dBc

OUT

= 5 dBm −45 dBc

OUT

= −3 dBm per tone 63 dBm

OUT

= −3 dBm per tone 25 dBm

OUT

Rev. 0 | Page 4 of 36

ADL5386

Parameter Conditions Min Typ Max Unit

Output Frequency = 1900 MHz

Output Power Single (lower) sideband output 3.2 dBm

Modulator Voltage Gain −3.7 dB

Output P1dB 9.2 dBm

Output Return Loss −13 dBm

Carrier Leakage Unadjusted (nominal drive level) −35 dBm

At 85°C after optimization at 25°C −53 dBm

At −40°C after optimization at +25°C −53 dBm

Sideband Suppression Unadjusted (nominal drive level) −30 dBc

At 85°C after optimization at 25°C −45 dBc

At −40°C after optimization at +25°C −45 dBc

Quadrature Error −3 Degrees

I/Q Amplitude Balance 0.02 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −160 dBm/Hz

20 MHz offset from LO, output power = −5 dBm −156 dBm/Hz

Output Frequency = 2150 MHz

Output Power Single (lower) sideband output 2.5 dBm

Modulator Voltage Gain −4.4 dB

Output P1dB 8.4 dBm

Output Return Loss −11 dB

Carrier Leakage Unadjusted (nominal drive level) −35 dBm

At 85°C after optimization at 25°C −48 dBm

At −40°C after optimization at +25°C −46 dBm

Sideband Suppression Unadjusted (nominal drive level) −34 dBc

At 85°C after optimization at 25°C −45 dBc

At −40°C after optimization at +25°C −45 dBc

Quadrature Error −1.2 Degrees

I/Q Amplitude Balance 0.03 dB

Second Harmonic (fLO − (2 × fBB)), P

Third Harmonic (fLO + (3 × fBB)), P

Output IP2 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Output IP3 F1 = 3.5 MHz, F2 = 4.5 MHz, P

Noise Floor 20 MHz offset from LO, all BB inputs at a bias of 500 mV −160 dBm/Hz

20 MHz offset from LO, output power = −5 dBm −155 dBm/Hz

LO Inputs Pin LOIP and Pin LOIN

LO Drive Level Characterization performed at typical level −13 −7 +2 dBm

Characterization performed at typical level (<140 MHz) −7 −7 +2 dBm

Input Impedance 50 Ω

Input Return Loss 350 MHz, LOIN ac-coupled to ground −7 dB

Baseband Inputs Pin IBBP, Pin IBBN, Pin QBBP, Pin QBBN

I and Q Input Bias Level 500 mV

Input Bias Current −60 μA

Bandwidth (0.1 dB) fLO = 2 × 900 MHz, P

Bandwidth (3 dB) fLO = 2 × 900 MHz, P

= 5 dBm −59 dBc

OUT

= 5 dBm −45 dBc

OUT

= −3 dBm per tone 55 dBm

OUT

= −3 dBm per tone 23 dBm

OUT

= 5 dBm −56 dBc

OUT

= 5 dBm −48 dBc

OUT

= −3 dBm per tone 53 dBm

OUT

= −3 dBm per tone 21 dBm

OUT

≈ −4 dBm 50 MHz

OUT

≈ −4 dBm 700 MHz

OUT

Rev. 0 | Page 5 of 36

ADL5386

Parameter Conditions Min Typ Max Unit

VOLTAGE VARIABLE AT TENUATOR

Pin VCTL, Pin ATTI, and Pin ATTO, open-loop mode,

attenuation control applied to VCTL

Output Frequency = 50 MHz

Insertion Loss Minimum attenuation, V

Attenuation Range Attenuation at V

= 2 V − Attenuation at V

VCTL

= 2 V 1.7 dB

VCTL

= 0 V 37.8 dB

VCTL

Return Loss 17 dB

Input IP3

Minimum attenuation, V

= 2 V, Δf = 1 MHz,

VCTL

input power = −3 dBm per tone

Output Frequency = 140 MHz

Insertion Loss Minimum attenuation, V

Attenuation Range Attenuation at V

= 2 V − Attenuation at V

VCTL

= 2 V 1.9 dB

VCTL

= 0 V 37 dB

VCTL

Return Loss 17 dB

Input IP3

Minimum attenuation, V

= 2 V, Δf = 1 MHz,

VCTL

input power = −3 dBm per tone

Output Frequency = 350 MHz

Insertion Loss Minimum attenuation, V

Attenuation Range Attenuation at V

= 2 V − Attenuation at V

VCTL

= 2 V 2.2 dB

VCTL

= 0 V 26.2 dB

VCTL

Return Loss 17 dB

Input IP3

Minimum attenuation, V

= 2 V, Δf = 1 MHz,

VCTL

input power = −3 dBm per tone

Output Frequency = 860 MHz

Insertion Loss Minimum attenuation, V

Attenuation Range Attenuation at V

= 2 V − Attenuation at V

VCTL

= 2 V 2.5 dB

VCTL

= 0 V 21 dB

VCTL

Return Loss 14 dB

Input IP3

Minimum attenuation, V

= 2 V, Δf = 1 MHz,

VCTL

input power = −3 dBm per tone

Output Frequency = 1900 MHz

Insertion Loss Minimum attenuation, V

Attenuation Range Attenuation at V

= 2 V − Attenuation at V

VCTL

= 2 V 3 dB

VCTL

= 0 V 19 dB

VCTL

Return Loss 13 dB

Input IP3

Minimum attenuation, V

= 2 V, Δf = 1 MHz,

VCTL

input power = −3 dBm per tone

Output Frequency = 2150 MHz

Insertion Loss Minimum attenuation, V

Attenuation Range Attenuation at V

= 2 V − Attenuation at V

VCTL

= 2 V 3.3 dB

VCTL

= 0 V 17 dB

VCTL

Return Loss 13 dB

Input IP3

Minimum attenuation, V

= 2 V, Δf = 1 MHz,

VCTL

input power = −3 dBm per tone

SWITCHING CHARACTERISTICS ATTCM (Pin 14 and Pin 17) = 1000 pF

VCTL Response Time

LOG DETECTOR

Frequency = 350 MHz, V

50 % of V

to10% of RF envelope

VCTL

Frequency = 350 MHz, V

50 % of V

to 90% of RF envelope

VCTL

In measurement mode, VDET/VCTL is shorted to VSET;

= 2 V to 0 V; measured from

VCTL

= 0 V to 2 V; measured from

VCTL

in controller mode, the setpoint voltage is applied to VSET;

the CW input signal is applied at INHI

f = 50 MHz R

= 22.1 kΩ

TAD J

±1 dB Dynamic Range TA = 25°C 28 dB

Slope1 −21 mV/dB

Intercept1 18.2 dBm

VDET or VSET Voltage PIN = −10 dBm 0.59 V

PIN = −30 dBm 1.01 V

36 dBm

36 dBm

35 dBm

35 dBm

36 dBm

35 dBm

125 ns

15 ns

Rev. 0 | Page 6 of 36

ADL5386

Parameter Conditions Min Typ Max Unit

f = 140 GHz R

±1 dB Dynamic Range TA = 25°C 28 dB

Slope1 −21.1 mV/dB

Intercept1 17.8 dBm

VDET or VSET Voltage PIN = −10 dBm 0.59 V

PIN = −30 dBm 1.01 V

f = 350 MHz R

±1 dB Dynamic Range TA = 25°C 26 dB

Slope1 −21.3 mV/dB

Intercept1 17.1 dBm

VDET or VSET Voltage PIN = −10 dBm 0.58 V

PIN = −30 dBm 1.0 V

f = 860 MHz R

±1 dB Dynamic Range TA = 25°C 25 dB

Slope1 −21.6 mV/dB

Intercept1 16.2 dBm

VDET or VSET Voltage PIN = −10 dBm 0.57 V

PIN = −30 dBm 1.00 V

f = 1900 MHz R

±1 dB Dynamic Range TA = 25°C 26 dB

Slope1 −22.7 mV/dB

Intercept1 13.5 dBm

VDET or VSET Voltage PIN = −10 dBm 0.54 V

PIN = −30 dBm 0.99 V

f = 2150 MHz R

±1 dB Dynamic Range TA = 25°C 24 dB

Slope1 −23.2 mV/dB

Intercept1 12.6 dBm

VDET or VSET Voltage PIN = −10 dBm 0.53 V

PIN = −30 dBm 0.99 V

LOG DETECTOR OUTPUT INTERFACE VDET

VDET Voltage Swing V

V

Small Signal Bandwidth Simulated, INHI = −10 dBm, from CLPF to VOUT >100 MHz

Output Noise INHI = 2.2 GHz, –10 dBm, f

Fall Time Input level = no signal to −10 dBm, 90% to 10%, C

Input level = no signal to −10 dBm, 90% to 10%, C

Rise Time Input level = −10 dBm to no signal, 10% to 90%, C

Input level = −10 dBm to no signal, 10% to 90%, C

Video Bandwidth 15 MHz

VSET Incremental Input Resistance P

VSET Input Bias Current P

TAD J INTERFACE TADJ

Input Resistance TADJ = 0.9 V, sourcing 50 μA 13 kΩ

Disable Threshold Voltage TADJ = open V

TEMPERATURE SENSOR OUTPUT TEMP

Output Voltage TA = 27.15°C, 300K, RL = 1 MΩ (after full warmup) 1.45 V

Temperature Slope −40°C ≤ TA ≤ +85°C, RL = 1 MΩ 4.6 mV/°C

Output Impedance 1 kΩ

= 22.1 kΩ

TAD J

= 22.1 kΩ

TAD J

= 22.1 kΩ

TAD J

= 22.1 kΩ

TAD J

= 22.1 kΩ

TAD J

= 0 V, INHI = open, controller mode 2 V

VSET

= 2 V, INHI = open, controller mode 10 mV

VSET

= 0 dBm, AGC mode, V

OUT

= 0 dBm, AGC mode, V

OUT

= 100 kHz, C

NOISE

= 0.9 V to 1 V 33,000 dV/dI

VSET

= 1 V 25 μA

VSET

= open 73 nV/√Hz

CLPF

= 8 pF 42 ns

CLPF

= 0.1 μF 178 μs

CLPF

= 8 pF 29 ns

CLPF

= 0.1 μF 174 μs

CLPF

− 0.4 V

VPOS

Rev. 0 | Page 7 of 36

ADL5386

Parameter Conditions Min Typ Max Unit

ENABLE INPUT ENBL

Input Bias Current ENBL = 5 V 0.5 μA

ENBL = 0 V −0.7 μA

ENBL High Level (Logic 1) 1.5 V

ENBL Low Level (Logic 0) 0.4 V

POWER SUPPLIES Pin VPOS

Voltage 4.75 5.5 V

Supply Current ENBL = high 230 245 mA

In sleep mode, ENBL = low and TADJ = high 2.2 mA

In detector disabled mode, ENBL = high and TADJ = high 215 mA

1

Slope and intercept are determined by calculating the best-fit line between the power levels of −33 dBm and −10 dBm at the specified input frequency.

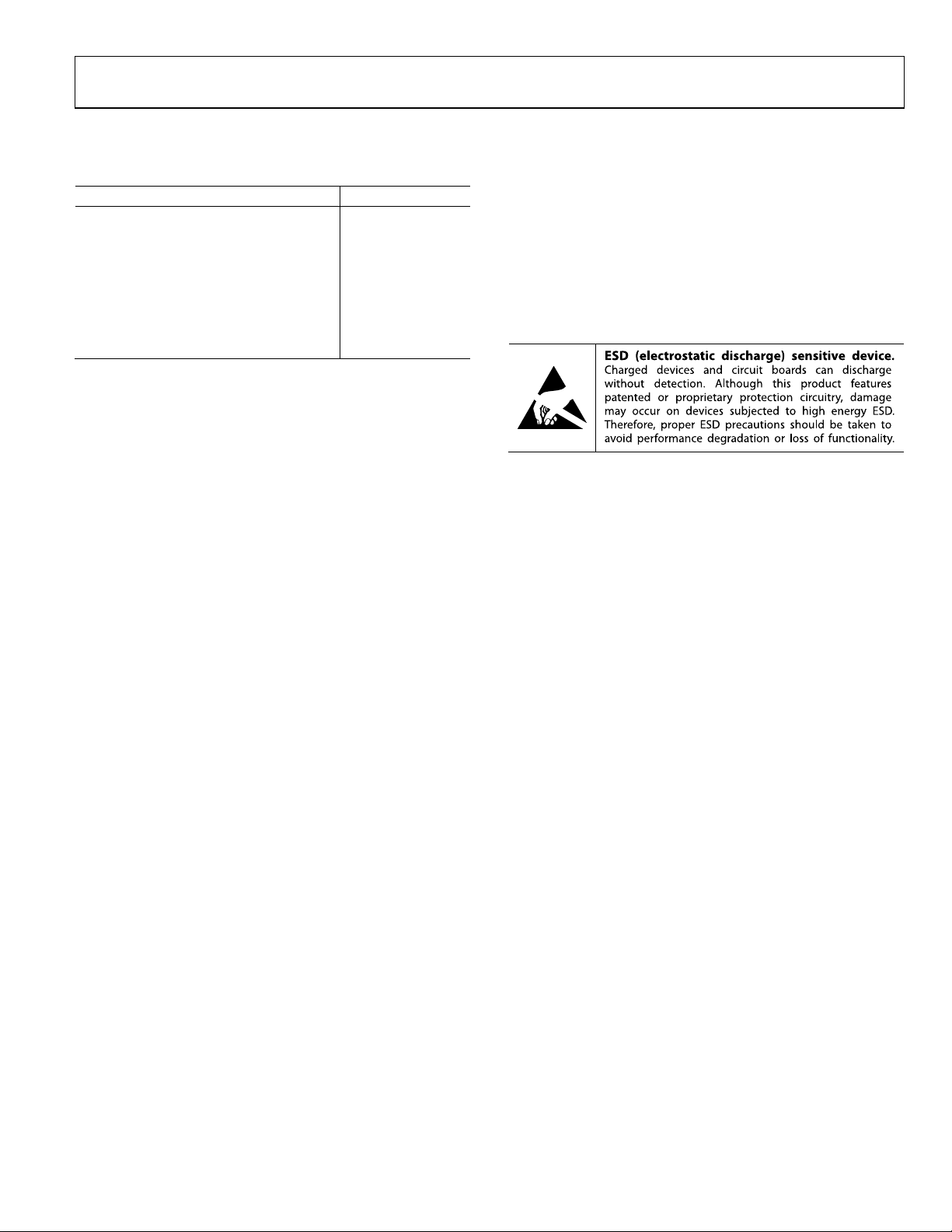

TYPICAL INPUT AND OUTPUT IMPEDANCES

Unless otherwise noted, VS = 5 V, TA = 25°C. All impedances are normalized to 50 Ω. The effects of the test fixture are de-embedded up to

the pins of the device.

Table 2.

Frequency (MHz) LO Input Impedance at 2× Frequency Modulator Output Impedance Detector Input Impedance

50 1.393 − j0.027 0.847 − j0.016 28.463 − j11.386

140 1.406 + j0.013 0.839 + j0.019 15.159 − j15.234

350 1.441 + j0.039 0.82 + j0.065 4.661 − j10.6

860 1.66 + j0.077 0.764 + j0.166 1.158 − j4.58

1450 2.261 − j0.304 0.799 + j0.231 0.567 − j2.545

1900 1.436 − j1.898 0.856 + j0.371 0.375 − j1.866

2150 0.517 − j1.446 0.862 + j0.51 0.308 − j1.652

Rev. 0 | Page 8 of 36

ADL5386

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage, VPOS 5.5 V

IBBP, IBBN, QBBP, QBBN Range 0 V to 2.0 V

LOIP and LOIN 13 dBm

Internal Power Dissipation 1.4 W

θJA (Exposed Paddle Soldered Down) 38°C/W

Maximum Junction Temperature 150°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 9 of 36

ADL5386

A

V

V

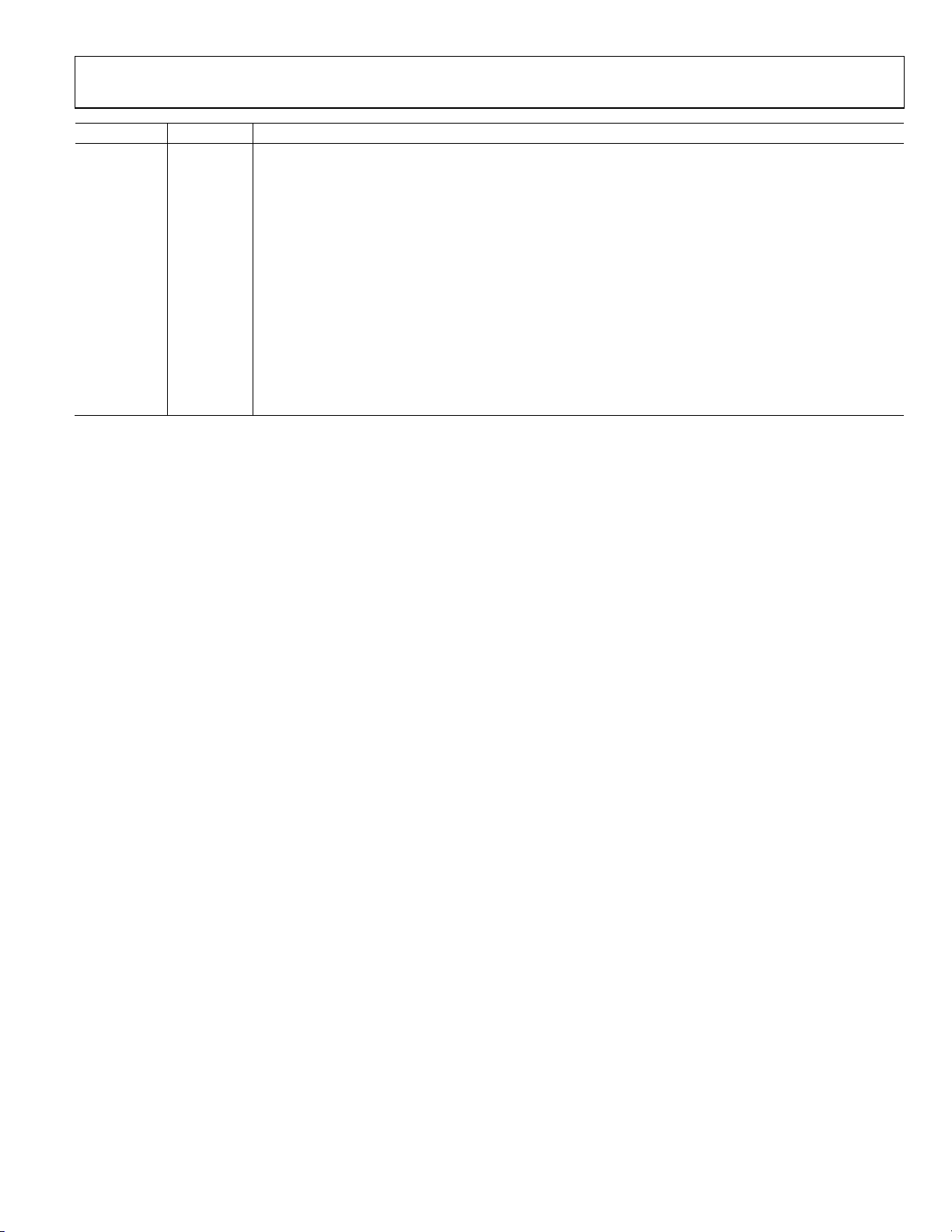

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

TTIMO DOUT

12

10

15dB

IV

9

ATTCM

17

14

ATTCM

20

ATTO

6

VREF

7

VDET/VCTL

4

CLPF

VSET

3

V

I

IBBP

IBBN

LOIP

LOIN

QBBN

QBBP

25

26

33

34

29

30

TEMPERATURE

SENSOR

POS

35 233638 37

QUADRATURE

PHASE

SPLITTER

ENBL NC

POS

22

21

24

IQ MOD

BIAS

ADL5386

LOG

DETECTOR

8

TEMP I NHIINLO

NOTES

1. NC = NO CONNEC T.

2. CONNECT T HE EXPOSED PAD TO GROUND VIA A LOW IMPEDANCE PATH.

12

39

13511 161815 2819 27 3231 40

COMMTADJ

07664-002

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 INLO Detector Common. This pin should be ac-coupled to ground.

2 INHI

Detector Input. When operating in AGC mode, a portion of the signal at the output of the VVA (or at the

output of a subsequent stage) is coupled back to this input. The signal should be ac-coupled into INHI. To provide

a 50 Ω match at INHI, a 50 Ω resistor should be connected between INHI and ground (with the ac-coupling

capacitor placed between the resistor and the INHI pin).

3 VSET Setpoint Input. Setpoint input for controller mode or feedback input for measurement mode.

4 CLPF

AGC Loop Filter Capacitor. The ground-referenced capacitor that is connected to this pin sets the loop bandwidth

of the AGC circuit.

5, 11, 13, 15,

COMM Device Common. Connect these pins to the same low impedance ground plane.

16, 18, 19, 27,

28, 31, 32, 40

6 VREF

Attenuator Control Voltage Reference. In AGC mode, this pin should be left open. In open-loop mode, when

the VVA is being controlled externally, a 2 V reference voltage should be applied to this pin.

7 VDET/VCTL

Detector Output/VVA Control Voltage Input. When the VVA is being controlled externally (open-loop mode),

the attenuation is controlled by the external voltage applied to this pin. The VVA control range is from 0 V

(maximum attenuation) to 2 V (minimum attenuation). In this mode, VREF (Pin 6) should be tied to approximately

2 V. When the VVA is being operated in AGC mode, this pin is left open with the voltage on the pin representing the

AGC drive voltage to the VVA. If the VVA is not being used, the AGC log amp can be used as a standalone detector

by connecting this pin to VSET. In this mode, the log amp output voltage is available at this pin.

8 TEMP

Temperature Sensor Output. This pin provides a standalone temperature sensor output voltage. At room

temperature, the nominal output voltage is equal to 1.45 V. The slope of the output voltage is equal to 4.6 mV/°C.

9 NC No Connect. Do not connect this pin.

10 MODOUT

RF Output of IQ Modulator. Single-ended, 50 Ω internally biased RF output. MODOUT is generally

ac-coupled to the input of the VVA (either ATTI or ATTO).

12, 20 ATTI, ATTO

VVA RF Input/Output. ATTI is normally ac-coupled to MODOUT. However, because the VVA is completely reversible,

MODOUT can also drive ATTO with ATTI operating as the VVA output.

14, 17 ATTCM VVA Input/Output Common. These pins should be ac-coupled to ground.

21 to 23,

35 to 38

VPOS

Power Supply. Positive supply voltage pins. All pins should be connected to the same supply (VS). To ensure

adequate external bypassing, connect a 0.1 μF capacitor between each pin and ground.

Rev. 0 | Page 10 of 36

ADL5386

Pin No. Mnemonic Description

24 ENBL

25, 26, 29, 30

33 LOIP

34 LOIN Local Oscillator Common. This pin should be ac-coupled to ground.

39 TADJ

41 (EPAD)

IBBP, IBBN,

QBBN, QBBP

Exposed

Pad (EPAD)

IQ Modulator Enable. The IQ modulator is enabled by connecting this pin to VPOS and is disabled by connecting

ENBL to ground.

Differential In-Phase and Quadrature Baseband Inputs. These high impedance inputs should be dc-biased to 0.5 V.

Nominal characterized ac signal swing is 700 mV p-p on each pin, resulting in a differential drive of

1.4 V p-p on each input pair. These inputs are not self-biased and have to be externally biased.

Local Oscillator Input. The local oscillator signal, at two times the output frequency, should be ac-coupled into

this pin.

Temperature Compensation Adjustment Pin and Detector Enable/Disable. This pin is primarily used to

provide temperature compensation to the on-chip log amp based AGC circuit. The correct compensation

current is set by connecting a ground-referenced resistor to this pin. A value of 22.1 kΩ is recommended

for the frequencies over which the ADL5386 is specified. The TADJ pin can also be used to power down the

detector section of the ADL5386 by connecting it to VPOS. The detector must be disabled when the

modulator/VVA is operating in open loop mode.

Connect the exposed pad to ground via a low impedance path.

Rev. 0 | Page 11 of 36

Loading...

Loading...