Analog Devices ADL5306 Datasheet

60 dB Range (100 nA to 100 µA)

FEATURES

Optimized for fiber optic photodiode interfacing

Measures current over 3 decades

Law conformance 0.1 dB from 100 nA to 100 μA

Single- or dual-supply operation (3 V to ±5.5 V total)

Full log-ratio capabilities

Temperature stable

Nominal slope of 10 mV/dB (200 mV/decade)

Nominal intercept of 1 nA (set by external resistor)

Optional adjustment of slope and intercept

Rapid response time for a given current level

Miniature 16-lead chip scale package (LFCSP 3 mm × 3 mm)

Low power: ~5 mA quiescent current

APPLICATIONS

Low cost optical power measurement

Wide range baseband logarithmic compression

Measurement of current and voltage ratios

Optical absorbance measurement

GENERAL DESCRIPTION

The ADL5306∗ is a low cost microminiature logarithmic converter

optimized for determining optical power in fiber optic systems. The

ADL5306 is derived from the AD8304 and AD8305 translinear

logarithmic converters. This family of devices provides wide

measurement dynamic range in a versatile and easy-to-use form. A

single-supply voltage between 3 V and 5.5 V is adequate; dual

supplies may optionally be used. Low quiescent current (5 mA

typical) permits use in battery-operated applications.

I

, the 100 nA to 100 µA input current applied to the INPT pin, is

PD

the collector current of an optimally scaled NPN transistor that

converts this current to a voltage (V

relationship. A second converter is used to handle the reference

current, I

, applied to IREF. These input nodes are biased slightly

REF

above ground (0.5 V). This is generally acceptable for photodiode

applications where the anode does not need to be grounded.

Similarly, this bias voltage is easily accounted for in generating I

The logarithmic front end’s output is available at VLOG.

The basic logarithmic slope at this output is 200 mV/decade

(10 mV/dB) nominal; a 60 dB range corresponds to a 600 mV

output change. When this voltage (or the buffer output) is applied

to an ADC that permits an external reference voltage to be

employed, the ADL5306’s 2.5 V voltage reference output at VREF

can be used to improve scaling accuracy.

) with a precise logarithmic

BE

REF

Low Cost Logarithmic Converter

ADL5306

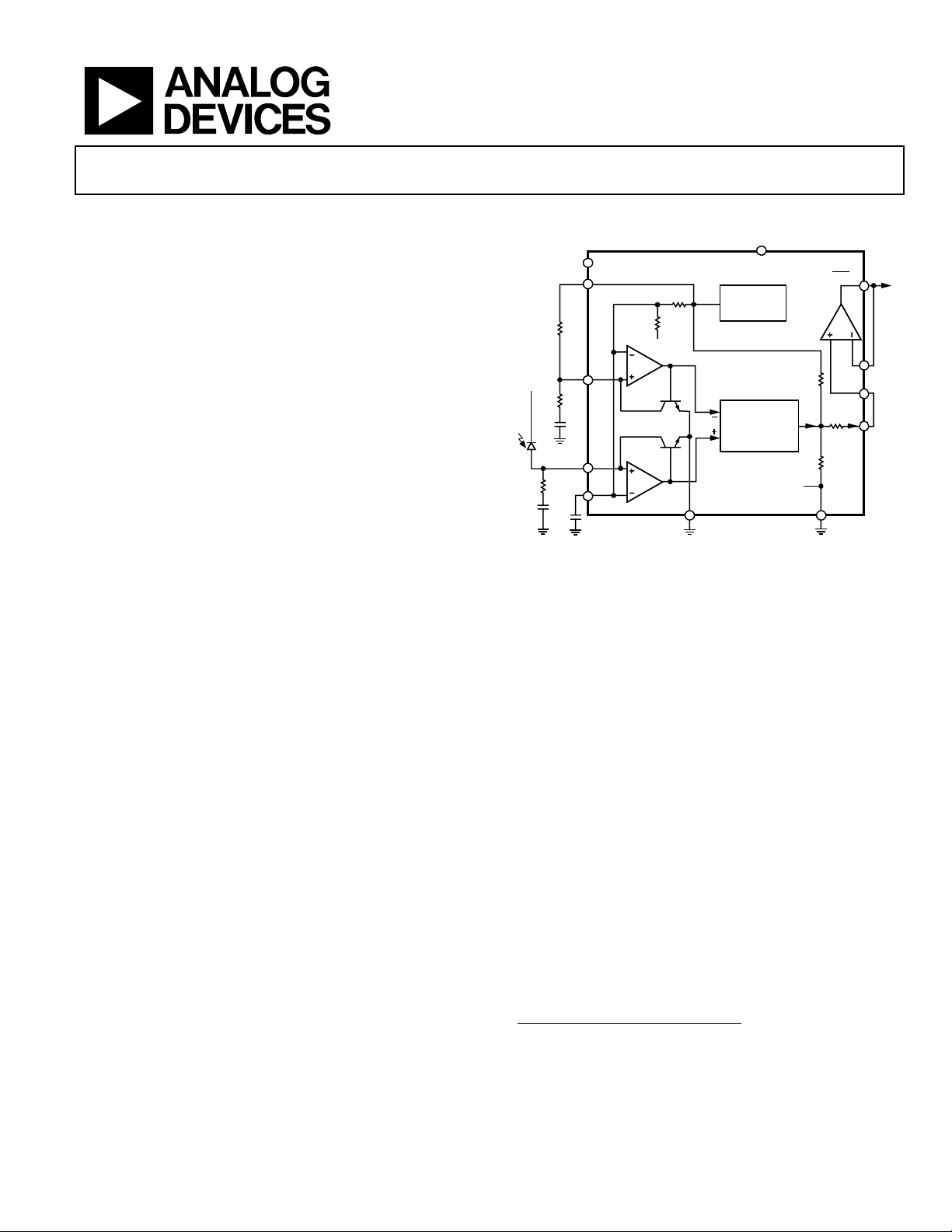

FUNCTIONAL BLOCK DIAGRAM

+5V

NC

VREF

200kΩ

V

BIAS

1kΩ

1nF

R

REF

1kΩ

1nF

0.5V

IREF

I

PD

INPT

VSUM

1nF

0.5V

20kΩ

80kΩ

COMM

Q2

Q1

VNEG

Figure 1. Functional Block Diagram

The logarithmic intercept (reference current) is nominally

positioned at 1 nA by using the externally generated, 100 µA I

current provided by a 200 kΩ resistor connected between VREF, at

2.5 V, and IREF, at 0.5 V. The intercept can be adjusted over a

narrow range by varying this resistor. The part can also operate in a

log-ratio mode, with limited accuracy, where the numerator and

denominator currents are applied to INPT and IREF, respectively.

A buffer amplifier is provided to drive substantial loads, raise the

basic 10 mV/dB slope, serve as a precision comparator (threshold

detector), or implement low-pass filters. Its rail-to-rail output stage

can swing to within 100 mV of the positive and negative supply

rails, and its peak current-sourcing capacity is 25 mA.

A fundamental aspect of translinear logarithmic converters is that

small-signal bandwidth falls as current level diminishes, and low

frequency noise-spectral density increases. At the 100 nA level, the

ADL5306’s bandwidth is about 100 kHz; it increases in proportion

to I

.

up to a maximum of about 10 MHz. The increase in noise

PD

level at low currents can be addressed by using a buffer amplifier to

realize low-pass filters of up to three poles.

The ADL5306 is available in a 16-lead LFCSP package and is

specified for operation from–40°C to +85°C.

∗

Protected by US Patents 4,604,532 and 5,519,308; other patents pending.

VPOS

2.5V

GENERATOR

V

BE2

TEMPERATURE

COMPENSATION

V

BE1

BIAS

COMM

0.2 log

14.2kΩ

I

6.69kΩ

COMM

LOG

I

PD

10

( )

1nA

451Ω

VOUT

SCAL

BFIN

VLOG

03727-0-001

REF

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2003 Analog Devices, Inc. All rights reserved.

ADL5306

TABLE OF CONTENTS

Specifications..................................................................................... 3

Response Time and Noise Considerations ............................. 10

Absolute Maximum Ratings............................................................ 4

Pin Configuration and Pin Function Descriptions...................... 5

Typical Performance Characteristics ............................................. 6

General Structure.............................................................................. 9

Theory............................................................................................ 9

Managing Intercept and Slope.................................................. 10

REVISION HISTORY

Rev. 0: Initial Version

Applications..................................................................................... 11

Using a Negative Supply ............................................................ 11

Characterization Methods ........................................................ 12

Evaluation Board............................................................................ 14

Outline Dimensions....................................................................... 16

Ordering Guide .......................................................................... 16

Rev. 0 | Page 2 of 16

ADL5306

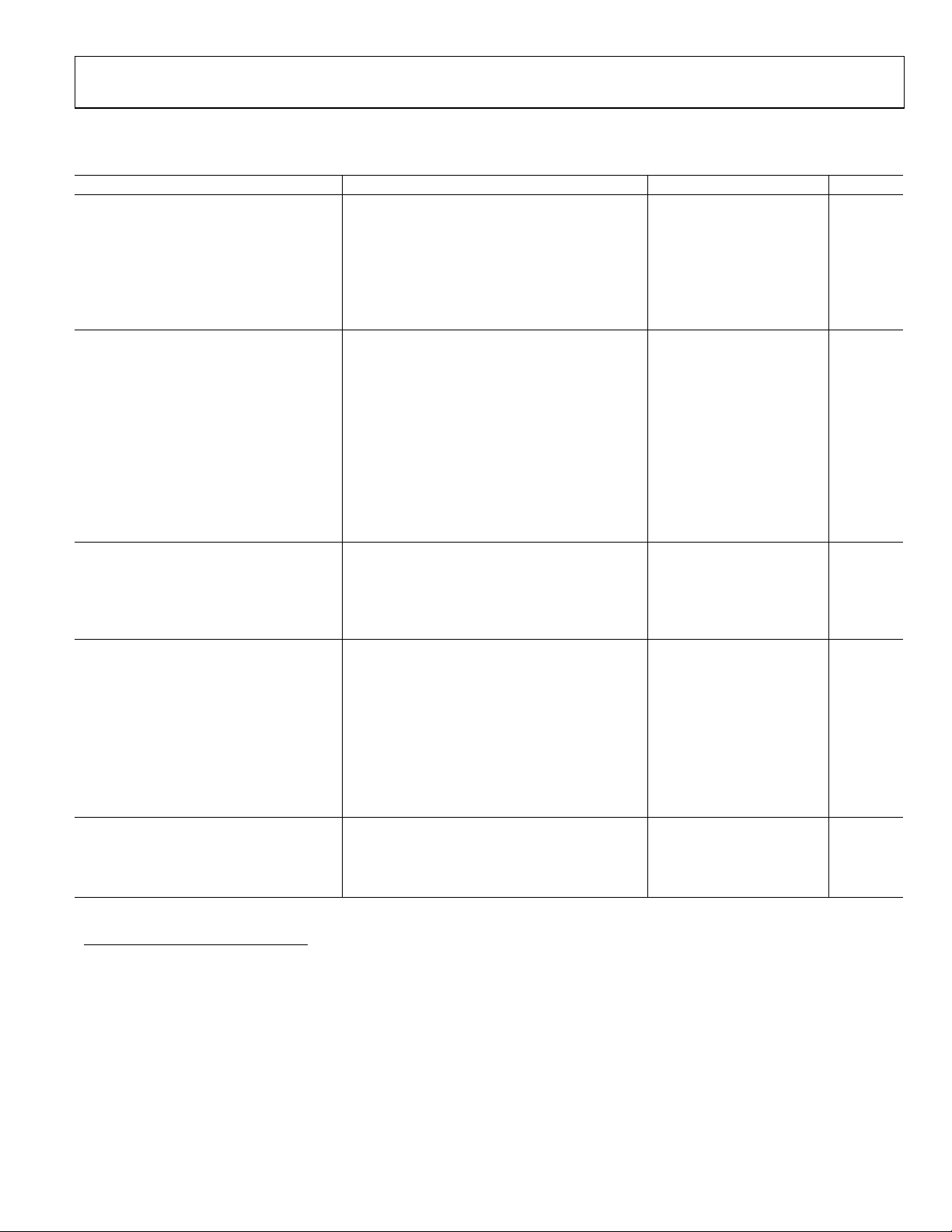

SPECIFICATIONS

Table 1. VP = 5 V, VN = 0, TA = 25°C, R

Parameter Conditions Min1 Typ Max1 Unit

INPUT INTERFACE INPT (Pin 4), IREF (Pin 3)

Specified Current Range, I

PD

Input Current Min/Max Limits Flows toward INPT pin 1 mA

Reference Current, I

, Range Flows toward IREF pin 100n 100µ A

REF

Summing Node Voltage Internally preset; may be altered by user 0.46 0.5 0.54 V

Temperature Drift

Input Offset Voltage VIN – V

LOGARITHMIC OUTPUT VLOG (Pin 9)

Law Conformance Error 100 nA < IPD < 100 µA 0.1 0.4 dB

Wideband Noise

Small-Signal Bandwidth

3

3

Maximum Output Voltage 1.7 V

Minimum Output Voltage Limited by VN = 0 V 0.01 V

Output Resistance 4.375 5 5.625 kΩ

REFERENCE OUTPUT VREF (Pin 2)

Maximum Output Current Sourcing (grounded load) 20 mA

Incremental Output Resistance Load current < 10 mA 2 Ω

OUTPUT BUFFER BFIN (Pin 10); SCAL (Pin 11); VOUT (Pin 12)

Input Offset Voltage –20 +20 mV

Input Bias Current Flowing out of Pin 10 or Pin 11 0.4

Incremental Input Resistance 35 MΩ

Output Range RL = 1 kΩ to ground VP – 0.1 V

Incremental Output Resistance Load current < 10 mA 0.5 Ω

Peak Source/Sink Current 50 mA

Small-Signal Bandwidth

Slew Rate 0.2 V to 4.8 V output swing 15 V/µs

POWER SUPPLY VPOS (Pin 8); VNEG (Pin 6)

Positive Supply Voltage

Quiescent Current 5.4 6.6 mA

Negative Supply Voltage (Optional)

= 200 kΩ, unless otherwise noted

REF

Flows toward INPT pin 100n 100µ A

–40°C < T

SUM

< +85°C

A

, V

– V

IREF

–20 +20 mV

SUM

0.015

190 200 210 mV/dec Logarithmic Slope

–40°C < TA < +85°C

185 215 mV/dec

0.3 1 1.7 nA Logarithmic Intercept2

–40°C < TA < +85°C

0.1 2.5 nA

IPD > 1 µA 0.7 µV/√Hz

IPD > 1 µA 0.7 MHz

2.435 2.5 2.565 V Voltage wrt Ground

–40°C < TA < +85°C

2.4 2.6 V

GAIN = 1 15 MHz

– VN ) ≤ 11 V

(V

P

– VN ) ≤ 11 V

(V

P

3 5 5.5 V

–5.5 0 V

mV/°C

µA

1

Minimum and maximum specified limits on parameters that are guaranteed but not tested are six sigma values.

2

Other values of logarithmic intercept can be achieved by adjusting R

3

Output noise and incremental bandwidth are functions of input current measured using the output buffer connected for GAIN = 1.

.

REF

Rev. 0 | Page 3 of 16

ADL5306

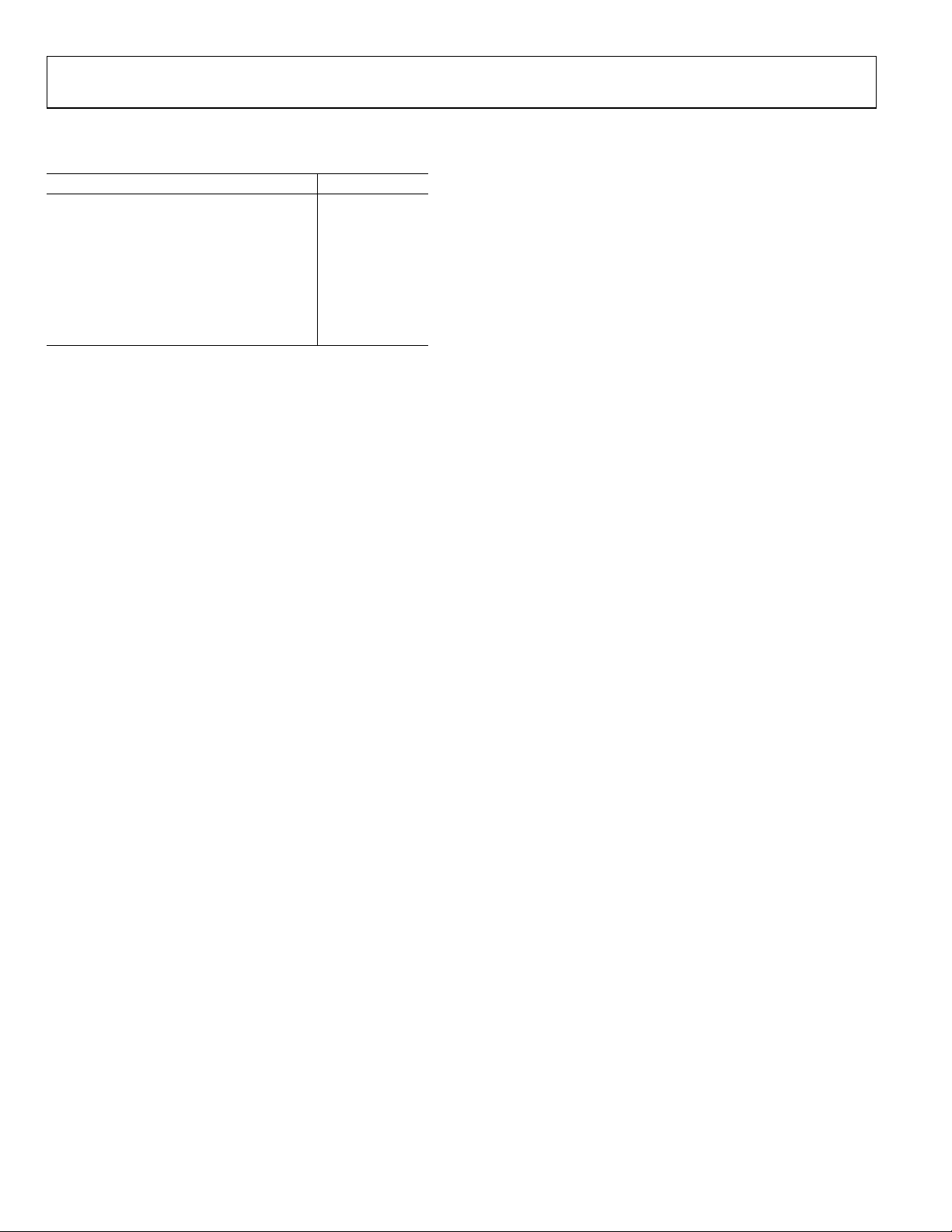

ABSOLUTE MAXIMUM RATINGS

Table 2. ADL5306 Absolute Maximum Ratings

Parameter Rating

Supply Voltage VP – V

Input Current 20 mA

Internal Power Dissipation 500 mW

θJA 135°C/W

Maximum Junction Temperature 125°C

Operating Temperature Range –40°C to +85°C

Storage Temperature Range –65°C to +150°C

Lead Temperature Range (Soldering 60 sec) 300°C

N

12 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. 0 | Page 4 of 16

ADL5306

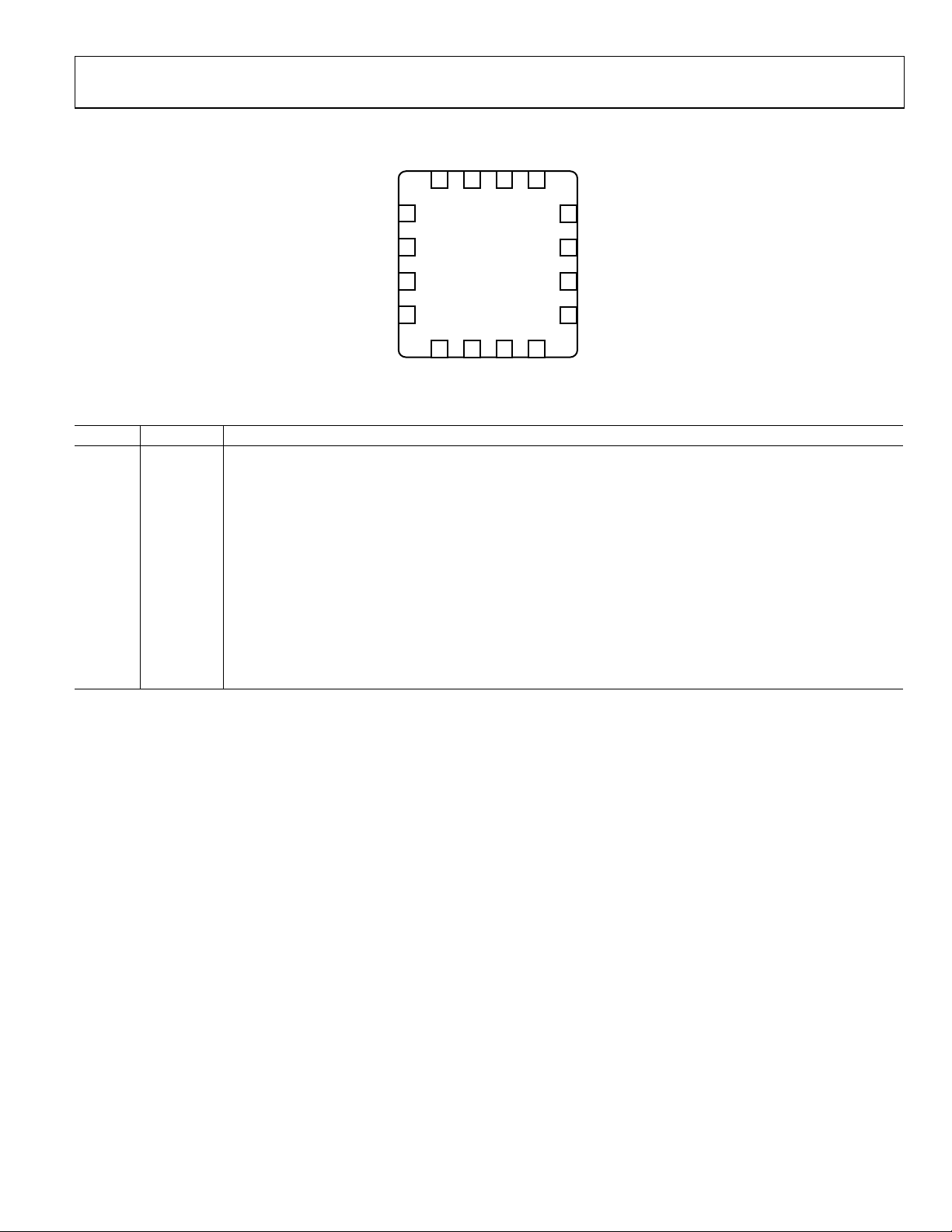

PIN CONFIGURATION AND PIN FUNCTION DESCRIPTIONS

COMMCOMMCOMM

COMM

13141516

VOUT

NC

1

12

VREF

2

SCAL

11

ADL5306

BFIN

VPOS

10

9

03727-0-002

VLOG

IREF

INPT

3

4

5678

VNEGVSUM

VNEG

Figure 2. 16-Lead Leadframe Chip Scale Package (LFCSP)

Table 3. Pin Function Descriptions

Pin No. Mnemonic Function

1 NC N/A

2 VREF Reference Output Voltage of 2.5 V.

3 IREF Accepts (Sinks) Reference Current I

4 INPT

Accepts (Sinks) Photodiode Current I

.

REF

. Usually connected to photodiode anode such that photocurrent flows

PD

into INPT.

5 VSUM Guard Pin. Used to shield the INPT current line and for optional adjustment of the INPT and IREF node potential.

6, 7 VNEG Optional Negative Supply, VN. This pin is usually grounded; for details of usage, see the Applications section.

8 VPOS Positive Supply, ( VP – VN ) ≤ 11 V.

9 VLOG Output of the Logarithmic Front End.

10 BFIN Buffer Amplifier Noninverting Input.

11 SCAL Buffer Amplifier Inverting Input.

12 VOUT Buffer Output.

13–16 COMM Analog Ground.

Rev. 0 | Page 5 of 16

Loading...

Loading...