Wide Dynamic Range, High Speed,

Data Sheet

FEATURES

−11.5 dB to +20 dB gain range

0.5 dB ± 0.1 dB step size

150 Ω differential input and output

7.5 dB noise figure at maximum gain

OIP3 > 50 dBm at 200 MHz

−3 dB upper frequency bandwidth of 700 MHz

Multiple control interface options

Parallel 6-bit control interface (with latch)

Serial peripheral interface (SPI) (with fast attack)

Gain up/down mode

Wide input dynamic range

Low power mode option

Power-down control

Single 5 V supply operation

24-lead, 4 mm × 4 mm LFCSP package

APPLICATIONS

Differential ADC drivers

High IF sampling receivers

High output power IF amplification

Instrumentation

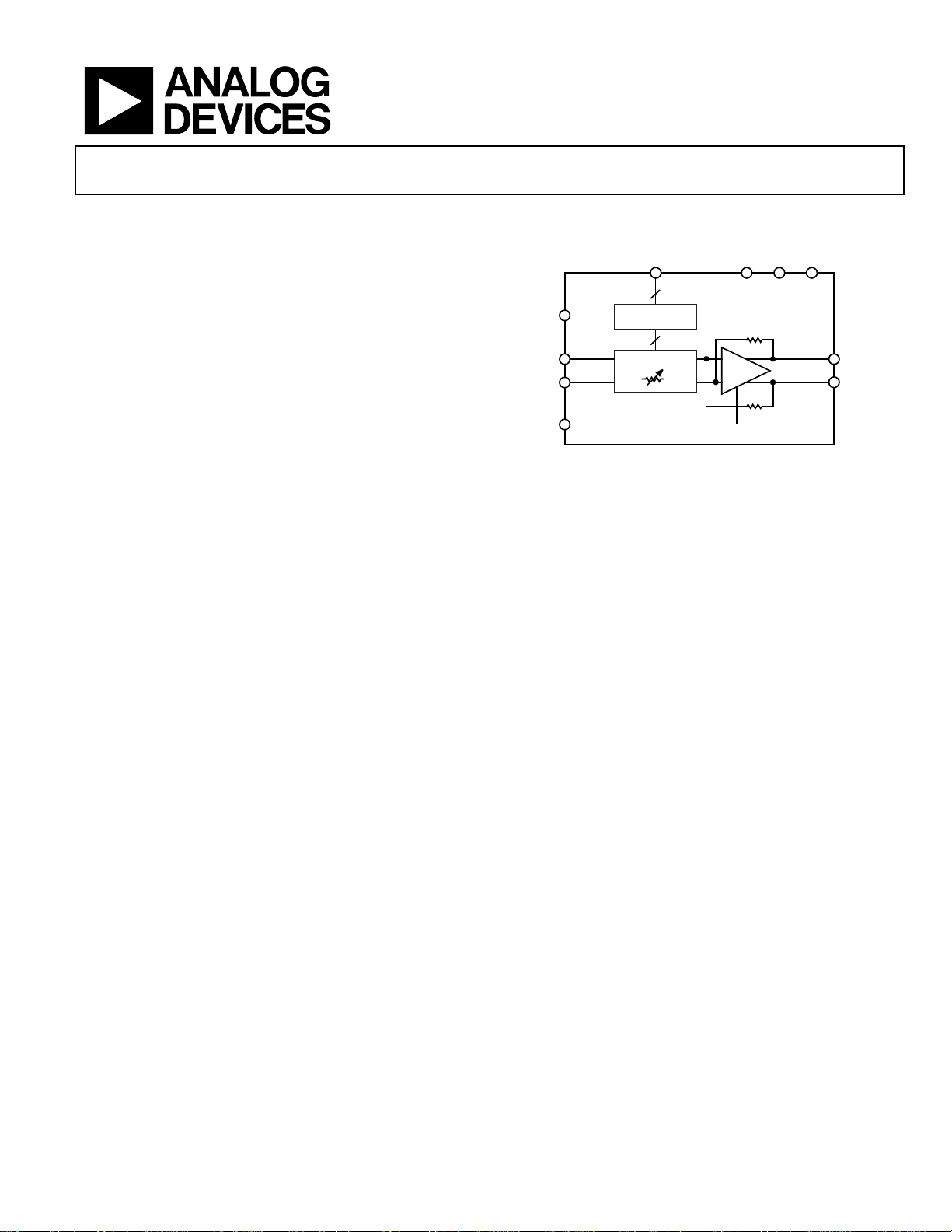

MODE0,

MODE1

VIN+

VIN–

PM

Digitally Controlled VGA

ADL5201

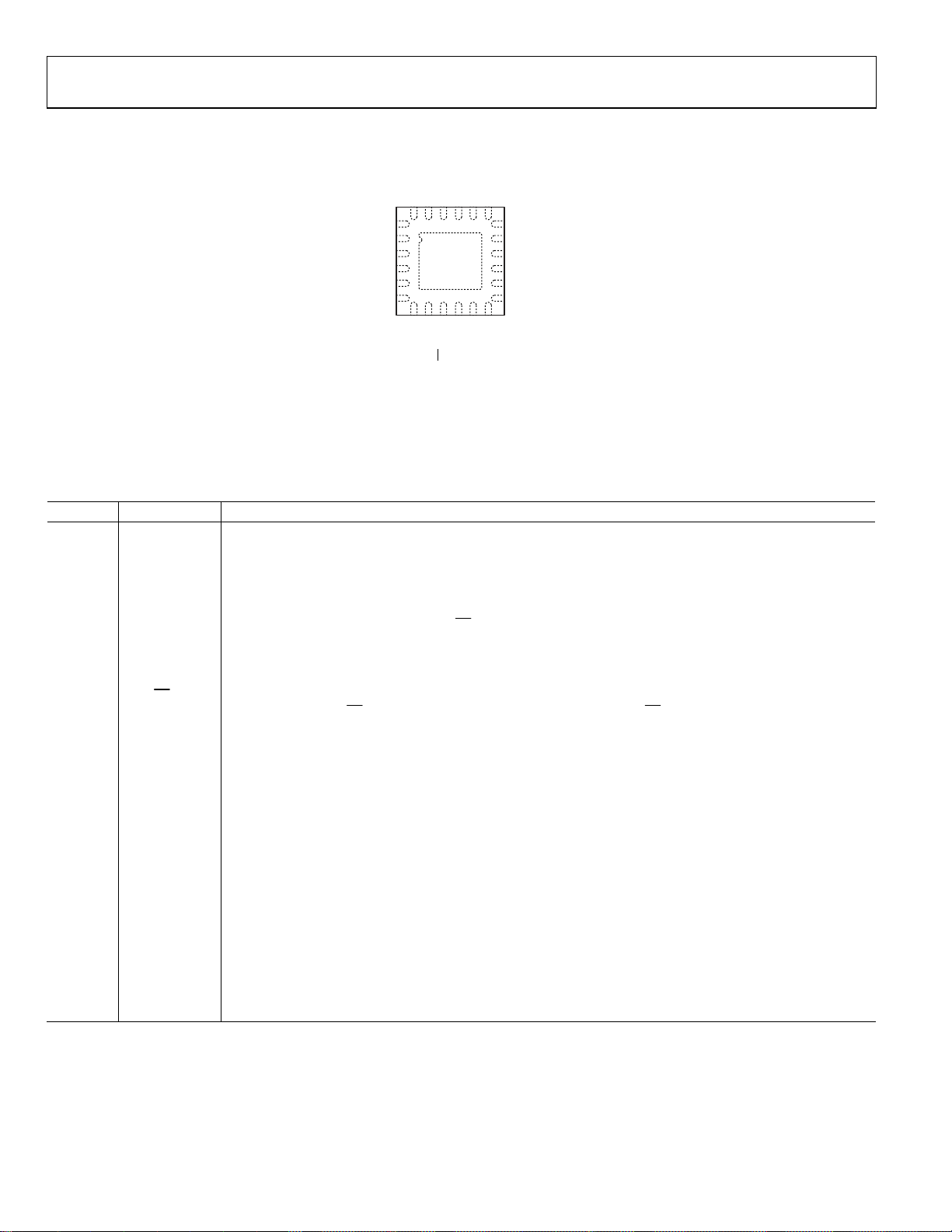

FUNCTIONAL BLOCK DIAGRAM

SPI WITH FA,

PARALLEL WITH LATCH,

UP/DOWN I NTERFACE VPOS GND PWUP

LOGIC

150Ω 150Ω

0dB TO 31.5dB

+20dB

ADL5201

Figure 1.

VOUT+

VOUT–

09388-001

GENERAL DESCRIPTION

The ADL5201 is a digitally controlled, variable gain, wide bandwidth amplifier that provides precise gain control, high IP3, and

low noise figure. The excellent distortion performance and high

signal bandwidth make the ADL5201 an excellent gain control

device for a variety of receiver applications. The ADL5201 also

incorporates a low power mode option that lowers the supply

current.

For wide input dynamic range applications, the ADL5201 provides

a broad 31.5 dB gain range with 0.5 dB resolution. The gain is

adjustable through multiple gain control interface options: parallel,

serial peripheral interface, and up/down.

Incorporating proprietary distortion cancellation techniques,

the ADL5201 achieves an output IP3 of greater than 47 dBm at

frequencies approaching 200 MHz for most gain settings.

The ADL5201 is powered on by applying the appropriate logic

level to the PWUP pin. The quiescent current of the ADL5201

is typically 80 mA in low power mode. When configured in high

performance mode for more demanding applications, the quiescent

current is 110 mA. When powered down, the ADL5201 consumes

less than 7 mA and offers excellent input-to-output isolation.

The gain setting is preserved during power-down.

Fabricated on an Analog Devices, Inc., high speed SiGe process,

the ADL5201 provides precise gain adjustment capabilities with

good distortion performance and low phase error. The ADL5201

amplifier comes in a compact, thermally enhanced, 24-lead,

4 mm × 4 mm LFCSP package and operates over the temperature

range of −40°C to +85°C.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADL5201 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram ..............................................................1

General Description......................................................................... 1

Revision History ...............................................................................2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics............................................. 7

Characterization and Test Circuits............................................... 14

Theory of Operation ......................................................................15

Digital Interface Overview ........................................................ 15

Parallel Digital Interface............................................................ 15

Serial Peripheral Interface (SPI)............................................... 15

Up/Down Interface .................................................................... 15

Circuit Description......................................................................... 17

Basic Structure............................................................................ 17

Input System ............................................................................... 17

Output Amplifier........................................................................ 17

Gain Control............................................................................... 17

Applications Information.............................................................. 18

Basic Connections...................................................................... 18

ADC Driving............................................................................... 18

Layout Considerations............................................................... 20

Evaluation Board............................................................................ 21

Evaluation Board Control Software......................................... 21

Schematics and Artwork ...........................................................22

Evaluation Board Configuration Options............................... 24

Outline Dimensions....................................................................... 26

Ordering Guide .......................................................................... 26

REVISION HISTORY

10/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

Data Sheet ADL5201

SPECIFICATIONS

VS = 5 V, TA = 25°C, RS = RL = 150 Ω at 100 MHz, high performance mode, 2 V p-p differential output, unless otherwise noted.

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Bandwidth V

Slew Rate

Input Return Loss (S11) 100 MHz

Output Return Loss (S22) 100 MHz

INPUT STAGE VIN+ and VIN− pins

Maximum Input Swing (Differential) Gain code = 111111

Differential Input Resistance

Common-Mode Input Voltage

CMRR Gain code = 000000

GAIN

Maximum Voltage Gain Gain code = 000000 20 dB

Minimum Voltage Gain Gain code = 111111 −11.5 dB

Gain Step Size 0.5 dB

Gain Flatness 30 MHz < fC < 200 MHz 0.285 dB

Gain Temperature Sensitivity Gain code = 000000

Gain Step Response For VIN = 0.2 V, gain code = 111111 to 000000

Gain Conformance Error Over 10 dB gain range

Phase Conformance Error Over 10 dB gain range

OUTPUT STAGE VOUT+ and VOUT− pins

Output Voltage Swing At P1dB, gain code = 000000

Differential Output Resistance Differential

NOISE/HARMONIC PERFORMANCE

46 MHz Gain code = 000000, high performance mode

Second Harmonic V

Third Harmonic V

Output IP3 (OIP3) V

70 MHz Gain code = 000000, high performance mode

Second Harmonic V

Third Harmonic V

Output IP3 (OIP3) V

140 MHz Gain code = 000000, high performance mode

Noise Figure

Second Harmonic V

Third Harmonic V

Output IP3 (OIP3) V

Output 1 dB Compression Point (OIP1dB)

300 MHz Gain code = 000000, high performance mode

Second Harmonic V

Third Harmonic V

Output IP3 (OIP3) V

< 2 V p-p (5.2 dBm)

OUT

700

5.5

−18.73

−18.8

MHz

V/ns

dB

dB

10.8

150

1.5

51.44

V p-p

Ω

V

dB

0.0089 dB/°C

15 ns

±0.03 dB

1.0 Degrees

10

150

V p-p

Ω

= 2 V p-p

OUT

= 2 V p-p

OUT

= 2 V p-p composite

OUT

−86

−104

50

dBc

dBc

dBm

= 2 V p-p

OUT

= 2 V p-p

OUT

= 2 V p-p composite

OUT

−91

−103

51

dBc

dBc

dBm

= 2 V p-p

OUT

= 2 V p-p

OUT

= 2 V p-p composite

OUT

7.5

−89

−97

51

19.8

dB

dBc

dBc

dBm

dBm

= 2 V p-p

OUT

= 2 V p-p

OUT

= 2 V p-p composite

OUT

−85

−90

50

dBc

dBc

dBm

Rev. 0 | Page 3 of 28

ADL5201 Data Sheet

Parameter Test Conditions/Comments Min Typ Max Unit

POWER-UP INTERFACE PWUP pin

Power-Up Threshold Minimum voltage to enable the device 1.4 V

Maximum voltage to enable the device 3.3 V

PWUP Input Bias Current 1 μA

GAIN CONTROL INTERFACE

VIH Minimum/maximum voltage for a logic high 1.4 3.3 V

VIL Maximum voltage for a logic low 0.8

Maximum Input Bias Current 1 μA

SPI TIMING LATCH, SCLK, SDIO, data pins

f

1/t

SCLK

tDH Data hold time 5 ns

tDS Data setup time 5 ns

tPW SCLK high pulse width 5 ns

POWER INTERFACE

Supply Voltage 4.5 5.5 V

Quiescent Current High performance mode

85°C

Low power mode

85°C

Power-Down Current PWUP low

20 MHz

SCLK

110 mA

120 mA

80 mA

95 mA

7 mA

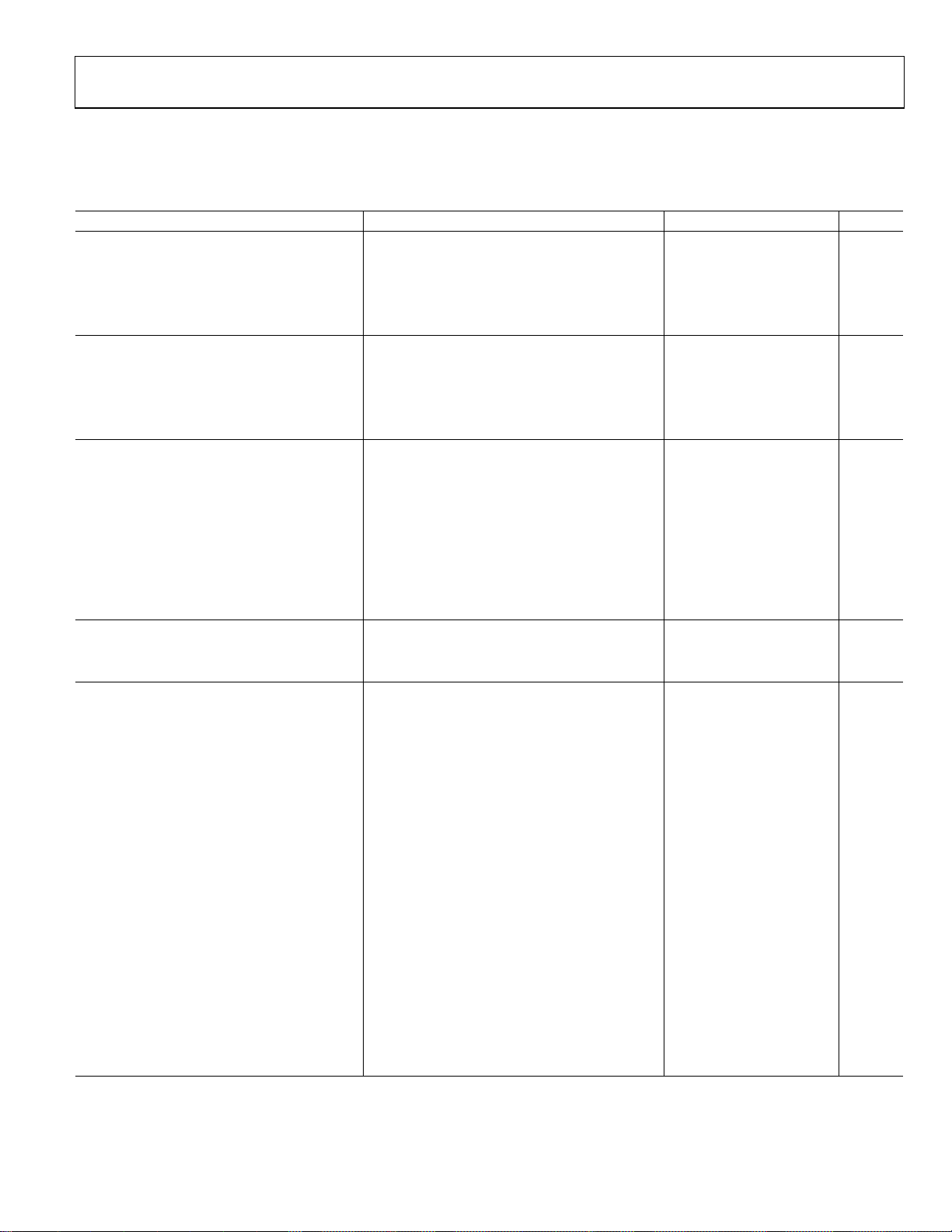

TIMING DIAGRAMS

SCLK

t

DS

CS

tDSt

DH

SDIO

DNC DNC DNC DNC DNC DNC DNC R/W FA1 FA0 D5 D4 D3 D2 D1 D0

t

SCLK

t

PW

Figure 2. SPI Interface Read/Write Mode Timing Diagram

UPDN_DAT

UPDN_CLK

t

PW

DNUP

t

DS

Figure 3. Up/Down Mode Timing Diagram

LATCH

t

DH

09388-002

t

t

DS

DS

RESET

t

DH

09388-003

A5 TO A0

t

DH

Figure 4. Parallel Mode Timing Diagram

Rev. 0 | Page 4 of 28

09388-104

Data Sheet ADL5201

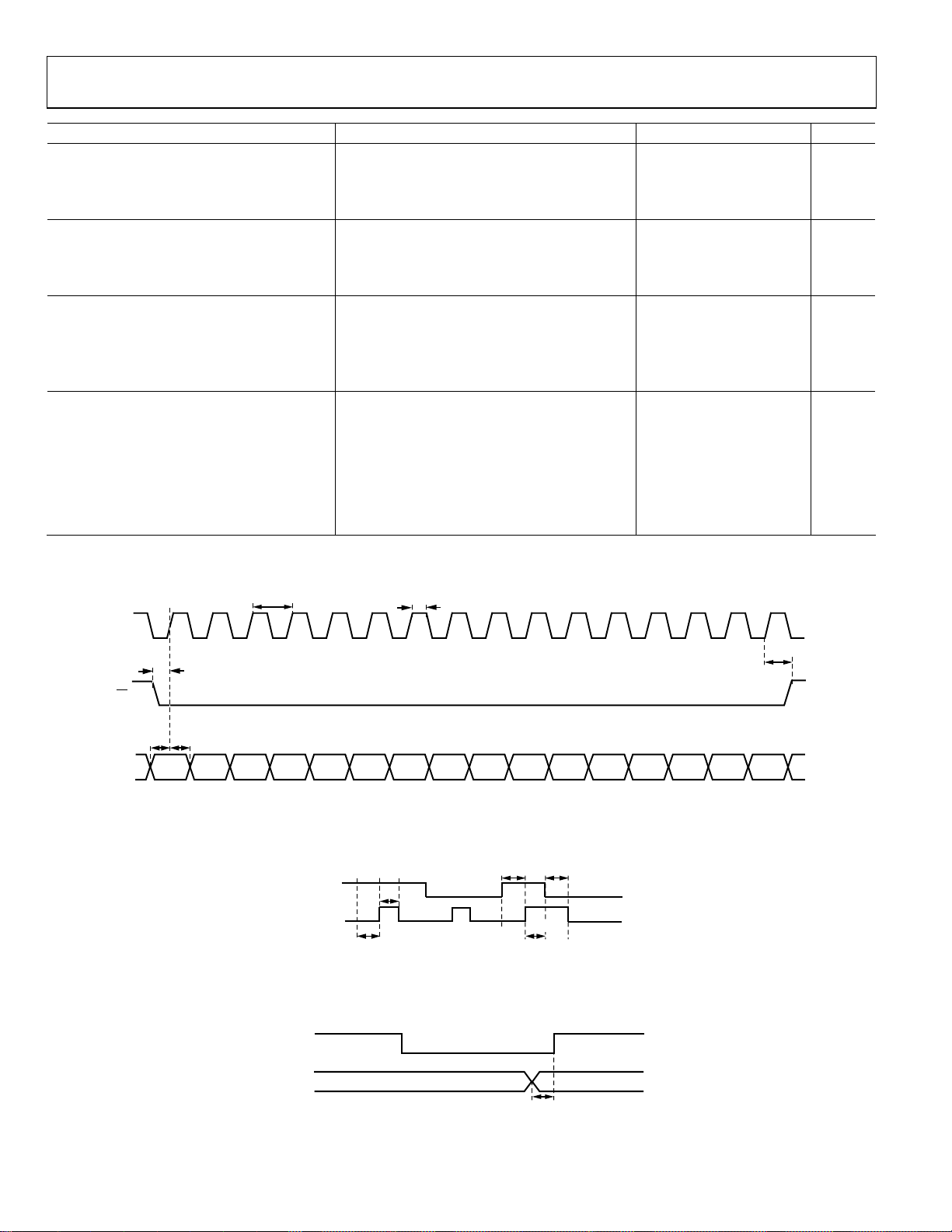

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage, VPOS 5.5 V

PWUP, A0 to A5, MODE0, MODE1, PM, LATCH 3.6 V

Input Voltage, VIN+ and VIN− +3.6 V to −1.2 V

Internal Power Dissipation 676.5 mW

θJA (Exposed Paddle Soldered Down) 37.16°C/W

θJC (at Exposed Paddle) 2.29°C/W

Maximum Junction Temperature 140°C

Operating Temperature Range –40°C to +85°C

Storage Temperature Range –65°C to +150°C

Lead Temperature (Soldering, 60 sec) 240°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 28

ADL5201 Data Sheet

P

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VPOS

VPOS

23

24

1

GND

2

VIN+

3

VIN–

GND

MODE1

MODE0

NOTES

1. THE EXPOSED PADDLE (EP) MUST BE CONNECTED TO

A LOW I MPEDANCE GROUND PAD.

4

5

6

ADL5201

TOP VIEW

(Not to Scale)

8

7

SDIO/A5

SCLK/A4

Figure 5. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1, 4, EP GND Ground. The exposed paddle (EP) must be connected to a low impedance ground pad.

2 VIN+ Positive Input.

3 VIN− Negative Input.

5 MODE1 MSB for Mode Control. With the MODE0 pin, selects parallel, SPI, or up/down interface mode.

6 MODE0 LSB for Mode Control. With the MODE1 pin, selects parallel, SPI, or up/down interface mode.

7 SDIO/A5

Serial Data Input/Output (SDIO). When CS

Bit 5 for Parallel Gain Control Interface (A5).

8 SCLK/A4

Serial Clock Input in SPI Mode (SCLK).

Bit 4 for Parallel Gain Control Interface (A4).

9

/A3 MSB for Gain Step Size Control in Up/Down Mode (GS1).

GS1/CS

SPI Interface Select (CS). When serial mode is enabled, a logic low (0 V ≤ CS ≤ 0.8 V) enables the SPI interface.

Bit 3 for Parallel Gain Control Interface (A3).

10 GS0/FA/A2

LSB for Gain Step Size Control in Up/Down Mode (GS0).

Fast Attack (FA). In serial mode, a logic high (1.4 V ≤ FA ≤ 3.3 V) attenuates according to the FA setting in the SPI

word. Bit 2 for Parallel Gain Control Interface (A2).

11 UPDN_CLK/A1

Clock Interface for Up/Down Function (UPDN_CLK).

Bit 1 for Parallel Gain Control Interface (A1).

12 UPDN_DAT/A0

Data Pin for Up/Down Function (UPDN_DAT).

Bit 0 for Parallel Gain Control Interface (A0).

13 LATCH

A logic low (0 V ≤ LATCH ≤ 0.8 V) allows gain changes. A logic high (1.4 V ≤ LATCH ≤ 3.3 V) disallows gain

changes.

14, 16 VOUT+ Positive Output.

15, 17 VOUT− Negative Output.

18, 21,

VPOS Positive Power Supply.

22, 23, 24

19 PWUP Power-Up Pin. A logic high (1.4 V ≤ PWUP ≤ 3.3 V) enables the part.

20 PM

Performance Mode. A logic low (0 V ≤ PM ≤ 0.8 V) enables high performance mode. A logic high (1.4 V ≤ PM ≤ 3.3 V)

enables low power mode.

U

PM

PW

VPOS

VPOS

21

20

22

19

18

VPOS

17

VOUT–

16

OUT+

V

15

VOUT–

14

VOUT+

H

LATC

13

9

11

12

10

GS0/FA/A2

GS1/CS/A3

PDN_CLK/A1

UPDN_DAT/A0

U

09388-004

is pulled low, SDIO is used for reading and writing to the SPI port.

Rev. 0 | Page 6 of 28

Data Sheet ADL5201

TYPICAL PERFORMANCE CHARACTERISTICS

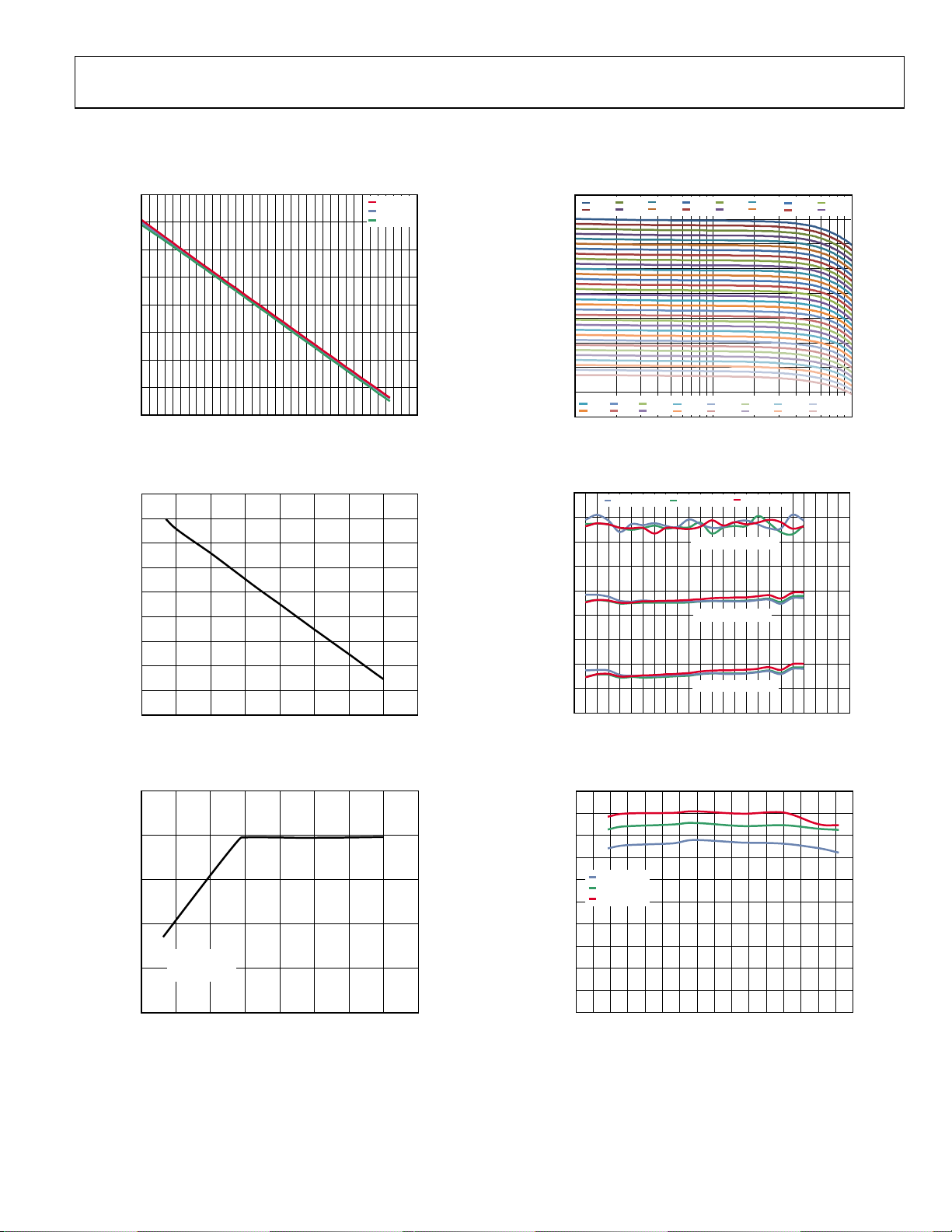

VS = 5 V, TA = 25°C, RS = RL = 150 Ω at 200 MHz, high performance mode, 2 V p-p differential output, unless otherwise noted.

25

20

15

10

5

GAIN (dB)

0

–5

–10

–15

0 10203040506070

GAIN CODE

46MHz

140MHz

300MHz

Figure 6. Gain vs. Gain Code at 46 MHz, 140 MHz, and 300 MHz

09388-005

25

20dB

19dB

20

15

10

5

0

GAIN (dB)

–5

–10

–15

4dB

3dB

–20

10 100 1000

2dB

1dB

18dB

17dB

0dB

–1dB

16dB

14dB

15dB

13dB

–2dB

–4dB

–3dB

–5dB

FREQUENCY (MHz)

12dB

11dB

–6dB

–7dB

10dB

9dB

–8dB

–9dB

8dB

7dB

Figure 9. Gain vs. Frequency Response (Every 1 dB Step)

6dB

5dB

–10dB

–11dB

09388-008

45

40

35

30

25

20

15

NOISE F IGURE (d B)

10

5

0

–15 –10 –5 0 5 10 15 20 25

PROGRAMMED G AIN (dB)

Figure 7. Noise Figure vs. Programmed Gain at 140 MHz

25

20

15

10

OP1dB (dBm)

INPUT

MAX RATINGS

5

BOUNDARY

0

–15 –10 –5 0 5 10 15 20 25

PROGRAMMED GAIN (dB)

Figure 8. OP1dB vs. Programmed Gain at 140 MHz

45

40

35

30

25

20

15

NOISE FIGURE (d B)

10

5

0

09388-006

TA = –40°C TA = +25°C TA = +85°C

MIN GAIN (–11. 5dB)

MID GAIN (+5dB)

MAX GAIN (+20dB)

0 100 200 300 400 500 600

FREQUENCY (MHz)

09388-009

Figure 10. Noise Figure vs. Frequency at Max, Mid, and Min Gain Outputs

20

18

16

14

TA = –40°C

12

T

= +25°C

A

T

= +85°C

A

10

8

OP1dB (dBm)

6

4

2

0

0 50 100 150 200 250 300 350 400

09388-007

FREQUENCY (MHz)

09388-010

Figure 11. OP1dB vs. Frequency at Maximum Gain, Three Temperatures

Rev. 0 | Page 7 of 28

ADL5201 Data Sheet

–

–

60

–11.5dB

0dB

+10dB

+20dB

55

50

45

OIP3 (dBm)

40

35

30

0 50 100 150 200 250 300 350 400

FREQUENCY (MHz)

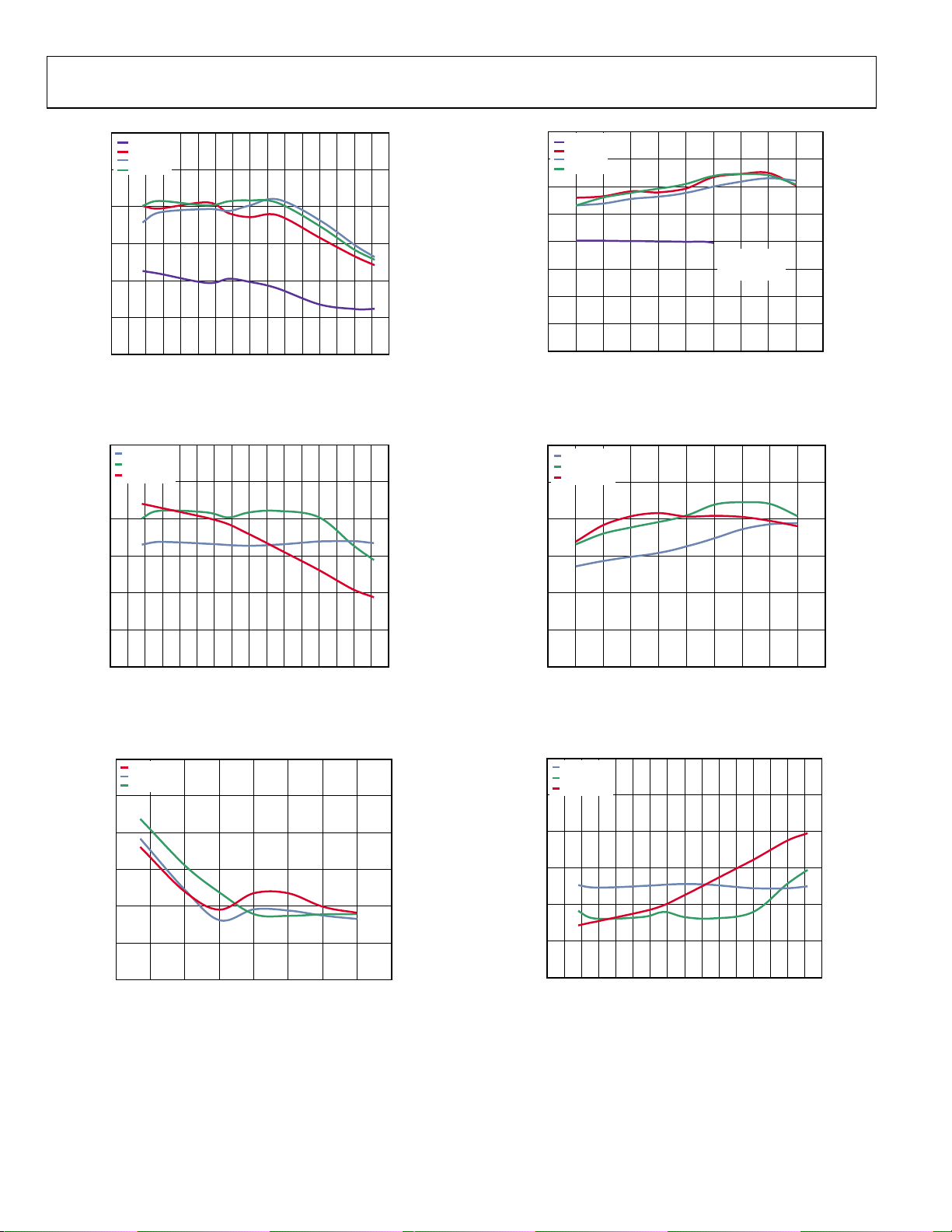

Figure 12. Output Third-Order Intercept vs. Frequency

at Four Gain Codes

60

TA = –40°C

= +25°C

T

A

= +85°C

T

A

55

50

45

OIP3 (dBm)

40

09388-011

60

–11.5dB

0dB

+10dB

55

+20dB

50

45

40

OIP3 (dBm)

35

30

25

20

–4 –3 –2 –1 0 1 2 3 4 5 6

P

(dBm)

OUT

INPUT

MAX RATINGS

BOUNDARY

Figure 15. Output Third-Order Intercept vs. Power at Four Gain Codes,

Frequency = 140 MHz at 2 V p-p Composite

60

TA = –40°C

T

= +25°C

A

T

= +85°C

A

55

50

45

OIP3 (dBm)

40

09388-014

35

30

0 50 100 150 200 250 300 350 400

FREQUENCY ( MHz)

Figure 13. Output Third-Order Intercept vs. Frequency,

Three Temperatures at 2 V p-p Composite

60

46MHz

140MHz

300MHz

–70

–80

–90

IMD3 (dBc)

–100

–110

–120

–15 –10 –5 0 5 10 15 20 25

PROGRAMME D GAIN (dB)

Figure 14. Two-Tone Output IMD3 vs. Programmed Gain

at 46 MHz, 140 MHz, and 300 MHz

35

30

–4 –3 –2 –1 0 1 2 3 4 5 6

P

(dBm)

09388-012

OUT

09388-015

Figure 16. Output Third-Order Intercept vs. Power, Frequency = 140 MHz,

Three Temperatures

60

TA = –40°C

= +25°C

T

A

= +85°C

T

A

–70

–80

–90

IMD3 (dBc)

–100

–110

–120

0 50 100 150 200 250 300 350 400

09388-013

FREQUENCY (MHz)

09388-016

Figure 17. Two-Tone Output IMD3 vs. Frequency,

Three Temperatures

Rev. 0 | Page 8 of 28

Data Sheet ADL5201

–

–

–

–

–

–

–

–50

–11.5dB

0dB

–60

+10dB

+20dB

–70

–80

–90

–100

–110

–120

–130

HARMONIC DI STORTI ON HD2 (dBc)

–140

–150

0 50 100 150 200 250 300 350

FREQUENCY (MHz)

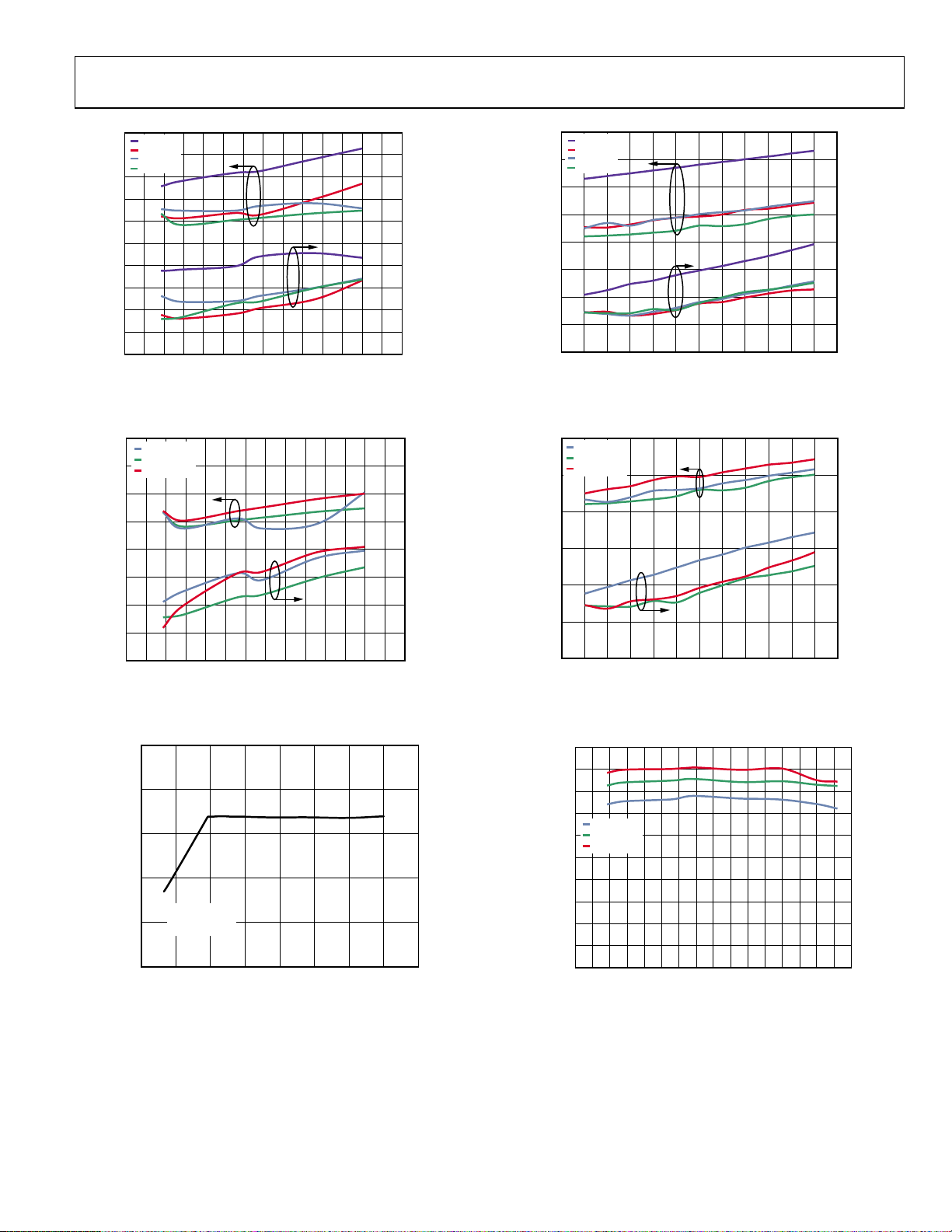

Figure 18. Harmonic Distortion vs. Frequency at Four Gain Codes

60

TA = –40°C

T

= +25°C

A

–70

T

= +85°C

A

–80

–90

–100

20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

40

–50

–60

–70

–80

HARMONIC DI STORTI ON HD3 (dBc)

60

–11.5dB

0dB

+10dB

–70

+20dB

–80

–90

–100

–110

–120

HARMONIC DIS TORTION HD2 (d Bc)

–130

–140

–6–5–4–3–2–10123456

P

(dBm)

09388-017

OUT

40

–50

–60

–70

–80

–90

–100

–110

–120

HARMONIC DIS TORTION HD3 (d Bc)

09388-020

Figure 21. Harmonic Distortion vs. Power at Four Gain Codes,

Frequency = 140 MHz

60

–70

–80

–90

–90

–100

–110

80

TA = –40°C

= +25°C

T

A

= +85°C

T

A

–110

–120

HARMONIC DIS TORTION HD2 (dBc)

–130

–140

0 50 100 150 200 250 300 350

FREQUENCY (MHz)

–90

–100

–110

–120

Figure 19. Harmonic Distortion vs. Frequency, Three Temperatures

25

20

15

10

OP1dB (dBm)

INPUT

MAX RATING S

5

BOUNDARY

0

–15 –10 –5 0 5 10 15 20 25

PROGRAMMED GAIN (dB)

Figure 20. OP1dB vs. Programmed Gain at 140 MHz, Low Power Mode

HARMONIC DIS TORTION HD3 (dBc)

–120

–130

HARMONIC DIS TORTIO N HD2 (dBc)

–140

–6 –5 –4 –3 –2 –1 0 1 2 3 4 5 6

P

(dBm)

09388-018

OUT

–100

–110

–120

HARMONIC DIS TORTIO N HD3 (dBc)

09388-021

Figure 22. Harmonic Distortion vs. Power, Frequency = 140 MHz,

Three Temperatures

20

18

16

14

TA = –40°C

12

T

= +25°C

A

T

= +85°C

A

10

8

OP1dB (dBm)

6

4

2

0

0 50 100 150 200 250 300 350 400

09388-019

FREQUENCY (MHz)

09388-022

Figure 23. OP1dB vs. Frequency at Maximum Gain, Three Temperatures,

Low Power Mode

Rev. 0 | Page 9 of 28

Loading...

Loading...