Programmable High-g Digital

A

FEATURES

Dual-axis sensing, ±70 g, ±37 g

14-bit resolution

Impact peak-level sample-and-hold

RSS output

Programmable event recorder

400 Hz double-pole Bessel sensor response

Digitally controlled sensitivity and bias

Digitally controlled sample rate, up to 4096 SPS

Programmable condition monitoring alarms

Auxiliary digital I/O

Digitally activated self-test

Embedded temperature sensor

Programmable power management

SPI-compatible serial interface

Auxiliary 12-bit ADC input and DAC output

Single-supply operation: +3.0 V to +3.6 V

4000 g powered shock survivability

APPLICATIONS

Crash or impact detection

Condition monitoring of valuable goods

Safety, shut-off sensing

Impact event recording

Security sensing, tamper detection

Impact Sensor and Recorder

ADIS16204

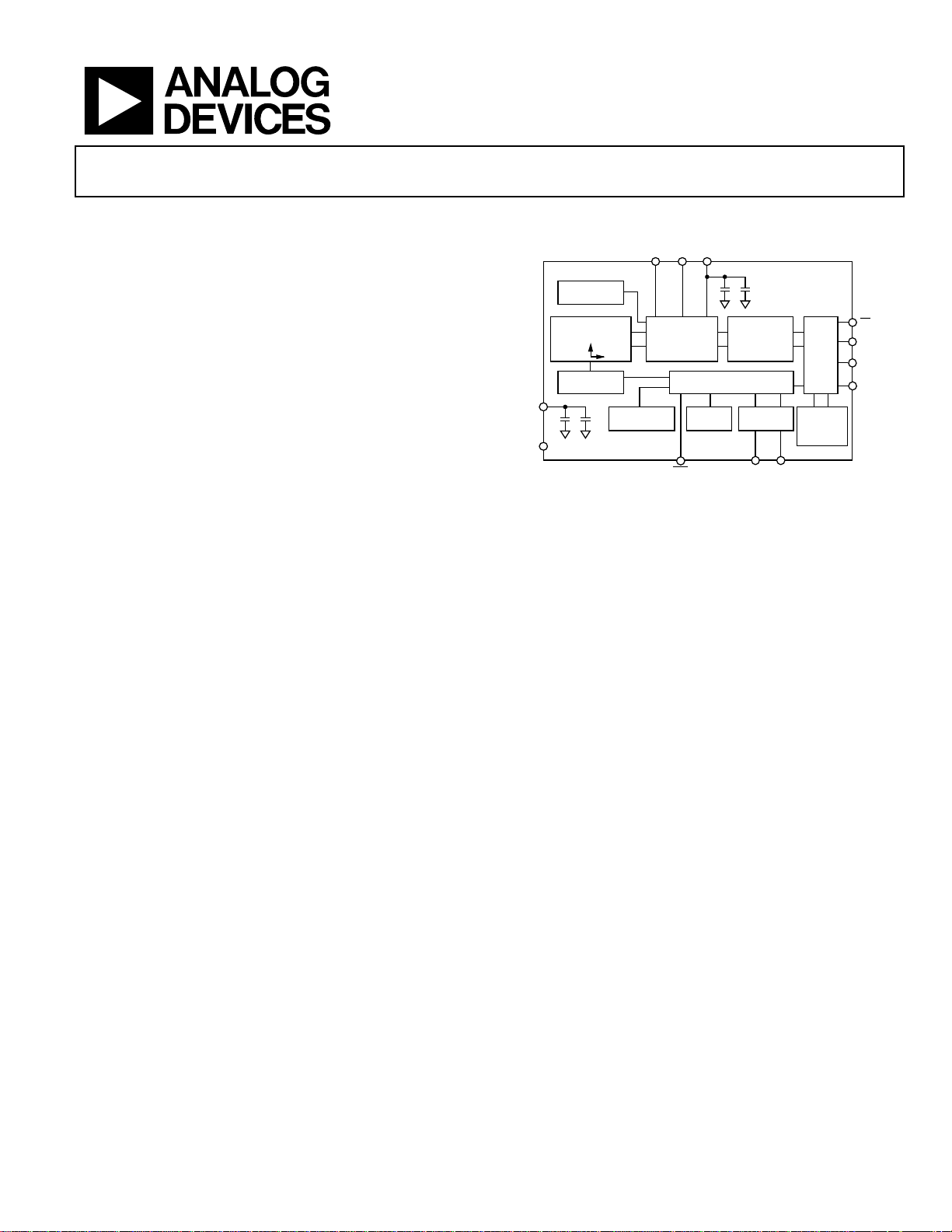

FUNCTIONAL BLOCK DIAGRAM

UX

AUX

ADC

DAC

VREF

DIGITAL

AUXILIARY

I/O

ADIS16204

SPI

PORT

EVENT

CAPTURE

BUFFER

MEMORY

VDD

COM

TEMPERATURE

SENSOR

INERTIAL

MEMS

SENSOR

SELF-TEST

CONDITIONING

CONVERSION

POWER

MANAGEMENT

SIGNAL

ALARMS

PROCESSING

DIGITAL

CONTROL

AND

RST DIO1 DIO2

Figure 1.

CS

SCLK

DIN

DOUT

06448-001

GENERAL DESCRIPTION

The ADIS16204 is a fully-contained programmable impact

sensor in a single compact package enabled by the Analog

Devices, Inc. iSensor™ integration. By enhancing the Analog

Devices iMEMS® sensor technology with an embedded signal

processing solution, the ADIS16204 provides tunable digital

sensor data in a convenient format that can be accessed using

a serial peripheral interface (SPI). The SPI provides access to

measurements for dual-axis linear acceleration, a root sum

square (RSS) of both axes, temperature, power supply, an

auxiliary analog input, and an event capture buffer memory. Easy

access to digital sensor data provides users with a system-ready

device, reducing development time, cost, and program risk.

Unique characteristics of the end system are accommodated

easily through several built-in features, such as a single command

in-system bias null/offset calibration, along with convenient

sample rate control.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The ADIS16204 offers the following embedded features, which

eliminate the need for external circuitry and provide a simplified

system interface:

• Peak sample-and-hold

• Programmable event recording (dual, 1K × 16 bit)

• RSS output (total shock in the XY plane)

• Configurable alarms

• Auxiliary 12-bit ADC and DAC

• Configurable digital I/O port

• Digital self-test function

The ADIS16204 offers two power management features for

managing system-level power dissipation: low power mode

and a configurable shutdown feature.

The ADIS16204 is available in a 9.2 mm × 9.2 mm × 3.9 mm

laminate-based land grid array (LGA) package with a temperature range of −40°C to +105°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

ADIS16204

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Timing Specifications .................................................................. 5

Absolute Maximum Ratings ............................................................ 6

ESD Caution .................................................................................. 6

Pin Configuration and Function Descriptions ............................. 7

Recommended Pad Geometry .................................................... 7

Typical Performance Characteristics ............................................. 8

Theory of Operation ...................................................................... 10

Overview ...................................................................................... 10

Acceleration Sensor .................................................................... 10

Temperature Sensor ................................................................... 10

REVISION HISTORY

10/07—Rev. 0 to Rev. A

Changes to Power Supply Current Specification .......................... 4

Changes to Overview Section ....................................................... 10

6/07—Revision 0: Initial Version

Impact/Shock Response ............................................................ 10

Auxiliary ADC Function ........................................................... 11

Basic Operation .............................................................................. 12

Serial Peripheral Interface ......................................................... 12

Data Output Register Access .................................................... 13

Programming and Control ............................................................ 14

Control Register Overview ....................................................... 14

Control Register Structure ........................................................ 14

Global Commands ..................................................................... 15

Calibration ................................................................................... 15

Operational Control ................................................................... 16

Status and Diagnostics ............................................................... 17

Alarm Detection and Event Capture ....................................... 18

Second-Level Assembly ................................................................. 21

Outline Dimensions ....................................................................... 22

Ordering Guide .......................................................................... 22

Rev. A | Page 2 of 24

ADIS16204

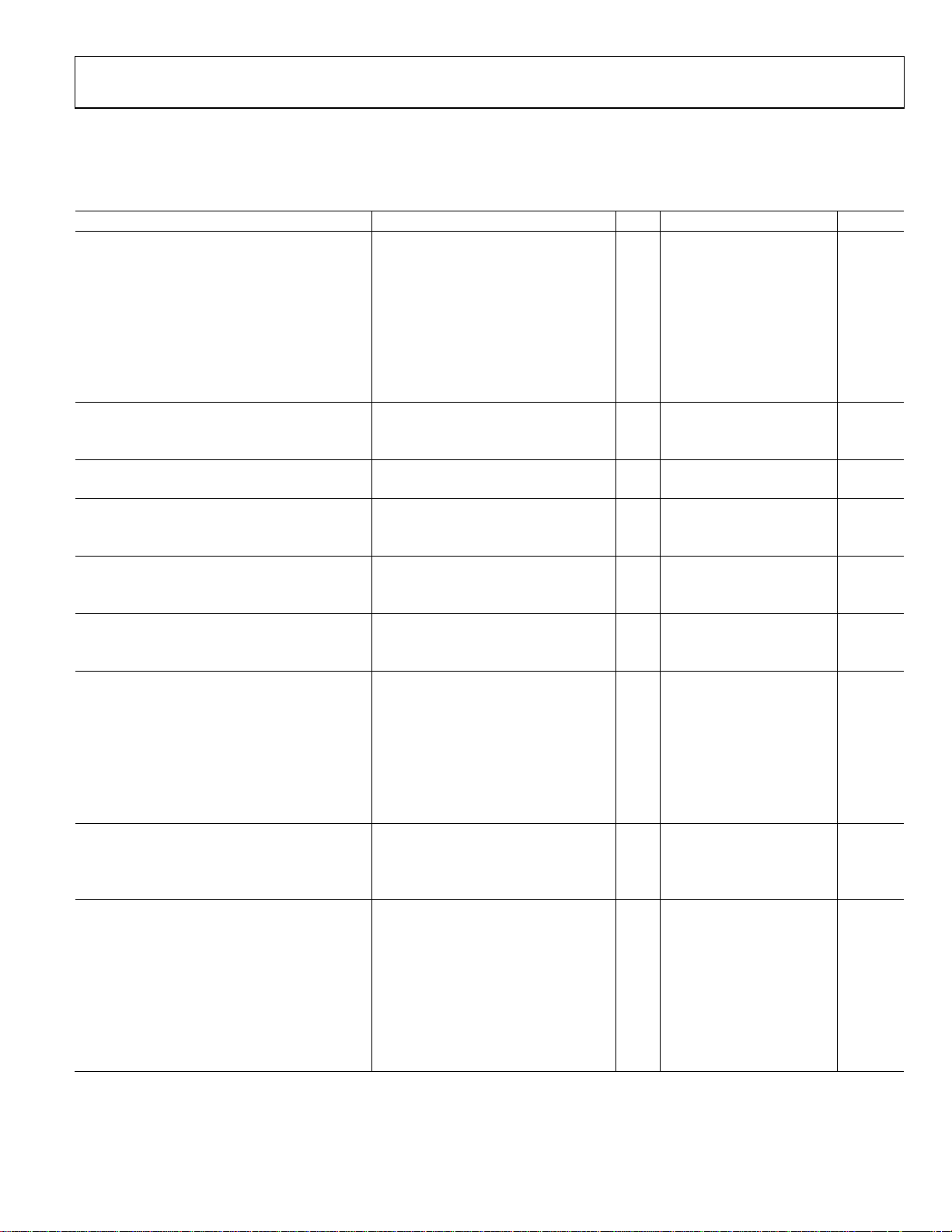

SPECIFICATIONS

TA = −40oC to +105°C, VDD = 3.3 V, unless otherwise noted.

Table 1.

Parameter Conditions Axis Min Typ Max Unit

ACCELEROMETER

Output Full-Scale Range X ±70

Y ±37

Sensitivity X 17.125 mg/LSB

Y 8.407 mg/LSB

Nonlinearity 0.2 %

Sensor-to-Sensor Alignment Error 0.1 Degrees

Cross-Axis Sensitivity −5 +5 %

Resonant Frequency 24 kHz

OFFSET

Zero-g Output1 X 0.2

Y 0.2

NOISE

Noise Density 10 Hz − 400 Hz, no postfiltering 1.8 mg/√Hz

FREQUENCY RESPONSE

Sensor Bandwidth (−3 dB) 2-pole Bessel 360 400 440 Hz

Temperature Drift |25°C − T

ACCELEROMETER SELF-TEST STATE2

Output Change When Active At 25°C X 254 LSB

Output Change When Active Y 518 LSB

TEMPERATURE SENSOR

Output at 25°C 1278 LSB

Scale Factor −2.13 LSB/°C

ADC INPUT

Resolution 12 Bits

Integral Nonlinearity (INL) ±2 LSB

Differential Nonlinearity (DNL) ±1 LSB

Offset Error ±4 LSB

Gain Error ±2 LSB

Input Range 0 2.5 V

Input Capacitance During acquisition 20 pF

ON-CHIP VOLTAGE REFERENCE 2.5 V

Accuracy At 25°C −10 +10 mV

Reference Temperature Coefficient ±40 ppm/oC

Output Impedance 70 Ω

DAC OUTPUT 5 kΩ/100 pF to GND

Resolution 12 Bits

Relative Accuracy For Code 101 to Code 4095 4 LSB

Differential Nonlinearity (DNL) 1 LSB

Offset Error ±5 mV

Gain Error ±0.5 %

Output Range 0 to 2.5 V

Output Impedance 2 Ω

Output Settling Time 10 μs

MIN

| or |T

− 25°C| 2 Hz

MAX

g

g

g

g

Rev. A | Page 3 of 24

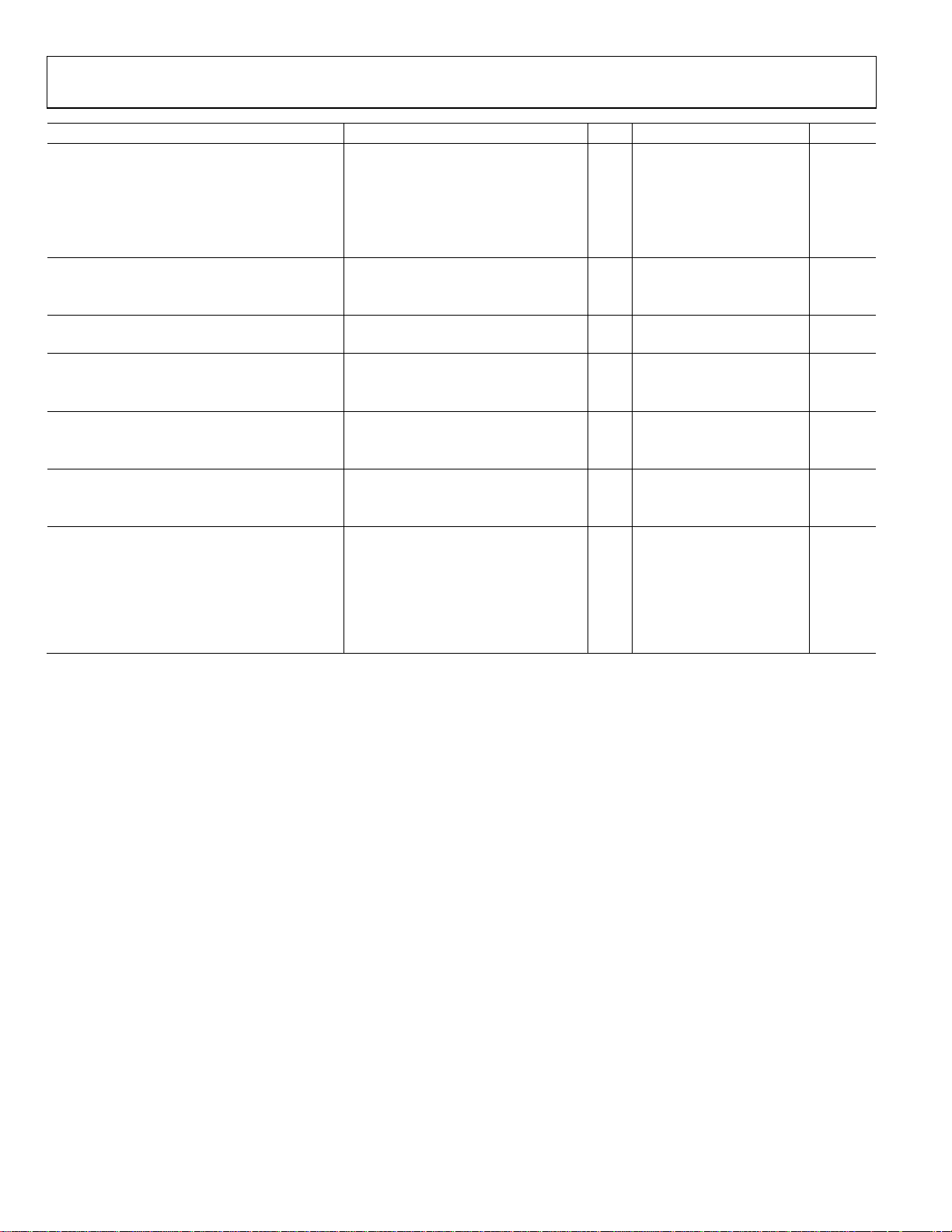

ADIS16204

Parameter Conditions Axis Min Typ Max Unit

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Logic 1 Input Current, I

Logic 0 Input Current, I

3

2.0 V

INH

0.8 V

INL

VIH = VDD ±0.2 ±1 µA

INH

V

INL

= 0 V −40 −60 A

IL

Input Capacitance, CIN 10 pF

DIGITAL OUTPUTS

Output High Voltage, VOH I

Output Low Voltage, VOL I

= 1.6 mA 2.4 V

SOURCE

= 1.6 mA 0.4 V

SINK

SLEEP TIMER

Timeout Period

4

0.5 128 Seconds

START-UP TIME

Initial 130 ms

Reset recovery 2.5 ms

FLASH MEMORY

Endurance

Data Retention

5

6

20,000 Cycles

TJ = 85°C 20 Years

CONVERSION RATE

Maximum Throughput Rate 4096 SPS

Minimum Throughput Rate 2.066 SPS

POWER SUPPLY

Operating Voltage Range, VDD 3.0 3.3 3.6 V

Power Supply Current

Normal mode, SMPL_PRD ≥ 0x08

12 15 mA

(fS ≤ 910 Hz), at 25°C

Fast mode, SMPL_PRD ≤ 0x07

≥ 1024 Hz), at 25°C

(f

S

37 43 mA

Sleep mode, at 25°C 150 µA

1

Note that gravity can impact this number; zero-g condition assumes both axes oriented normal to the earth’s gravity.

2

Self-test response changes as the square of VDD.

3

Note that the inputs are +5 V tolerant.

4

Guaranteed by design.

5

Endurance is qualified as per JEDEC Standard 22, Method A117 and measured at −40°C, +25°C, +85°C, and +105°C.

6

Retention lifetime equivalent at junction temperature (TJ), 55°C as per JEDEC Standard 22, Method A117. Retention lifetime decreases with junction temperature.

Rev. A | Page 4 of 24

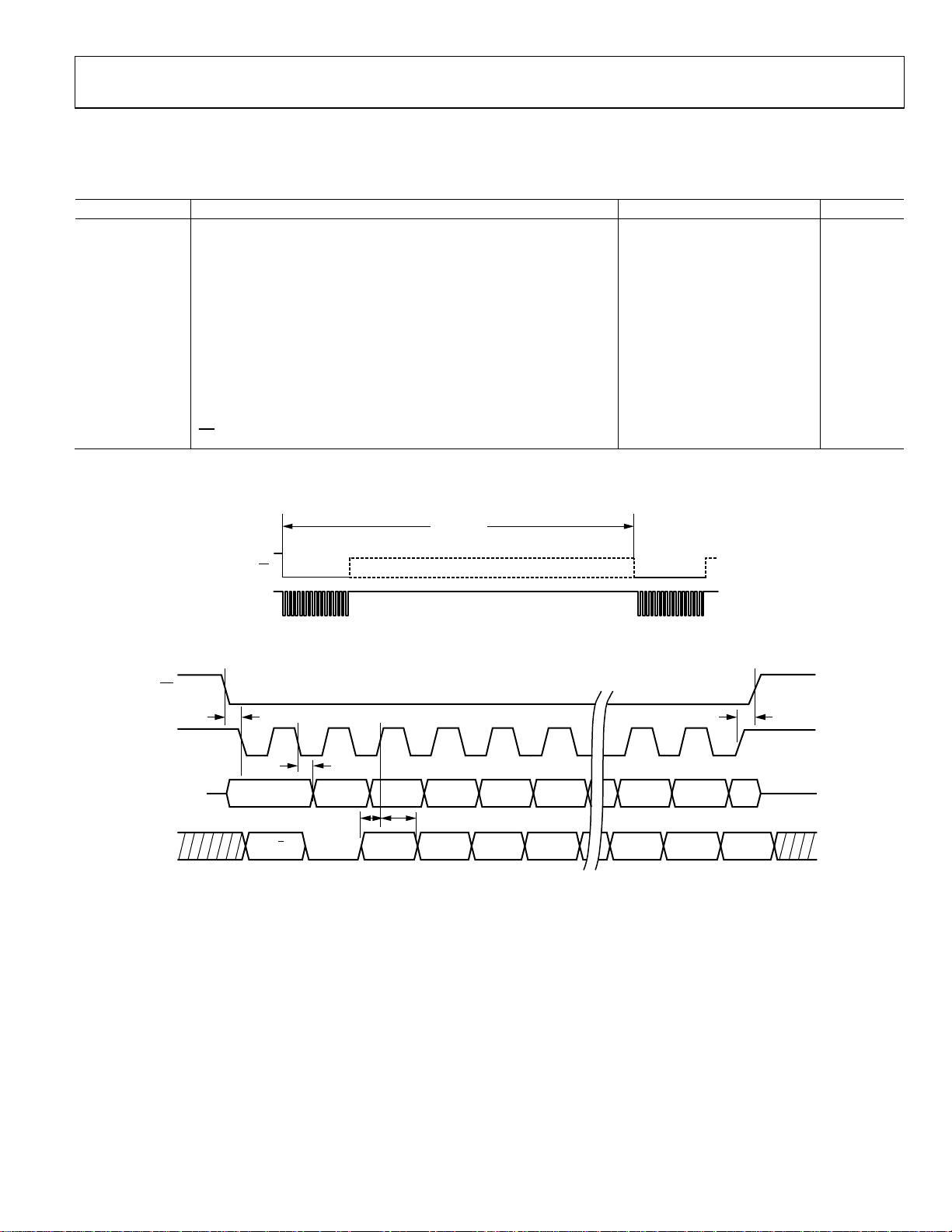

SCLK

ADIS16204

TIMING SPECIFICATIONS

TA = +25°C, VCC = +3.3 V, unless otherwise noted.

Table 2.

Parameter Description Min1 Typ Max1 Unit

f

Fast mode2 0.01 2.5 MHz

SCLK

Normal mode2 0.01 1.0 MHz

t

Chip select period, fast mode

DATARATE

Chip select period, normal mode2 100 μs

t

CSHIGH

Chip select high 1/f

tCS Chip select to clock edge 48.8 ns

t

Data output valid after SCLK edge 100 ns

DAV

t

Data input setup time before SCLK rising edge 24.4 ns

DSU

t

Data input hold time after SCLK rising edge 48.8 ns

DHD

tDF Data output fall time 5 12.5 ns

tDR Data output rise time 5 12.5 ns

t

SFS

1

Guaranteed by design; typical specifications are not tested or guaranteed.

2

Based on sample rate selection.

high after SCLK edge

CS

2

40 μs

SCLK

5 ns

t

DATARATE

CS

06448-002

Figure 2. SPI Chip Select Timing

CS

SCLK

DOUT

DIN

t

CS

123456 1516

t

DAV

MSB DB14

t

W/R A5 A4 A3 A2

DB13 DB12 DB10DB11 DB2 LSBDB1

t

DSU

DHD

D2

D1 LSB

t

SFS

06448-003

Figure 3. SPI Timing

(Utilizing SPI Settings Typically Identified as Phase = 1, Polarity = 1)

Rev. A | Page 5 of 24

ADIS16204

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Acceleration (Any Axis, Unpowered, 0.5 ms) 4000 g

Acceleration (Any Axis, Powered, 0.5 ms) 4000 g

VCC to COM −0.3 V to +6.0 V

Digital Input/Output Voltage to COM −0.3 V to +5.5 V

Analog Inputs to COM −0.3 V to +3.5 V

Operating Temperature Range −40°C to +125°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. A | Page 6 of 24

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

ADC

AUX

VDD

13

12

11

10

SCLK

DOUT

DIN

16

1

X

2

3

COM

VREF

15 14

Y

ADIS16204

TOP

VIEW

(Not to Scale)

ADIS16204

AUX DAC

NC

NC

4

CS

56

NC = NO CONNECT

NOTES

1. PINS ARE NOT VISIBLE FROM THE TOP VIEW. THEY ARE

SHOWN FO R CONVENIENCE IN CRE ATING CAD LIBRARY

PARTS.

DIO1

7

8

NC

DIO2

NC

Figure 4. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Type1Description

1 SCLK I SPI, Serial Clock.

2 DOUT O SPI, Data Out.

3 DIN I SPI, Data In.

4

CS

I SPI, Chip Select, Active Low.

5, 6 DIO1, DIO2 I/O Multifunction Digital Input/Output Pins.

7, 8, 10, 11 NC – No Connect.

9

RST

I Reset, Active Low. This input resets the embedded microcontroller to a known state.

12 AUX DAC O Auxiliary DAC Analog Voltage Output.

13 VDD S +3.3 V Power Supply.

14 AUX ADC I Auxiliary ADC Analog Input Voltage.

15 VREF O Precision Reference Output.

16 COM S Common. Reference point for all circuitry.

1

S = supply; O = output; I = input.

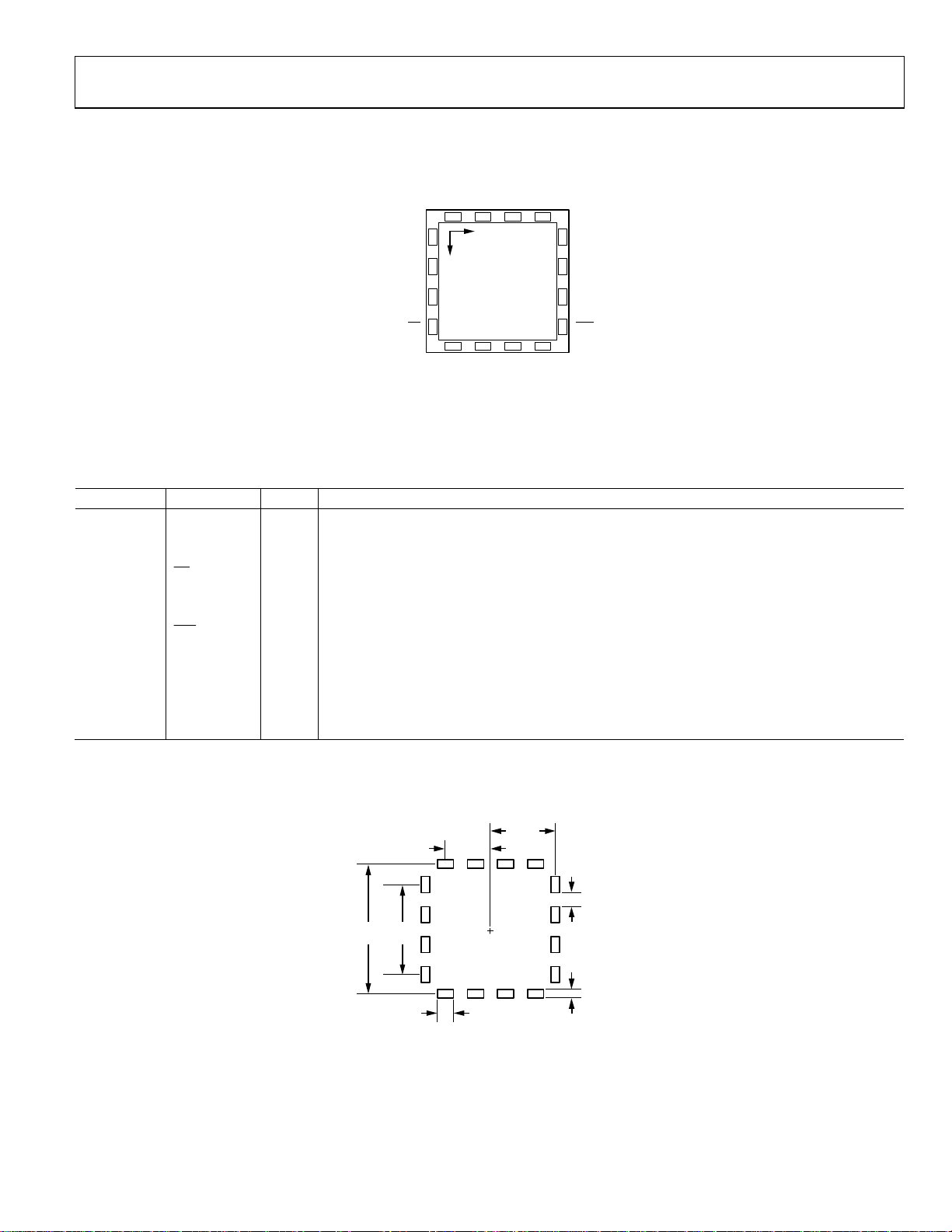

RECOMMENDED PAD GEOMETRY

4.1865

2.6955

8×

8×

9

RST

06448-004

0.670

12×

5.391

8.373

4×

2×

0.500

1.127

16×

9.2mm × 9.2mm S TACKED LGA PACKAGE

16×

06448-005

Figure 5. Example of a Pad Layout

Rev. A | Page 7 of 24

ADIS16204

%

TYPICAL PERFORMANCE CHARACTERISTICS

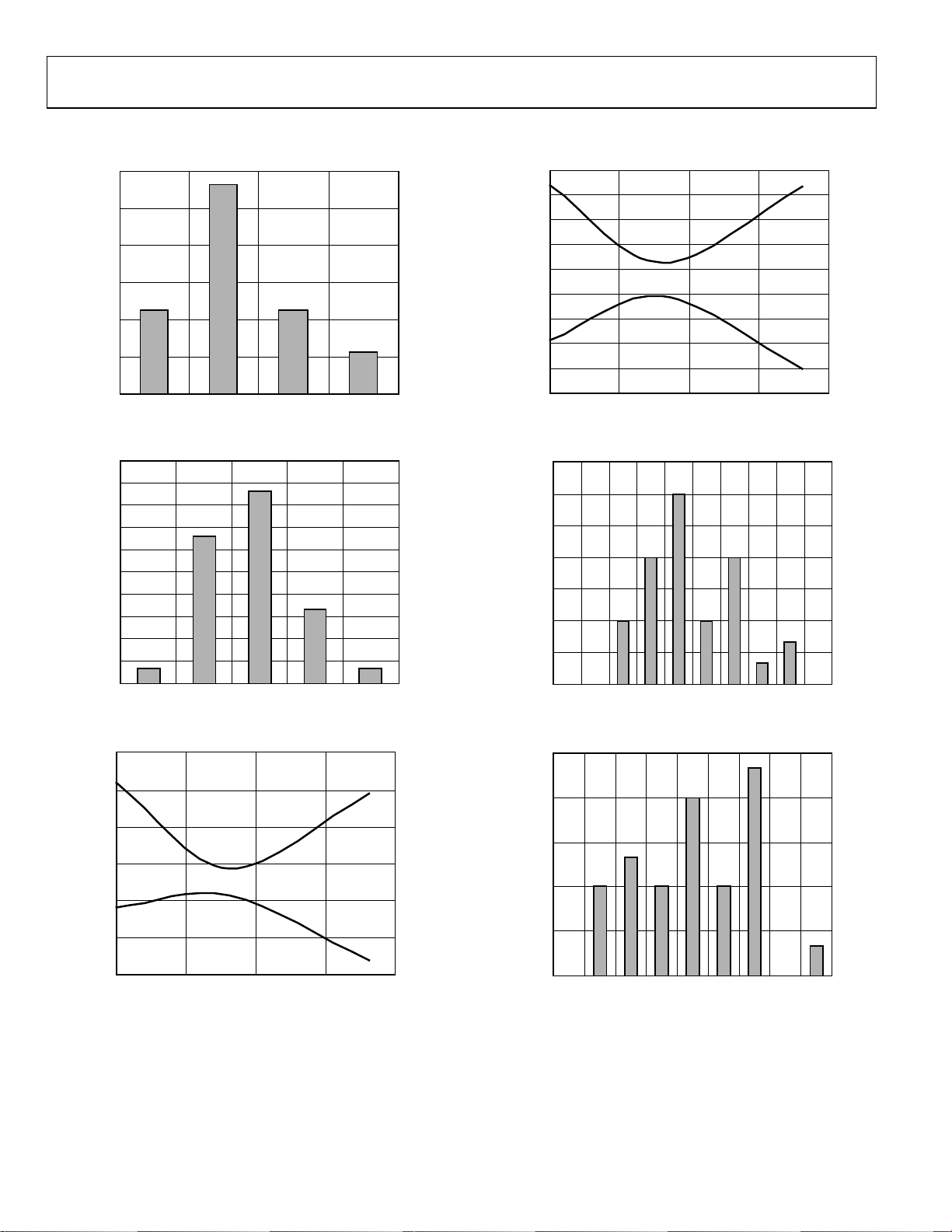

60

50%

40%

30%

20%

% OF POPULATION

10%

0%

0.040 0.125 0.210 0.295

OFFSET BIAS (g)

Figure 6. Bias Offset Distribution, X-Axis

50%

45%

40%

35%

30%

25%

20%

% OF POPULATION

15%

10%

5%

0%

0.045 0.040 0.125 0.2950.210

OFFSET BIAS (g)

Figure 7. Bias Offset Distribution, Y-Axis

0.8

06448-025

026

06448-

0.5

0.4

0.3

0.2

0.1

0

–0.1

Y-AXIS OF FSET BIAS (g)

–0.2

–0.3

–0.4

–40 0 40 80 120

+1 SIGMA

–1 SIGMA

TEMPERATURE ( °C)

Figure 9. Offset Bias Change vs. Temperature, Y-Axis

35

30

25

20

15

% OF POPULATION

10

5

0

0 0.02 0.04 0.06 0.08 0.10 0.12 0.14 0.16

TOTAL OFFSET BIAS CHANGE (g)

0.18

Figure 10. Offset Bias Change, X-Axis vs. Power Supply (3.0 V to 3.6 V)

25

06448-016

06448-019

0.6

0.4

0.2

0

X-AXIS OFFSET BIAS (g)

–0.2

–0.4

–40 0 40 80 120

+1 SIGMA

–1 SIGMA

TEMPERATURE (°C)

Figure 8. Offset Bias Change vs. Temperature, X-Axis

06448-015

20

15

10

% OF POPULATION

5

0

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07

TOTAL OFFSET BIAS CHANGE (g)

0.08

Figure 11. Offset Bias Change, Y-Axis vs. Power Supply (3.0 V to 3.6 V)

8-0200644

Rev. A | Page 8 of 24

Loading...

Loading...