Analog Devices ADG774ABRQ Datasheet

Low Voltage 400 MHz Quad 2:1 Mux

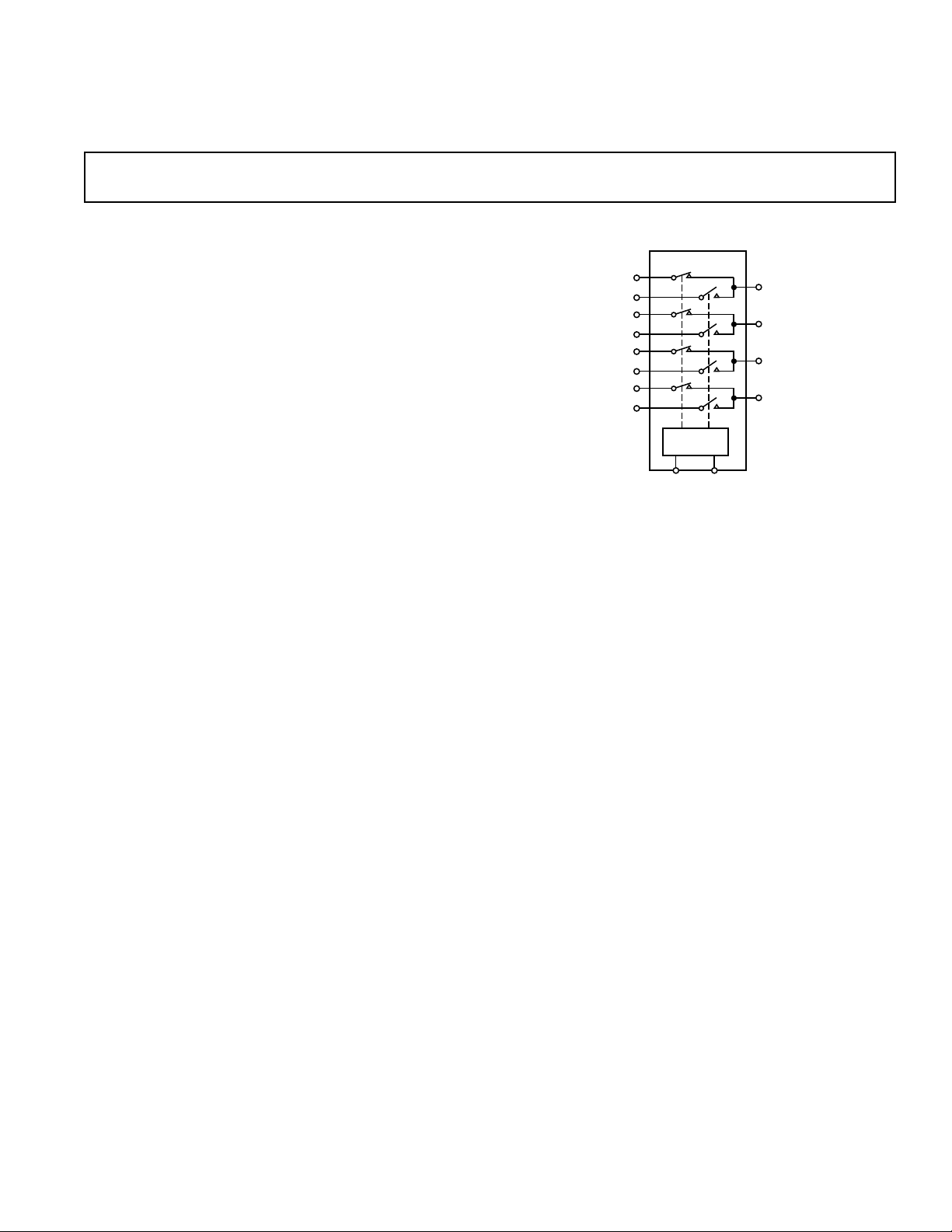

1 OF 2

DECODER

ADG774A

EN

IN

S1A

S1B

S2A

S2B

S3A

S3B

S4A

S4B

D1

D2

D3

D4

a

FEATURES

Bandwidth >400 MHz

Low Insertion Loss and On Resistance: 2.2 Typical

On-Resistance Flatness 0.3 Typical

Single 3 V/5 V Supply Operation

Very Low Distortion: <0.3%

Low Quiescent Supply Current (1 nA Typical)

Fast Switching Times

6 ns

t

ON

3 ns

t

OFF

TTL/CMOS Compatible

GENERAL DESCRIPTION

The ADG774A is a monolithic CMOS device comprising four

2:1 multiplexer/demultiplexers with high impedance outputs.

The CMOS process provides low power dissipation yet gives

high switching speed and low on resistance. The on-resistance

variation is typically less than 0.5 Ω over the input signal range.

The bandwidth of the ADG774A is typically 400 MHz and this,

coupled with low distortion (typically 0.3%), makes the part

suitable for switching of high-speed data signals.

The on-resistance profile is very flat over the full analog input

range ensuring excellent linearity and low distortion. CMOS construction ensures ultralow power dissipation.

The ADG774A operates from a single 3.3 V/5 V supply and is

TTL logic compatible. The control logic for each switch is shown

in the Truth Table.

These switches conduct equally well in both directions when

ON. In the OFF condition, signal levels up to the supplies are

blocked. The ADG774A switches exhibit break-before-make

switching action.

with 3 ns Switching Time

ADG774A

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. Wide bandwidth data rates >400 MHz.

2. Ultralow Power Dissipation.

3. Low leakage over temperature.

4. Break-Before-Make Switching.

This prevents channel shorting when the switches are configured as a multiplexer.

5. Crosstalk is typically –70 dB @ 10 MHz.

6. Off isolation is typically –65 dB @ 10 MHz.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

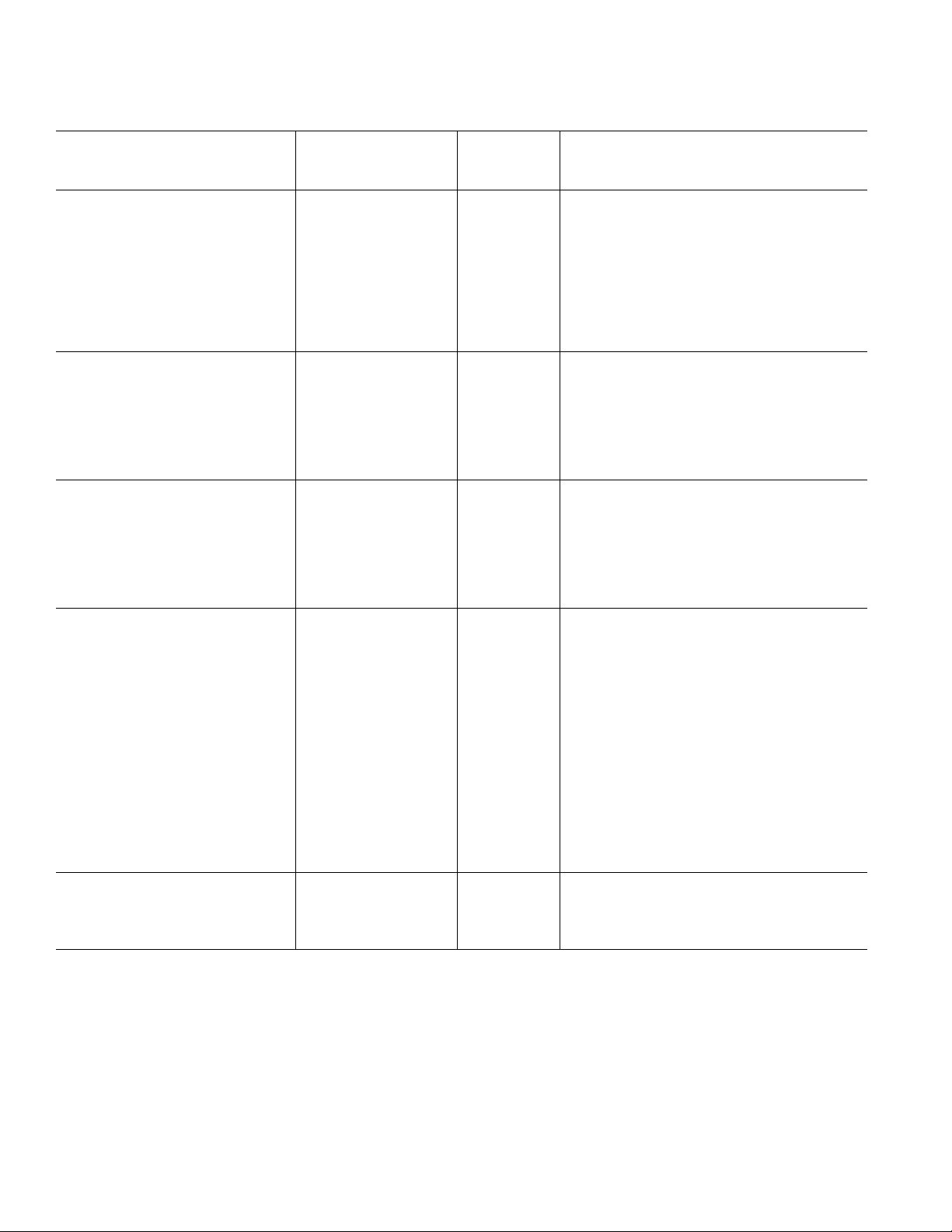

ADG774A–SPECIFICATIONS

1

SINGLE SUPPLY

(VDD = 5 V 10%, GND = 0 V. All specifications T

B Version

to

T

Parameter 25CT

MIN

MAX

ANALOG SWITCH

Analog Signal Range 0 to 2.5 V

On Resistance (R

) 2.2 Ω typ VD = 0 V to 1 V; IS = –10 mA

ON

3.5 4 Ω max

On Resistance Match Between

Channels (∆R

)0.15 Ω typ VD = 0 V to 1 V; IS = –10 mA

ON

0.5 Ω max

On Resistance Flatness (R

FLAT(ON)

) 0.3 Ω typ VD = 0 V to 1 V; IS = –10 mA

0.6 Ω max

LEAKAGE CURRENTS

Source OFF Leakage IS (OFF) ± 0.001 nA typ VD = 3 V, VS = 1 V; VD = 1 V, VS = 3 V;

± 0.1 ± 0.25 nA max Test Circuit 2

Drain OFF Leakage I

(OFF) ± 0.001 nA typ VD = 3 V, VS = 1 V; VD = 1 V, VS = 3 V;

D

± 0.1 ± 0.25 nA max Test Circuit 2

Channel ON Leakage I

, IS (ON) ±0.001 nA typ VD = VS = 3 V; VD = VS = 1 V; Test Circuit 3

D

± 0.1 ± 0.25 nA max

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

INL

INH

2.4 V min

0.8 V max

Input Current

I

INL

or I

INH

0.001 µA typ VIN = V

± 0.1 µA max

CIN, Digital Input Capacitance 3 pF typ

DYNAMIC CHARACTERISTICS

2

tON, tON (EN) 6 ns typ CL = 35 pF, RL = 50 Ω;

12 ns max V

, t

t

OFF

(EN) 3 ns typ CL = 35 pF, RL = 50 Ω;

OFF

6 ns max V

Break-Before-Make Time Delay, t

D

3 ns typ CL = 35 pF, RL = 50 Ω;

1 ns min V

Off Isolation –65 dB typ f = 10 MHz; R

Channel-to-Channel Crosstalk –70 dB typ f = 10 MHz; R

Bandwidth –3 dB 400 MHz typ Test Circuit 6, R

Distortion 0.3 % typ R

Charge Injection 6 pC typ C

(OFF) 5 pF typ

C

S

C

(OFF) 7.5 pF typ

D

CD, CS (ON) 12 pF typ

POWER REQUIREMENTS V

I

DD

1 µA max

0.001 µA typ

NOTES

1

Temperature ranges are as follows: B Version, –40°C to +85°C.

2

Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

to T

MIN

unless otherwise noted.)

MAX

Unit Test Conditions/Comments

or V

INL

= 2 V; Test Circuit 4

S

= 2 V; Test Circuit 4

S

= VS2 = 2 V; Test Circuit 5

S1

= 100 Ω

L

= 1 nF; Test Circuit 9, VS = 0 V

L

= 5.5 V

DD

Digital Inputs = 0 V or V

INH

= 50 Ω; Test Circuit 7

L

= 50 Ω; Test Circuit 8

L

= 50 Ω;

L

DD

–2–

REV. 0

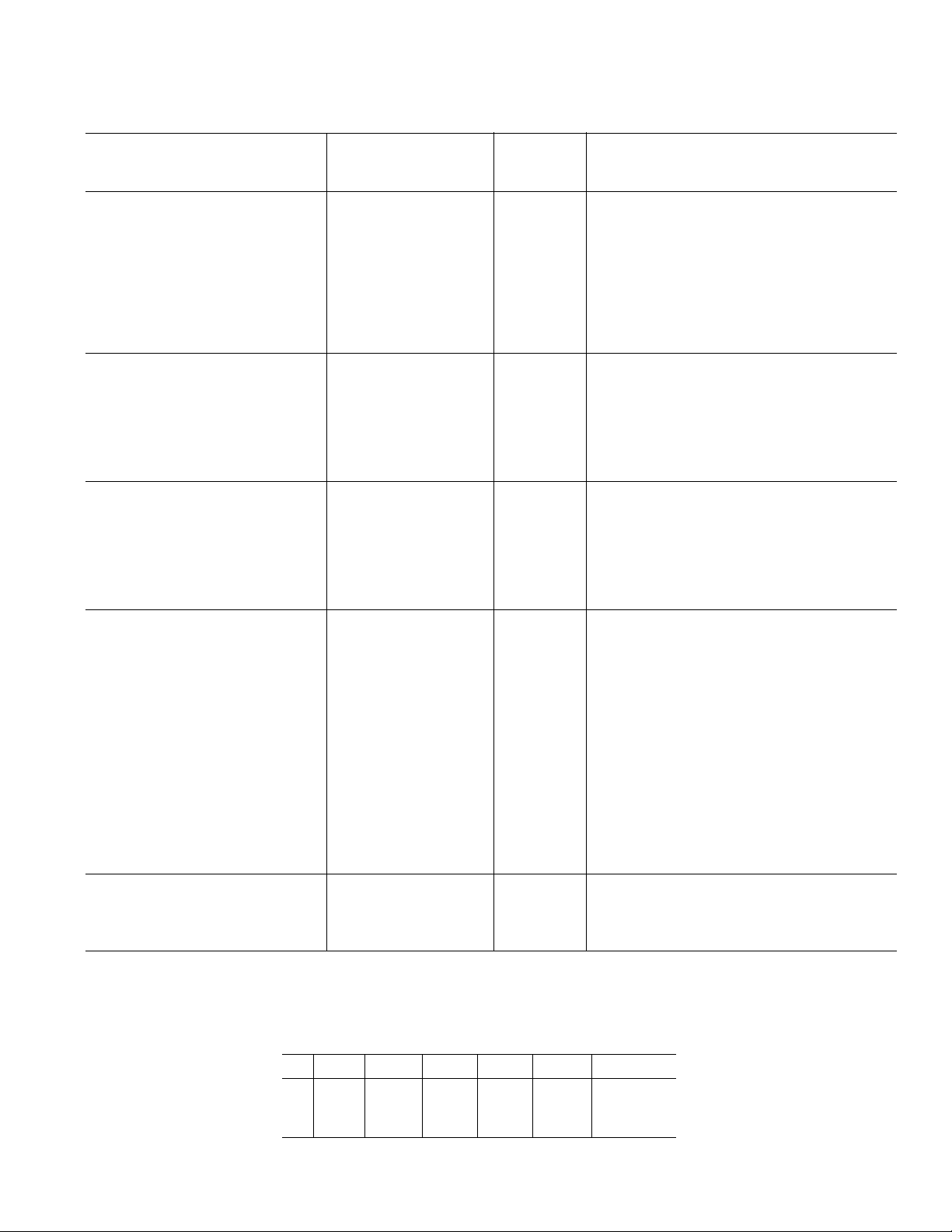

SINGLE SUPPLY

(VDD = 3 V 10%, GND = 0 V. All specifications T

MIN

to T

unless otherwise noted.)

MAX

1

B Version

T

to

Parameter 25CT

MIN

MAX

Unit Test Conditions/Comments

ANALOG SWITCH

Analog Signal Range 0 to 1.5 V

On Resistance (R

)4 Ω typ VD = 0 V to 1 V; IS = –10 mA

ON

67 Ω max

On Resistance Match Between

Channels (∆R

)0.15 Ω typ VD = 0 V to 1 V; IS = –10 mA

ON

0.5 Ω max

On Resistance Flatness (R

FLAT(ON)

) 1.5 Ω typ VD = 0 V to 1 V; IS = –10 mA

3 Ω max

LEAKAGE CURRENTS

Source OFF Leakage IS (OFF) ± 0.001 nA typ VD = 2 V, VS = 1 V; VD = 1 V, VS = 2 V;

± 0.1 ± 0.25 nA max Test Circuit 2

Drain OFF Leakage I

(OFF) ± 0.001 nA typ VD = 2 V, VS = 1 V; VD = 1 V, VS = 2 V;

D

± 0.1 ± 0.25 nA max Test Circuit 2

Channel ON Leakage I

, IS (ON) ±0.001 nA typ VD = VS = 2 V; VD = VS = 1 V; Test Circuit 3

D

± 0.1 ± 0.25 nA max

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

INL

INH

2.0 V min

0.4 V max

Input Current

I

INL

or I

INH

0.001 µA typ VIN = V

INL

or V

INH

± 0.1 µA max

CIN, Digital Input Capacitance 3 pF typ

DYNAMIC CHARACTERISTICS

2

tON, tON (EN) 7 ns typ CL = 35 pF, RL = 50 Ω;

14 ns max V

t

, t

OFF

(EN) 4 ns typ CL = 35 pF, RL = 50 Ω;

OFF

8 ns max V

Break-Before-Make Time Delay, t

D

3 ns typ CL = 35 pF, RL = 50 Ω;

1 ns min V

Off Isolation –65 dB typ f = 10 MHz; R

Channel-to-Channel Crosstalk –70 dB typ f = 10 MHz; R

Bandwidth –3 dB 400 MHz typ Test Circuit 6; R

Distortion 1.5 % typ R

Charge Injection 4 pC typ C

C

(OFF) 5 pF typ

S

(OFF) 7.5 pF typ

C

D

= 1.5 V; Test Circuit 4

S

= 1.5 V; Test Circuit 4

S

= VS2 = 1.5 V; Test Circuit 5

S1

= 100 Ω

L

= 1 nF; Test Circuit 9, VS = 0 V

L

= 50 Ω, Test Circuit 7

L

= 50 Ω, Test Circuit 8

L

= 50 Ω

L

CD, CS (ON) 12 pF typ

POWER REQUIREMENTS V

I

DD

1 µA max

= 3.3 V

DD

Digital Inputs = 0 V or V

DD

0.001 µA typ

NOTES

1

Temperature ranges are as follows: B Version, –40°C to +85°C.

2

Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

ADG774A

Table I. Truth Table

EN IN D1 D2 D3 D4 Function

1 X Hi-Z Hi-Z Hi-Z Hi-Z DISABLE

0 0 S1A S2A S3A S4A IN = 0

0 1 S1B S2B S3B S4B IN = 1

–3–REV. 0

Loading...

Loading...