ANALOG DEVICES ADG467 Service Manual

VDDV

Octal Channel Protectors

FEATURES

Fault and overvoltage protection up to ±40 V

Signal paths open circuit with power off

Signal path resistance of R

44 V supply maximum ratings

Low on resistance: 62 Ω typical

±1 nA maximum path current leakage @ +25°C

Low R

match (5 Ω maximum)

ON

Low power dissipation 0.8 μW typical

Latch-up proof construction

APPLICATIONS

ATE equipment

Sensitive measurement equipment

Hot insertion rack systems

GENERAL DESCRIPTION

The ADG467 is an octal channel protector. The channel

protector is placed in series with the signal path. The channel

protector protects sensitive components from voltage transience

in the signal path regardless if the power supplies are present or

not. For this reason, the channel protectors are ideal for use in

applications where correct power sequencing cannot always be

guaranteed (for example, hot insertion rack systems) to protect

analog inputs. This is described further, and some example

circuits are given in the Applications Information section.

Each channel protector has an independent operation and consists of an N-channel MOSFET, a P-channel MOSFET, and an

N-channel MOSFET, connected in series. The channel protector

behaves just like a series resistor during normal operation, that

is, (V

+ 1.5 V) < VIN < (VDD − 1.5 V). When a channel’s analog

SS

input exceeds the power supplies (including V

one of the MOSFETs switches off, clamping the output to either

V

+ 1.5 V or VDD − 1.5 V. Circuitry and signal source protec-

SS

tion is provided in the event of an overvoltage or power loss.

The channel protectors can withstand overvoltage inputs from

−40 V to +40 V. See the Circuit Information section.

The ADG467 can operate off both bipolar and unipolar

supplies. The channels are normally on when power is

with power on

ON

and VSS = 0 V),

DD

ADG467

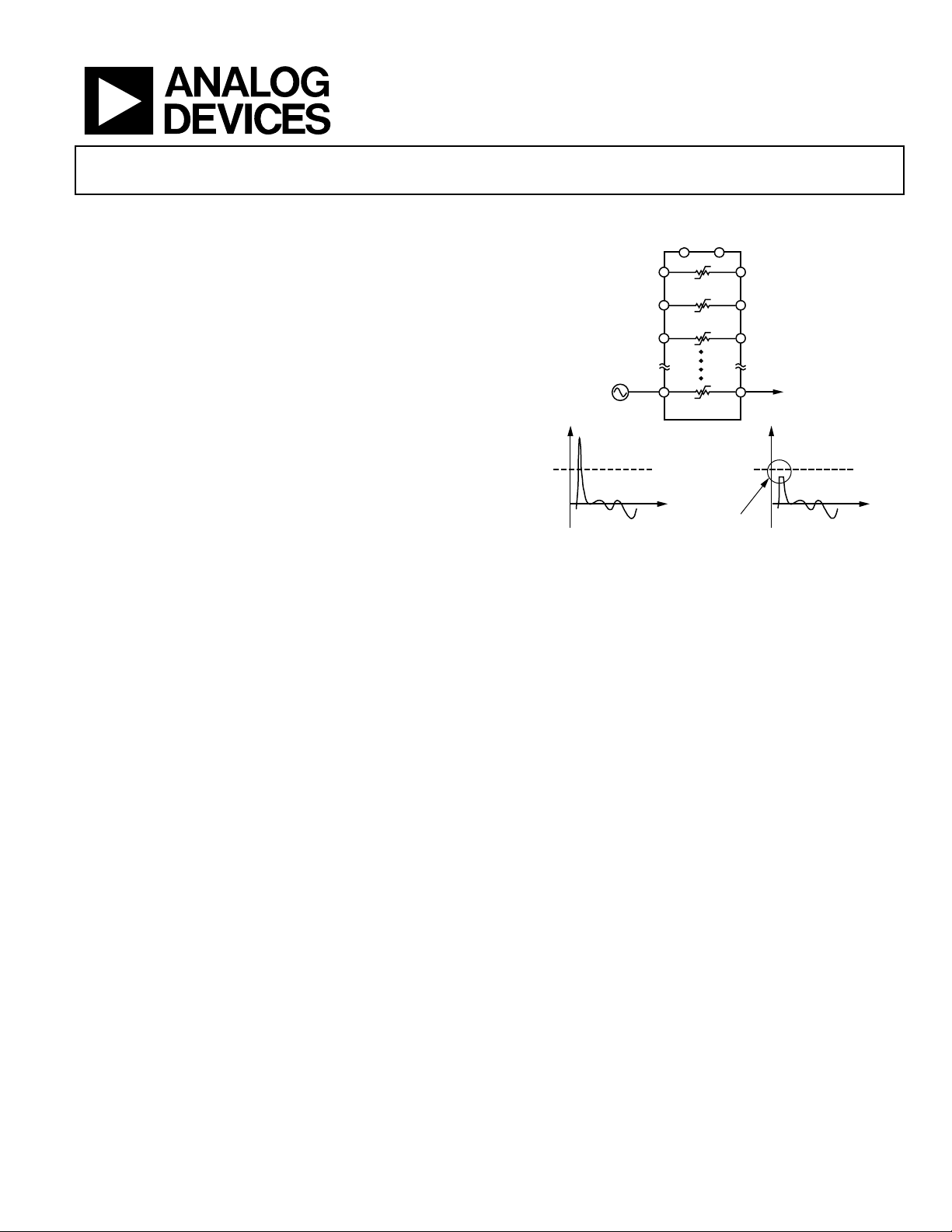

FUNCTIONAL BLOCK DIAGRAM

SS

V

D1

V

D2

V

D3

V

V

V

IN

V

DD

D8

IN

ADG467

OUTPUT CLAMPED

AT V

Figure 1.

connected and open circuit when power is disconnected. With

power supplies of ±15 V, the on resistance of the ADG467 is

62 Ω typical with a leakage current of ±1 nA maximum. When

power is disconnected, the input leakage current is approximately ±0.5 nA typical.

The ADG467 is available in an 18-lead SOIC package and a

20-lead SSOP package.

PRODUCT HIGHLIGHTS

1. Fault Protection.

The ADG467 can withstand continuous voltage inputs

from −40 V to +40 V. When a fault occurs due to the

power supplies being turned off or due to an overvoltage

being applied to the ADG467, the output is clamped.

When power is turned off, current is limited to the

microampere level.

2. Low Power Dissipation.

3. Low R

4. Trench Isolation Latch-Up Proof Construction.

A dielectric trench separates the p- and n-channel

MOSFETs thereby preventing latch-up.

. 62 Ω typical.

ON

DD

V

V

V

V

V

DD

– 1.5V

S1

S2

S3

S8

V

OUT

V

OUT

08191-001

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADG467

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Dual Supply................................................................................... 3

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

REVISION HISTORY

2/11—Rev. A to Rev. B

Updated Format..................................................................Universal

Deleted ADG466 ................................................................Universal

Changes to Features Section, General Description Section,

Figure 1, and Product Highlights Section ..................................... 1

Changes to Power Requirements, V

Deleted 8-Lead DIP, SOIC, and μSOIC Pin Configuration........ 3

Deleted Figure 12; Renumbered Sequentially .............................. 5

Changes to Figure 4 to Figure 6...................................................... 6

Added Figure 7; Renumbered Sequentially .................................. 6

Changes to Figure 11 to Figure 15.................................................. 7

Parameter, Table 1... 3

DD/VSS

Typical Performance Characteristics..............................................6

Test Circuits........................................................................................8

Circuit Information...........................................................................9

Overvoltage Protection.................................................................9

Trench Isolation.............................................................................. 11

Applications Information.............................................................. 12

Overvoltage and Power Supply Sequencing Protection........ 12

High Voltage Surge Suppression .............................................. 13

Outline Dimensions....................................................................... 14

Ordering Guide .......................................................................... 15

Added Test Circuits Section and Figure 16 to Figure 20..............8

Changes to Overvoltage Protection Section and Figure 23.........9

Changes to Figure 24...................................................................... 10

Change to Figure 26....................................................................... 11

Changes to Overvoltage and Power Supply Sequencing

Protection Section and Figure 27................................................. 12

Changes to High Voltage Surge Suppression Section and

Figure 28 .......................................................................................... 13

Changes to Outline Dimensions .................................................. 14

Changes to Ordering Guide.......................................................... 15

Rev. B | Page 2 of 16

ADG467

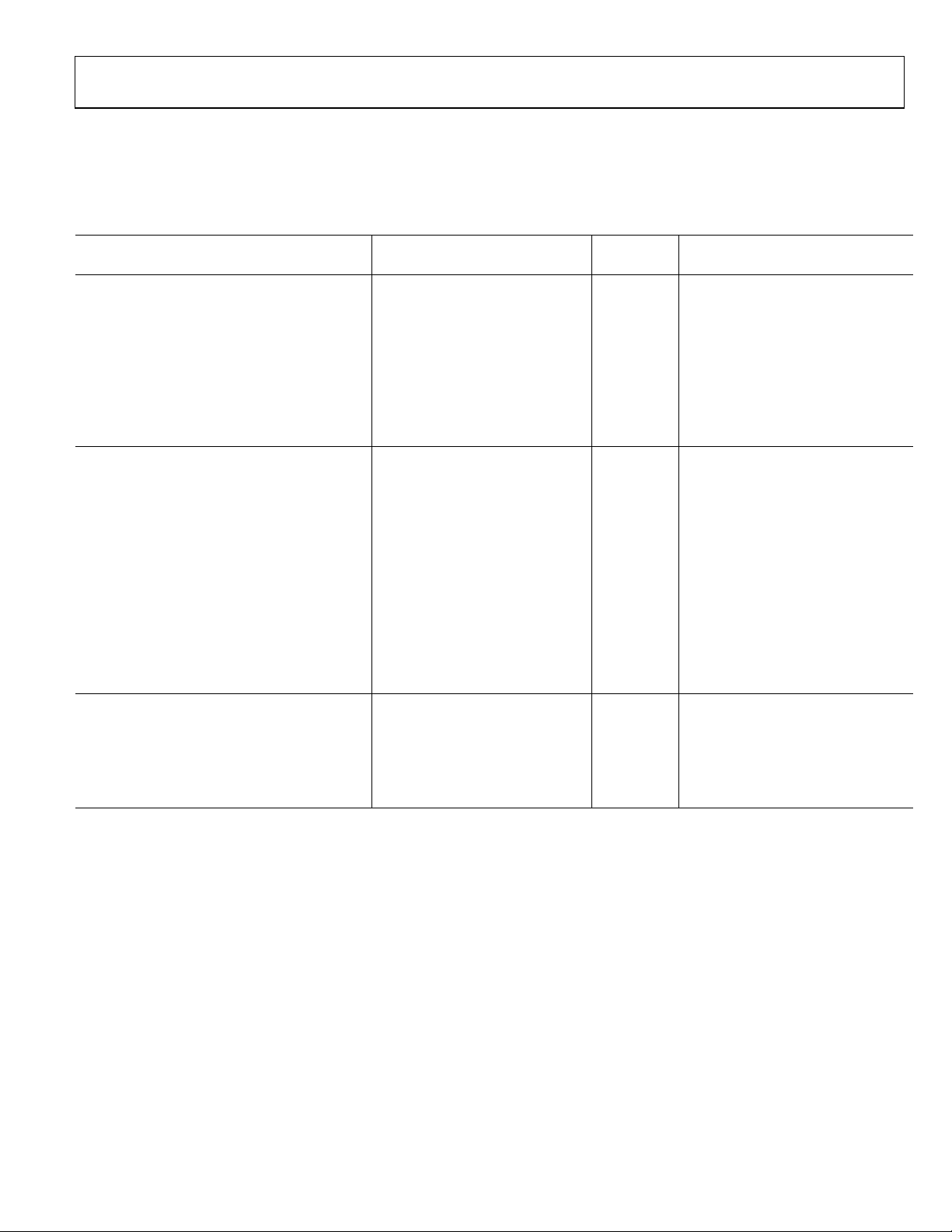

SPECIFICATIONS

DUAL SUPPLY

VDD = +15 V, VSS = −15 V, GND = 0 V, unless otherwise noted.

Table 1.

ADG467

Parameter +25°C −40°C to +85°C Unit Test Conditions/Comments

FAULT PROTECTED CHANNEL

Fault-Free Analog Signal Range V

V

V

V

RON 62 80 Ω typ −10 V ≤ VSx ≤ +10 V, ISx = 1 mA

95 Ω max

RON Flatness 6 Ω max −5 V ≤ VSx ≤ +5 V

RON Match between Channels 5 6 Ω max VSx = ±10 V, ISx = 1 mA

LEAKAGE CURRENTS

Channel Output Leakage, I

V

S(ON)

(Without Fault Condition) ±0.04 ±0.2 nA typ

±1 ±5 nA max

Channel Input Leakage, I

V

D(ON)

(with Fault Condition) ±0.2 ±0.4 nA typ VDx = open circuit

±2 ±5 nA max

Channel Input Leakage, I

V

D(OFF)

(with Power Off and Fault) ±0.5 ±2 nA typ VSx = ±35 V

±2 ±10 nA max VDx = open circuit

Channel Input Leakage, I

V

D(OFF)

(with Power Off and Output Short Circuit) ±0.006 ±0.16 μA typ VSx = ±35 V, VDx = 0 V

±0.015 ±0.5 μA max

POWER REQUIREMENTS

IDD ±0.05 μA typ

±0.5 ±8 μA max

ISS ±0.05 μA typ

±0.5 ±8 μA max

VDD/VSS ±4.5/±20 V min/max

+ 1.5 V typ Output open circuit

SS

− 1.5 V typ

DD

+ 1.7 V typ Output loaded, 1 mA

SS

− 1.7 V typ

DD

= VDx = ±10 V

Sx

= ±25 V

Sx

= 0 V, VSS = 0 V

DD

= 0 V, VSS = 0 V

DD

Rev. B | Page 3 of 16

ADG467

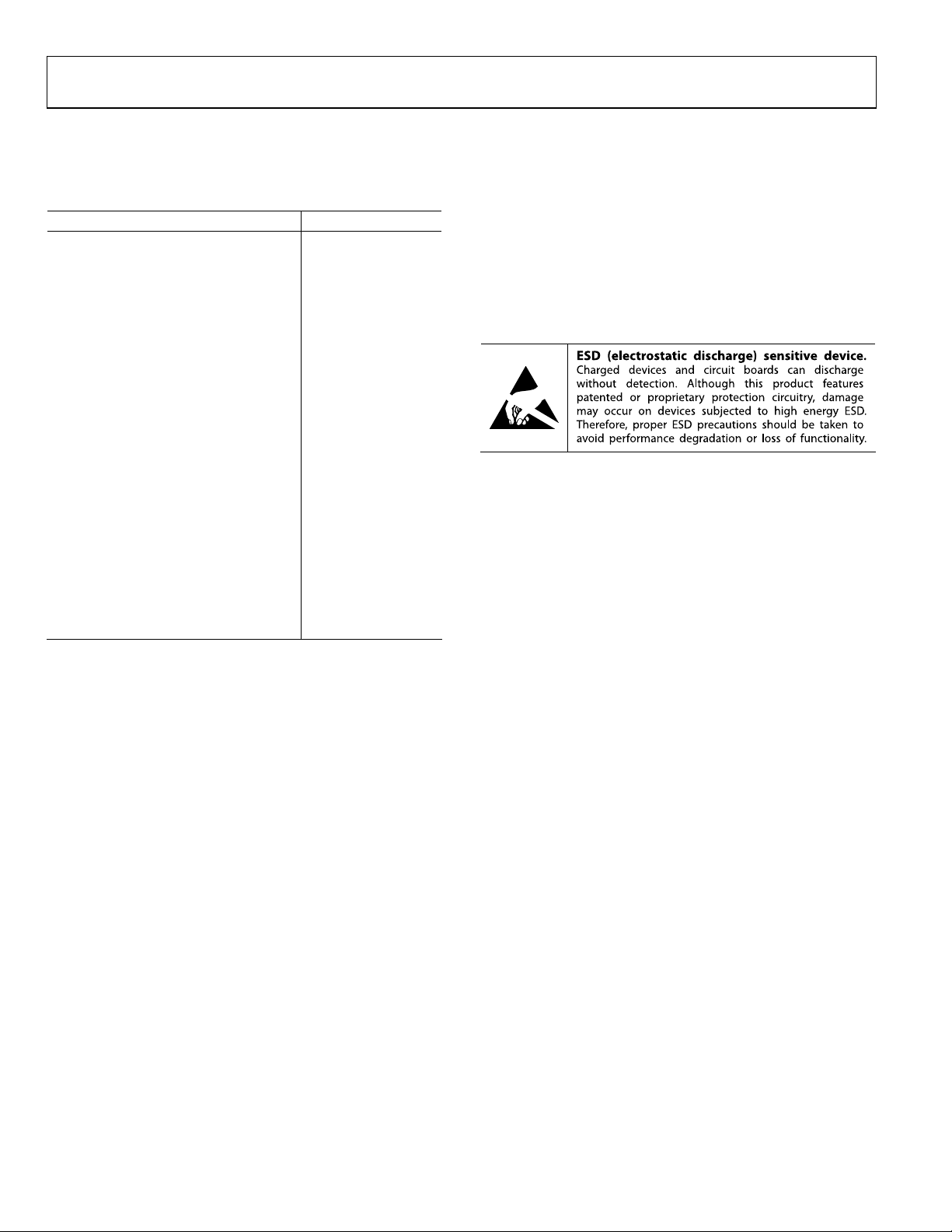

ABSOLUTE MAXIMUM RATINGS

TA = +25°C, unless otherwise noted.

Table 2.

Parameter Rating

V

to VSS +44 V

DD

VSx, VDx, Analog Input Overvoltage with

Power On

VSx, VDx, Analog Input Overvoltage with

Power Off

Continuous Current, VSx, VDx 20 mA

Peak Current, VSx, VDx (Pulsed at 1 ms,

10% Duty Cycle Maximum)

Operating Temperature Range

Industrial (B Version) −40°C to +85°C

Storage Temperature Range −65°C to +125°C

Junction Temperature +150°C

SOIC Package

θJA, Thermal Impedance 160°C/W

Lead Temperature, Soldering

SSOP Package

θJA, Thermal Impedance 130°C/W

Lead Temperature, Soldering

1

Overvoltages at VSx or VDx are clamped by the channel protector; see the

Circuit Information section.

1

1

Vapor Phase (60 sec) +215°C

Infrared (15 sec) +220°C

Vapor Phase (60 sec) +215°C

Infrared (15 sec) +220°C

VSS − 20 V to VDD + 20 V

−40 V to +40 V

40 mA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. B | Page 4 of 16

ADG467

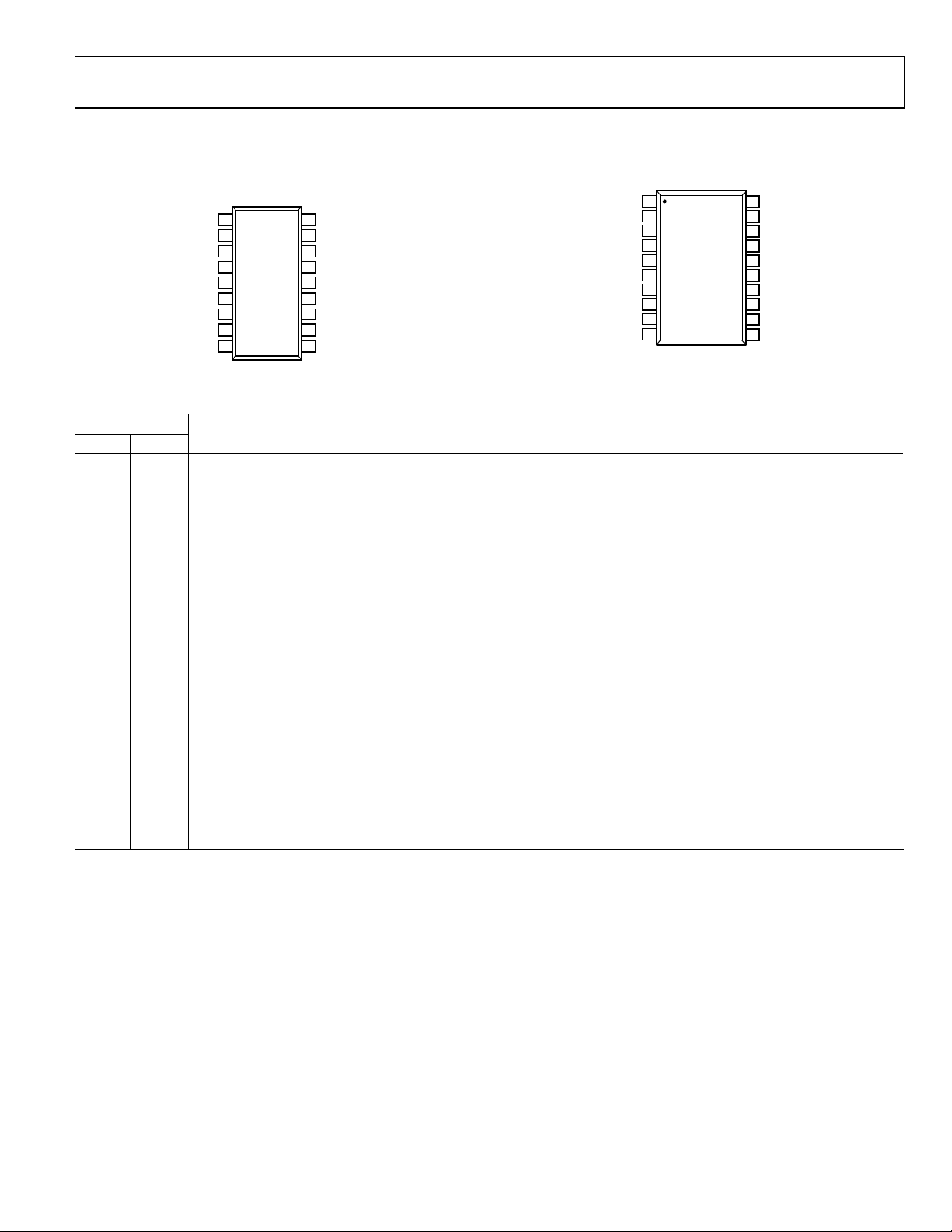

V

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

V

1

V

D1

V

2

D2

V

3

D3

ADG467

4

V

D4

TOP VIEW

V

5

D5

(Not to Scale)

V

6

D6

7

V

D7

V

8

D8

9

SS

Figure 2. 18-Lead SOIC Pin Configuration

18

V

DD

V

17

S1

V

16

S2

15

V

S3

V

14

S4

V

13

S5

12

V

S6

V

11

S7

V

10

S8

8191-002

Figure 3. 20-Lead SSOP Pin Configuration

Table 3. Pin Function Descriptions

Pin No.

SOIC SSOP Mnemonic Description

1 1 VD1 Drain Terminal 1. This pin can be an input or an output.

2 2 VD2 Drain Terminal 2. This pin can be an input or an output.

3 3 VD3 Drain Terminal 3. This pin can be an input or an output.

4 4 VD4 Drain Terminal 4. This pin can be an input or an output.

5 5 VD5 Drain Terminal 5. This pin can be an input or an output.

6 6 VD6 Drain Terminal 6. This pin can be an input or an output.

7 7 VD7 Drain Terminal 7. This pin can be an input or an output.

8 8 VD8 Drain Terminal 8. This pin can be an input or an output.

9 9 VSS

Most Negative Power Supply Potential. In single-supply applications, this pin can be connected to

ground.

N/A 10 NC No Connect.

10 11 VS8 Source Terminal 1. This pin can be an input or an output.

11 12 VS7 Source Terminal 2. This pin can be an input or an output.

12 13 VS6 Source Terminal 3. This pin can be an input or an output.

13 14 VS5 Source Terminal 4. This pin can be an input or an output.

14 15 VS4 Source Terminal 5. This pin can be an input or an output.

15 16 VS3 Source Terminal 6. This pin can be an input or an output.

16 17 VS2 Source Terminal 7. This pin can be an input or an output.

17 18 VS1 Source Terminal 8. This pin can be an input or an output.

18 19 VDD Most Positive Power Supply Potential.

N/A 20 NC No Connect. Do not connect to this pin.

1

D1

V

2

D2

V

3

D3

V

4

D4

V

5

D5

V

6

D6

7

V

D7

V

8

D8

V

9

SS

NC

10

NC = NO CONNECT

ADG467

TOP VIEW

(Not to Scale)

20

NC

19

V

DD

18

V

S1

17

V

S2

16

V

S3

V

15

S4

V

14

S5

V

13

S6

12

V

S7

11

V

S8

08191-003

Rev. B | Page 5 of 16

Loading...

Loading...