ANALOG DEVICES ADG1219 Service Manual

Low Capacitance, Low Charge Injection,

FEATURES

<0.5 pC charge injection over full signal range

2.5 pF off capacitance

Low leakage; 0.6 nA maximum @ 85°C

120 Ω on resistance

Fully specified at +12 V, ±15 V

No V

supply required

L

3 V logic-compatible inputs

Rail-to-rail operation

8-lead SOT-23 package

APPLICATIONS

Automatic test equipment

Data acquisition systems

Battery-powered systems

Sample-and-hold systems

Audio/video signal routing

Communication systems

±15 V/12 V iCMOS SPDT in SOT-23

ADG1219

FUNCTIONAL BLOCK DIAGRAM

ADG1219

SA

SB

DECODER

IN EN

SWITCHES S HOWN FOR A LOGIC 0 INPUT

Figure 1.

D

06575-001

GENERAL DESCRIPTION

The ADG1219 is a monolithic iCMOS® device containing an

SPDT switch. An EN input is used to enable or disable the

device. When disabled, all channels are switched off. When on,

each channel conducts equally well in both directions and has

an input signal range that extends to the supplies. Each switch

exhibits break-before-make switching action.

The iCMOS (industrial CMOS) modular manufacturing

process combines high voltage complementary metal-oxide

semiconductor (CMOS) and bipolar technologies. It enables the

development of a wide range of high performance analog ICs

capable of 33 V operation in a footprint that no other generation

of high voltage parts has been able to achieve. Unlike analog ICs

using conventional CMOS processes, iCMOS components can

tolerate high supply voltages while providing increased performance, dramatically lower power consumption, and reduced

package size.

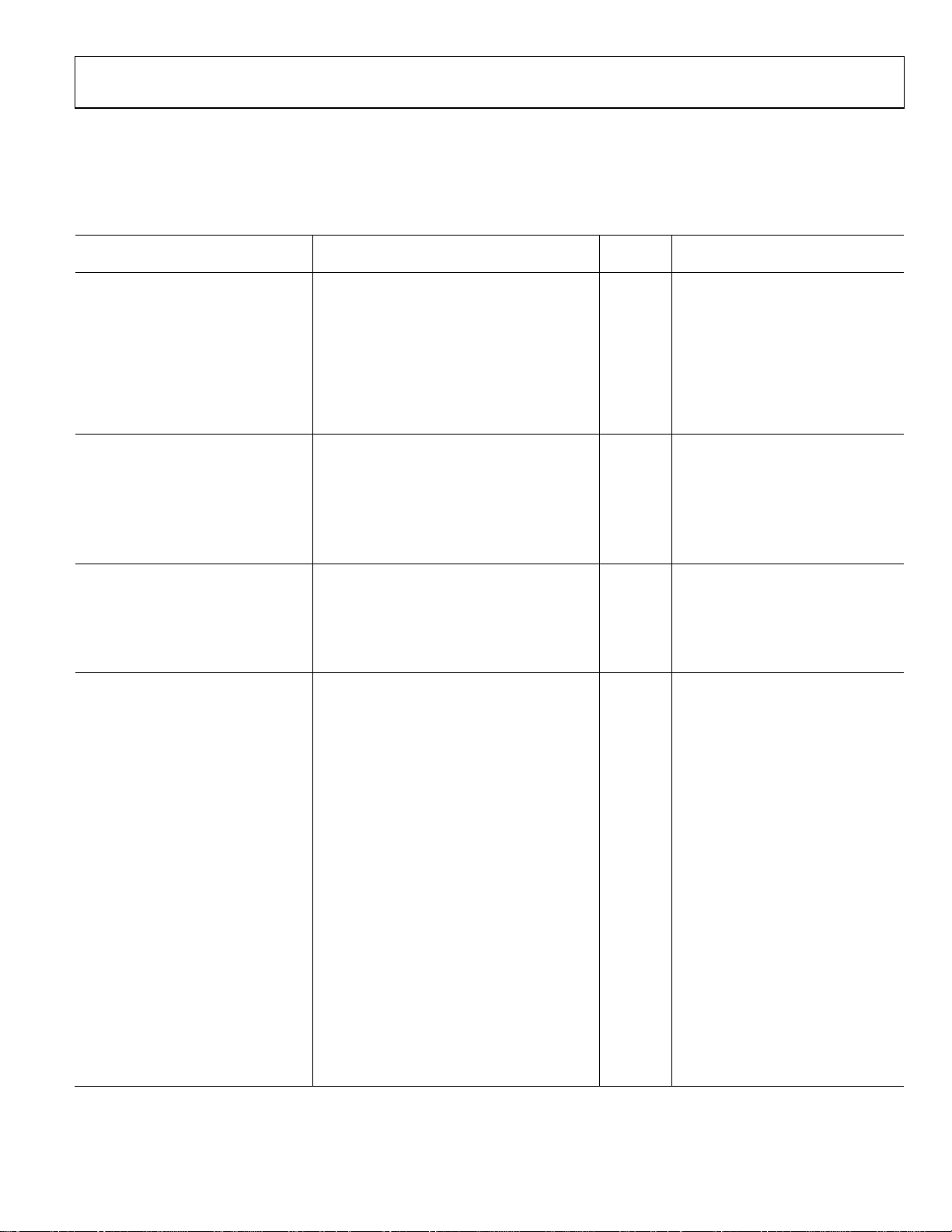

The ultralow capacitance and exceptionally low charge injection

of these multiplexers make them ideal solutions for data acquisition and sample-and-hold applications, where low glitch and

fast settling are required. Figure 2 shows that there is minimum

charge injection over the entire signal range of the device.

iCMOS construction also ensures ultralow power dissipation,

making the parts ideally suited for portable and batterypowered instruments.

0.5

TA = 25ºC

0.4

0.3

0.2

0.1

0

–0.1

–0.2

CHARGE INJECTI ON (pC)

–0.3

–0.4

–0.5

–15 15

Figure 2. Charge Injection vs. Input Voltage

VDD = +15V

V

= –15V

SS

VDD = +12V

V

SS

VDD = +5V

V

= –5V

SS

–10 –5 0 5 10

INPUT VOLTAGE (V)

= 0V

06575-033

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008–2009 Analog Devices, Inc. All rights reserved.

ADG1219

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Dual Supply ................................................................................... 3

Single Supply ................................................................................. 4

REVISION HISTORY

3/09—Rev. 0 to Rev. A

Change to Power Requirements, I

Change to Power Requirements, I

Updated Outline Dimensions ........................................................ 15

4/08—Revision 0: Initial Version

Parameter, Table 1 .............. 4

DD

Parameter, Table 2 .............. 5

DD

Absolute Maximum Ratings ............................................................6

ESD Caution...................................................................................6

Pin Configuration and Function Descriptions ..............................7

Typical Performance Characteristics ..............................................8

Test Circuits ..................................................................................... 12

Terminology .................................................................................... 14

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 15

Rev. A | Page 2 of 16

ADG1219

SPECIFICATIONS

DUAL SUPPLY

VDD = 15 V ± 10%, VSS = −15 V ± 10%, GND = 0 V, unless otherwise noted.

Table 1.

1

B Version

Parameters 25°C −40°C to +85°C −40°C to +125°C Unit Test Conditions/Comments

ANALOG SWITCH

Analog Signal Range VDD to VSS V

On Resistance, RON 120 Ω typ

200 240 270 Ω max VDD = +13.5 V, VSS = −13.5 V

On Resistance Match Between

Channels, ∆R

ON

3.5 Ω typ V

6 10 12 Ω max

On Resistance Flatness, R

20 Ω typ VS = −5 V, 0 V, +5 V; IS = −1 mA

FLAT(ON)

64 76 84 Ω max

LEAKAGE CURRENTS VDD = +16.5 V, VSS = −16.5 V

Source Off Leakage, IS (Off) ±0.004 nA typ

±0.1 ±0.6 ±1 nA max

Drain Off Leakage, ID (Off) ±0.009 nA typ

±0.1 ±0.6 ±1 nA max

Channel On Leakage, ID, IS (On) ±0.02 nA typ

±0.2 ±0.6 ±1 nA max

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, I

INL

2.0 V min

INH

0.8 V max

INL

or I

0.005 μA typ VIN = V

INH

±0.1 μA max

Digital Input Capacitance, CIN 2 pF typ

DYNAMIC CHARACTERISTICS

Transition Time, t

TRANSITION

2

140 ns typ RL = 300 Ω, CL = 35 pF

170 200 230 ns max

tON (EN) 85 ns typ RL = 300 Ω, CL = 35 pF

105 130 140 ns max

t

(EN) 105 ns typ RL = 300 Ω, CL = 35 pF

OFF

125 150 170 ns max

Break-Before-Make Time Delay, t

40 ns typ RL = 300 Ω, CL = 35 pF

BBM

10 ns min

Charge Injection 0.1 pC typ VS = 0 V, RS = 0 Ω, CL = 1 nF;

Off Isolation 77 dB typ RL = 50 Ω, CL = 5 pF, f = 1 MHz;

Channel-to-Channel Crosstalk 80 dB typ RL = 50 Ω, CL = 5 pF, f = 1 MHz;

Total Harmonic Distortion + Noise 0.15 % typ RL = 10 kΩ, 5 V rms, f = 20 Hz to 20 kHz

−3 dB Bandwidth 520 MHz typ

CS (Off) 2.5 pF typ f = 1 MHz; VS = 0 V

3.3 pF max f = 1 MHz; VS = 0 V

CD (Off) 4.3 pF typ f = 1 MHz; VS = 0 V

5.1 pF max f = 1 MHz; VS = 0 V

CD, CS (On) 7.5 pF typ f = 1 MHz; VS = 0 V

10 pF max f = 1 MHz; VS = 0 V

V

= ±10 V, IS = −1 mA; see Figure 23

S

= ±10 V, IS = −1 mA

S

V

= ±10 V, VS = ±10 V; see Figure 24

S

V

= ±10 V, VS = ±10 V; see Figure 24

S

V

= VD = ±10 V; see Figure 25

S

or V

INL

V

= 10 V; see Figure 30

S

V

= 10 V; see Figure 30

S

V

= 10 V; see Figure 30

S

V

= VS2 = 10 V; see Figure 31

S1

see

Figure 32

see

Figure 26

see

Figure 27

R

= 50 Ω, CL = 5 pF; see Figure 28

L

INH

Rev. A | Page 3 of 16

ADG1219

B Version

1

Parameters 25°C −40°C to +85°C −40°C to +125°C Unit Test Conditions/Comments

POWER REQUIREMENTS VDD = +16.5 V, VSS = −16.5 V

IDD 0.001 μA typ Digital inputs = 0 V or VDD

1.0 μA max

IDD 140 μA typ Digital inputs = 5 V

190 μA max

ISS 0.001 μA typ Digital inputs = 0 V, 5 V or VDD

1.0 μA max

VDD/VSS ±5/±16.5 V

|V

| = |VSS|

DD

min/max

1

Temperature range for B version is −40°C to +125°C.

2

Guaranteed by design; not subject to production test.

SINGLE SUPPLY

VDD = 12 V ± 10%, VSS = 0 V, GND = 0 V, unless otherwise noted.

Table 2.

B Version

Parameters 25°C −40°C to +85°C −40°C to +125°C Unit Test Conditions/Comments

ANALOG SWITCH

Analog Signal Range 0 V to VDD V

On Resistance, RON 300 Ω typ

On Resistance Match Between

Channels, ∆R

ON

16 26 27 Ω max

On Resistance Flatness, R

60 Ω typ VS = 3 V, 6 V, 9 V, IS = −1 mA

FLAT(ON)

LEAKAGE CURRENTS

Source Off Leakage, IS (Off) ±0.006 nA typ

Drain Off Leakage, ID (Off) ±0.006 nA typ

Channel On Leakage, ID, IS (On) ±0.02 nA typ

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, I

2.0 V min

INH

0.8 V max

INL

or I

0.001 μA typ VIN = V

INL

INH

Digital Input Capacitance, CIN 3

DYNAMIC CHARACTERISTICS

Transition Time, t

TRANSITION

2

195 ns typ RL = 300 Ω, CL = 35 pF

250 300 340 ns max

tON (EN) 120 ns typ RL = 300 Ω, CL = 35 pF

150 190 210 ns max

t

(EN) 145 ns typ RL = 300 Ω, CL = 35 pF

OFF

185 220 255 ns max

Break-Before-Make Time Delay, t

Charge Injection −0.8

Off Isolation 80

Channel-to-Channel Crosstalk 80

−3 dB Bandwidth 400

475 567 625 Ω max V

4.5 Ω typ V

±0.1 ±0.6 ±1 nA max

±0.1 ±0.6 ±1 nA max

±0.2 ±0.6 ±1 nA max

±0.1 μA max

70

BBM

10 ns min

1

Rev. A | Page 4 of 16

V

= 0 V to 10 V, IS = −1 mA; see Figure 23

S

= 10.8 V, VSS = 0 V

DD

= 0 V to 10 V, IS = −1 mA

S

VDD = 13.2 V

V

= 1 V/10 V, VD = 10 V/1 V; see Figure 24

S

V

= 1 V/10 V, VD = 10 V/1 V; see Figure 24

S

V

= VD = 1 V or 10 V; see Figure 25

S

or V

INL

INH

pF typ

V

= 8 V; see Figure 30

S

V

= 8 V; see Figure 30

S

V

= 8 V; see Figure 30

S

ns typ RL = 300 Ω, CL = 35 pF

= VS2 = 8 V; see Figure 31

V

S1

pC typ

V

= 6 V, RS = 0 Ω, CL = 1 nF; see Figure 32

S

dB typ RL = 50 Ω, CL = 5 pF, f = 1 MHz;

see

Figure 26

dB typ RL = 50 Ω, CL = 5 pF, f = 1 MHz;

see

Figure 27

MHz typ

R

= 50 Ω, CL = 5 pF; see Figure 28

L

ADG1219

B Version

1

Parameters 25°C −40°C to +85°C −40°C to +125°C Unit Test Conditions/Comments

CS (Off) 2.9 pF typ f = 1 MHz; VS = 6 V

3.7 pF max f = 1 MHz; VS = 6 V

CD (Off) 5 pF typ f = 1 MHz; VS = 6 V

5.8 pF max f = 1 MHz; VS = 6 V

CD, CS (On) 8.5 pF typ f = 1 MHz; VS = 6 V

11 pF max f = 1 MHz; VS = 6 V

POWER REQUIREMENTS

VDD = 13.2 V

IDD 0.001 μA typ Digital inputs = 0 V or VDD

1.0 μA max

IDD 140 μA typ Digital inputs = 5 V

190 μA max

VDD 5/16.5 V min/max VSS = 0 V, GND = 0 V

1

Temperature range for B version is −40°C to +125°C.

2

Guaranteed by design; not subject to production test.

Rev. A | Page 5 of 16

Loading...

Loading...