Analog Devices ADCMP580 1 2 pra Datasheet

Ultrafast SiGe

© 2004

Preliminary Technical Data

FEATURES

150 ps propagation delay

25 ps overdrive and slew rate dispersion

8 GHz equivalent input rise time bandwidth

100 ps minimum pulse width

35 ps typical output rise/fall

10 ps deterministic jitter(DJ)

200 fs random jitter (RJ)

−2 V to +3 V input range with +5 V/−5.2 V supplies

On-chip terminations at both input pinsl

Resistor-programmable hysteresis

Differential latch control

Power supply rejection > 70 dB

APPLICATIONS

Automatic test equipment (ATE)

High speed instrumentation

Pulse spectroscopy

Medical imaging and diagnostics

High speed line receivers

Threshold detection

Peak and zero-crossing detectors

High speed trigger circuitry

Clock and data signal restoration

GENERAL DESCRIPTION

The ADCMP580/ADCMP581/ADCMP582 are ultrafast voltage

comparators fabricated on Analog Devices, Inc.’s proprietary

XFCB3 Silicon Germanium (SiGe) bipolar process. The

ADCMP580 features CML output drivers; the ADCMP581

features reduced swing ECL (negative ECL) output drivers; and

the ADCMP582 features reduced-swing PECL (positive ECL)

output drivers.

Voltage Comparator

ADCMP580/ADCMP581/ADCMP582

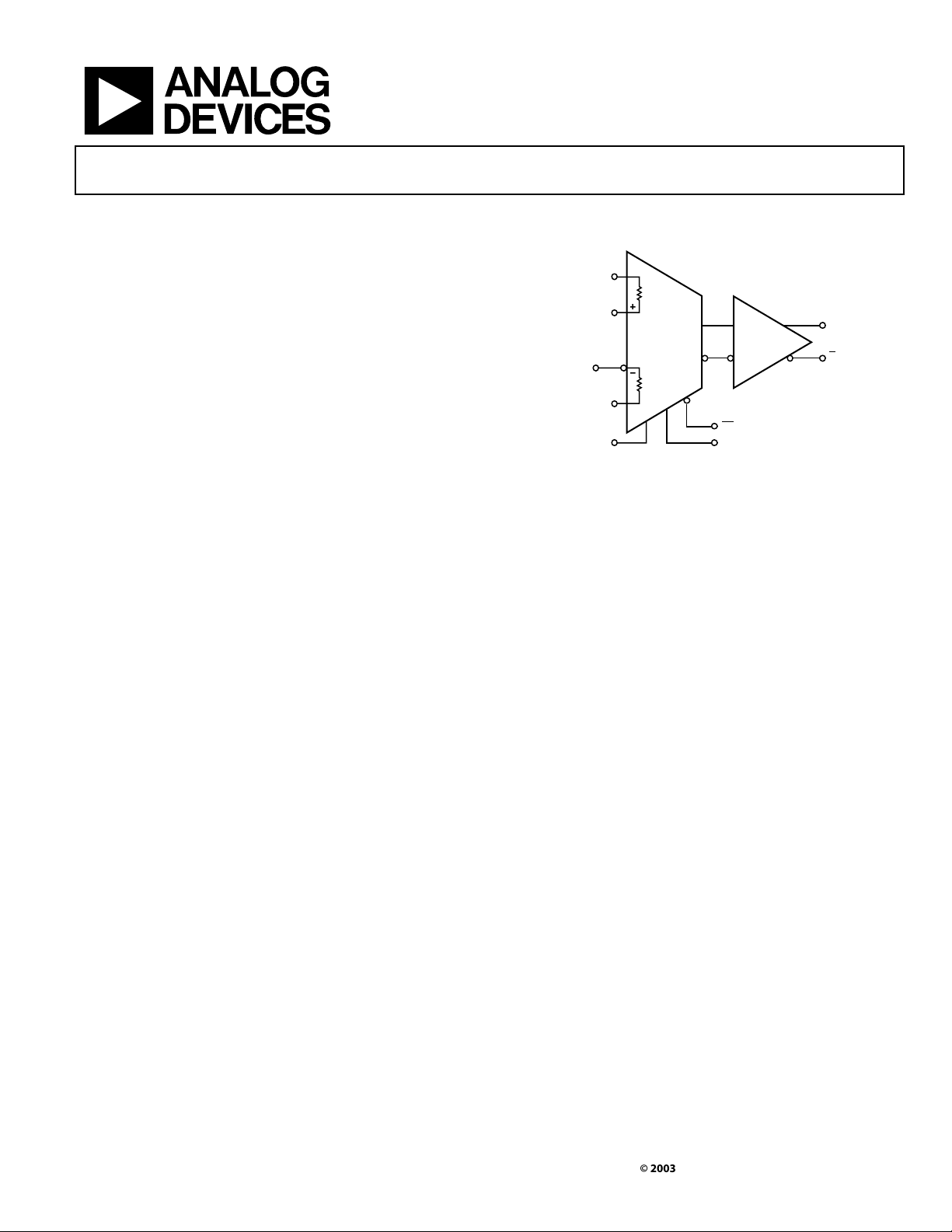

FUNCTIONAL BLOCK DIAGRAM

V

TERMINATION

TP

VP NONINVERTING

VN INVERTING

V

TN

The ±5 V power supplies enable a wide −2 V to +3 V input

range with logic levels referenced to the CML/NECL/PECL

outputs. The three inputs have 50 Ω on-chip termination

resistors with the optional capability to be left open (on an

individual pin basis) for applications requiring high impedance

input.

The CML output stage is designed to directly drive 400 mV into

50 Ω transmission lines terminated to ground. The NECL

output stages are designed to directly drive 400 mV into 50 Ω

terminated to −2 V. The PECL output stages are designed to

directly drive 400 mV into 50 Ω terminated to V

speed latch and programmable hysteresis are also provided. The

differential latch input controls are also 50 Ω terminated to an

independent V

PECL logic.

The ADCMP580/ADCMP581/ADCMP582 are available in a

16-lead LFCSP package.

INPUT

INPUT

TERMINATION

ADCMP580/

ADCMP581/

ADCMP582

Figure 1.

pin to interface to either CML or ECL or to

TT

CML/ECL/

PECL

LE INPUT

LE INPUTHYS

Q OUTPUT

Q OUTPUT

− 2 V. High

CCO

04672-0-001

The three comparators offer 150 ps propagation delay and 100

ps minimum pulse width for 10 Gbps operation with 200 fs

random jitter (RJ). Overdrive and slew rate dispersion is

typically less than 25 ps.

Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2003 Analog Devices, Inc. All rights reserved.

www.analog.com

Preliminary Technical Data ADCMP580/ADCMP581/ADCMP582

TABLE OF CONTENTS

Electrical Characteristics ................................................................. 3

Using/Disabling the Latch Feature..............................................9

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Thermal Considerations.............................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics............................................. 7

Application Information.................................................................. 9

Power/Ground Layout and Bypassing....................................... 9

ADCMP58x Family of Output Stages ....................................... 9

REVISION HISTORY

6/04—Revision PrA

Optimizing High Speed Performance ..................................... 10

Comparator Propagation Delay Dispersion ........................... 10

Comparator Hysteresis .............................................................. 11

Minimum Input Slew Rate Requirement................................ 11

Typical Application Circuits .......................................................... 12

Timing Information ....................................................................... 13

Outline Dimensions....................................................................... 14

Ordering Guide .......................................................................... 14

Rev. PrA | Page 2 of 16

Preliminary Technical Data ADCMP580/ADCMP581/ADCMP582

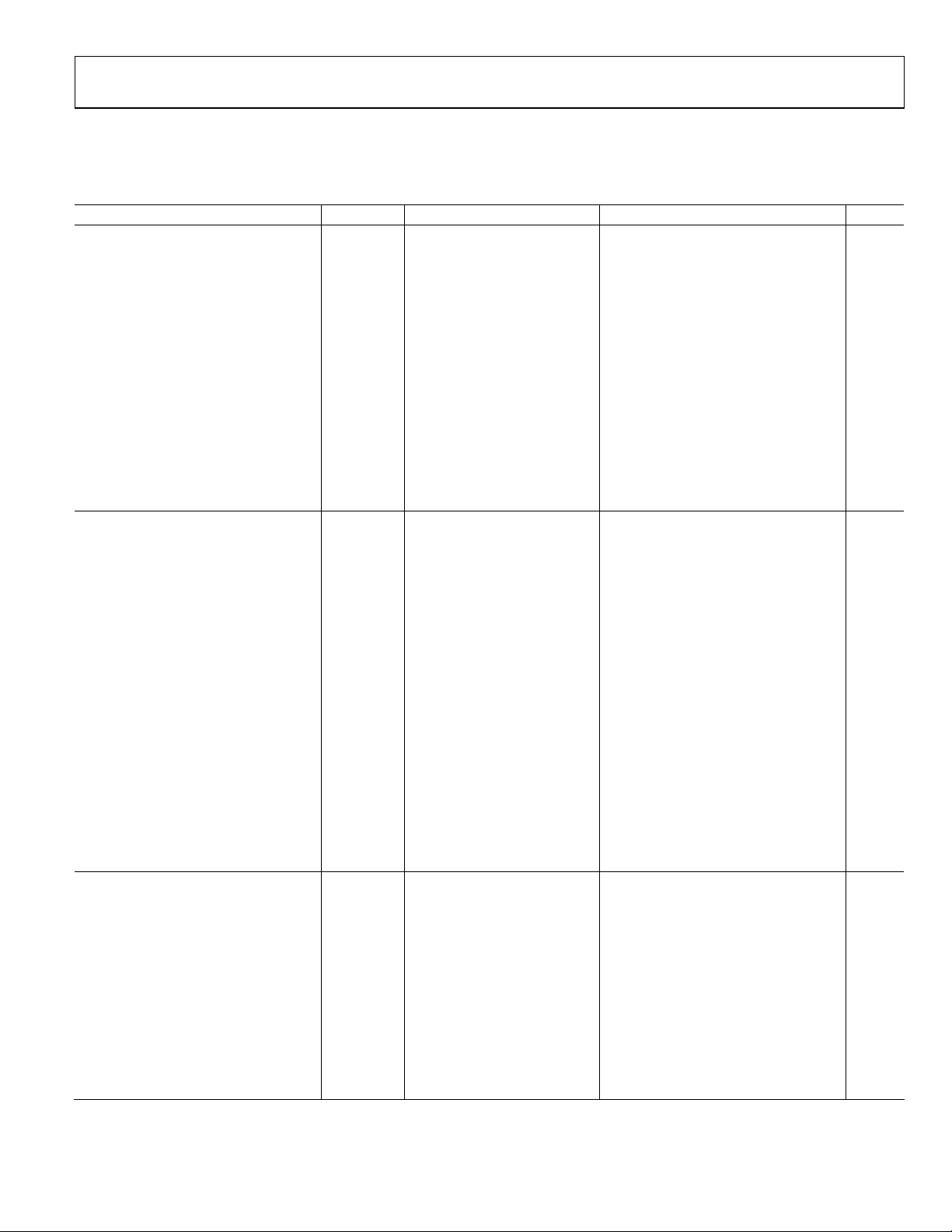

ELECTRICAL CHARACTERISTICS

V

= +5.0 V, VEE = −5.0 V, V

CCI

Table 1.

Parameter Symbol Condition Min Typ Max Unit

DC INPUT CHARACTERISTICS

Input Voltage Range VP, V

Input Differential Range −2.0 +2.0 V

Input Offset Voltage V

Offset Voltage Tempco ∆VOS/d

Input Bias Current IP, I

Input Bias Current Tempco 50.0 nA/°C

Input Offset Current 2.0 5.0 µA

Input Capacitance CP, C

Input Resistance 47.5 50 52.5 Ω

Input Resistance, Differential Mode Open termination 50 kΩ

Input Resistance, Common Mode Open termination 500 kΩ

Active Gain A

Common-Mode Rejection CMRR VCM = −2.0 V to +3.0 V 50 dB

Hysteresis R

LATCH ENABLE CHARACTERISTICS

ADCMP580 (CML)

Latch Enable Input Range −0.8 0 V

Latch Enable Input Differential 0.2 0.4 0.5 V

Latch Setup Time t

Latch Hold Time t

ADCMP581 (NECL)

Latch Enable Input Range −1.8 +0.8 V

Latch Enable Input Differential 0.2 0.4 0.5 V

Latch Setup Time t

Latch Hold Time t

ADCMP582 (PECL)

Latch Enable Input Range V

Latch Enable Input Differential 0.2 0.4 0.5 V

Latch Setup Time t

Latch Hold Time t

Latch Enable Input Impedance 47.5 50.0 52.5 ps

Latch to Output Delay t

Latch Minimum Pulse Width t

DC OUTPUT CHARACTERISTICS

ADCMP580 (CML)

Output Impedance Z

Output Voltage High Level V

Output Voltage Low Level V

Output Voltage Differential 50 Ω to GND 350 400 450 mV

Temperature Coefficient, V

Temperature Coefficient, V

ADCMP581 (NECL)

Output Voltage High Level V

Output Voltage Low Level V

Output Voltage Differential 50 Ω to −2.0 V 350 400 450 mV

= +3.3 V, TA = 25°C, unless otherwise noted.

CCO

N

OS

N

N

V

S

H

S

H

S

H

, t

PLOH

PLOL

PL

OUT

OH

OL

OH

OL

∆VOH/d

∆VOL/d

OH

OL

−2.0 +3.0 V

−5.0 ±2.0 +5.0 mV

10.0 µV/°C

T

Open termination 15.0 30.0 µA

TBD pF

48 dB

= ∞ ±1 mV

HYS

VOD = 100 mV 60 ps

VOD = 100 mV 0 ps

VOD = 100 mV 25 ps

VOD = 100 mV 0 ps

VOD = 100 mV 5 ps

VOD = 100 mV 0 ps

VOD = 100 mV 150 ps

VOD = 100 mV 100 ps

47.5 50 52.5 Ω

50 Ω to GND −0.10 −0.05 0.00 V

50 Ω to GND VOH − 0.45 VOH − 0.40 VOH − 0.35 V

50 Ω to GND TBD mV/°C

T

50 Ω GND TBD mV/°C

T

50 Ω to −2.0 V −0.90 −0.80 −0.70 V

50 Ω to −2.0 V VOH − 0.45 VOH − 0.40 VOH − 0.35 V

− 1.8 V

CCO

− 0.8 V

CCO

Rev. PrA | Page 3 of 16

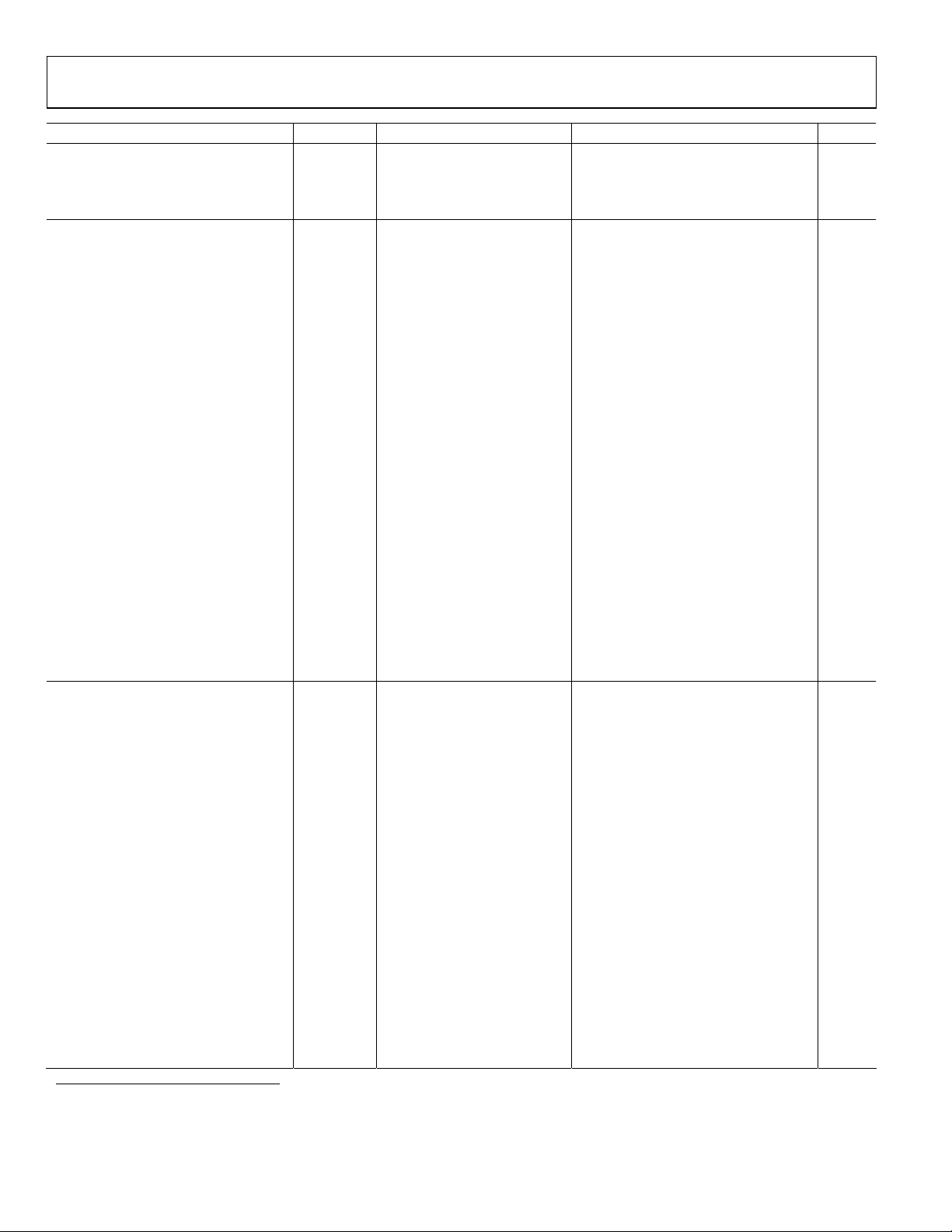

Preliminary Technical Data ADCMP580/ADCMP581/ADCMP582

Parameter Symbol Condition Min Typ Max Unit

ADCMP582 (PECL)

Output Voltage High Level V

Output Voltage Low Level V

OH

OL

Output Voltage Differential 50 Ω to V

AC PERFORMANCE

Propagation Delay t

PD

Propagation Delay VOD = 20 mV 165 ps

Propagation Delay Tempco ∆tPD/d

Prop Delay Skew—Rising Transition

T

V

to Falling Transition

Overdrive Dispersion 50 mV < VOD < 1.0 V 10 ps

5 mV < VOD < 1.0 V 15 ps

Slew Rate Dispersion 2 V/ns to 10 V/ns 25 ps

Pulse Width Dispersion 100 ps to 5 ns 5 ps

Duty Cycle Dispersion 1.0 V/ns, VCM = 0.0 V 10 ps

1.0 V/ns, VCM = 2.0 V 5 ps

Common-Mode Dispersion VOD = 0.4V , −2 V < VCM < 3 V 5 ps/V

Equivalent Input Bandwidth

1

BW

EQ

Toggle Rate >50% Output Swing 12.5 Gbps

Deterministic Jitter DJ

Deterministic Jitter DJ

RMS Random Jitter RJ VOD = 200 mV, 5 V/ns, 1.25 GHz 0.2 ps

Minimum Pulse Width PW

Minimum Pulse Width PW

Rise Time t

Fall Time t

MIN

MIN

R

F

POWER SUPPLY

Positive Supply Voltage V

Negative Supply Voltage V

Logic Supply Voltage V

CCI

EE

CCO

ADCMP580 (CML)

Positive Supply Current I

Negative Supply Current I

Power Dissipation P

ADCMP581 (NECL)

Positive Supply Current I

Negative Supply Current I

Power Dissipation P

VCCI

VEE

D

VCCI

VEE

D

ADCMP582 (PECL)

Positive Supply Current I

Negative Supply Current I

Power Dissipation P

Power Supply Rejection (V

) PSR

CCI

VCCI

VEE

+ I

D

VCCI

50 Ω to V

50 Ω to V

− 2.0 V V

CCO

− 2.0 V VOH − 0.45 VOH − 0.40 VOH − 0.35 V

CCO

− 2.0 V 350 400 450 mV

CCO

− 0.9 V

CCO

− 0.80 V

CCO

− 0.70 V

CCO

VOD = 200 mV 150 ps

0.5 ps/°C

= 200 mV, 5 V/ns 10 ps

OD

0.0 V to 400 mV input

= tF = 25 ps, 20/80

t

R

= 200 mV, 5 V/ns

V

OD

31

− 1 NRZ, 4 Gbps

PRBS

= 200 mV, 5 V/ns

V

OD

31

− 1 NRZ, 10 Gbps

PRBS

8.0 GHz

10 ps

TBD ps

tPD/PW < 5 ps 100 ps

tPD/PW < 10 ps 80 ps

20/80 35 ps

20/80 35 ps

+4.5 +5.0 +5.5 V

−5.5 −5.0 −4.5 V

+4.5/+2.0 +5.0/+2.5 +5.5/+3.0 V

V

= +5.0 V, 50 Ω to Ground 6 8 mA

CCI

VEE = −5.0 V, 50 Ω to Ground 43 50 mA

50 Ω to Ground 244 260 mW

V

= +5.0 V, 50 Ω to −2 V 6 8 mA

CCI

VEE = −5.0 V, 50 Ω to −2 V 28 35 mA

50 Ω to −2 V 218 240 mW

V

VCCO

= +5.0 V, V

CCI

50 Ω to V

VEE = −5.0 V, 50 Ω to V

50 Ω to V

V

=5.0 V + 5% 70 dB

CCI

= +5.0 V

CCO

− 2 V

CCO

− 2 V 28 35 mA

CCO

− 2 V 253 275 mW

CCO

47 55 mA

Power Supply Rejection (VEE) PSR

Power Supply Rejection (V

) PSR

CCO

VEE

VCCO

VEE=-5.0 V + 5% 75 dB

V

=3.3 V + 5% 70 dB

CCO

1

Equivalent Input Bandwidth assumes a simple first-order input response and is calculated with the following formula: BW

is the 20/80 transition time of a quasi-Gaussian input edge applied to the comparator input and tr

comparator.

Rev. PrA | Page 4 of 16

is the effective transition time digitized by the

COMP

= 0.22/√(tr

EQ

COMP

2

– tr

2

), where trIN

IN

Preliminary Technical Data ADCMP580/ADCMP581/ADCMP582

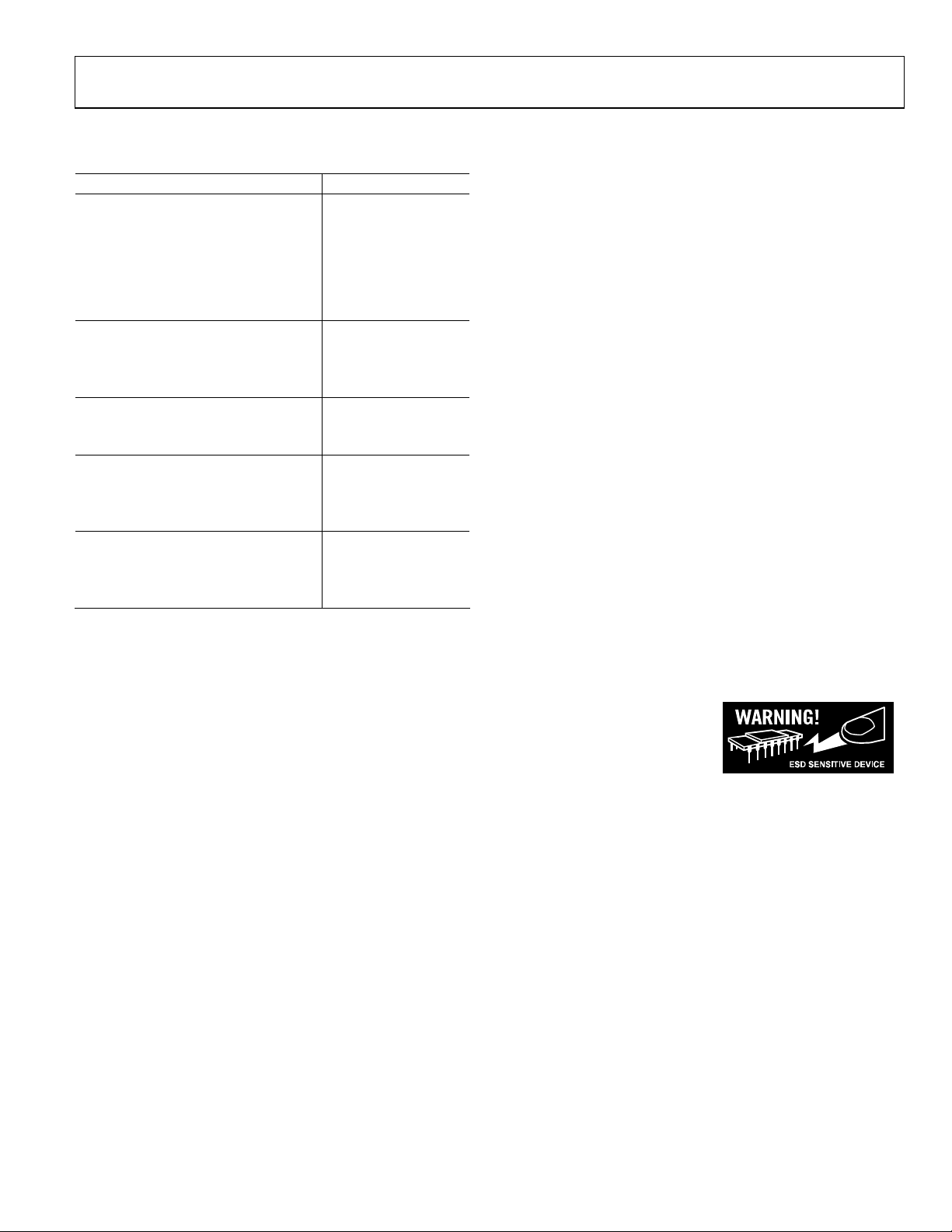

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

SUPPLY VOLTAGES

Positive Supply Voltage

(V

to GND)

CCI

Negative Supply Voltage

to GND)

(V

EE

Logic Supply Voltage

to GND)

(V

CCO

INPUT VOLTAGES

Input Voltage −3.0 V to +4.0 V

Differential Input Voltage −2.5 V to +2.5 V

Input Voltage, Latch Enable −2.5 V to +5.5 V

HYSTERESIS CONTROL PIN

Applied Voltage (HYS to VEE) −5.5 V to +0.5 V

Maximum Input/Output Current 1 mA

OUTPUT CURRENT

ADCMP580 (CML) −25 mA

ADCMP581 (NECL) −40 mA

ADCMP582 (PECL) −40 mA

TEMPERATURE

Operating Temperature, Ambient −40°C to +85°C

Operating Temperature, Junction 125°C

Storage Temperature Range −65°C to +150°C

−0.5 V to +6.0 V

–6.0 V to +0.5 V

−0.5 V to +6.0 V

THERMAL CONSIDERATIONS

The ADCMP580/ADCMP581/ADCMP582 LFCSP 16-lead

package option has a θJA (junction to ambient thermal

resistance) of 70°C/W in still air.

Stress above those listed under Absolute Maximum Ratings may

cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device

reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. PrA | Page 5 of 16

Loading...

Loading...