A

www.BDTIC.com/ADI

Dual, High Speed ECL Comparators

FEATURES

Differential ECL-compatible outputs

700 ps propagation delay input to output

75 ps propagation delay dispersion

Input common-mode range: –2.0 V to +3.0 V

Robust input protection

Differential latch control

Internal latch pull-up resistors

Power supply rejection greater than 85 dB

700 ps minimum pulse width

1.5 GHz equivalent input rise time bandwidth

Typical output rise/fall time of 500 ps

ESD protection > 4kV HBM, >200V MM

Programmable hysteresis

APPLICATIONS

Automatic test equipment

High speed instrumentation

Scope and logic analyzer front ends

Window comparators

High speed line receivers

Threshold detection

Peak detection

High speed triggers

Patient diagnostics

Hand-held test instruments

Zero crossing detectors

Line receivers and signal restoration

Clock drivers

GENERAL DESCRIPTION

The ADCMP563/ADCMP564 are high speed comparators

fabricated on Analog Devices’ proprietary XFCB process. The

devices feature a 700 ps propagation delay with less than 75 ps

overdrive dispersion. Dispersion, a measure of the difference in

propagation delay under differing overdrive conditions, is a

particularly important characteristic of high speed comparators.

A separate programmable hysteresis pin is available on the

ADCMP564.

A differential input stage permits consistent propagation delay

wi

th a wide variety of signals in the common-mode range from

−2.0 V to +3.0 V. Outputs are complementary digital signals

ADCMP563/ADCMP564

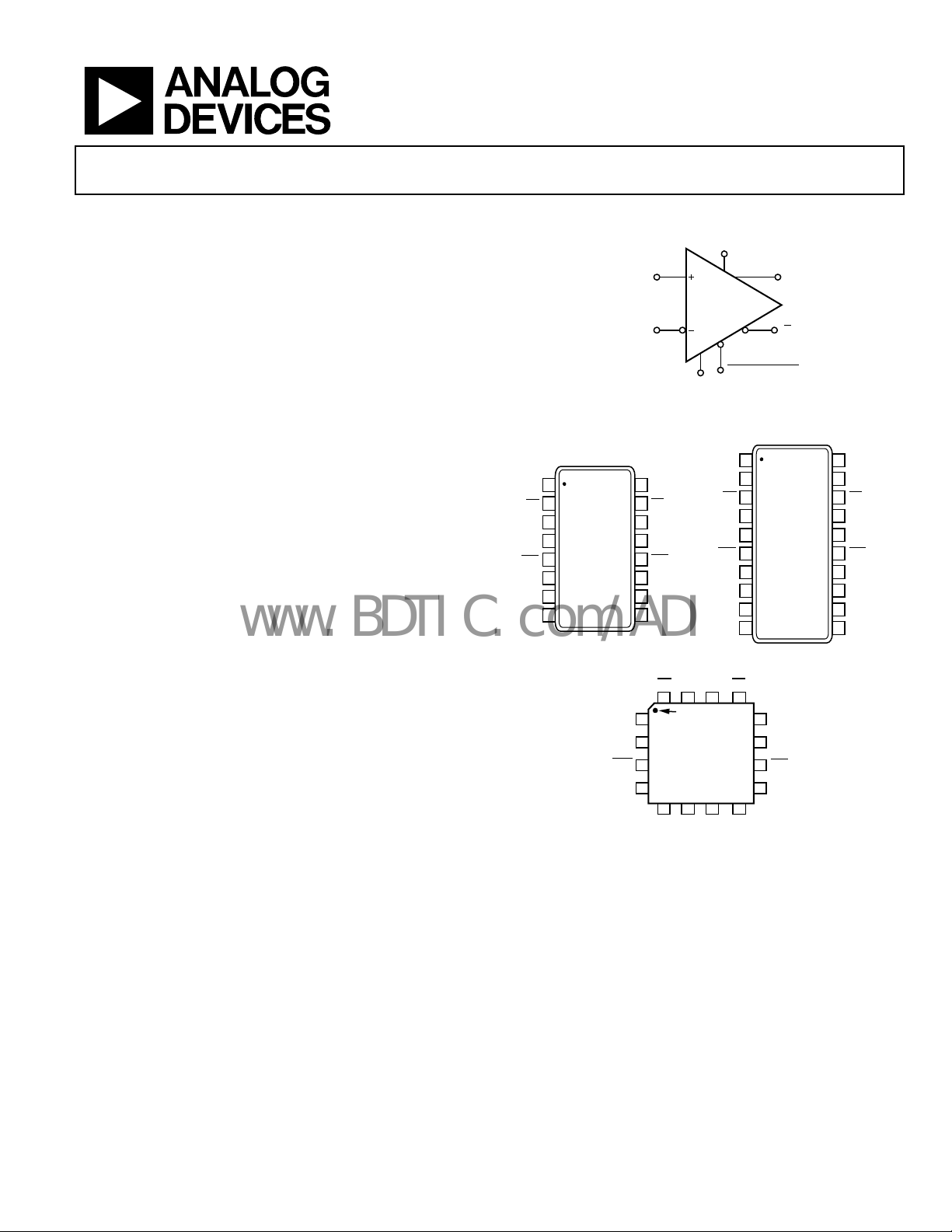

FUNCTIONAL BLOCK DIAGRAM

HYS*

NONINVERTING

INPUT

ADCMP563/

INVERTING

INPUT

LATCH ENABLE

INPUT

ADCMP564

LATCH ENABLE

INPUT

*ADCMP564 ONLY

Figure 1.

GND

04650-0-002

GND

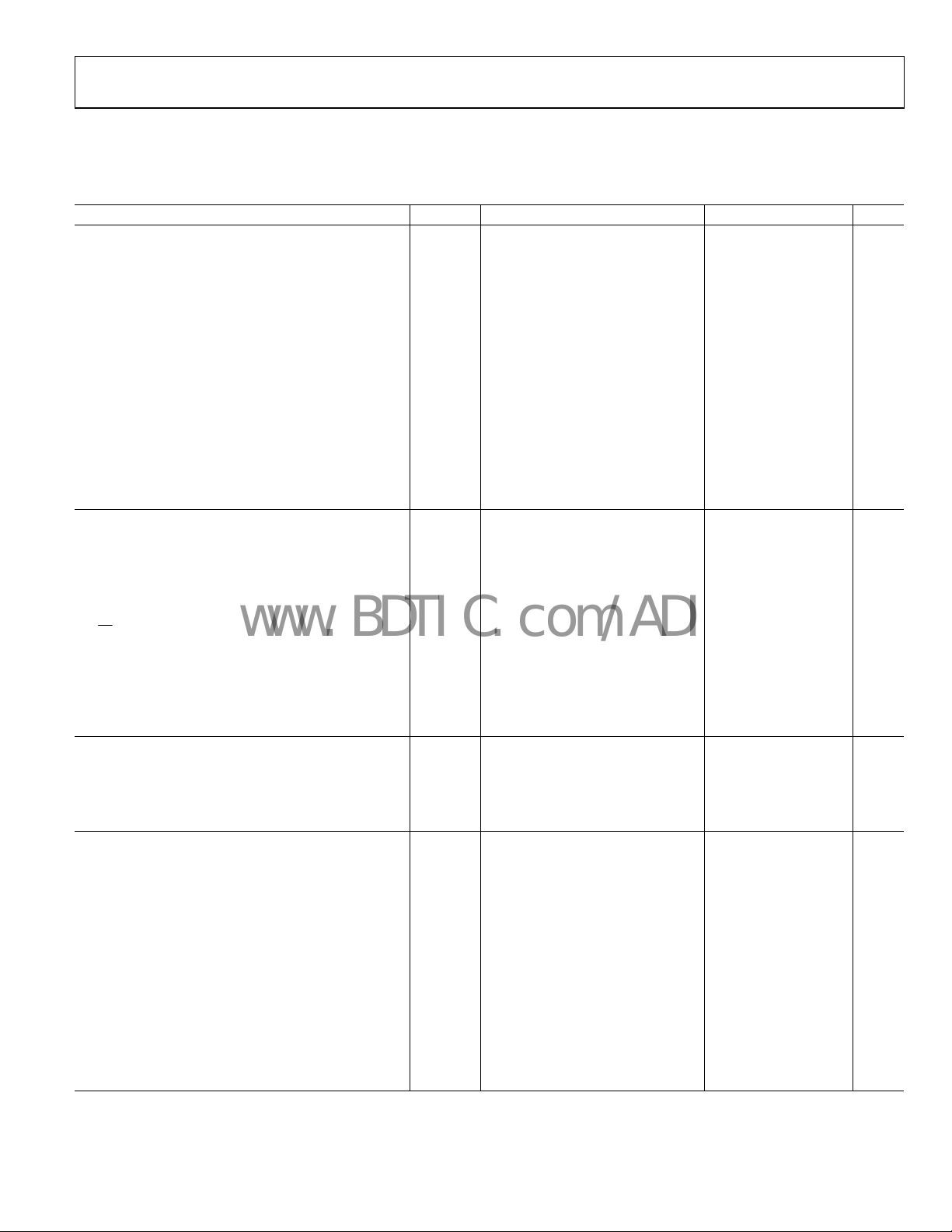

–INA

+INA

HYS

QA

QA

LEA

LEA

V

EE

QA

QA

GND

LEA

LEA

V

–INA

+INA

1

2

3

4

5

6

EE

7

8

ADCMP563

BRQ

TOP VIEW

(Not to Scale)

16

QB

15

QB

14

GND

13

LEB

12

LEB

11

V

CC

–INB

10

+INB

9

Figure 2. ADCMP563 16-Lead QSOP Figure 3. ADCMP564 20-Lead QSOP

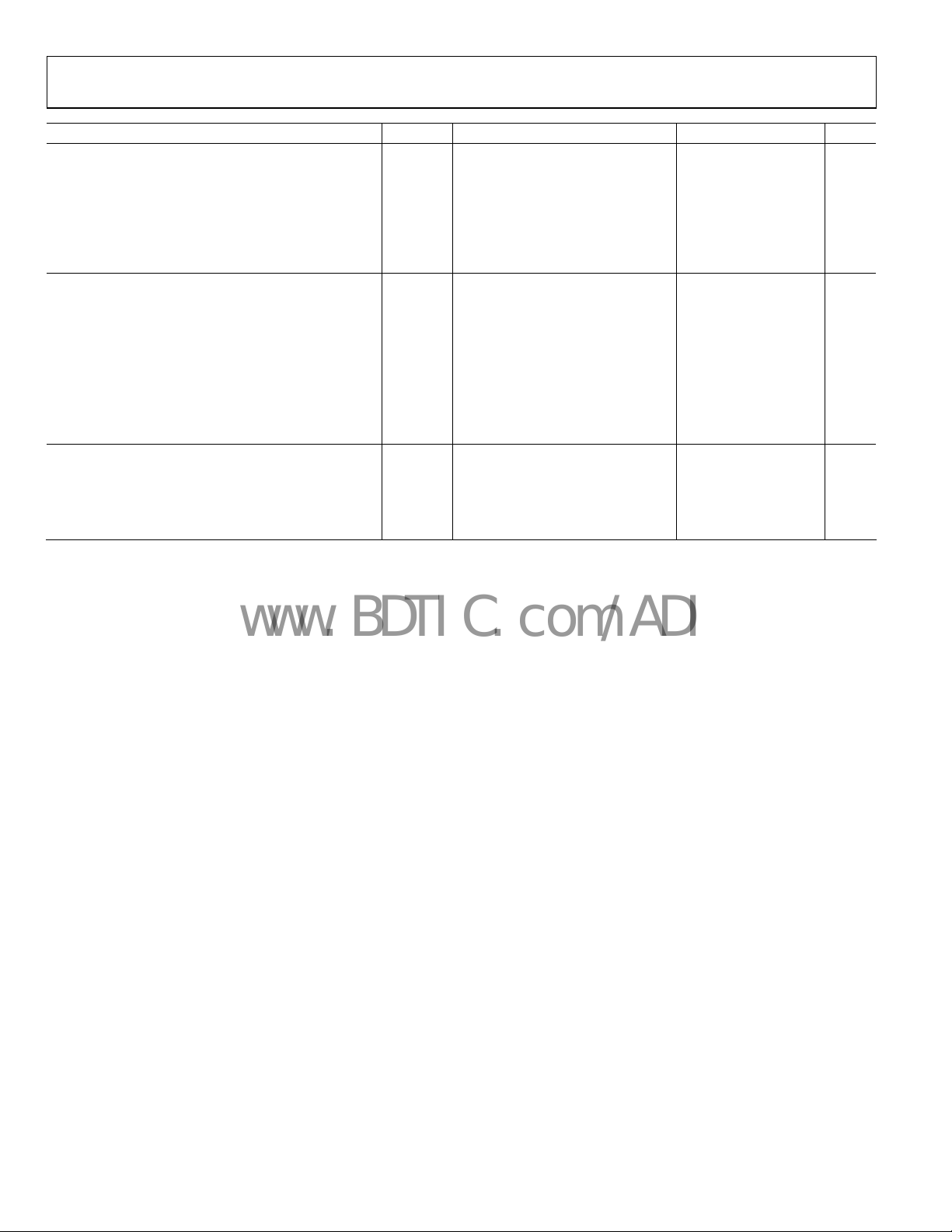

QA QA QB QB

16 15 14 13

GND

LEA

LEA

V

EE

PIN1

1

ADCMP563

2

3

4

BCP

TOP VIEW

(Not to Scale)

–INA +INA +INB –INB

8765

Figure 4. ADCMP563 16-Lead LFCSP

that are fully compatible with ECL 10 K and 10 KH logic

families. The outputs provide sufficient drive current to directly

drive transmission lines terminated in 50 Ω to −2 V. A latch

input, which is included, permits tracking, track-and-hold, or

sample-and-hold modes of operation. The latch input pins

contain internal pull-ups that set the latch in tracking mode

when left open.

The ADCMP563/ADCMP564 are specified over the industrial

emperature range (−40°C to +85°C).

t

1

2

3

ADCMP564

4

BRQ

5

TOP VIEW

(Not to Scale)

6

7

8

9

10

GND

12

LEB

11

LEB

10

9

V

CC

Q OUTPUT

Q OUTPUT

111151-0-026

04650-0-001

GND

20

QB

19

QB

18

GND

17

LEB

16

LEB

15

V

14

–INB

13

+INB

12

HYSB

11

CC

04650-0-012

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2005 Analog Devices, Inc. All rights reserved.

ADCMP563/ADCMP564

www.BDTIC.com/ADI

TABLE OF CONTENTS

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

Thermal Considerations.............................................................. 5

ESD Caution.................................................................................. 5

Pin Configurations and Function Descriptions ........................... 6

Typical Performance Characteristics ............................................. 8

Timing Information ....................................................................... 10

Application Information................................................................ 11

REVISION HISTORY

5/05—Rev. A to Rev. B

Added 16-Lead LFCSP.......................................................Universal

Changes to Applications .................................................................. 1

Changes to Table 1............................................................................ 3

Changes to Optimizing High Speed Performance Section....... 11

Changes to Comparator Hysteresis Section................................ 12

Changes to Minimum Input Slew Rate Requirement Section.. 12

Changes to Ordering Guide.......................................................... 14

Clock Timing Recovery............................................................. 11

Optimizing High Speed Performance ..................................... 11

Comparator Propagation Delay Dispersion ........................... 11

Comparator Hysteresis .............................................................. 12

Minimum Input Slew Rate Requirement ................................ 12

Typical Application C i r c uits ......................................................... 13

Outline Dimensions ....................................................................... 14

Ordering Guide .......................................................................... 14

7/04—Rev. 0 to Rev. A

hanges to Specification Table ....................................................... 4

C

Changes to Figure 14........................................................................ 9

Changes to Figure 21...................................................................... 12

Changes to Figure 23...................................................................... 13

4/04—Revision 0: Initial Version

Rev. B | Page 2 of 16

ADCMP563/ADCMP564

www.BDTIC.com/ADI

SPECIFICATIONS

VCC = +5.0 V, VEE = −5.2 V, TA = −40°C to +85°C. Typical values are at TA = +25°C, unless otherwise noted.

Table 1. Electrical Characteristics

Parameter Symbol Conditions Min Typ Max Unit

DC INPUT CHARACTERISTICS

Input Voltage Range −2.0 3.0 V

Input Differential Voltage −5 +5 V

Input Offset Voltage V

OS

Input Offset Voltage Channel Matching ±2.0 mV

Offset Voltage Temperature Coefficient ∆VOS/d

Input Bias Current I

BC

Input Bias Current Temperature Coefficient 0.5 nA/°C

Input Offset Current ±1.0 μA

Input Capacitance C

IN

Input Resistance, Differential Mode 750 kΩ

Input Resistance, Common Mode 1800 kΩ

Active Gain A

V

Common-Mode Rejection Ratio CMRR VCM = −2.0 V to +3.0 V 80 dB

Hysteresis R

LATCH ENABLE CHARACTERISTICS

Latch Enable Voltage Range −2.0 0 V

Latch Enable Differential Input Voltage 0.4 2.0 V

Latch Enable Input High Current @ 0.0 V −300 +300 μA

Latch Enable Input Low Current @ −2.0 V −300 +300 μA

LE Voltage, Open Latch inputs not connected −0.2 0 +0.1 V

LE Voltage, Open

Latch Setup Time t

Latch Hold Time t

Latch to Output Delay

Latch Minimum Pulse Width t

Latch inputs not connected −2.8 −2.6 −2.4 V

S

H

t

PLOH

t

PLOL

PL

DC OUTPUT CHARACTERISTICS

Output Voltage—High Level V

Output Voltage—Low Level V

Rise Time t

Fall Time t

OH

OL

R

F

AC PERFORMANCE

Propagation Delay t

PD

V

Propagation Delay Temperature Coefficient ∆tPD /d

Prop Delay Skew—Rising Transition to Falling

V

Transition

Within Device Propagation Delay Skew—

V

Channel-to-Channel

Overdrive Dispersion 20 mV ≤ VOD ≤ 100 mV 75 ps

100 mV ≤ VOD ≤ 1.5 V 75 ps

Slew Rate Dispersion 0.4 V/ns ≤ SR ≤ 1.33 V/ns 50 ps

Pulse Width Dispersion 750ps ≤ PW ≤ 10ns 25 ps

Duty Cycle Dispersion 33 MHz, 1 V/ns, 0.5 V 10 ps

Common-Mode Voltage Dispersion 1 V swing, −1.5 V ≤ VCM ≤ +2.5 V 10 ps

VCM = 0 V −10.0 ±2.0 +10.0 mV

2.0 μV/°C

T

@ −IN = −2 V, +IN = +3 V −10.0 ±3 +10.0 μA

0.75 pF

63 dB

= ∞ ±1.0 mV

HYS

VOD = 250 mV 200 ps

VOD = 250 mV 200 ps

VOD = 250 mV 500 ps

,

VOD = 250 mV 500 ps

ECL 50 Ω to −2.0 V −1.15 −0.81 V

ECL 50 Ω to −2.0 V −1.95 −1.54 V

10% to 90% 530 ps

10% to 90% 450 ps

VOD = 1 V 700 ps

= 20 mV 830 ps

OD

VOD = 1 V 0.25 ps/°C

T

= 1 V 50 ps

OD

= 1 V 50 ps

OD

Rev. B | Page 3 of 16

ADCMP563/ADCMP564

www.BDTIC.com/ADI

Parameter Symbol Conditions Min Typ Max Unit

AC PERFORMANCE (Continued)

Equivalent Input Rise Time Bandwidth

Maximum Toggle Rate >50% output swing, 50% duty cycle 800 MHz

Minimum Pulse Width PW

RMS Random Jitter

Unit to Unit Propagation Delay Skew 100 ps

POWER SUPPLY

Positive Supply Current I

Negative Supply Current I

Positive Supply Voltage V

Negative Supply Voltage V

Power Dissipation P

Dual, with load 150 180 230 mW

DC Power Supply Rejection Ratio—V

DC Power Supply Rejection Ratio—V

HYSTERESIS (ADCMP564 Only)

Hysteresis R

R

Hysteresis Pin Bias Voltage Referred to AGND −1 V

Hysteresis Pin Series Resistance 3 kΩ

1

Equivalent input rise time bandwidth assumes a first-order input response and is calculated by the following formula: BWEQ = 0.22/√(tr

20/80 input transition time applied to the comparator and tr is the effective transition time, as digitized by the comparator input.

1

BW

EQ

MIN

0 V to 1 V swing, 2 V/ns 1500 MHz

ΔtPD < 25 ps 700 ps

= 400 mV, 1.3 V/ns, 312 MHz,

V

OD

1.0 ps

50% duty cycle

VCC

VEE

CC

EE

D

CC

EE

PSRR

PSRR

COMP

@ +5.0 V 2 3.2 5 mA

@ −5.2 V 10 19 25 mA

Dual 4.75 5.0 5.25 V

Dual −4.96 −5.2 −5.45 V

Dual, without load 90 120 150 mW

85 dB

VCC

85 dB

VEE

= 23.5 kΩ 20 mV

HYS

= 9.0 kΩ 70 mV

HYS

2

2

P

– tr

COMP

), where tr is the

IN

IN

Rev. B | Page 4 of 16

ADCMP563/ADCMP564

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltages

Positive Supply Voltage (VCC to GND) −0.5 V to +6.0 V

Negative Supply Voltage (VEE to GND) −6.0 V to +0.5 V

Ground Voltage Differential −0.5 V to +0.5 V

Input Voltages

Input Common-Mode Voltage −3.0 V to +4.0 V

Differential Input Voltage −7.0 V to +7.0 V

Input Voltage, Latch Controls VEE to +0.5 V

Output

Output Current 30 mA

Temperature

Operating Temperature, Ambient −40°C to +85°C

Operating Temperature, Junction 125°C

Storage Temperature Range −65°C to +150°C

S

tresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to

absolute maximum rating conditions for extended periods may

affect device reliability.

THERMAL CONSIDERATIONS

The ADCMP563 QSOP 16-lead package option has a θJA

(junction-to-ambient thermal resistance) of 104°C/W in

still air.

The ADCMP563 LFCSP 16-lead package option has a θ

(junction-to-ambient thermal resistance) of 70°C/W in

still air.

The ADCMP564 QSOP 20-lead package option has a θ

(junction-to-ambient thermal resistance) of 80°C/W in

still air.

JA

JA

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. B | Page 5 of 16

Loading...

Loading...