Precision, Ultralow Noise, RRIO,

–

Data Sheet

FEATURES

Low offset: 2.5 µV maximum

Low offset voltage drift: 0.015 V/°C maximum

Low noise

5.6 nV/√Hz at f = 1 kHz, A

97 nV p-p at f = 0.1 Hz to 10 Hz, A

Open-loop voltage gain: 130 dB minimum

CMRR: 135 dB minimum

PSRR: 130 dB minimum

Gain bandwidth product: 4 MHz

Single-supply operation: 2.2 V to 5.5 V

Dual-supply operation: ±1.1 V to ±2.75 V

Rail-to-rail input and output

Unity-gain stable

APPLICATIONS

Thermocouple/thermopile

Load cell and bridge transducer

Precision instrumentation

Electronic scales

Medical instrumentation

Handheld test equipment

= +100

V

= +100

V

Zero-Drift Op Amp

ADA4528-1

PIN CONFIGURATIONS

NC

1

ADA4528-1

2

IN

TOP VIEW

3

+IN

(Not to Scale)

V–

4

NC = NO CONNECT. DO NOT

CONNECT TO THIS PIN.

Figure 1. 8-Lead MSOP

1NC

ADA4528-1

2–IN

TOP VIEW

3+IN

(Not to Scale)

4V–

NOTES

1. NC = NO CONNECT. DO NOT CONNECT

TO THIS PIN.

2. IT I S RECOMMENDED T HAT THE

EXPOSED PAD BE CONNECT ED TO V–.

Figure 2. 8-Lead LFCSP

NC

8

7

V+

6

OUT

NC

5

8NC

7V+

6OUT

5NC

09437-001

09437-102

GENERAL DESCRIPTION

The ADA4528-1 is an ultralow noise, zero-drift operational amplifier featuring rail-to-rail input and output swing. With an

offset voltage of 2.5 V, offset voltage drift of 0.015 V/°C, and

typical noise of 97 nV p-p (0.1 Hz to 10 Hz, A

ADA4528-1 is well suited for applications in which error sources

cannot be tolerated.

The ADA4528-1 has a wide operating supply range of 2.2 V to

5.5 V, high gain, and excellent CMRR and PSRR specifications

that make it ideal for precision amplification of low level signals,

such as position and pressure sensors, strain gages, and medical

instrumentation.

The ADA4528-1 is specified over the extended industrial

temperature range (−40°C to +125°C) and is available in an

8-lead MSOP and an 8-lead LFCSP package.

For more information on the ADA4528-1, refer to AN-1114

Lowest Noise Zero-Drift Amplifier Has 5.6 nV/√Hz Voltage Noise

Density.

= +100), the

V

Table 1. Analog Devices, Inc., Zero-Drift Op Amp Portfolio1

Typ e

Ultralow

Noise

Micropower

(<20 µA)

Low

Power

(<1 mA)

16 V

Operating

Voltage

Single ADA4528-1 ADA4051-1 AD8628 AD8638

AD8538

Dual ADA4051-2 AD8629 AD8639

AD8539

Quad AD8630

1

See www.analog.com for a selection of zero-drift operational amplifiers.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADA4528-1 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Pin Configurations........................................................................... 1

General Description......................................................................... 1

Revision History ...............................................................................2

Specifications..................................................................................... 3

Electrical Characteristics—2.5 V Operation ............................ 3

Electrical Characteristics—5 V Operation................................ 4

Absolute Maximum Ratings............................................................ 5

Thermal Resistance...................................................................... 5

REVISION HISTORY

9/11—Rev. 0 to Rev. A

Added 8-Lead LFCSP_WD Package................................Universal

Changes to General Description Section ..................................... 1

Added Figure 2; Renumbered Sequentially .................................. 1

Changes to Offset Voltage, Offset Voltage Drift, Power Supply

Rejection Ratio, and Settling Time to 0.1% Parameters,

Table 2 ................................................................................................ 3

Changes to Thermal Resistance Section and Table 5................... 5

Changes to Figure 41 and Figure 44............................................. 12

Changes to Figure 45 and Figure 48............................................. 13

Updated Outline Dimensions....................................................... 18

Changes to Ordering Guide.......................................................... 18

1/11—Revision 0: Initial Version

ESD Caution...................................................................................5

Typical Performance Characteristics..............................................6

Applications Information.............................................................. 15

Input Protection ......................................................................... 15

Rail-to-Rail Input and Output.................................................. 15

Noise Considerations................................................................. 15

Printed Circuit Board Layout................................................... 17

Outline Dimensions....................................................................... 18

Ordering Guide .......................................................................... 18

Rev. A | Page 2 of 20

Data Sheet ADA4528-1

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS—2.5 V OPERATION

VS = 2.5 V, VCM = VSY/2 V, TA = 25°C, unless otherwise specified.

Table 2.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS V

−40°C ≤ TA ≤ +125°C; MSOP package 4 V

−40°C ≤ TA ≤ +125°C; LFCSP package 4.3 V

Offset Voltage Drift ∆VOS/∆T −40°C ≤ TA ≤ +125°C; MSOP package 0.002 0.015 V/°C

−40°C ≤ TA ≤ +125°C; LFCSP package 0.018 V/°C

Input Bias Current IB 220 400 pA

−40°C ≤ TA ≤ +125°C 600 pA

Input Offset Current IOS 440 800 pA

−40°C ≤ TA ≤ +125°C 1 nA

Input Voltage Range 0 2.5 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 2.5 V 135 158 dB

−40°C ≤ TA ≤ +125°C 116 dB

Open-Loop Gain AVO R

−40°C ≤ TA ≤ +125°C 126 dB

R

−40°C ≤ TA ≤ +125°C 121 dB

Input Resistance, Differential Mode R

Input Resistance, Common Mode R

Input Capacitance, Differential Mode C

Input Capacitance, Common Mode C

225 kΩ

INDM

1 GΩ

INCM

15 pF

INDM

30 pF

INCM

OUTPUT CHARACTERISTICS

Output Voltage High VOH R

−40°C ≤ TA ≤ +125°C 2.485 V

R

−40°C ≤ TA ≤ +125°C 2.44 V

Output Voltage Low VOL R

−40°C ≤ TA ≤ +125°C 15 mV

R

−40°C ≤ TA ≤ +125°C 60 mV

Short-Circuit Current ISC ±30 mA

Closed-Loop Output Impedance Z

f = 1 kHz, AV = +10 0.1 Ω

OUT

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = 2.2 V to 5.5 V 130 150 dB

−40°C ≤ TA ≤ +125°C 127 dB

Supply Current/Amplifier ISY I

−40°C ≤ TA ≤ +125°C 2.1 mA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 10 kΩ, CL = 100 pF, AV = +1 0.45 V/s

Settling Time to 0.1% ts V

Gain Bandwidth Product

GBP R

Phase Margin ΦM R

Overload Recovery Time RL = 10 kΩ, CL = 100 pF, AV = −10 50 s

NOISE PERFORMANCE

Voltage Noise en p-p f = 0.1 Hz to 10 Hz, AV = +100 97 nV p-p

Voltage Noise Density en f = 1 kHz, AV = +100 5.6 nV/√Hz

f = 1 kHz, AV = +100, VCM = 2.0 V 5.5 nV/√Hz

Current Noise in p-p f = 0.1 Hz to 10 Hz, AV = +100 10 pA p-p

Current Noise Density in f = 1 kHz, AV = +100 0.7 pA/√Hz

= 0 V to 2.5 V 0.3 2.5 V

CM

= 10 kΩ, VO = 0.1 V to 2.4 V 130 140 dB

L

= 2 kΩ, VO = 0.1 V to 2.4 V 125 132 dB

L

= 10 kΩ to VCM 2.49 2.495 V

L

= 2 kΩ to VCM 2.46 2.48 V

L

= 10 kΩ to VCM 5 10 mV

L

= 2 kΩ to VCM 20 40 mV

L

= 0 mA 1.4 1.7 mA

O

= 1.5 V step, RL = 10 kΩ, CL = 100 pF, AV = −1 7 µs

IN

= 10 kΩ, CL = 100 pF, AV = +1

L

= 10 kΩ, CL = 100 pF, AV = +1 57 Degrees

L

4

MHz

Rev. A | Page 3 of 20

ADA4528-1 Data Sheet

ELECTRICAL CHARACTERISTICS—5 V OPERATION

VS = 5 V, VCM = VSY/2 V, TA = +25°C, unless otherwise specified.

Table 3.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS V

−40°C ≤ TA ≤ +125°C 4 V

Offset Voltage Drift ∆VOS/∆T −40°C ≤ TA ≤ +125°C 0.002 0.015 V/°C

Input Bias Current IB 90 200 pA

−40°C ≤ TA ≤ +125°C 300 pA

Input Offset Current IOS 180 400 pA

−40°C ≤ TA ≤ +125°C 500 pA

Input Voltage Range 0 5 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 5 V 137 160 dB

−40°C ≤ TA ≤ +125°C 122 dB

Open-Loop Gain AVO R

−40°C ≤ TA ≤ +125°C 125 dB

R

−40°C ≤ TA ≤ +125°C 120 dB

Input Resistance, Differential Mode R

Input Resistance, Common Mode R

Input Capacitance, Differential Mode C

Input Capacitance, Common Mode C

190 kΩ

INDM

1 GΩ

INCM

16.5 pF

INDM

33 pF

INCM

OUTPUT CHARACTERISTICS

Output Voltage High VOH R

−40°C ≤ TA ≤ +125°C 4.98 V

R

−40°C ≤ TA ≤ +125°C 4.94 V

Output Voltage Low VOL R

−40°C ≤ TA ≤ +125°C 20 mV

R

−40°C ≤ TA ≤ +125°C 60 mV

Short-Circuit Current ISC ±40 mA

Closed-Loop Output Impedance Z

f = 1 kHz, AV = +10 0.1 Ω

OUT

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = 2.2 V to 5.5 V 130 150 dB

−40°C ≤ TA ≤ +125°C 127 dB

Supply Current/Amplifier ISY I

−40°C ≤ TA ≤ +125°C 2.2 mA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 10 kΩ, CL = 100 pF, AV = +1 0.5 V/s

Settling Time to 0.1% ts V

Gain Bandwidth Product

GBP R

Phase Margin ΦM R

Overload Recovery Time RL = 10 kΩ, CL = 100 pF, AV = −10 50 s

NOISE PERFORMANCE

Voltage Noise en p-p f = 0.1 Hz to 10 Hz, AV = +100 99 nV p-p

Voltage Noise Density en f = 1 kHz, AV = +100 5.9 nV/√Hz

f = 1 kHz, AV = +100, VCM = 4.5 V 5.3 nV/√Hz

Current Noise in p-p f = 0.1 Hz to 10 Hz, AV = +100 10 pA p-p

Current Noise Density in f = 1 kHz, AV = +100 0.5 pA/√Hz

= 0 V to 5 V 0.3 2.5 V

CM

= 10 kΩ, VO = 0.1 V to 4.9 V 127 139 dB

L

= 2 kΩ, VO = 0.1 V to 4.9 V 121 131 dB

L

= 10 kΩ to VCM 4.99 4.995 V

L

= 2 kΩ to VCM 4.96 4.98 V

L

= 10 kΩ to VCM 5 10 mV

L

= 2 kΩ to VCM 20 40 mV

L

= 0 mA 1.5 1.8 mA

O

= 4 V step, RL = 10 kΩ, CL = 100 pF, AV = −1 10 µs

IN

= 10 kΩ, CL = 100 pF, AV = +1

L

= 10 kΩ, CL = 100 pF, AV = +1 57 Degrees

L

4

MHz

Rev. A | Page 4 of 20

Data Sheet ADA4528-1

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage 6 V

Input Voltage ±VSY ± 0.3 V

Input Current1 ±10 mA

Differential Input Voltage ±VSY

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +125°C

Junction Temperature Range −65°C to +150°C

Lead Temperature (Soldering, 60 sec) 300°C

1

The input pins have clamp diodes to the power supply pins. Limit the

input current to 10 mA or less whenever input signals exceed the

power supply rail by 0.5 V.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages. This

was measured using a 4-layer JEDEC thermal board with the

exposed pad soldered to the PCB.

Table 5. Thermal Resistance

Package Type θJA θ

8-Lead MSOP (RM-8) 142 45 °C/W

8-Lead LFCSP (CP-8-12) 80 14 °C/W

Unit

JC

ESD CAUTION

Rev. A | Page 5 of 20

ADA4528-1 Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, unless otherwise noted.

100

VSY = 2.5V

90

V

CM

80

70

60

50

40

30

NUMBER OF AMPLI FIERS

20

10

0

–1.0 –0.6

–0.8 –0.4

60

= VSY/2

00.6

0.2

–0.2

VOS (µV)

0.4 0.8

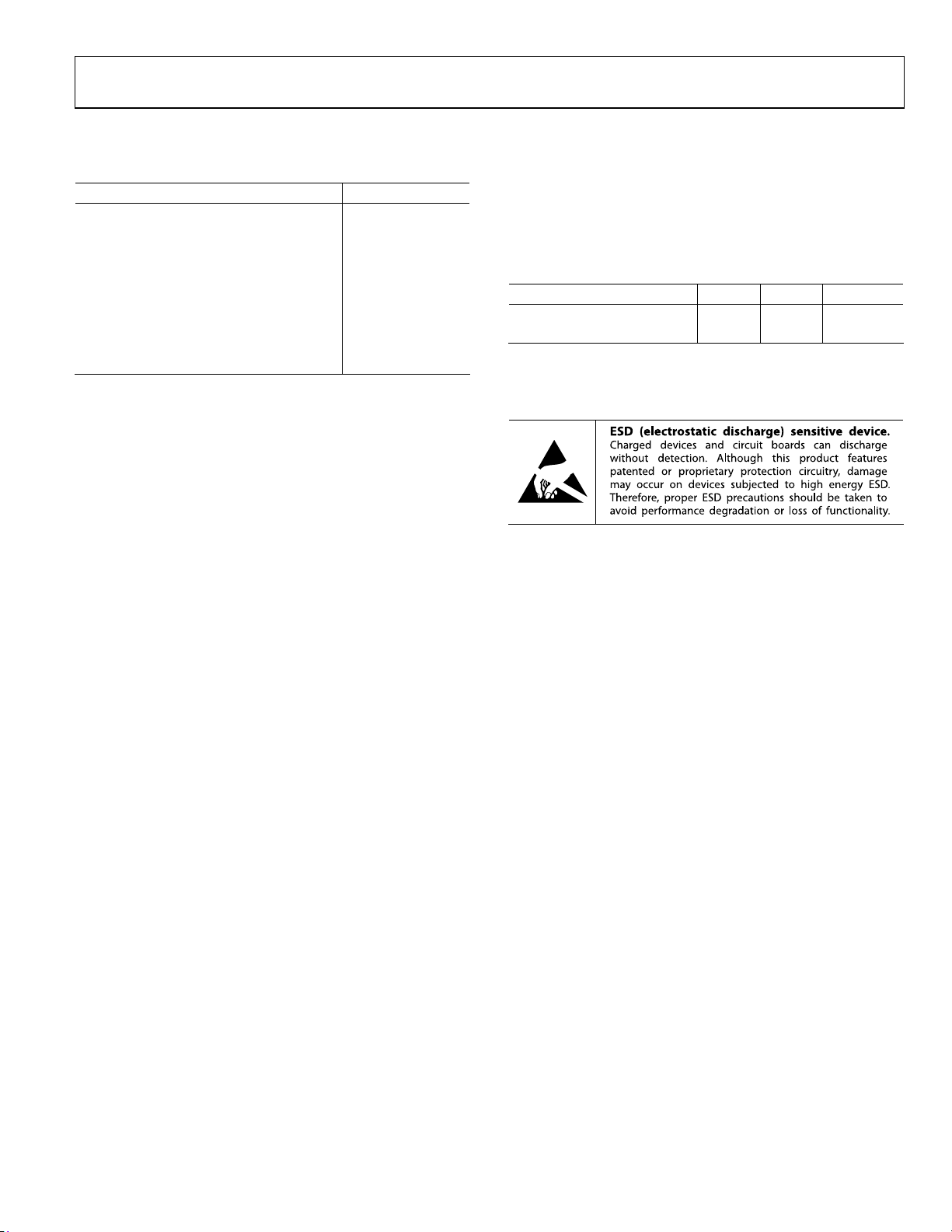

Figure 3. Input Offset Voltage Distribution

1.0

09437-002

100

VSY = 5V

90

V

CM

80

70

60

50

40

30

NUMBER OF AMPLI FIERS

20

10

0

–1.0 –0.6

–0.8 –0.4

60

= VSY/2

00.6

0.2

–0.2

VOS (µV)

0.4 0.8

Figure 6. Input Offset Voltage Distribution

1.0

09437-005

50

40

30

20

NUMBER OF AMPLI FIERS

10

0

09631

TCVOS (nV/°C)

VSY = 2.5V

= VSY/2

V

CM

215

09437-003

Figure 4. Input Offset Voltage Drift Distribution

1.0

VSY = 2.5V

0.8

0.6

0.4

0.2

(µV)

0

OS

V

–0.2

–0.4

–0.6

–0.8

–1.0

00.5

1.0

VCM (V)

1.5

2.0

2.5

09437-004

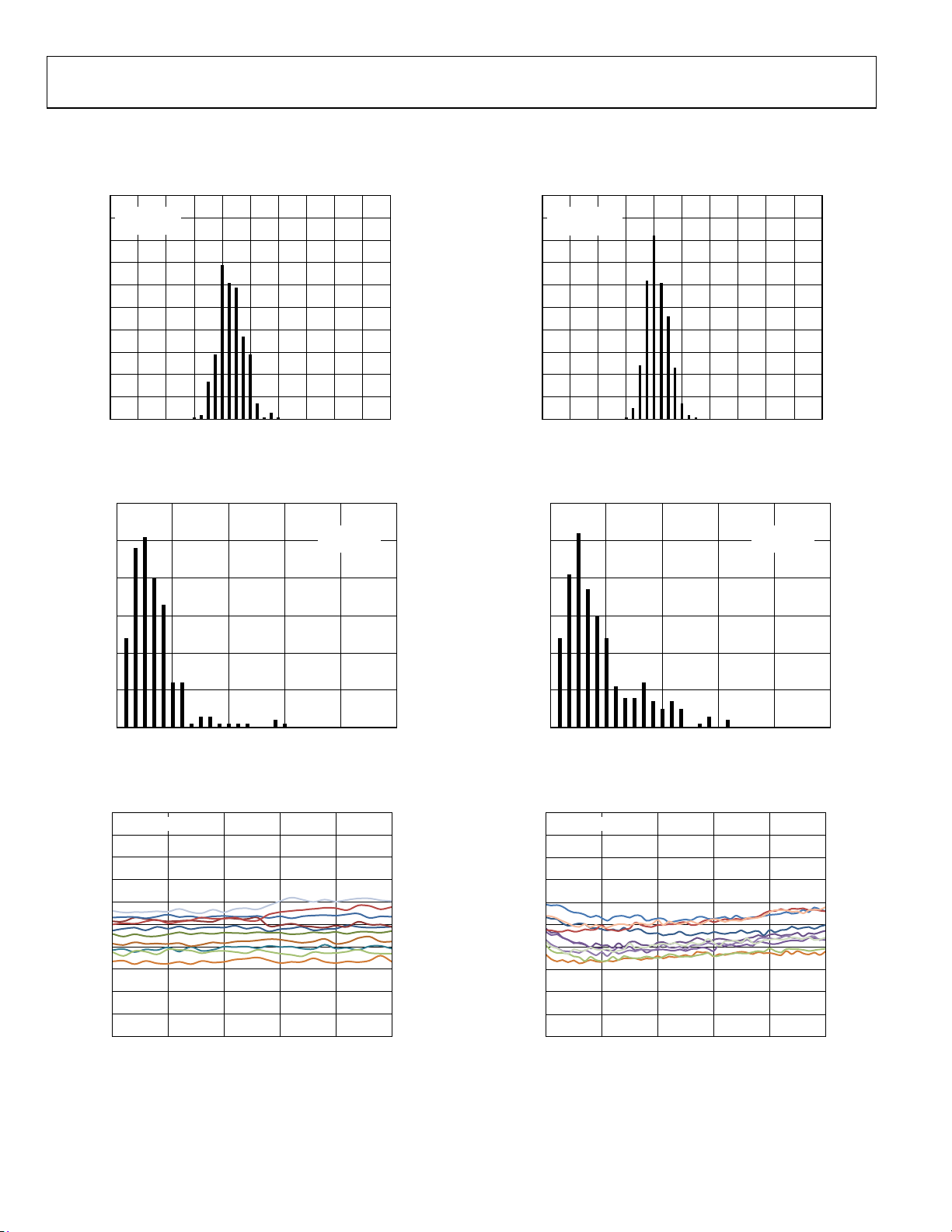

Figure 5. Input Offset Voltage vs. Common-Mode Voltage

50

40

30

20

NUMBER OF AMPLI FIERS

10

0

09631

TCV

OS

(nV/°C)

VSY = 5V

= VSY/2

V

CM

215

09437-006

Figure 7. Input Offset Voltage Drift Distribution

1.0

VSY = 5V

0.8

0.6

0.4

0.2

(µV)

0

OS

V

–0.2

–0.4

–0.6

–0.8

–1.0

01

2

VCM (V)

3

4

5

09437-007

Figure 8. Input Offset Voltage vs. Common-Mode Voltage

Rev. A | Page 6 of 20

Data Sheet ADA4528-1

400

300

200

100

VSY = 2.5V

V

= VSY/2

CM

IB+

400

300

200

100

VSY = 5V

V

= VSY/2

CM

IB+

0

(pA)

B

I

–100

–200

–300

–400

–50 –25 0 25 50 75 100 125

I

–

B

TEMPERATURE (°C)

Figure 9. Input Bias Current vs. Temperature

600

+85°C

400

–40°C

200

+25°C

+125°C

0

(pA)

B

I

–200

–400

VSY = 2.5V

–600

0 0.5 1.0 1.5 2.0 2.5

VCM (V)

Figure 10. Input Bias Current vs. Common-Mode Voltage

10

VSY = 2.5V

1

0

(pA)

B

I

–100

–200

–300

–400

–50 –25 0 25 50 75 100 125

09437-008

–

I

B

TEMPERATURE (°C)

09437-110

Figure 12. Input Bias Current vs. Temperature

600

400

200

0

(pA)

B

I

–200

–400

–600

–800

09437-009

+85°C

–40°C

+25°C

+125°C

VSY = 5V

012345

VCM (V)

09437-012

Figure 13. Input Bias Current vs. Common-Mode Voltage

10

VS = 5V

1

100m

) TO SUPPLY RAIL (V)

OL

10m

1m

OUTPUT VO LTAGE (V

0.1m

0.001

–40°C

+25°C

+85°C

+125°C

Figure 11. Output Voltage (V

0.1 1

LOAD CURRENT (mA)

) to Supply Rail vs. Load Current

OL

100m

) TO SUPPLY RAIL (V)

OL

10m

1m

OUTPUT VOLTAGE (V

10

1000.01

09437-014

0.1m

Figure 14. Output Voltage (V

0.001

–40°C

+25°C

+85°C

+125°C

0.1 1

LOAD CURRENT (mA)

) to Supply Rail vs. Load Current

OL

10

1000.01

09437-017

Rev. A | Page 7 of 20

ADA4528-1 Data Sheet

10

VSY = 2.5V

1

10

VSY = 5V

1

100m

) TO SUPPLY RAIL (V)

OH

10m

1m

OUTPUT VOLT AGE (V

0.1m

Figure 15. Output Voltage (V

0.001

–40°C

+25°C

+85°C

+125°C

0.1 1

LOAD CURRENT (mA)

) to Supply Rail vs. Load Current

OH

10

25

VSY = 2.5V

20

15

) TO SUPPLY RAIL (mV)

OL

10

5

OUTPUT VOLTAGE (V

0

–50–25 0 255075100125

Figure 16. Output Voltage (V

RL = 2kΩ

R

= 10kΩ

L

TEMPERATURE (° C)

) to Supply Rail vs. Temperature

OL

25

V

= 2.5V

SY

20

RL = 2kΩ

0.001

–40°C

+25°C

+85°C

+125°C

0.1 1

LOAD CURRENT (mA)

) to Supply Rail vs. Load Current

OH

10

1000.01

09437-013

100m

) TO SUPPLY RAIL (V)

OH

10m

1m

OUTPUT VOL TAGE (V

1000.01

09437-010

0.1m

Figure 18. Output Voltage (V

45

VSY = 5V

40

35

30

25

) TO SUPPLY RAIL (mV)

OL

20

15

10

5

OUTPUT VOLTAGE (V

0

9437-016

–50 –25 0 25 50 75 100 125

Figure 19. Output Voltage (V

RL = 2kΩ

= 10kΩ

R

L

TEMPERATURE (°C)

) to Supply Rail vs. Temperature

OL

09437-019

25

V

= 5V

SY

20

RL = 2kΩ

15

) TO SUPPLY RAIL (mV)

OH

10

= 10kΩ

R

5

OUTPUT VOLTAGE (V

0

–50–25 0 255075100125

Figure 17. Output Voltage (V

L

TEMPERATURE (° C)

) to Supply Rail vs. Temperature

OH

9437-015

Rev. A | Page 8 of 20

15

) TO SUPPLY RAIL (mV)

OH

10

= 10kΩ

R

5

OUTPUT VOLTAGE (V

0

–50 –25 0 25 50 75 100 125

Figure 20. Output Voltage (V

L

TEMPERATURE (° C)

) to Supply Rail vs. Temperature

OH

9437-117

Data Sheet ADA4528-1

2.00

1.75

1.50

1.25

1.00

0.75

PER AMPLIFIER (mA)

SY

I

0.50

0.25

0

0 0.51.01.52.02.53.03.54.04.55.05.5

+125°C

+85°C

+25°C

–40°C

VSY (V)

Figure 21. Supply Current vs. Supply Voltage

120

90

60

30

OPEN-LOOP GAIN (dB)

VSY = 2.5V

0

R

= 10kΩ

L

C

= 100pF

L

PHASE

GAIN

135

90

45

0

–45

09437-021

PHASE (Degrees)

2.0

1.8

1.6

1.4

PER AMPLIFIER (mA)

SY

I

1.2

1.0

–50 –25 0 25 50 75 100 125

VSY= 5.0V

VSY= 2.5V

TEMPERATURE (°C)

Figure 24. Supply Current vs. Temperature

120

90

60

30

OPEN-LOOP GAIN (dB)

VSY = 5V

0

R

= 10kΩ

L

C

= 100pF

L

PHASE

GAIN

135

90

45

0

–45

09437-024

PHASE (Degrees)

–30

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 22. Open-Loop Gain and Phase vs. Frequency

60

50

40

30

20

10

0

CLOSED-LOOP GAIN (dB)

–10

–20

10 100 1k 10k 100k 1M 10M

AV = 100

= 10

A

V

A

= 1

V

FREQUENCY (Hz)

V

SY

= 2.5V

Figure 23. Closed-Loop Gain vs. Frequency

–90

–30

1k 10k 100k 1M 10M

09437-022

FREQUENCY (Hz)

–90

09437-025

Figure 25. Open-Loop Gain and Phase vs. Frequency

60

50

40

30

20

10

0

CLOSED-LOOP GAIN (dB)

–10

–20

10 100 1k 10k 100k 1M 10M

09437-026

AV = 100

A

= 10

V

A

= 1

V

FREQUENCY (Hz)

V

= 5V

SY

09437-029

Figure 26. Closed-Loop Gain vs. Frequency

Rev. A | Page 9 of 20

ADA4528-1 Data Sheet

160

140

120

100

80

CMRR (dB)

60

40

= VSY/2

V

20

0

100 1k 10k 100k 1M 10M

CM

V

= 1.1V

CM

FREQUENCY (Hz)

VSY = 2.5V

Figure 27. CMRR vs. Frequency

120

VSY = 2.5V

100

09437-126

140

120

100

80

60

CMRR (dB)

40

20

0

100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

VSY = 5V

V

= VSY/2

CM

Figure 30. CMRR vs. Frequency

120

100

VSY = 5V

09437-031

80

60

40

PSRR (dB)

20

0

–20

100 1k 10k 100k 1M 10M

PSRR–

FREQUENCY (Hz)

PSRR+

Figure 28. PSRR vs. Frequency

1k

V

= 2.5V

SY

100

10

(Ω)

1

OUT

Z

0.1

0.01

AV = 100

= 10

A

V

= 1

A

V

80

60

40

PSRR (dB)

20

0

–20

100 1k 10k 100k 1M 10M

09437-032

PSRR–

FREQUENCY (Hz)

PSRR+

09437-035

Figure 31. PSRR vs. Frequency

1k

V

= 5V

SY

100

10

(Ω)

1

OUT

Z

0.1

0.01

AV = 100

= 10

A

V

A

= 1

V

0.001

100 1k 10k 100k 1M 10M

FREQUENCY ( Hz)

Figure 29. Output Impedance vs. Frequency

09437-027

Rev. A | Page 10 of 20

0.001

100 1k 10k 100k 1M 10M

FREQUENCY ( Hz)

Figure 32. Output Impedance vs. Frequency

09437-030

Data Sheet ADA4528-1

VSY = ±1.25V

= 2V p-p

V

VOLTAGE (0.5V/DIV)

IN

A

= 1

V

RL = 10kΩ

= 100pF

C

L

TIME (20µs/DIV)

Figure 33. Large Signal Transient Response

VSY = ±1.25V

VIN = 100mV p-p

AV = 1

RL = 10kΩ

VOLTAGE (50mV/DIV)

CL = 100pF

TIME (1µs/DIV)

Figure 34. Small Signal Transient Response

16

VSY = 2.5V

= 100mV p-p

V

IN

14

= 1

A

V

= 10kΩ

R

L

12

10

OS+

VSY = ±2.5V

= 4V p-p

VOLTAGE (1V/DIV)

09437-034

V

IN

A

= 1

V

RL = 10kΩ

= 100pF

C

L

TIME (20µs/DIV)

09437-037

Figure 36. Large Signal Transient Response

VSY = ±2.5V

VIN = 100mV p-p

VOLTAGE (50mV/DIV)

09437-038

AV = 1

RL = 10kΩ

CL = 100pF

TIME (1µs/DIV)

09437-041

Figure 37. Small Signal Transient Response

16

VSY = 5V

= 100mV p-p

V

IN

14

= 1

A

V

= 10kΩ

R

L

12

10

OS+

8

6

OVERSHOOT (%)

4

2

0

1 10 100 1000

OS–

LOAD CAPACITANCE (pF)

Figure 35. Small Signal Overshoot vs. Load Capacitance

09437-033

Rev. A | Page 11 of 20

8

6

OVERSHOOT (%)

4

2

0

1 10 100 1000

OS–

LOAD CAPACITANCE (pF)

Figure 38. Small Signal Overshoot vs. Load Capacitance

09437-036

ADA4528-1 Data Sheet

0.5

0

INPUT

0.5

0

INPUT

–0.5

INPUT VOLTAGE (V)

OUTPUT

TIME ( 10µs/DIV)

VSY = ±1.25V

= –10

A

V

V

= 187.5mV

IN

RL = 10kΩ

CL = 100pF

2

1

0

OU TP U T V OLTA G E ( V)

–1

09437-040

Figure 39. Positive Overload Recovery

–0.5

INPUT VOLTAGE (V)

OUTPUT

TIME ( 10µs/DIV)

VSY = ±2.5V

A

= –10

V

VIN = 375mV

RL = 10kΩ

CL = 100pF

3

2

1

0

OU TP U T V OLTA G E ( V)

–1

09437-043

Figure 42. Positive Overload Recovery

0.5

0

–0.5

INPUT VOLTAGE (V)

INPUT

OUTPUT

VSY = ±1.25V

VIN = 187.5mV

AV = –10

RL = 10kΩ

CL = 100pF

TIME ( 10µs/DIV)

1

0

–1

OU TP U T V OLTA G E ( V)

–2

09437-039

Figure 40. Negative Overload Recovery

0.5

0

–0.5

INPUT VOLTAGE (V)

INPUT

OUTPUT

VSY = ±2.5V

AV = –10

VIN = 375mV

RL = 10kΩ

CL = 100pF

TIME ( 10µs/DIV)

1

0

–1

–2

OUTPUT VOLTAGE (V)

–3

09437-042

Figure 43. Negative Overload Recovery

INPUT

VSY = 2.5V

R

= 10kΩ

L

C

= 100pF

L

DUT A

= –1

V

OUTPUT

VOLTAGE (1V/DIV)

ERROR BAND

POST GAIN = 5

TIME ( 10µs/DI V)

Figure 41. Positive Settling Time to 0.1%

+7.5mV

0

–7.5mV

VOLTAGE (2V/DIV)

ERROR BAND

POST GAIN = 5

09437-044

Figure 44. Positive Settling Time to 0.1%

INPUT

OUTPUT

TIME (10µs/DIV)

VSY = 5V

R

= 10kΩ

L

= 100pF

C

L

DUT A

V

= –1

+20mV

0

–20mV

09437-047

Rev. A | Page 12 of 20

Data Sheet ADA4528-1

VSY = 2.5V

= 10kΩ

R

L

C

= 100pF

L

DUT A

= –1

INPUT

OUTPUT

VOLTAGE (1V/DIV)

ERROR BAND

POST GAIN = 5

TIME (10µs/DIV)

Figure 45. Negative Settling Time to 0.1%

V

+7.5mV

0

–7.5mV

09437-045

VOLTAGE (2V/DIV)

ERROR BAND

POST GAIN = 5

TIME (10µs/DIV)

Figure 48. Negative Settling Time to 0.1%

VSY = 5V

= 10kΩ

R

L

= 100pF

C

L

DUT A

INPUT

OUTPUT

V

= –1

+20mV

0

–20mV

09437-048

100

10

VSY = 2.5V

A

= 100

V

V

= VSY/2

CM

100

VSY = 5V

= 100

A

V

= VSY/2

V

CM

10

VOLTAGE NOISE DENSITY (nV/√Hz)

1

1 10 100 1k 10k

FREQUENCY (Hz)

Figure 46. Voltage Noise Density vs. Frequency

10

VSY = 2.5V

= 100

A

V

V

= VSY/2

CM

1

CURRENT NOISE DENSI TY (pA/ √Hz)

0.1

1 10 100 1k 10k 100k

FREQUENCY (Hz)

Figure 47. Current Noise Density vs. Frequency

VOLTAGE NOISE DENSITY (nV/√Hz)

1

1 10 100 1k 10k

09437-046

FREQUENCY (Hz)

09437-049

Figure 49. Voltage Noise Density vs. Frequency

10

VSY = 5V

= 100

A

V

V

= VSY/2

CM

1

CURRENT NOISE DENSI TY (pA/ √Hz)

0.1

09437-150

1 10 100 1k 10k 100k

FREQUENCY (Hz)

09437-153

Figure 50. Current Noise Density vs. Frequency

Rev. A | Page 13 of 20

ADA4528-1 Data Sheet

VSY = 2.5V

AV = 100

VCM = VSY/2

INPUT VOLTAGE (20nV/DIV)

TIME (1s/DIV)

Figure 51. 0.1 Hz to 10 Hz Noise

10

1

0.1

THD + N (%)

0.01

VSY = 2.5V

= 1

A

V

f = 1kHz

R

= 10kΩ

L

0.001

0.001 0.01 0.1 1 10

AMPLITUDE (V p -p)

Figure 52. THD + Noise vs. Amplitude

1

VSY = 2.5V

= 10kΩ

R

L

= 1

A

V

80kHz LOW- PASS FIL TER

V

= 2V p-p

IN

0.1

VSY = 5V

A

= 100

V

V

= VSY/2

CM

INPUT VOLTAGE (20nV/DIV)

09437-050

TIME (1s/DIV)

09437-053

Figure 54. 0.1 Hz to 10 Hz Noise

10

1

0.1

THD + N (%)

VSY = 5V

0.01

AV = 1

f = 1kHz

R

= 10kΩ

L

0.001

0.001 0.01 0 .1 1 10

09437-152

AMPLITUDE (V p -p)

09437-155

Figure 55. THD + Noise vs. Amplitude

1

= 5V

V

SY

= 10kΩ

R

L

AV = 1

80kHz LOW-PASS FILTER

V

= 2V p-p

IN

0.1

THD + N (%)

0.01

0.001

10 100 1k 10k 100k

FREQUENCY (Hz)

Figure 53. THD + Noise vs. Frequency

09437-056

THD + N (%)

0.01

0.001

10 100 1k 10k 100k

FREQUENCY (Hz)

Figure 56. THD + Noise vs. Frequency

09437-057

Rev. A | Page 14 of 20

Data Sheet ADA4528-1

APPLICATIONS INFORMATION

The ADA4528-1 is a precision, ultralow noise, zero-drift operational amplifier that features a patented chopping technique. This

chopping technique offers ultralow input offset voltage of 0.3 µV

typical and input offset voltage drift of 0.002 µV/

Offset voltage errors due to common-mode voltage swings and

power supply variations are also corrected by the chopping technique, resulting in a typical CMRR figure of 158 dB and a PSRR

figure of 150 dB at 2.5 V supply voltage. The ADA4528-1 has low

broadband noise of 5.6 nV/√Hz (at f = 1 kHz, A

2.5 V) and no 1/f noise component. These features are ideal for

amplification of low level signals in dc or subhertz high

precision applications.

INPUT PROTECTION

The ADA4528-1 has internal ESD protection diodes that are

connected between the inputs and each supply rail. These diodes

protect the input transistors in the event of electrostatic discharge and are reverse-biased during normal operation. This

protection scheme allows voltages as high as approximately

300 mV beyond the rails to be applied at the input of either

terminal without causing permanent damage. Refer to Table 4

in the Absolute Maximum Ratings section.

When either input exceeds one of the supply rails by more than

300 mV, these ESD diodes become forward-biased and large

amounts of current begin to flow through them. Without current

limiting, this excessive fault current causes permanent damage

to the device. If the inputs are expected to be subject to overvoltage

conditions, insert a resistor in series with each input to limit the

input current to 10 mA maximum. However, consider the resistor

thermal noise effect on the entire circuit.

At a 5 V supply voltage, the broadband voltage noise of the

ADA4528-1 is approximately 6 nV/√Hz (at unity gain), and a

1 kΩ resistor has thermal noise of 4 nV/√Hz. Adding a 1 kΩ

resistor increases the total noise by 30% root sum square (rss).

RAIL-TO-RAIL INPUT AND OUTPUT

The ADA4528-1 features rail-to-rail input and output with a

supply voltage from 2.2 V to 5.5 V. Figure 57 shows the input

and output waveforms of the ADA4528-1 configured as a unitygain buffer with a supply voltage of ±2.5 V and a resistive load

of 10 kΩ. With an input voltage of ±2.5 V, the ADA4528-1 allows

the output to swing very close to both rails. Additionally, it does

not exhibit phase reversal.

o

C typical.

= +100, VSY =

V

3

V

IN

V

OUT

TIME (200µs/DIV)

09437-059

VOLTAGE (V)

2

1

0

–1

–2

–3

VSY = ±2.5V

= 1

A

V

= 10kΩ

R

L

Figure 57. Rail-to Rail Input and Output

NOISE CONSIDERATIONS

1/f noise

1/f noise, also known as pink noise or flicker noise, is inherent

in semiconductor devices and increases as frequency decreases.

At low frequency, 1/f noise is a major noise contributor and causes

a significant output voltage offset when amplified by the noise

gain of the circuit. However, the ADA4528-1 eliminates the 1/f

noise internally, thus making it an excellent choice for dc or

subhertz high precision applications. The 0.1 Hz to 10 Hz amplifier voltage noise is only 97 nV p-p (A

supply voltage.

The low frequency 1/f noise appears as a slow varying offset to

the ADA4528-1 and is greatly reduced by the chopping technique.

This allows the ADA4528-1 to have a much lower noise at dc

and low frequency in comparison to standard low noise amplifiers

that are susceptible to 1/f noise. Figure 46 and Figure 49 show

the voltage noise density of the amplifier with no 1/f noise.

Source Resistance

The ADA4528-1 is one of the lowest noise zero drift amplifiers

with 5.6 nV/√Hz of broadband noise at 1 kHz (V

A

= +100) currently available in the industry. Therefore, it is

V

important to consider the input source resistance of choice to

maintain a total low noise. The total input referred broadband

noise (e

total) from any amplifier is primarily a function of

N

three types of noise: input voltage noise, input current noise,

and thermal (Johnson) noise from the external resistors. These

uncorrelated noise sources can be summed up in a root sum

squared (rss) manner by using the following equation:

e

total = [e

N

2

+ 4 kTRS + (in × RS)2]

n

where:

e

is the input voltage noise of the amplifier (V/√Hz).

n

is the input current noise of the amplifier (A/√Hz).

I

n

R

is the total input source resistance (Ω).

S

k is the Boltzmann’s constant (1.38 × 10

T is the temperature in Kelvin (K).

= +100) at 2.5 V of

V

= 2.5 V and

SY

1/2

−23

J/K).

Rev. A | Page 15 of 20

ADA4528-1 Data Sheet

T

√

T

√

The total equivalent rms noise over a specific bandwidth is

expressed as

e

= eN total √BW

N,RMS

where BW is the bandwidth in hertz.

This analysis is valid for broadband noise calculation. If the

bandwidth of concern includes the chopping frequency, more

complicated calculations must be made to include the effect of

the noise spike at the chopping frequency (see Figure 60).

With a low source resistance of R

< 1 kΩ, the voltage noise of

S

the amplifier dominates. As source resistance increases, the

thermal noise of R

increases, where R

dominates. As the source resistance further

S

> 100 kΩ, the current noise becomes the

S

main contributor of the total input noise. A good selection table

for low noise op amps can be found in the AN-940 Application

Note, Low Noise Amplifier Selection Guide for Optimal Noise

Performance.

Voltage Noise Density with Different Gain Configurations

Figure 58 shows the voltage noise density vs. closed-loop gain of

a zero-drift amplifier from Competitor A. The voltage noise density

of the amplifier increases from 11 nV/√Hz to 21 nV/√Hz as closedloop gain decreases from 1000 to 1. Figure 59 shows the voltage

noise density vs. frequency of the ADA4528-1 for three different

gain configurations. The ADA4528-1 offers lower input voltage

noise density of 6 nV/√Hz to 7 nV/√Hz regardless of gain

configurations.

24

20

Hz)

VSY = 5V

f = 100Hz

COMPETITOR A

100

VSY = 5V

V

= VSY/2

CM

10

AV = 1

VOLTAGE NOISE DENSITY (nV/√Hz)

AV = 10

AV = 100

1

1 10 100 1k 10k

FREQUENCY (Hz)

09437-062

Figure 59. Voltage Noise Density vs. Frequency

Residual Ripple

Although the ACFB suppresses the chopping related ripples,

there exists higher noise spectrum at the chopping frequency

and its harmonics due to the remaining ripples. Figure 60 shows

the voltage noise density of the ADA4528-1 configured in unity

gain. A noise spike of 50 nV/√Hz can be seen at the chopping

frequency of 200 kHz. This noise spike is significant when the

op amp has a closed-loop frequency that is higher than the

chopping frequency. To further suppress the noise to a desired

level, it is recommended to have a post filter at the output of the

amplifier.

100

VSY

=

5

V

A

=

1

V

/

=

2

V

V

CM

Hz)

SY

16

12

8

AGE NOISE DENSITY (nV/

4

VOL

0

1 10 100 1000

CLOSED-LOOP GAIN (V/V)

09437-061

Figure 58. Competitor A: Voltage Noise Density vs. Closed-Loop Gain

10

AGE NOISE DENSITY (nV/

VOL

1

1

100 1k 10k 100k 1M 10M

10

U

E

Q

F

R

)

Y

C

z

(

H

E

N

Figure 60. Voltage Noise Density

09437-063

Rev. A | Page 16 of 20

Data Sheet ADA4528-1

V

PRINTED CIRCUIT BOARD LAYOUT

The ADA4528-1 is a high precision device with ultralow offset

voltage and noise. Therefore, care must be taken in the design of

the printed circuit board (PCB) layout to achieve optimum

performance of the ADA4528-1 at board level.

To avoid leakage currents, keep the surface of the board clean

and free of moisture. Coating the board surface creates a barrier

to moisture accumulation and reduces parasitic resistance on

the board.

Properly bypassing the power supplies and keeping the supply

traces short minimizes power supply disturbances caused by

output current variation. Connect bypass capacitors as close

as possible to the device supply pins. Stray capacitances are a

concern at the outputs and the inputs of the amplifier. It is

recommended that signal traces be kept at a distance of at

least 5 mm from supply lines to minimize coupling.

A potential source of offset error is the Seebeck voltage on the

circuit board. The Seebeck voltage occurs at the junction of two

dissimilar metals and is a function of the temperature of the

junction. The most common metallic junctions on a circuit board

are solder-to-board trace and solder-to-component lead. Figure 61

shows a cross section of a surface-mount component soldered

to a PCB. A variation in temperature across the board (where T

T

) causes a mismatch in the Seebeck voltages at the solder joints,

A2

thereby resulting in thermal voltage errors that degrade the performance of the ultralow offset voltage of the ADA4528-1.

≠

A1

COMPONENT

LEAD

T

SC1

V

SC2

SOLDER

+

V

TS2

+

A2

≠ V

+ V

TS2

SC2

V

SC1

TS1

COPPER

TRACE

+

+

T

A1

SURFACE-MOUNT

COMPON ENT

PC BOARD

IF TA1 ≠ TA2, THEN

V

+ V

TS1

Figure 61. Mismatch in Seebeck Voltages Causes

Seebeck Voltage Error

To minimize these thermocouple effects, orient resistors so that

heat sources warm both ends equally. Where possible, the input

signal paths should contain matching numbers and types of components to match the number and type of thermocouple junctions.

For example, dummy components, such as zero value resistors,

can be used to match the thermoelectric error source (real resistors

in the opposite input path). Place matching components in close

proximity and orient them in the same manner to ensure equal

Seebeck voltages, thus cancelling thermal errors. Additionally,

use leads that are of equal length to keep thermal conduction in

equilibrium. Keep heat sources on the PCB as far away from

amplifier input circuitry as is practical.

It is highly recommended to use a ground plane. A ground

plane helps distribute heat throughout the board, maintains a

constant temperature across the board, and reduces EMI noise

pickup.

09437-154

Rev. A | Page 17 of 20

ADA4528-1 Data Sheet

OUTLINE DIMENSIONS

3.20

3.00

2.80

8

5

3.20

3.00

2.80

PIN 1

IDENTIFIER

0.95

0.85

0.75

0.15

0.05

COPLANARITY

1

0.65 BSC

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 62. 8-Lead Mini Small Outline Package [MSOP]

3.10

3.00 SQ

2.90

5.15

4.90

4.65

4

15° MAX

6°

0°

0.23

0.09

0.40

0.25

1.10 MAX

(RM-8)

Dimensions shown in millimeters

5

0.50 BSC

8

0.80

0.55

0.40

10-07-2009-B

PIN 1 INDEX

AREA

0.80

0.75

0.70

SEATING

PLANE

0.50

0.40

0.30

TOP VIEW

0.05 MAX

0.02 NOM

COPLANARIT Y

0.30

0.25

0.20

COMPLIANTTOJEDEC STANDARDS MO-229-WEED

0.08

0.203 REF

EXPOSED

PAD

4

BOTTOM VIEW

1

P

I

N

I

R

(

FOR PROP ER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CO NFIGURAT ION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

1.70

1.60 SQ

1.50

1

N

A

D

C

I

5

1

.

0

R

O

T

)

07-06-2011-A

Figure 63.8-Lead Lead Frame Chip Scale Package [LFCSP_WD]

3 mm × 3 mm Body, Very Very Thin, Dual Lead

(CP-8-12)

Dimensions shown in millimeters

ORDERING GUIDE

Model1 Temperature Range Package Description Package Option Branding

ADA4528-1ARMZ −40°C to +125°C 8-Lead Mini Small Outline Package [MSOP] RM-8 A2R

ADA4528-1ARMZ-R7 −40°C to +125°C 8-Lead Mini Small Outline Package [MSOP] RM-8 A2R

ADA4528-1ARMZ-RL −40°C to +125°C 8-Lead Mini Small Outline Package [MSOP] RM-8 A2R

ADA4528-1ACPZ-R7 −40°C to +125°C 8-Lead Lead Frame Chip Scale Package [LFCSP_WD] CP-8-12 A2R

ADA4528-1ACPZ-RL −40°C to +125°C 8-Lead Lead Frame Chip Scale Package [LFCSP_WD] CP-8-12 A2R

1

Z = RoHS Compliant Part.

Rev. A | Page 18 of 20

Data Sheet ADA4528-1

NOTES

Rev. A | Page 19 of 20

ADA4528-1 Data Sheet

NOTES

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09437-0-9/11(A)

Rev. A | Page 20 of 20

Loading...

Loading...