I/O, Low Power Operational Amplifier

ADA4084-2

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

Trademarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2011–2012 Analog Devices, Inc. All rights reserved.

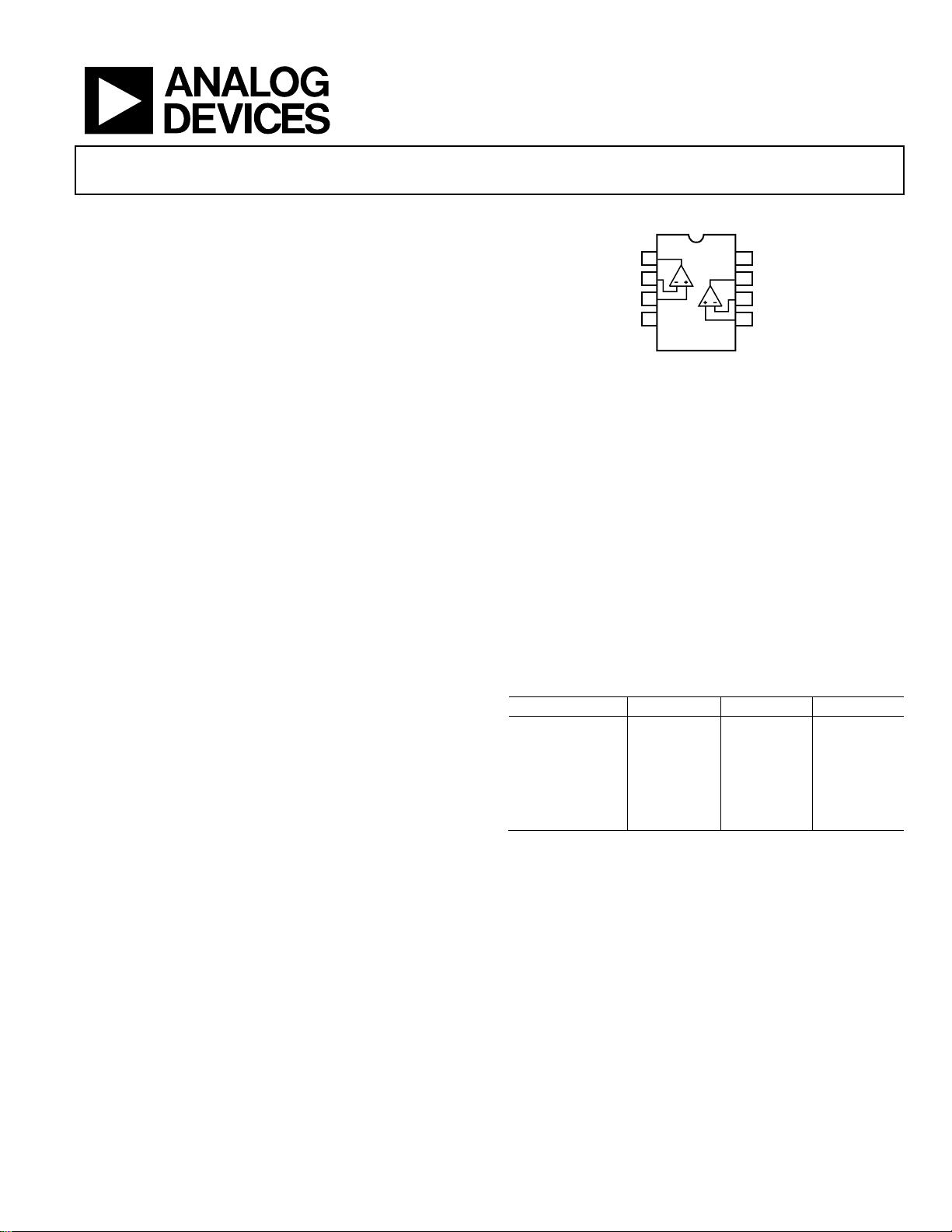

1

2

3

4

8

7

6

5

OUT B

–IN B

+IN B

V+

OUT A

–IN A

+IN A

V–

ADA4084-2

TOP VIEW

(Not to S cale)

08237-001

Data Sheet

FEATURES

Rail-to-rail input/output

Low power: 625 µA typical

Gain bandwidth product: 15.9 MHz at A

Unity-gain crossover: 9.9 MHz typical

−3 dB closed-loop bandwidth: 13.9 MHz typical at ±15 V

Low offset voltage: 100 μV maximum (SOIC)

Unity-gain stable

High slew rate: 4.6 V/μs typical

Low noise: 3.9 nV/√Hz typical at 1 kHz

APPLICATIONS

Battery-powered instrumentation

Power supply control and protection

Telecommunications

DAC output amplifier

ADC input buffer

GENERAL DESCRIPTION

The ADA4084-2 is a dual, single-supply, 10 MHz bandwidth

amplifier featuring rail-to-rail inputs and outputs. It is guaranteed to operate from 3 V to 30 V (or ±1.5 V to ±15 V).

These amplifiers are well suited for single-supply applications

requiring both ac and precision dc performance. The combination of wide bandwidth, low noise, and precision makes the

ADA4084-2 useful in a wide variety of applications, including

filters and instrumentation.

Other applications for these amplifiers include portable telecom-

munications equipment, power supply control and protection,

and use as amplifiers or buffers for transducers with wide output

ranges. Sensors requiring a rail-to-rail input amplifier include

Hall effect, piezoelectric, and resistive transducers.

The ability to swing rail-to-rail at both the input and output

enables designers to build multistage filters in single-supply

systems and to maintain high signal-to-noise ratios.

The ADA4084-2 is specified over the industrial temperature

range of −40°C to +125°C. The dual ADA4084-2 is available in

the 8-lead SOIC and MSOP surface-mount packages.

=100 typical

V

30 V, Low Noise, Rail-to-Rail

PIN CONFIGURATIONS

Figure 1. 8-Lead MSOP (RM)

8-Lead SOIC (R)

The ADA4084-2 is a member of a growing series of high voltage,

low noise op amps offered by Analog Devices, Inc., (see Table 1).

For a more complete selection table of low input voltage noise

amplifiers, see the AN-940 Application Note, Low Noise

Amplifier Selection Guide for Optimal Noise Performance,

available at www.analog.com.

Table 1. Low Noise Op Amps

Voltage Noise Single Dual Quad

1.1 nV/Hz AD8597 AD8599

1.8 nV/Hz ADA4004-1 ADA4004-2 ADA4004-4

2.8 nV/Hz RRO1 AD8675 AD8676

2.8 nV/Hz AD8671 AD8672 AD8674

3.2 nV/Hz OP27/OP37

3.9 nV/Hz RRIO2 ADA4084-2

1

Rail-to-rail output.

2

Rail-to-rail input/output.

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change with out notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

ADA4084-2 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Pin Configurations ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Characteristics ............................................................. 3

Absolute Maximum Ratings ............................................................ 6

Thermal Resistance ...................................................................... 6

ESD Caution .................................................................................. 6

Typical Performance Characteristics ............................................. 7

±1.5 V Characteristics .................................................................. 7

±5 V Characteristics ................................................................... 11

REVISION HISTORY

2/12—Rev. 0 to Rev. A

Changes to Data Sheet Title ............................................................ 1

Changes to Voltage Range in General Description ...................... 1

Changes to Supply Current/Amplifier Parameter, Table 2.......... 3

Changes to Common-Mode Rejection Ratio Parameter, Table 3 .. 4

Changes to Common-Mode Rejection Ratio Parameter, Table 4 .. 5

Changes to Figure 2 .......................................................................... 6

Changes to Figure 24 ...................................................................... 10

Changes to Figure 32 ...................................................................... 12

Changes to Figure 47 ...................................................................... 14

Changes to Figure 55 ...................................................................... 16

Changes to Figure 62 ...................................................................... 17

Changes to Figure 73 ...................................................................... 20

10/11—Revision 0: Initial Version

±15 V Characteristics ................................................................ 15

Comparative Voltage and Variable Voltage Graphs ............... 19

Applications Information .............................................................. 20

Functional Description .............................................................. 20

Input Protection ......................................................................... 21

Output Phase Reversal ............................................................... 21

Designing Low Noise Circuits in Single-Supply

Applications ................................................................................ 21

Comparator Operation .............................................................. 22

Outline Dimensions ....................................................................... 23

Ordering Guide .......................................................................... 23

Rev. A | Page 2 of 24

Data Sheet ADA4084-2

Large Signal Voltage Gain

AVO

RL = 2 kΩ, 0.5 V ≤ VO ≤ 2.5 V

100

104 dB

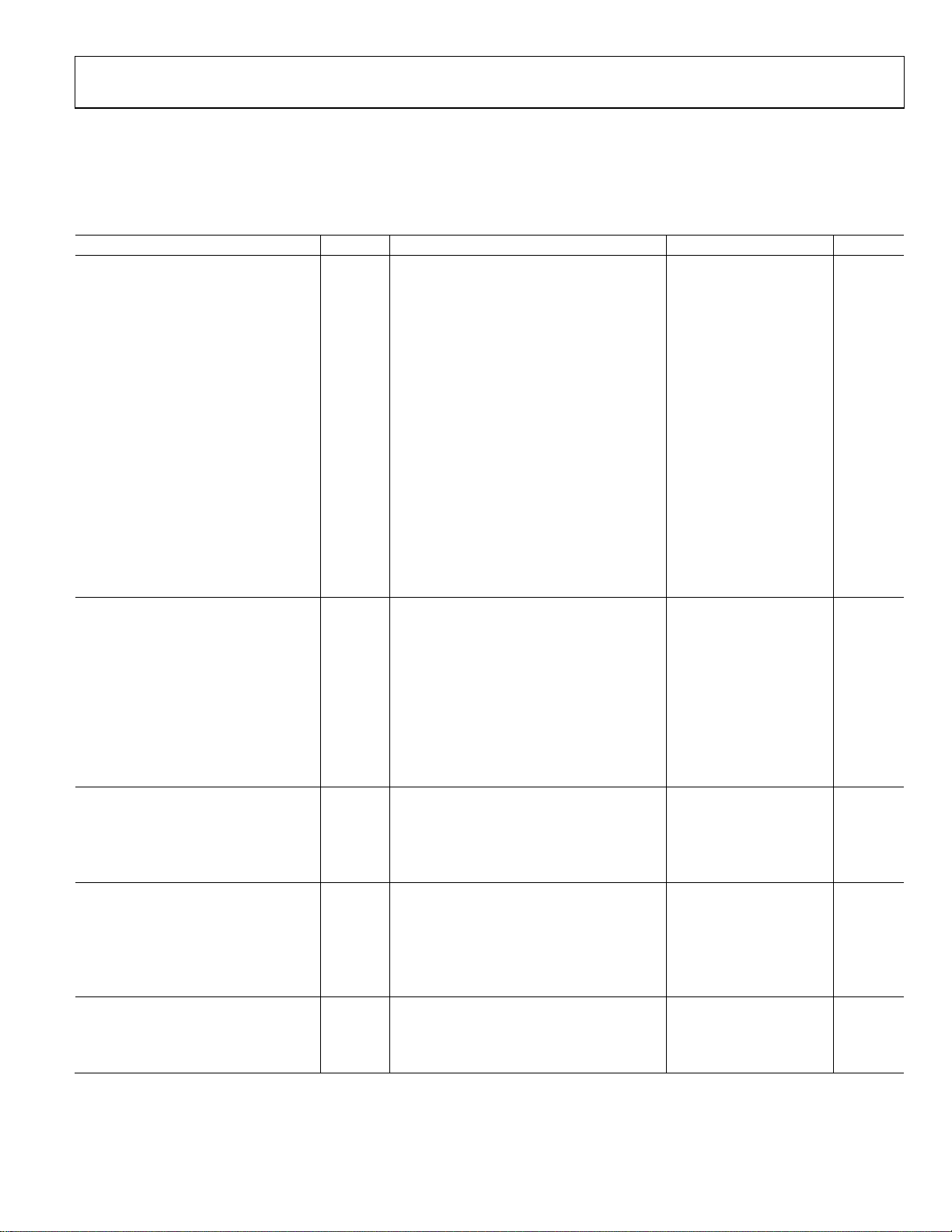

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VSY = 3 V, VCM =1.5 V, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage1 VOS SOIC package 100 μV

−40°C ≤ TA ≤ +125°C 200 μV

MSOP package 130 μV

−40°C ≤ TA ≤ +125°C 250 μV

Offset Voltage Drift ΔVOS/ΔT −40°C ≤ TA ≤ +125°C 0.5 1.75 µV/°C

Offset Voltage Matching Channel A vs. Channel B, TA = 25°C 150 μV

Input Bias Current IB 140 300 nA

–40°C ≤ TA ≤ +125°C 450 nA

Input Offset Current IOS 25 nA

–40°C ≤ TA ≤ +125°C 50 nA

Input Voltage Range 0 3 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 3 V 64 80 dB

−40°C ≤ TA ≤ +125°C 60 dB

RL = 2 kΩ, −40°C ≤ TA ≤ +125°C 97 dB

Input Impedance, Differential 100||1.1 kΩ||pF

Input Impedance, Common-Mode 80||2.9 MΩ||pF

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 10 kΩ to VCM 2.85 2.95 V

–40°C ≤ TA ≤ +125°C 2.8 V

RL = 2 kΩ to VCM 2.8 2.9 V

–40°C ≤ TA ≤ +125°C 2.7 V

Output Voltage Low VOL RL = 10 kΩ to VCM 10 20 mV

–40°C ≤ TA ≤ +125°C 40 mV

RL = 2 kΩ to VCM 50 mV

–40°C ≤ TA ≤ +125°C 75 mV

Short-Circuit Current I

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = ±1.25 V to ±1.75 V 100 110 dB

–40°C ≤ TA ≤ +125°C 90 dB

Supply Current/Amplifier ISY IO = 0 mA 565 650 µA

–40°C ≤ TA ≤ +125°C 950 µA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 2 kΩ 2.0 2.6 V/µs

Gain Bandwidth Product GBP VIN = 5 mV p-p, RL = 10 kΩ, AV = 100 15.4 MHz

Unity-Gain Crossover UGC VIN = 5 mV p-p, RL = 10 kΩ, AV = 1 8.08 MHz

Phase Margin ΦM 86 Degrees

−3 dB Closed-Loop Bandwidth −3 dB AV = 1, VIN = 5 mV p-p 12.3 MHz

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 0.14 μV p-p

Voltage Noise Density en f = 1 kHz 3.9 nV/√Hz

Current Noise Density in f = 1 kHz 0.55 pA/√Hz

1

Offset voltage does not include solder heat resistance.

−17/+10 mA

SC

Rev. A | Page 3 of 24

ADA4084-2 Data Sheet

MSOP package

130

μV

−40°C ≤ TA ≤ +125°C

450

nA

−40°C ≤ TA ≤ +125°C

4.7

V

Supply Current/Amplifier

ISY

IO = 0 mA

595

700

µA

Current Noise Density

in

0.55 pA/√Hz

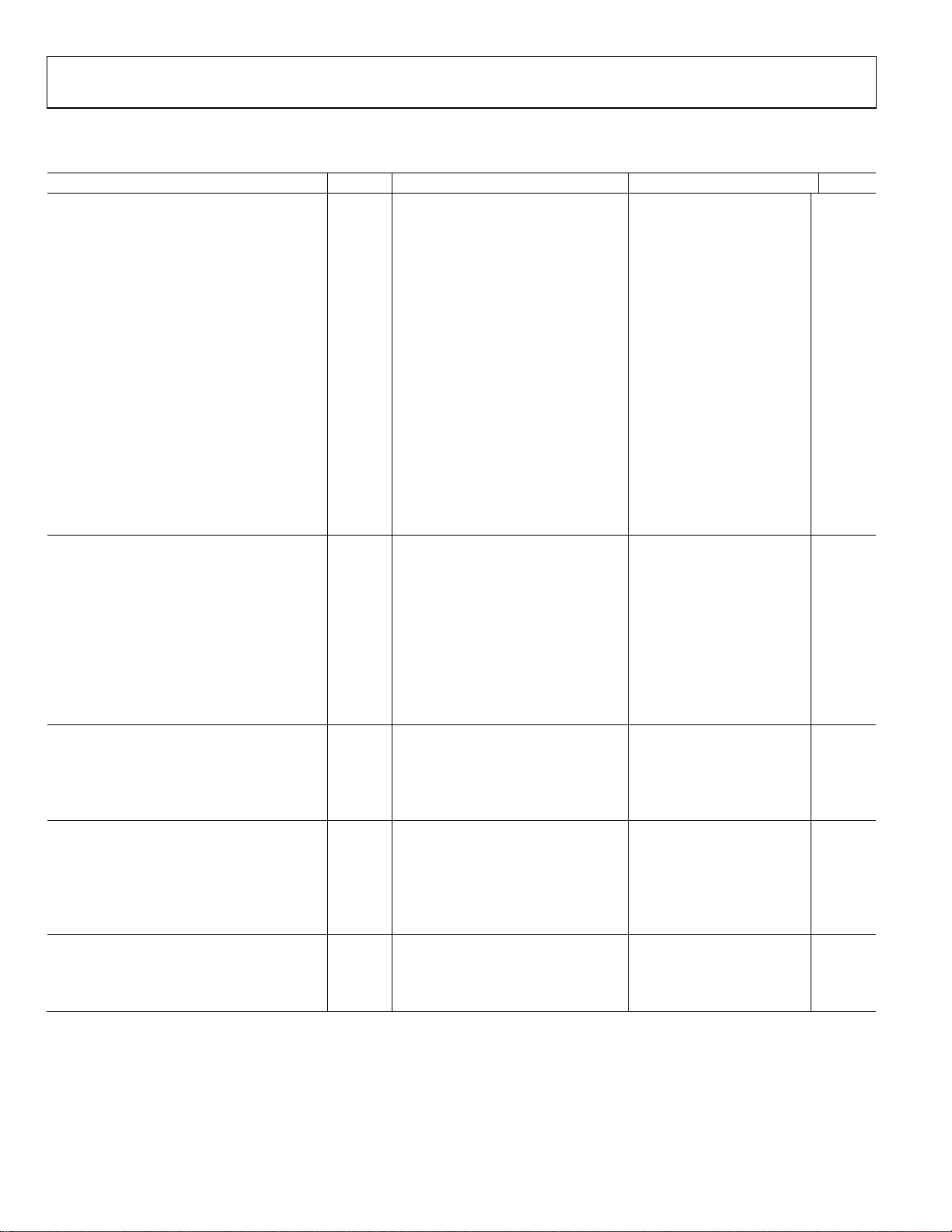

VSY = ±5.0 V, VCM = 0 V, TA = 25°C, unless otherwise noted.

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage1 VOS SOIC package 100 μV

−40°C ≤ TA ≤ +125°C 250 μV

−40°C ≤ TA ≤ +125°C 250 μV

Offset Voltage Drift ΔVOS/ΔT −40°C ≤ TA ≤ +125°C 0.5 1.75 μV/°C

Offset Voltage Matching Channel A vs. Channel B, TA = 25°C 150 μV

Input Bias Current IB 140 300 nA

Input Offset Current IOS 25 nA

−40°C ≤ TA ≤ +125°C 50 nA

Input Voltage Range −5 +5 V

Common-Mode Rejection Ratio CMRR VCM = ±4 V 106 124 dB

VCM = ±5 V, −40°C ≤ TA ≤ +125°C 76 dB

Large Signal Voltage Gain AVO RL = 2 kΩ, −4 V ≤ VO ≤ 4 V 108 112 dB

RL = 2 kΩ, −40°C ≤ TA ≤ +125°C 103 dB

Input Impedance, Differential 100||1.1 kΩ||pF

Input Impedance, Common-Mode 200||2.5 MΩ||pF

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 10 kΩ to VCM 4.9 4.95 V

−40°C ≤ TA ≤ +125°C 4.8 V

RL = 2 kΩ to VCM 4.8 4.85 V

Output Voltage Low VOL RL = 10 kΩ to VCM −4.95 −4.9 V

−40°C ≤ TA ≤ +125°C −4.8 V

RL = 2 kΩ to VCM −4.95 −4.8 V

−40°C ≤ TA ≤ +125°C −4.7 V

Short Circuit Current ISC −24/+17 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = ±2 V to ±18 V 110 120 dB

−40°C ≤ TA ≤ +125°C 105 dB

−40°C ≤ TA ≤ +125°C 1000 µA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 2 kΩ to VCM 2.4 3.7 V/µs

Gain Bandwidth Product GBP VIN = 5 mV p-p, RL = 10 kΩ, AV = 100 15.9 MHz

Unity-Gain Crossover UGC VIN = 5 mV p-p, RL = 10 kΩ, AV = 1 9.6 MHz

Phase Margin ΦM 85 Degrees

−3 dB Closed-Loop Bandwidth −3 dB AV = 1, VIN = 5 mV p-p 13.9 MHz

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 0.14 µV p-p

Voltage Noise Density en f = 1 kHz 3.9 nV/√Hz

1

Offset Voltage does not include solder heat resistance.

Rev. A | Page 4 of 24

Data Sheet ADA4084-2

MSOP package

130

μV

−40°C ≤ TA ≤ +125°C

450

nA

−40°C ≤ TA ≤ +125°C

14.3

V

Supply Current/Amplifier

ISY

IO = 0 mA

625

750

µA

Current Noise Density

in

0.55 pA/√Hz

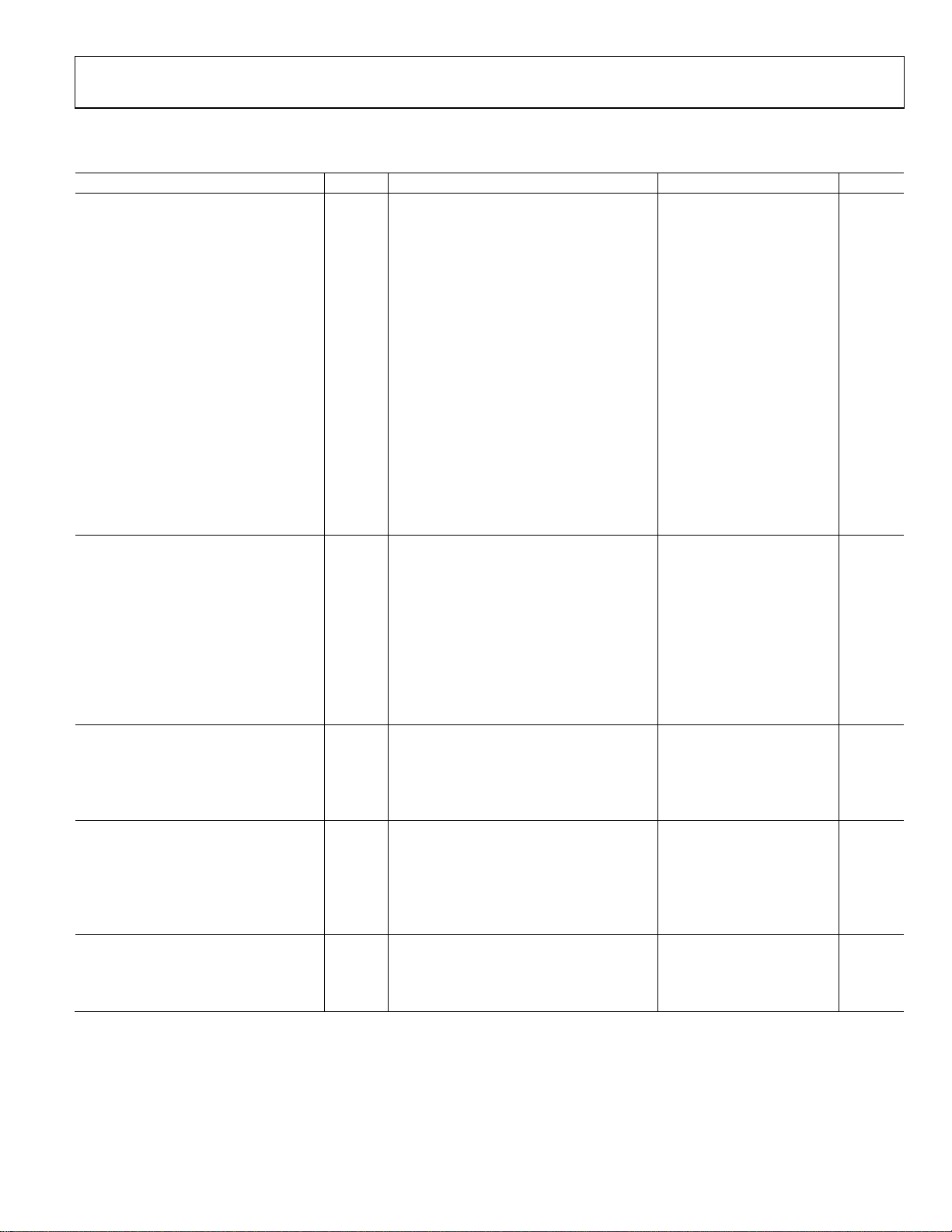

VSY = ±15.0 V, VCM = 0 V, TA = 25°C, unless otherwise noted.

Table 4.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage1 VOS SOIC package 100 μV

−40°C ≤ TA ≤ +125°C 200 μV

−40°C ≤ TA ≤ +125°C 250 μV

Offset Voltage Drift ΔVOS/ΔT 0.5 1.75 μV/°C

Offset Voltage Matching Channel A vs. Channel B, TA = 25°C 150 μV

Input Bias Current IB 140 300 nA

Input Offset Current IOS 25 nA

−40°C ≤ TA ≤ +125°C 50 nA

Input Voltage Range −15 +15 V

Common-Mode Rejection Ratio CMRR VCM = ±14 V 106 124 dB

VCM = ±15 V, −40°C ≤ TA ≤ +125°C 85 dB

Large Signal Voltage Gain AVO RL = 2 kΩ, −13.5 V ≤ VO ≤ +13.5 V 110 117 dB

−40°C ≤ TA ≤ +125°C 105 dB

Input Impedance, Differential 100||1.1 kΩ||pF

Input Impedance, Common-Mode 200||2.5 MΩ||pF

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 10 kΩ to VCM 14.8 14.9 V

−40°C ≤ TA ≤ +125°C 14.8 V

RL = 2 kΩ to VCM 14.5 14.6 V

Output Voltage Low VOL RL = 10 kΩ to VCM −14.95 −14.9 V

−40°C ≤ TA ≤ +125°C −14.8 V

RL = 2 kΩ to VCM −14.9 −14.8 V

−40°C ≤ TA ≤ +125°C −14.7 V

Short Circuit Current ISC ±30 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = ±2 V to ±18 V 110 120 dB

−40°C ≤ TA ≤ +125°C 105 dB

−40°C ≤ TA ≤ +125°C 1050 µA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 2 kΩ 2.4 4.6 V/µs

Gain Bandwidth Product GBP VIN = 5 mV p-p, RL = 10 kΩ, AV = 100 15.9 MHz

Unity-Gain Crossover UGC VIN = 5 mV p-p, RL = 10 kΩ, AV = 1 9.9 MHz

Phase Margin ΦM 86 Degrees

−3 dB Closed-Loop Bandwidth −3 dB AV = 1, VIN = 5 mV p-p 13.9 MHz

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 0.1 µV p-p

Voltage Noise Density en f = 1 kHz 3.9 nV/√Hz

1

Offset Voltage does not include solder heat resistance.

Rev. A | Page 5 of 24

ADA4084-2 Data Sheet

Input Voltage

V− ≤ VIN ≤ V+

D2

D101

D100

D5 D4

D1

Q1

Q4 Q3

Q24

Q21

D20

Q13

Q18

Q19

Q23

Q2

FOLDED

CASCADE

V

EE

V

OUT

V

CC

V

BIAS

MIRROR

08237-002

R4

R5

R6

R7

C2

C1

R1 R2

R3

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

Supply Voltage ±18 V

Differential Input Voltage1 ±0.6 V

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +125°C

Junction Temperature Range −65°C to +150°C

Lead Temperature (Soldering 60 sec) 300°C

1

For input differential voltages greater than 0.6 V, the input current should be

limited to less than 5 mA to prevent degradation or destruction of the input

devices.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the device soldered on a 4-layer JEDEC

standard printed circuit board (PCB) with zero airflow.

Table 6. Thermal Resistance

Package Type θJA θJC Unit

8-Lead SOIC 121 43 °C/W

8-Lead MSOP 142 45 °C/W

ESD CAUTION

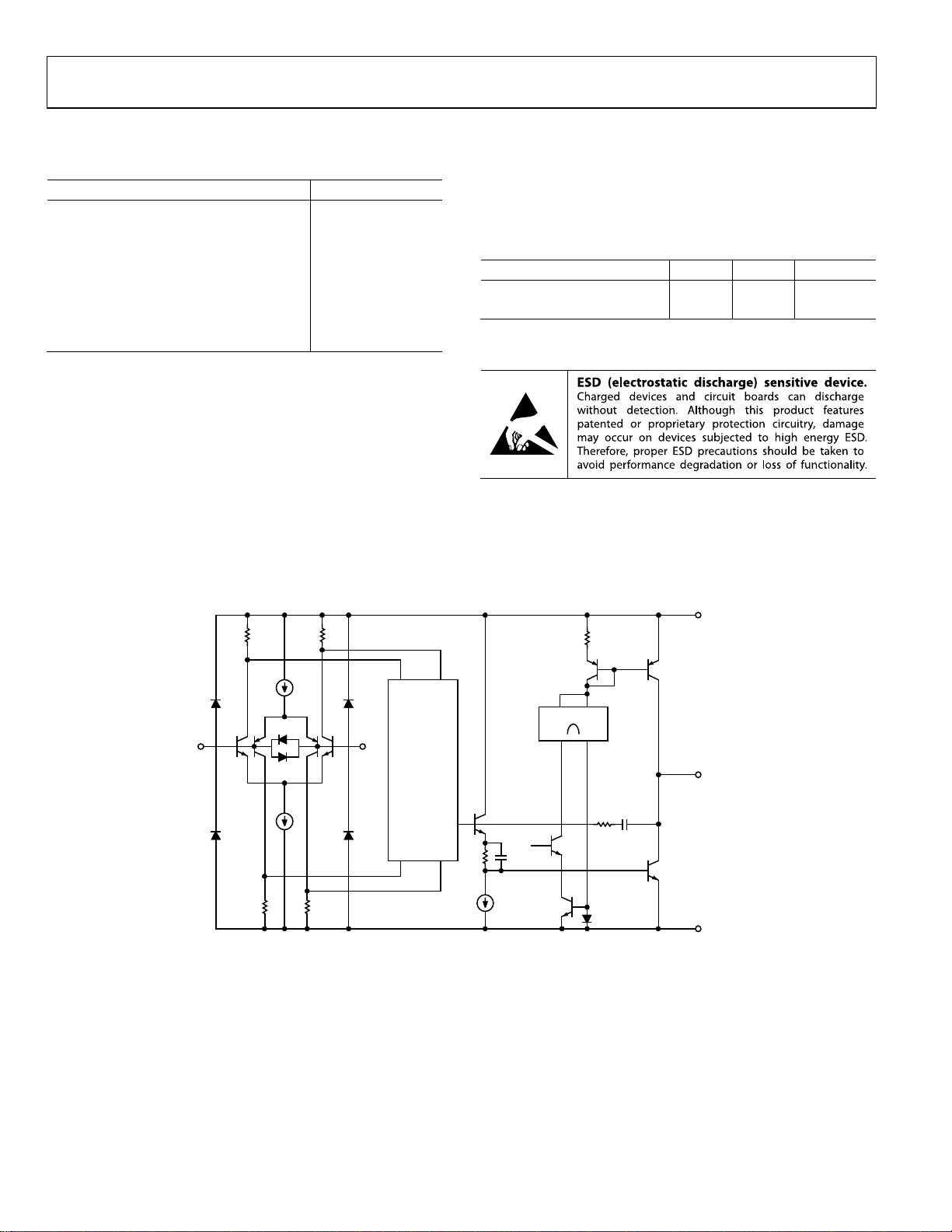

Figure 2. Simplified Schematic

Rev. A | Page 6 of 24

Data Sheet ADA4084-2

120

NUMBER OF AMP LIFIE RS

08237-003

50

NUMBER OF AMP LIFIE RS

08237-004

60

0

0 2.0

NUMBER OF AMP LIFIE RS

TCVOS (µV/°C)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

R

L

= ∞

–40° ≤ T

A

≤ +125°C

10

20

30

40

50

0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8

08237-005

500

–500

0 0.50 0.75 1.00 1.25 1.500.25 3.002.75

2.502.252.001.75

INPUT OFFSET VOLTAGE (µV)

COMMON-MODE VOLTAGE (V)

–400

–300

–200

–100

0

100

200

300

400

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

R

L

= ∞

08237-006

–50

–100

–150

–200

–250

–40 125

INPUT BIAS ( nA)

TEMPERATURE (°C)

–25 –10 5 20 35 50 65 80 95 110

ADA4084-2

V

SY

= ±1.5V

V

CM

= 0V

R

L

= ∞

IB+

IB–

08237-007

600

–600

–1.5 –1.0

1.0–0.5 0.50 1.5

INPUT BIAS ( nA)

VCM (V)

–400

–200

0

200

400

TA = +85°C

T

A

= +25°C

T

A

= +125°C

TA = –40°C

ADA4084-2

V

SY

= ±1.5V

08237-008

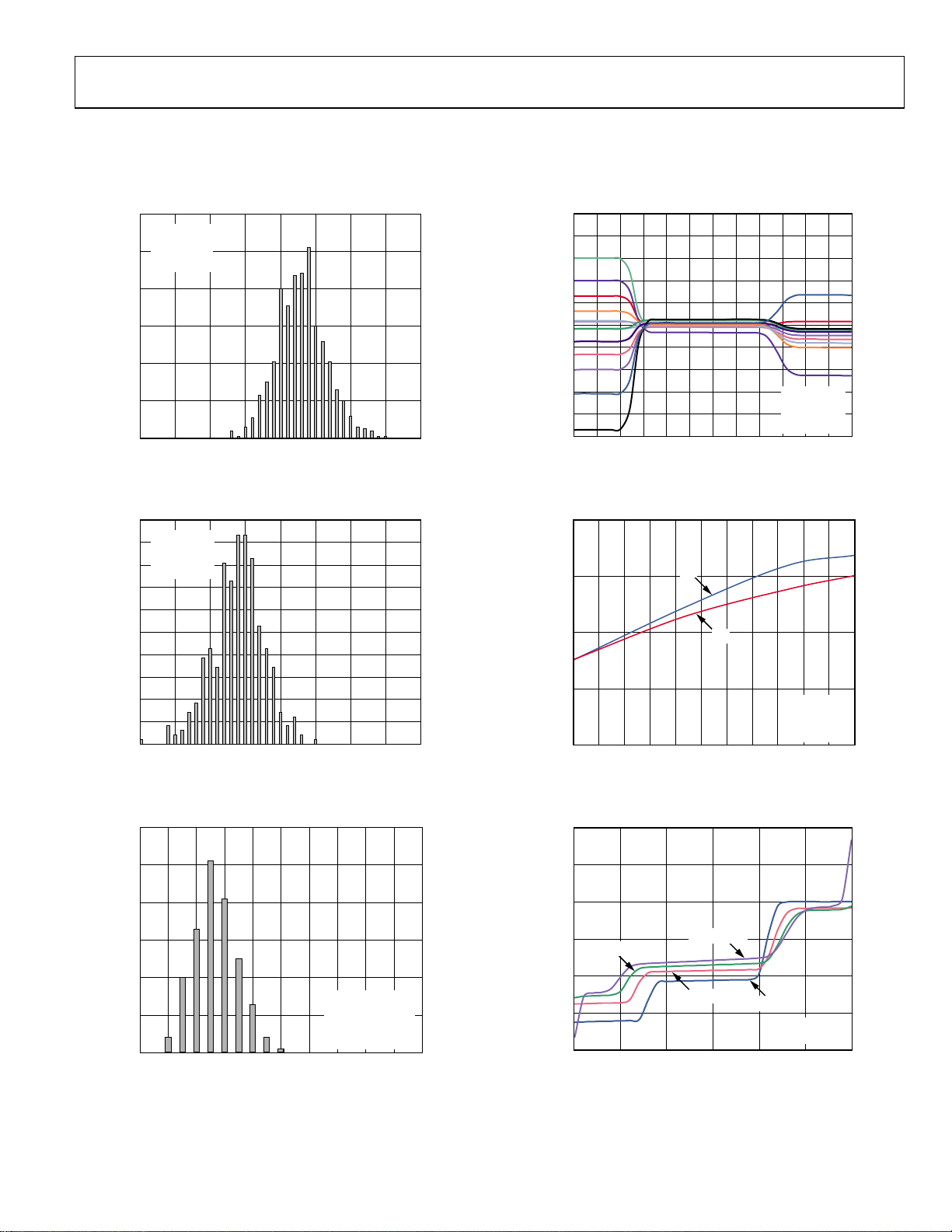

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, unless otherwise noted.

±1.5 V CHARACTERISTICS

ADA4084-2

V

= ±1.5V

SY

100

= 25°C

T

A

R

= ∞

L

80

60

40

20

0

–100 –50 500 100

–25 25–75 75

VOS (µV)

Figure 3. Input Offset Voltage Distribution, SOIC

ADA4084-2

45

V

= ±1.5V

SY

= 25°C

T

A

40

R

= ∞

L

35

30

25

20

15

10

5

0

–100 –50 –25 25–75 75500 100

VOS (µV)

Figure 4. Input Offset Voltage Distribution, MSOP

Figure 6. Input Offset Voltage vs. Common-Mode Voltage

Figure 7. Input Bias Current vs. Temperature

Figure 5. TCVOS Distribution, SOIC

Figure 8. Input Bias Current vs. VCM and Temperature

Rev. A | Page 7 of 24

ADA4084-2 Data Sheet

1000

100

10

1

0.001 0.01 0.1 1 10

V

DO

(mV)

LOAD CURRENT ( mA)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

(V+) –V

OH

08237-009

1000

100

10

1

0.001 0.01 0.1 1 10

V

DO

(mV)

LOAD CURRENT ( mA)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

V

OL

– (V–)

08237-010

120

–40

270

–90

0.1 100k

GAIN (dB)

PHASE (Degrees)

FREQUENCY ( kHz )

–45

0

45

90

135

180

225

–20

20

0

40

60

80

100

1 10 100 1k 10k

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

R

L

= 10kΩ

08237-011

60

–20

10 100M

GAIN (dB)

FREQUENCY ( Hz )

–10

0

10

20

30

40

50

100 1k 10k 100k 10M1M

AV = +100

AV = +10

AV = +1

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

08237-012

1000

100

10

1

0.10

0.01

10 100M

Z

OUT

(Ω)

FREQUENCY ( Hz )

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

AV = +10

AV = +100

A

V

= +1

08237-013

140

–20

10 100M

PSRR (dB)

FREQUENCY ( Hz )

0

20

40

60

80

100

120

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

PSRR–

PSRR+

08237-014

Figure 9. Dropout Voltage vs. Source Current

Figure 12. Closed-Loop Gain vs. Frequency

Figure 10. Dropout Voltage vs. Sink Current

Figure 11. Open-Loop Gain and Phase vs. Frequency

Figure 13. Output Impedance vs. Frequency

Figure 14. PSRR vs. Frequency

Rev. A | Page 8 of 24

Data Sheet ADA4084-2

120

20

10 100M

CMRR (dB)

FREQUENCY ( Hz )

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

30

40

50

60

70

80

90

100

110

08237-015

1.5

1.0

0.5

0

–1.5

–1.0

–0.5

0 2 4 6 8 10 12 14 16 18

VOLTAGE (V)

TIME (µs)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

R

L

= 2kΩ

C

L

= 100pF

08237-016

80

60

40

20

0

–80

–60

–40

–20

0 18

VOLTAGE (mV)

TIME (µs)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

R

L

= 2kΩ

C

L

= 100pF

08237-017

2 4 6 8 10 12 14 16

2

–10

–8

–6

–4

–2

0

0.08

–0.04

–0.02

0

0.02

0.04

0.06

–1 0 21

43

7 865 9

VOLTAGE (V)

VOLTAGE (V)

TIME (µs)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

OUTPUT

INPUT

08237-018

10

4

1

1 10 100 1k 10k 100k

VOLTAGE NOISE DENSITY (nV/√Hz)

FREQUENCY ( Hz )

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

08237-019

60

50

40

30

20

10

0

1 100010010

OVERSHOOT (%)

CAPACITANCE (pF)

ADA4084-2

V

SY

= ±1.5V

V

IN

= 100mV p-p

R

L

= 2kΩ

T

A

= 25°C

OS+

OS–

08237-020

Figure 15. CMRR vs. Frequency

Figure 18. Settling Time

Figure 16. Large Signal Transient Response

Figure 17. Small Signal Transient Response

Figure 19. Voltage Noise Density

Figure 20. Overshoot vs. Capacitance

Rev. A | Page 9 of 24

ADA4084-2 Data Sheet

80

–80

0 1 2 3 4 5 6 7 8 9 10

VOLTAGE NOISE (nV)

TIME (Seconds)

–60

–40

–20

0

20

40

60

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

08237-021

0

–160

–140

–120

–100

–80

–60

–40

–20

100 1k 10k 100k

CHANNEL SEPARAT ION (dB)

FREQUENCY ( Hz )

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

V

IN

= 1V p-p

08237-022

1

0.1

0.01

0.001

0.001 0.01 0.1 1

THD + N (%)

AMPLITUDE (V

RMS

)

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

f

= 1kHz

08237-023

0.01

0.001

0.0001

10 100 1k 10k 100k

THD + N (%)

FREQUENCY ( Hz )

ADA4084-2

R

L

= 2kΩ

V

IN

= 0.4V

RMS

VSY = ±1.5V

T

A

= 25°C

500kHz FILTER

08237-024

2.0

–2.0

0 1000

VOLTAGE (V)

TIME (µs)

–1.5

–1.0

–0.5

0

0.5

1.0

1.5

100 200 300 400 500 600 700 800 900

ADA4084-2

V

SY

= ±1.5V

T

A

= 25°C

OUTPUT

INPUT

08237-025

Figure 21. Voltage Noise 0.1 Hz to 10 Hz

Figure 22. Channel Separation

Figure 24. THD + N vs. Frequency

Figure 25. No Phase Reversal

Figure 23. THD + N vs. Amplitude

Rev. A | Page 10 of 24

Data Sheet ADA4084-2

–

±5 V CHARACTERISTICS

120

ADA4084-2

= ±5V

V

SY

100

= 25°C

T

A

= ∞

R

L

80

60

40

NUMBER OF AMP LIFI ERS

20

0

–100 – 50 50–25 250–75 75 100

VOS (µV)

Figure 26. Input Offset Voltage Distribution SOIC

08237-026

600

500

400

300

200

100

0

–100

–200

–300

INPUT OFFSET VOLTAGE (µV)

–400

–500

–600

–4 –3 –2 –1 0 1 2 3 4

–5 5

COMMON-MODE VOLTAGE (V)

ADA4084-2

V

SY

T

A

R

L

Figure 29. Input Offset Voltage vs. Common-Mode Voltage

= ±5V

= 25°C

= ∞

08237-029

60

ADA4084-2

= ±5V

V

50

40

30

20

NUMBER OF AMP LIFI ERS

10

0

–100 100

–50 50–25 250–75 75

VOS (µV)

SY

T

A

R

L

= 25°C

= ∞

08237-027

Figure 27. Input Offset Voltage Distribution MSOP

50

45

40

35

30

25

20

15

NUMBER OF AMPLIFIERS

10

5

0

0.2 0.4 0. 6 0.8 1. 0 1.2 1. 4 1.6 1. 8

02.0

TCVOS (µV/°C)

ADA4084-2

= ±5V

V

SY

= ∞

R

L

–40° ≤ T

A

≤ +125°C

08237-028

Figure 28. TCVOS Distribution

50

–100

–150

INPUT BI AS (nA)

–200

–250

–40 125

–25 –10 5 20 35 50 65 80 95 110

Figure 30. Input Bias Current vs. Temperature

800

600

400

200

0

–200

INPUT BI AS (nA)

–400

–600

–800

–5 5

–4–3–2–101234

Figure 31. Input Bias Current vs. VCM and Temperature

IB+

TEMPERATURE (°C)

IB–

TA = +85°C

VCM (V)

TA = +125°C

TA = +25°C

ADA4084-2

V

= ±5V

SY

V

= 0V

CM

R

= ∞

L

TA = –40°C

ADA4084-2

= ±5V

V

SY

08237-030

08237-031

Rev. A | Page 11 of 24

ADA4084-2 Data Sheet

1000

100

10

1

0.001 0.01 0.1 1 10

V

DO

(mV)

LOAD CURRENT ( mA)

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

(V+) –V

OH

08237-032

1000

100

10

1

0.001 0.01 0.1 1 10

V

DO

(mV)

LOAD CURRENT ( mA)

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

V

OL

– (V–)

08237-033

120

–40

270

–90

0.1 100k

GAIN (dB)

PHASE (Degrees)

FREQUENCY ( kHz )

–45

0

45

90

135

180

225

–20

20

0

40

60

80

100

1 10 100 1k 10k

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

R

L

= 10kΩ

08237-034

60

–20

10 100M

GAIN (dB)

FREQUENCY ( Hz )

–10

0

10

20

30

40

50

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

08237-035

AV = +100

AV = +10

AV = +1

1000

100

10

1

0.10

0.01

10 100M

Z

OUT

(Ω)

FREQUENCY ( Hz )

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

A

V

= +100

A

V

= +1

A

V

= +10

08237-036

140

–20

10 100M

PSRR (dB)

FREQUENCY ( Hz )

0

20

40

60

80

100

120

100 1k 10k 100k 10M

1M

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

PSRR–

PSRR+

08237-037

Figure 32. Dropout Voltage vs. Source Current

Figure 33. Dropout Voltage vs. Sink Current

Figure 35. Closed-Loop Gain vs. Frequency

Figure 36. Output Impedance vs. Frequency

Figure 34. Open-Loop Gain and Phase vs. Frequency

Figure 37. PSRR vs. Frequency

Rev. A | Page 12 of 24

Data Sheet ADA4084-2

120

20

10 100M

CMRR (dB)

FREQUENCY ( Hz )

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

30

40

50

60

70

80

90

100

110

08237-038

5

–5

VOLTAGE (V)

TIME (µs)

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

R

L

= 2kΩ

C

L

= 100pF

–4

–3

–2

–1

0

1

2

3

4

08237-039

0 182 4 6 8 10 12 14 16

80

60

40

20

0

–80

–60

–40

–20

VOLTAGE (mV)

TIME (µs)

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

R

L

= 2kΩ

C

L

= 100pF

08237-040

0 102 31 4 6 7

5 8 9

10

–25

–20

–5

–10

–15

0

5

0.16

–0.12

–0.08

–0.04

0

0.04

0.08

0.12

–2 0 2

4

86 18161210 14

VOLTAGE (V)

VOLTAGE (V)

TIME (µs)

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

OUTPUT

INPUT

08237-041

10

1

1 10 100 1k 10k 100k

VOLTAGE NOISE DENSITY (nV/√Hz)

FREQUENCY ( Hz )

ADA4084-2

V

SY

= ±5V

T

A

= 25°C

08237-042

4

60

50

40

30

20

10

0

1 100010010

OVERSHOOT (%)

CAPACITANCE (pF)

ADA4084-2

V

SY

= ±5V

V

IN

= 100mV p-p

R

L

= 2kΩ

T

A

= 25°C

OS+

OS–

08237-043

Figure 38. CMRR vs. Frequency

Figure 39. Large Signal Transient Response

Figure 41. Settling Time

Figure 42. Voltage Noise Density

Figure 40. Small Signal Transient Response

Figure 43. Overshoot vs. Load Capacitance

Rev. A | Page 13 of 24

ADA4084-2 Data Sheet

80

60

40

20

1

ADA4084-2

R

V

VSY = ±5V

T

0.1

500kHz FIL TER

= 2kΩ

L

= 2.0V

IN

= 25°C

A

RMS

0

–20

VOLTAGE NOISE (nV)

–40

ADA4084-2

–60

V

= ±5V

SY

T

= 25°C

A

–80

012345678910

TIME ( Second s)

Figure 44. Volage Noise 0.1 Hz to 10 Hz

0

–20

–40

–60

–80

–100

–120

CHANNEL SEP ARATION (dB)

–140

–160

100 1k 10k 100k

FREQUENCY (Hz)

ADA4084-2

V

SY

= 25°C

T

A

V

IN

Figure 45. Channel Separation

1

= ±5V

= 5V p-p

0.01

THD + N (%)

0.001

0.0001

10 100 1k 10k 100k

08237-044

FREQUENCY (Hz)

08237-047

Figure 47. THD + N vs. Frequency

6

4

2

0

VOLTAGE (V)

–2

–4

–6

100 200 300 400 500 600 700 800 900

01000

08237-045

INPUT

OUTPUT

TIME (µs)

ADA4084-2

= ±5V

V

SY

= 25°C

T

A

08237-048

Figure 48. No Phase Reversal

0.1

0.01

THD + N (%)

0.001

ADA4084-2

= ±5V

V

SY

= 25°C

T

A

f

= 1kHz

0.0001

0.001 0.01 0.1 1

AMPLIT UDE (V

RMS

)

08237-046

Figure 46. THD + N vs. Amplitude

Rev. A | Page 14 of 24

Data Sheet ADA4084-2

–

±15 V CHARACTERISTICS

100

ADA4084-2

NUMBER OF AMP LIFI ERS

90

80

70

60

50

40

30

20

10

= ±15V

V

SY

= 25°C

T

A

= ∞

R

L

0

–100 – 50 50–25 250–75 75 100

VOS (µV)

Figure 49. Input Offset Voltage Distribution, SOIC

08237-049

600

500

400

300

200

100

0

–100

–200

–300

INPUT OFFSET VOLTAGE (µV)

–400

–500

–600

–15 –10 –5 5 1510

COMMON-MODE VOLTAGE (V)

0

ADA4084-2

V

T

R

Figure 52. Input Offset Voltage vs. Common-Mode Voltage

= ±15V

SY

= 25°C

A

= ∞

L

08237-052

60

ADA4084-2

V

50

40

30

20

NUMBER OF AMP LIFI ERS

10

0

–100 100

–50 50–25 250–75 75

VOS (µV)

SY

T

A

R

L

Figure 50. Input Offset Voltage Distribution, MSOP

60

50

40

30

= ±15V

= 25°C

= ∞

50

–100

–150

INPUT BI AS (nA)

–200

–250

–40 125

–25 –10 5 20 35 50 65 80 95 110

08237-050

IB+

IB–

TEMPERATURE (°C)

ADA4084-2

V

= ±15V

SY

V

= 0V

CM

R

= ∞

L

08237-053

Figure 53. Input Bias Current vs. Temperature

1200

800

400

TA = +85°C

0

TA = +125°C

INPUT BIAS (nA)

20

NUMBER OF AMPLIFIERS

10

0

02.0

0.2 0.4 0. 6 0.8 1. 0 1.2 1. 4 1.6 1. 8

TCVOS (µV/°C)

ADA4084-2

= ±15V

V

SY

= ∞

R

L

–40° ≤ T

A

≤ +125°C

08237-051

Figure 51. TCVOS Distribution

–400

–800

–1200

–15 –10 –5 5 10 15

Figure 54. Input Bias Current vs. VCM and Temperature

0

VCM (V)

TA = +25°C

TA = –40°C

ADA4084-2

V

= ±15V

SY

08237-054

Rev. A | Page 15 of 24

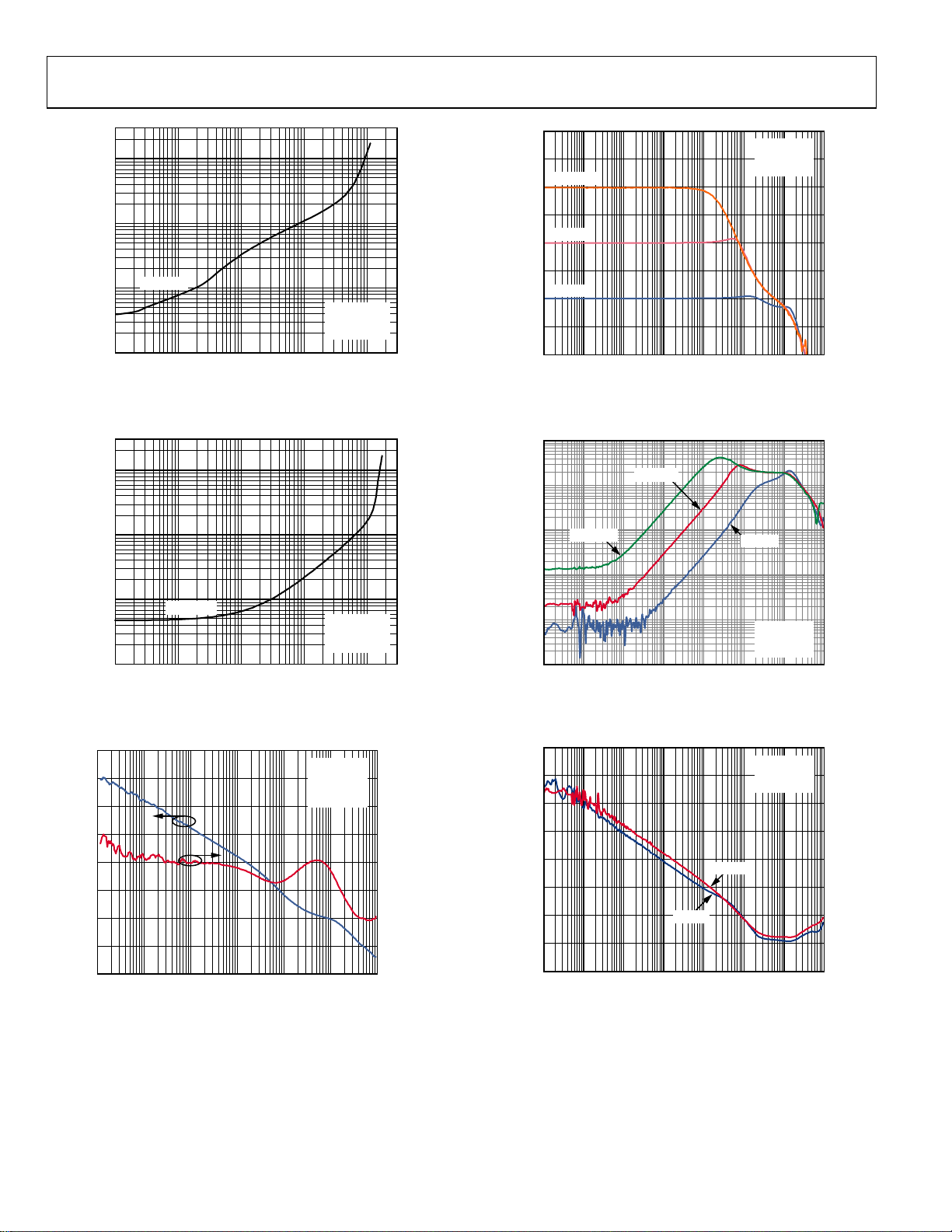

ADA4084-2 Data Sheet

1000

10000

100

10

1

0.001 0.01 0.1 1 10

V

DO

(mV)

LOAD CURRENT ( mA)

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

(V+) –V

OH

08237-055

1000

10000

100

10

1

0.001 0.01 0.1 1 10

V

DO

(mV)

LOAD CURRENT ( mA)

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

V

OL

– (V–)

08237-056

120

–40

270

–90

100 100M

GAIN (dB)

PHASE (Degrees)

FREQUENCY ( Hz )

–45

0

45

90

135

180

225

–20

20

0

40

60

80

100

1k 10k 100k 1M 10M

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

R

L

= 10kΩ

08237-057

60

–20

10 100M

GAIN (dB)

FREQUENCY ( Hz )

–10

0

10

20

30

40

50

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

08237-058

AV = +100

AV = +10

AV = +1

1000

100

10

1

0.1

0.01

10 100M

Z

OUT

(Ω)

FREQUENCY ( Hz )

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

A

V

= +100

A

V

= +1

A

V

= +10

08237-059

140

–20

10 100M

PSRR (dB)

FREQUENCY ( Hz )

0

20

40

60

80

100

120

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

PSRR–

PSRR+

08237-060

Figure 55. Dropout Voltage vs. Source Current

Figure 56. Dropout Voltage vs. Sink Current

Figure 58. Closed-Loop Gain vs. Frequency

Figure 59. Output Impedance vs. Frequency

Figure 57. Open-Loop Gain and Phase vs. Frequency

Figure 60. PSRR vs. Frequency

Rev. A | Page 16 of 24

Data Sheet ADA4084-2

120

20

10 100M

CMRR (dB)

FREQUENCY ( Hz )

100 1k 10k 100k 10M1M

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

30

40

50

60

70

80

90

100

110

08237-061

15

10

–15

–10

–5

0

5

0 4 8 12 3628 32242016

VOLTAGE (V)

TIME (µs)

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

R

L

= 2kΩ

C

L

= 100pF

08237-062

80

60

40

20

0

–80

–60

–40

–20

0 21

43

7 8 965 10

VOLTAGE (mV)

TIME (µs)

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

R

L

= 2kΩ

C

L

= 100pF

08237-063

10

–25

–20

–5

–10

–15

0

5

0.20

–0.15

–0.10

–0.05

0

0.05

0.10

0.15

–2 0 2

4

86 18161210 14

VOLTAGE (V)

VOLTAGE (V)

TIME (µs)

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

INPUT

OUTPUT

08237-064

10

1

1 10 100 1k 10k 100k

VOLTAGE NOISE DENSITY (nV/√Hz)

FREQUENCY ( Hz )

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

08237-065

4

70

50

60

40

30

20

10

0

1 100010010

OVERSHOOT (%)

CAPACITANCE (pF)

ADA4084-2

V

SY

= ±15V

V

IN

= 100mV p-p

R

L

= 2kΩ

T

A

= 25°C

OS+

OS–

08237-066

Figure 61. CMRR vs. Frequency

Figure 62. Large Signal Transient Response

Figure 64. Settling Time

Figure 65. Voltage Noise Density

Figure 63. Small Signal Transient Response

Figure 66. Overshoot vs. Load Capacitance

Rev. A | Page 17 of 24

ADA4084-2 Data Sheet

0 2 4 6 8 10

60

–60

VOLTAGE NOISE (nV)

TIME (Seconds)

–40

–20

0

20

40

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

08237-067

0

–180

–140

–160

–120

–100

–80

–60

–40

–20

100 1k 10k 100k

CHANNEL SEPARAT ION (dB)

FREQUENCY ( Hz )

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

V

IN

= 10V p-p

08237-068

1

0.001

0.01

0.1

0.0001

0.001

0.01 0.1 1 10

THD + N (%)

AMPLITUDE (V

RMS

)

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

f

= 1kHz

08237-069

1

0.001

0.01

0.1

0.0001

10 100 1k 10k 100k

THD + N (%)

FREQUENCY ( Hz )

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

500kHz FILTER

08237-070

20

15

10

5

–15

–10

–5

–20

0 1000

VOLTAGE (V)

TIME (µs)

0

100 200 300 400 500 600 700 800 900

ADA4084-2

V

SY

= ±15V

T

A

= 25°C

OUTPUT

INPUT

08237-071

Figure 67. Voltage Noise 0.1 Hz to 10 Hz

Figure 68. Channel Sepatation

Figure 70. THD + N vs. Frequency

Figure 71. No Phase Reversal

Figure 69. THD + N vs. Amplitude

Rev. A | Page 18 of 24

Data Sheet ADA4084-2

1000

0

0 36

I

SY

/AMPLIFIER (µA)

V

SY

(V)

100

200

300

400

500

600

700

800

900

4 8 12 16 20 24 28 32

ADA4084-2

T

A

= 25°C

R

L

= ∞

+125°C

+25°C

–40°C

+85°C

08237-072

COMPARATIVE VOLTAGE AND VARIABLE VOLTAGE GRAPH

Figure 72. Supply Current vs. Supply Voltage

Rev. A | Page 19 of 24

ADA4084-2 Data Sheet

D2

D101

D100

D5 D4

D1

Q1

Q4 Q3

Q2

08237-073

R4

R1 R2

R3

Q24

Q21

D20

Q13

Q18

Q19

Q23

V

EE

V

OUT

V

CC

V

BIAS

MIRROR

08237-074

R5

R6

R7

C2

C1

APPLICATIONS INFORMATION

FUNCTIONAL DESCRIPTION

The ADA4084-2 is a precision single-supply, rail-to-rail opera-

tional amplifier. Intended for portable instrumentation, the

ADA4084-2 combines the attributes of precision, wide band-

width, and low noise to make it an ideal choice in single-supply

applications that require both ac and precision dc performance.

Other low supply voltage applications for which the ADA4084-2

is well suited are active filters, audio microphone preamplifiers,

power supply control, and telecommunications. To combine all

of these attributes with rail-to-rail input/output operation, novel

circuit design techniques are used.

important that the effective source impedances connected to

the ADA4084-2 inputs be balanced for optimum dc and ac

performance.

To achieve rail-to-rail output, the ADA4084-2 output stage

design employs a unique topology for both sourcing and sinking

current. This circuit topology is illustrated in Figure 74. The

output stage is voltage-driven from the second gain stage. The

signal path through the output stage is inverting; that is, for

positive input signals, Q13 provides the base current drive to Q19

so that it conducts (sinks) current. For negative input signals, the

signal path via Q18 → mirror → Q24 provides the base current

drive for Q23 to conduct (source) current. Both transistors

provide output current until they are forced into saturation.

Figure 73. ADA4084-2 Equivalent Input Circuit

For example, Figure 73 illustrates a simplified equivalent circuit

for the input stage of the ADA4084-2. It comprises a PNP

differential pair, Q1 and Q2, and an NPN differential pair, Q3

and Q4, operating concurrently. Diode D100 and Diode D101

serve to clamp the applied differential input voltage to the

ADA4084-2, thereby protecting the input transistors against

Zener breakdown of the emitter-base junctions. Input stage

voltage gains are kept low for input rail-to-rail operation. The

two pairs of differential output voltages are connected to the

second stage of the ADA4084-2, which is a modified compound

folded cascade gain stage. It is also in the second gain stage,

where the two pairs of differential output voltages are combined

into a single-ended output signal voltage used to drive the

output stage.

A key issue in the input stage is the behavior of the input bias

currents over the input common-mode voltage range. Input bias

currents in the ADA4084-2 are the arithmetic sum of the base

currents in Q1 and Q4 and in Q2 and Q3. As a result of this

design approach, the input bias currents in the ADA4084-2 not

only exhibit different amplitudes; they also exhibit different

polarities. This effect is best illustrated by Figure 7, Figure 8,

Figure 30, Figure 31, Figure 53, and Figure 54. It is therefore

Figure 74. ADA4084-2 Equivalent Output Circuit

Thus, the saturation voltage of the output transistors sets the

limit on the ADA4084-2 maximum output voltage swing. Output

short-circuit current limiting is determined by the maximum

signal current into the base of Q13 from the second gain stage.

The output stage also exhibits voltage gain. This is accomplished

by the use of common-emitter amplifiers, and, as a result, the

voltage gain of the output stage (thus, the open-loop gain of the

device) exhibits a dependence on the total load resistance at the

output of the ADA4084-2.

Rev. A | Page 20 of 24

VV

R1

R2

V

IN

V

OUT

1/2

ADA4084-2

08237-075

[

]

22

2

)()()(2

nOA

SnOA

nR

nT

eee

Ri

+×+=

Hz

V

e

nR

e

nR

e

nOA

i

nOA

i

nOA

R

NOISELESS

R

NOISELESS

08237-076

IDEAL

NOISELESS

OP AMP

R

S

= 2R

Data Sheet ADA4084-2

INPUT PROTECTION

As with any semiconductor device, if conditions exist where the

applied input voltages to the device exceed either supply voltage,

the input overvoltage I-to-V characteristic of the device must be

considered. When an overvoltage occurs, the amplifier may be

damaged, depending on the magnitude of the applied voltage

and the magnitude of the fault current.

The D1, D2, D4, and D5 diodes conduct when the input commonmode voltage exceeds either supply pin by a diode drop. This

varies with temperature and is in the range of 0.3 V to 0.8 V. As

illustrated in the simplified equivalent circuit shown in Figure 73,

the ADA4084-2 does not have any internal current limiting resis-

tors; thus, fault currents can quickly rise to damaging levels.

This input current is not inherently damaging to the device,

provided that it is limited to 5 mA or less. If a fault condition

causes more than 5 mA to flow, an external series resistor

should be added at the expense of additional thermal noise.

Figure 75 illustrates a typical noninverting configuration for an

overvoltage-protected amplifier where the series resistance, R

is chosen, such that

R−=

S

IN

( )

MAX

SUPPLY

mA5

For example, a 1 kΩ resistor protects the ADA4084-2 against

input signals up to 5 V above and below the supplies. Note that

the thermal noise of a 1 kΩ resistor at room temperature is

4 nV/√Hz, which exceeds the voltage noise of the ADA4084-2.

For other configurations where both inputs are used, each input

should be protected against abuse with a series resistor. Again,

to ensure optimum dc and ac performance, it is recommended

that source impedance levels be balanced.

Figure 75. Resistance in Series with Input

Limits Overvoltage Currents to Safe Values

To protect Q1-Q2 and Q3-Q4 from large differential voltages

that may result in Zener breakdown of the emitter-base junction,

D100 and D101 are connected between the two inputs. This

precludes operation as a comparator. For a more complete

description, see the MT-035 Tutorial, Op Amp Inputs, Outputs,

Single-Supply, and Rail-to-Rail Issues; the MT-083 Tutor ial ,

Comparators, the MT-084 Tutorial, Using Op Amps As

Comparators; and the AN-849 Application Note, Using Op

Amps as Comparators, at www.analog.com.

,

S

OUTPUT PHASE REVERSAL

Some operational amplifiers designed for single-supply operation

exhibit an output voltage phase reversal when their inputs are

driven beyond their useful common-mode range. Typically, for

single-supply bipolar op amps, the negative supply determines

the lower limit of their common-mode range. With these devices,

external clamping diodes, with the anode connected to ground

and the cathode to the inputs, prevent input signal excursions

from exceeding the negative supply of the device (that is, GND),

preventing a condition that causes the output voltage to change

phase. JFET input amplifiers can also exhibit phase reversal,

and, if so, a series input resistor is usually required to prevent it.

The ADA4084-2 is free from reasonable input voltage range

restrictions, provided that input voltages no greater than the

supply voltages are applied. Although device output does not

change phase, large currents can flow through the input

protection diodes. Therefore, the technique recommended in the

Input Protection section should be applied to those applications

where the likelihood of input voltages exceeding the supply

voltages is high.

DESIGNING LOW NOISE CIRCUITS IN SINGLESUPPLY APPLICATIONS

In single-supply applications, devices like the ADA4084-2

extend the dynamic range of the application through the use of

rail-to-rail operation. Referring to the op amp noise model

circuit configuration illustrated in Figure 76, the expression for

an amplifier’s total equivalent input noise voltage for a source

resistance level, R

where:

R

= 2R, the effective, or equivalent, circuit source resistance.

S

(e

)2 is the source resistance thermal noise voltage power (4kTR).

nR

k is the Boltzmann’s constant, 1.38 × 10

T is the ambient temperature in Kelvin of the circuit, 273.15 +

T

(°C).

A

(i

)2 is the op amp equivalent input noise current spectral

nOA

power (1 Hz bandwidth).

(e

)2 is the op amp equivalent input noise voltage spectral

nOA

power (1 Hz bandwidth).

Figure 76. Op Amp Noise Circuit Model Used to Determine Total Circuit

, is given by

S

, units in

–23

J/K.

Equivalent Input Noise Voltage and Noise Figure

Rev. A | Page 21 of 24

ADA4084-2 Data Sheet

TOTAL S OURCE RESIST ANCE , R

S

(Ω)

100

1

EQUIVALENT THERMAL NOISE (nV/ Hz)

10

10k

ADA4084-2 TOTAL

EQUIVALENT NOISE

RESISTOR THERMAL

NOISE ONLY

08237-077

100 1k 100k

FREQUENCY = 1kHz

T

A

= 25°C

800

SUPPLY CURRENT (µA)

As a design aid, Figure 77 shows the total equivalent input noise

of the ADA4084-2 and the total thermal noise of a resistor for

comparison. Note that for source resistance less than 1 kΩ, the

equivalent input noise voltage of the ADA4084-2 is dominant.

Figure 77. ADA4084-2 Equivalent Thermal Noise vs. Total Source Resistance

Because circuit SNR is the critical parameter in the final analysis,

the noise behavior of a circuit is sometimes expressed in terms

of its noise figure, NF. The noise figure is defined as the ratio of

a circuit’s output signal-to-noise to its input signal-to-noise.

Noise figure is generally used for RF and microwave circuit

analysis in a 50 Ω system. This is not very useful for op amp

circuits where the input and output impedances can vary

greatly. For a more complete description of noise figure, see the

MT-052 Tutorial, Op Amp Noise Figure: Don’t be Mislead,

available at www.analog.com.

Signal levels in the application invariably increase to maximize

circuit SNR, which is not an option in low voltage, single-supply

applications.

Therefore, to achieve optimum circuit SNR in single-supply

applications, it is recommended that an operational amplifier

with the lowest equivalent input noise voltage be chosen, along

with source resistance levels that are consistent with maintaining

low total circuit noise.

COMPARATOR OPERATION

Although op amps are quite different from comparators,

occasionally an unused section of a dual or a quad op amp

can be used as a comparator; however, this is not recommended

for any rail-to-rail output op amps. For rail-to-rail output op

amps, the output stage is generally a ratioed current mirror with

bipolar or MOSFET transistors. With the part operating open

loop, the second stage increases the current drive to the ratioed

mirror to close the loop. However, it cannot, which results in an

increase in supply current. With the op amp configured as a

comparator, the supply current can be significantly higher (see

Figure 76). An unused section should be configured as a voltage

follower with the noninverting input connected to a voltage

within the input voltage range. The ADA4084-2 has unique

second stage and output stage designs that greatly reduce the

excess supply current when the op amp is operating open loop.

COMPARATOR

OUTPUT LOW

700

600

500

400

300

200

100

0

0 36

COMPARATOR

OUTPUT HIGH

4 8 12 16 20 24 28 32

VSY (V)

Figure 78. Supply Current vs. Supply Voltage

BUFFER

ADA4084-2

T

A

R

L

= 25°C

= ∞

08237-078

Rev. A | Page 22 of 24

Data Sheet ADA4084-2

OUTLINE DIMENSIONS

3.20

3.00

2.80

8

5

3.20

3.00

2.80

PIN 1

IDENTIFIER

0.95

0.85

0.75

0.15

0.05

COPLANARITY

1

0.65 BSC

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 79. 8-Lead Mini Small Outline Package [MSOP]

5.00(0.1968)

4.80(0.1890)

5.15

4.90

4.65

4

15° MAX

6°

0°

0.23

0.09

0.40

0.25

1.10 MAX

(RM-8)

Dimensions shown in millimeters

0.80

0.55

0.40

10-07-2009-B

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLYAND ARE NOT APPROPRIATE FOR USE IN DESIGN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-AA

BSC

6.20 (0.2441)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

45°

012407-A

Figure 80. 8-Lead Standard Small Outline Package [SOIC_N]

Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

ORDERING GUIDE

Model1 Temperature Range Package Description Package Option Branding

ADA4084-2ARMZ −40°C to +125°C 8-Lead Mini Small Outline Package [MSOP] RM-8 A2Q

ADA4084-2ARMZ-R7 −40°C to +125°C 8-Lead Mini Small Outline Package [MSOP] RM-8 A2Q

ADA4084-2ARMZ-RL −40°C to +125°C 8-Lead Mini Small Outline Package [MSOP] RM-8 A2Q

ADA4084-2ARZ −40°C to +125°C 8-Lead Standard Small Outline Package [SOIC_N] R-8

ADA4084-2ARZ-R7 −40°C to +125°C 8-Lead Standard Small Outline Package [SOIC_N] R-8

ADA4084-2ARZ-RL −40°C to +125°C 8-Lead Standard Small Outline Package [SOIC_N] R-8

1

Z = RoHS Compliant Part.

Rev. A | Page 23 of 24

ADA4084-2 Data Sheet

©2011–2012 Analog Devices, Inc. All rights reserved. Trademarks and

NOTES

registered trademarks are the property of their respective owners.

D08237-0-2/12(A)

Rev. A | Page 24 of 24

Loading...

Loading...