CCD Signal Processor with Vertical Driver

FEATURES

Integrated 10-channel V-driver

Register-compatible with the AD9991 and AD9995

3-field (6-phase) vertical clock support

2 additional vertical outputs for advanced CCDs

Complete on-chip timing generator

Precision Timing core with <600 ps resolution

Correlated double sampler (CDS)

6 dB to 42 dB 10-bit variable gain amplifier (VGA)

12-bit 36 MHz ADC

Black level clamp with variable level control

On-chip 3 V horizontal and RG drivers

2-phase and 4-phase H-clock modes

Electronic and mechanical shutter support

On-chip driver for external crystal

On-chip sync generator with external sync input

8 mm × 8 mm CSPBGA package with 0.65 mm pitch

APPLICATIONS

Digital still cameras

Digital video camcorders

CCD camera modules

and

Precision Timing

™ Generator

AD9925

GENERAL DESCRIPTION

The AD9925 is a complete 36 MHz front end solution for digital still camera and other CCD imaging applications. Based on

the AD9995 product, the AD9925 includes the analog front end

and a fully programmable timing generator (AFETG), combined

with a 10-channel vertical driver (V-driver). A Precision Timing

core allows adjustment of high speed clocks with approximately

600 ps resolution at 36 MHz operation.

The on-chip V-driver supports up to 10 channels for use with

3-field (6-phase) CCDs. Two additional vertical outputs can be

used with CCDs that contain advanced video readout modes.

Voltage levels of up to +15 V and −8 V are supported.

The analog front end includes black level clamping, CDS, VGA,

and a 12-bit ADC. The timing generator and V-driver provide

all the necessary CCD clocks: RG, H-clocks, vertical clocks,

sensor gate pulses, substrate clock, and substrate bias control.

The internal registers are programmed using a 3-wire serial

interface.

Packaged in an 8 mm × 8 mm CSPBGA, the AD9925 is specified over an operating temperature range of −25°C to +85°C.

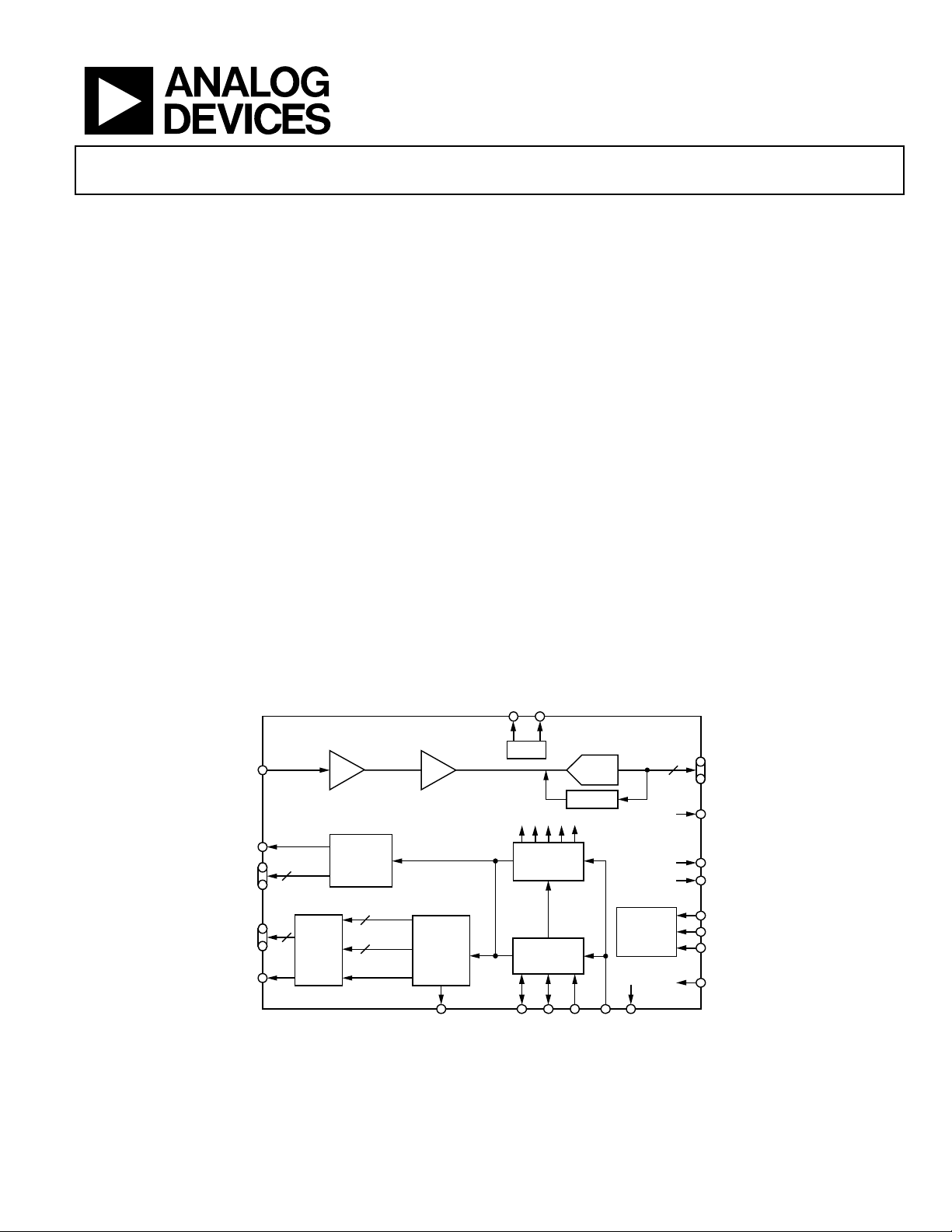

FUNCTIONAL BLOCK DIAGRAM

6dB TO 42dB

VGA

VERTICAL

TIMING

CONTROL

VSUB

0dB, –2dB, –4dB

V-DRIVER

CDS

HORIZONTAL

DRIVERS

XV1 TO XV8

8

XSG1 TO XSG6

6

SUBCK

CCDIN

RG

H1 TO H4

V1, V2

V3A, V3B

V4, V6

V5A, V5B

V7, V8

SUBCK

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

4

10

REFT REFB

Figure 1.

AD9925

VREF

12-BIT

ADC

CLAMP

INTERNAL CLOCKS

PRECISION

TIMING

GENERATOR

SYNC

GENERATOR

HD VD SYNC

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

CLI

www.analog.com

INTERNAL

REGISTERS

CLO

12

DOUT

DCLK

MSHUT

STROBE

SL

SDI

SCK

RSTB

04637-0-001

AD9925

TABLE OF CONTENTS

Specifications..................................................................................... 3

Vertical Timing Generation ...................................................... 22

Digital Specifications........................................................................ 4

Vertical Driver Specifications ......................................................... 5

Analog Specifications....................................................................... 6

Timing Specifications....................................................................... 7

Absolute Maximum Ratings............................................................ 8

Package Thermal Characteristics ............................................... 8

ESD Caution.................................................................................. 8

Pin Configuration and Function Descriptions............................. 9

Te r mi n ol o g y .................................................................................... 11

Equivalent Circuits......................................................................... 12

Typical Performance Characteristics ...........................................13

System Overview ........................................................................ 14

Precision Timing High Speed Timing Generation.................. 15

Horizontal Clamping and Blanking......................................... 18

Horizontal Timing Sequence Example.................................... 21

Ver t ic al Tim in g Ex am p l e........................................................... 34

Shutter Timing Control............................................................. 36

Example of Exposure and Readout of Interlaced Frame........... 41

FG_TRIG Operation.................................................................. 43

Analog Front End Description and Operation ...................... 45

Vertical Driver Signal Configuration ...................................... 47

Power-Up and Synchronization ............................................... 51

Standby Mode Operation.......................................................... 55

Circuit Layout Information....................................................... 57

Serial Interface Timing.............................................................. 59

Complete Listing for Register Bank 1 .......................................... 62

Complete Listing for Register Bank 2 .......................................... 66

Complete Listing for Register Bank 3 .......................................... 87

Outline Dimensions ....................................................................... 94

Ordering Guide .......................................................................... 94

REVISION HISTORY

10/04—Data Sheet Changed from Rev. 0 to Rev. A

Changes to Specifications........................................................................................3

Added Stress Disclaimer..........................................................................................8

Changes to Figure 12................................................................................................13

Changes to Figure 22................................................................................................18

Changes to Figure 55................................................................................................45

Change to DC Restore Section ...............................................................................45

Change to Correlated Double Sampler Section....................................................45

Change to ADC Section...........................................................................................46

Change to Digital Data Outputs Section...............................................................46

Added Paragraph to Digital Data Outputs Section..............................................46

Changes to Table 34..................................................................................................55

Change to Circuit Layout Information Section....................................................57

Changes to Register Address Bank 1, Bank 2, and Bank 3 Section ...................60

Changes to Table 40..................................................................................................63

Change to Table 46 ...................................................................................................65

Changes to Tables 47–56, 58–73.............................................................................66

4/04—Revision 0: Initial Version

Rev. A | Page 2 of 96

AD9925

SPECIFICATIONS

Table 1.

Parameter Min Typ Max Unit

TEMPERATURE RANGE

Operating –25 +85 °C

Storage –65 +150 °C

POWER SUPPLY VOLTAGES

AVDD (AFE Analog Supply) 2.7 3.0 3.6 V

TCVDD (Timing Core Analog Supply) 2.7 3.0 3.6 V

RGVDD (RG Driver) 2.7 3.0 3.6 V

HVDD (H1 to H4 Drivers) 2.7 3.0 3.6 V

DRVDD (Data Output Drivers) 2.7 3.0 3.6 V

DVDD (Digital) 2.7 3.0 3.6 V

V-DRIVER SUPPLY VOLTAGES

VDVDD (V-Driver Input Logic Supply) 2.7 3.0 3.6 V

VH1, VH2 (V-Driver High Supply for 3-Level Outputs) 10.5 15.0 16.0 V

VM1, VM2 (V-Driver Mid Supply for 3-Level and 2-Level Outputs) –1.0 0.0 +3.0 V

VL1, VL2 (V-Driver Low Supply for 3-Level and 2-Level Outputs) –10.0 –7.5 –6.0 V

POWER DISSIPATION—AFETG Section Only (see Figure 9 for Power Curves)

36 MHz, 3.0 V Supply, 100 pF Load on Each H1 to H4 Output, 20 pF RG Load 370 mW

Standby 1 Mode 10 mW

Standby 2 Mode 10 mW

Standby 3 Mode 1 mW

Power from HVDD Only1 130 mW

Power from RGVDD Only 10 mW

Power from AVDD Only 105 mW

Power from TCVDD Only 42 mW

Power from DVDD Only 57 mW

Power from DRVDD Only 26 mW

POWER DISSIPATION—V-Driver Section Only (VDVDD, VH, VL)

Normal Operation (VH = 15.0 V, VL = −7.5 V)

Standby 1 Mode2 70 mW

Standby 2 Mode2 70 mW

Standby 3 Mode2 110 mW

MAXIMUM CLOCK RATE (CLI) 36 MHz

1

The total power dissipated by the HVDD supply may be approximated using the equation Total HVDD Power = [C

Reducing the H-loading and/or using a lower HVDD supply will reduce the power dissipation. C

2

The power dissipated by the V-driver circuitry depends on the logic states of the inputs as well as actual CCD operation; default dc values are used for each measure-

ment, in each mode of operation. Load conditions are described in the section.

2

Vertical Driver Specifications

60 mW

× HVDD × Pixel Frequency] × HVDD.

is the total capacitance seen by all H-outputs.

LOAD

LOAD

Rev. A | Page 3 of 96

AD9925

DIGITAL SPECIFICATIONS

RGVDD = HVDD = DVDD = DRVDD = 2.7 V to 3.6 V, CL = 20 pF, T

Table 2.

Parameter Symbol Min Typ Max Unit

LOGIC INPUTS

High Level Input Voltage VIH 2.1 V

Low Level Input Voltage V

High Level Input Current I

Low Level Input Current I

Input Capacitance C

LOGIC OUTPUTS (Powered by DVDD, DRVDD)

High Level Output Voltage at IOH = 2 mA V

Low Level Output Voltage at IOL = 2 mA VOL 0.5 V

RG and H-DRIVER OUTPUTS (Powered by HVDD, RGVDD)

High Level Output Voltage at Maximum Current VDD – 0.5 V

Low Level Output Voltage at Maximum Current 0.5 V

Maximum Output Current (Programmable) 30 mA

Maximum Load Capacitance (for Each Output) 100 pF

MIN

to T

IL

IH

IL

IN

OH

, unless otherwise noted.

MAX

0.6 V

10 µA

10 µA

10 pF

VDD – 0.5 V

Rev. A | Page 4 of 96

AD9925

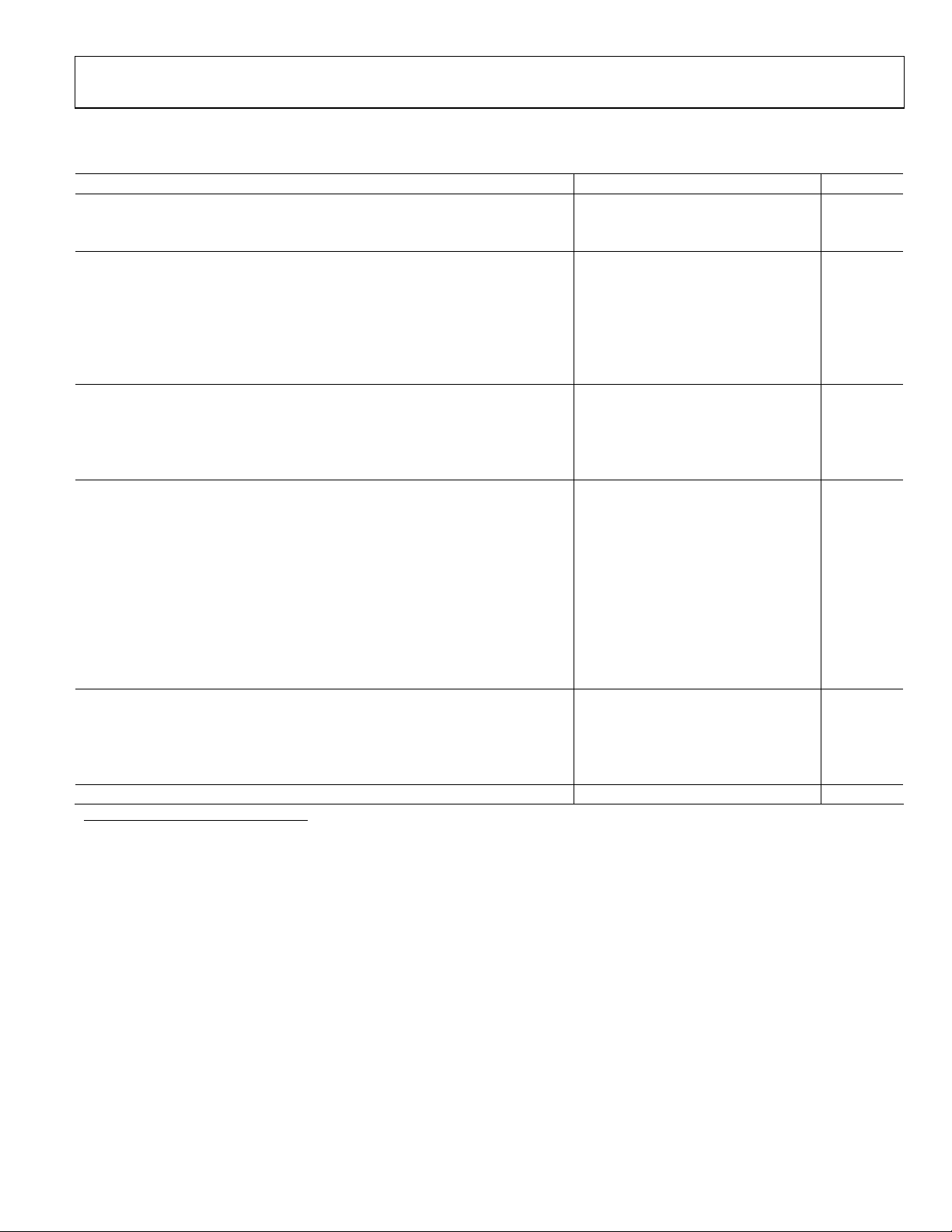

VERTICAL DRIVER SPECIFICATIONS

VDVDD = 3.3 V, VH = 15 V, VM = 0 V, VL = −7.5 V, CL shown in load model, 25°C.

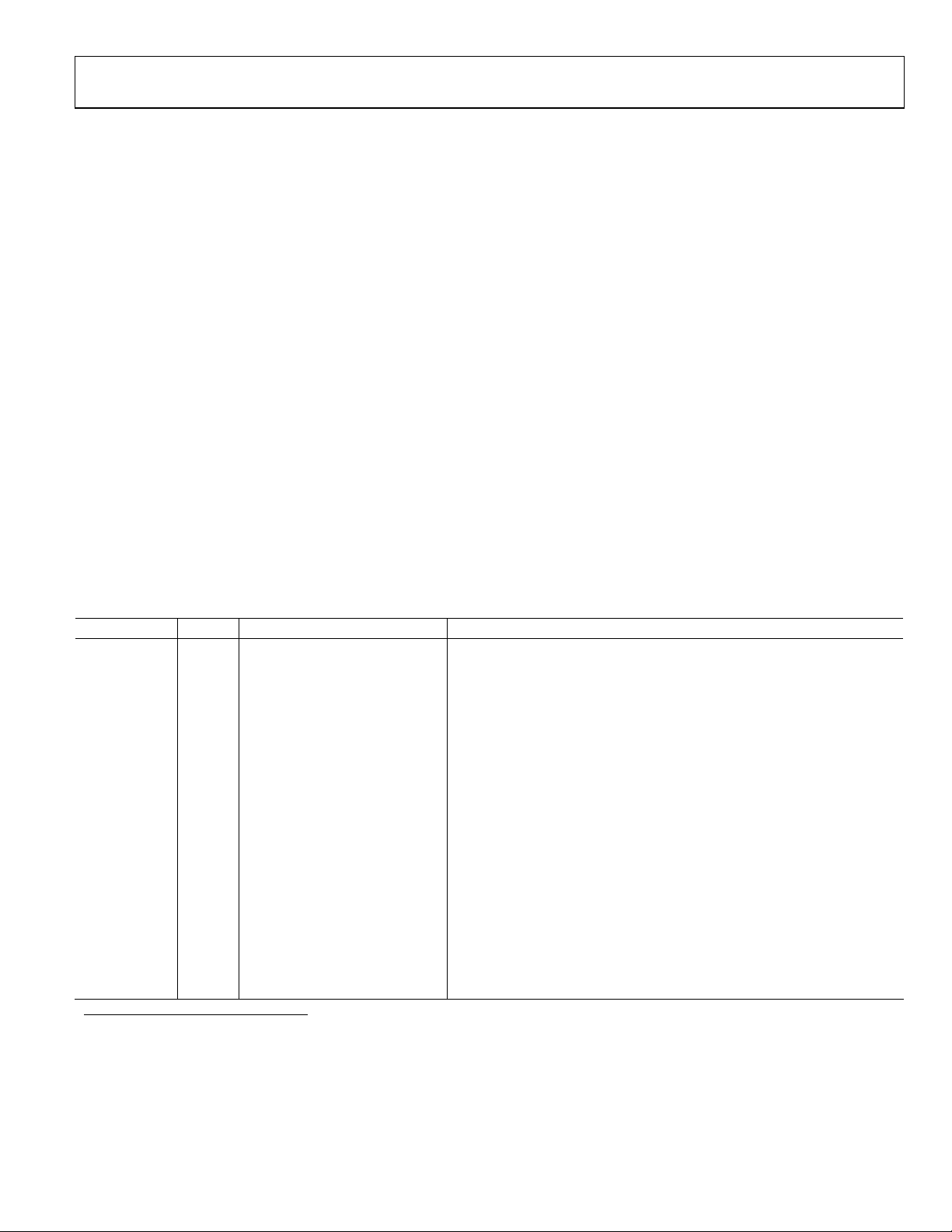

Table 3.

Parameter Symbol Min Typ Max Unit

3-LEVEL OUTPUTS (V1, V2, V3A, V3B, V5A, V5B)

(Simplified Load Conditions, 6000 pF to Ground)

Delay Time, VL to VM and VM to VH t

Delay Time, VM to VL and VH to VM t

Rise Time, VL to VM and VM to VH t

Fall Time, VM to VL and VH to VM t

Output Currents

At −7.25 V 10.0 mA

At −0.25 V −5.0 mA

At +0.25 V 5.0 mA

At +14.75 V −7.2 mA

2-LEVEL OUTPUTS (V4, V6, V7, V8)

(Simplified Load Conditions, 6000 pF to Ground)

Delay Time, VL to VM t

Delay Time, VM to VL t

Rise Time, VL to VM t

Fall Time, VM to VL t

Output Currents

At −7.25 V 10.0 mA

At −0.25 V −5.0 mA

SUBCK OUTPUT

(Simplified Load Conditions, 1000 pF to Ground)

Delay Time, VL to VH t

Delay Time, VH to VL t

Rise Time, VL to VH t

Fall Time, VH to VL t

Output Currents

At −7.25 V 5.4 mA

At +14.75 V −4.0 mA

SERIAL VERTICAL CLOCK RESISTANCE 30 Ω

GND VERTICAL CLOCK RESISTANCE 10 Ω

, t

100 ns

PLM

PMH

, t

200 ns

PML

PHM

, t

500 ns

RLM

RMH

, t

500 ns

FML

FHM

100 ns

PLM

PML

500 ns

RLM

500 ns

FML

100 ns

PLH

200 ns

PHL

200 ns

RLH

200 ns

FHL

200 ns

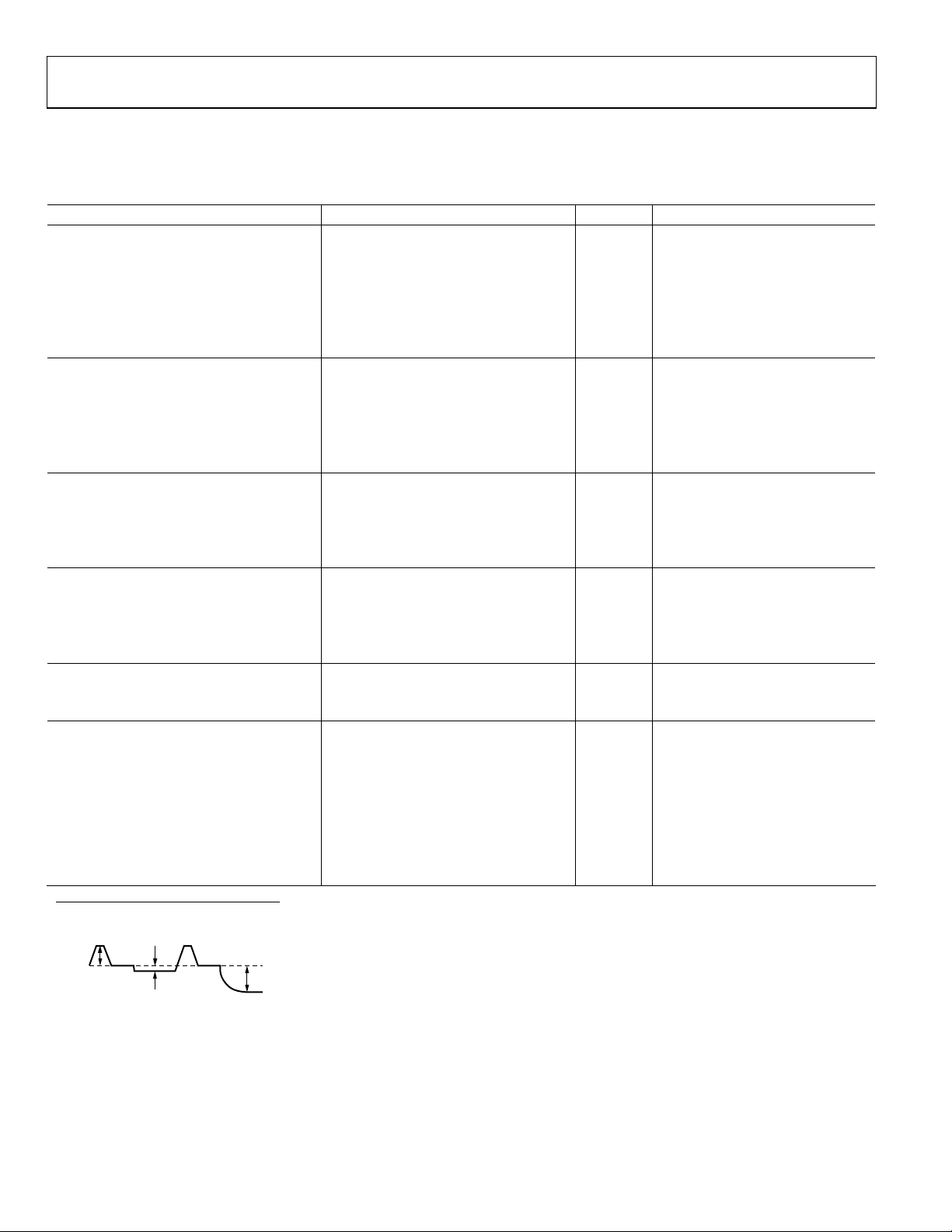

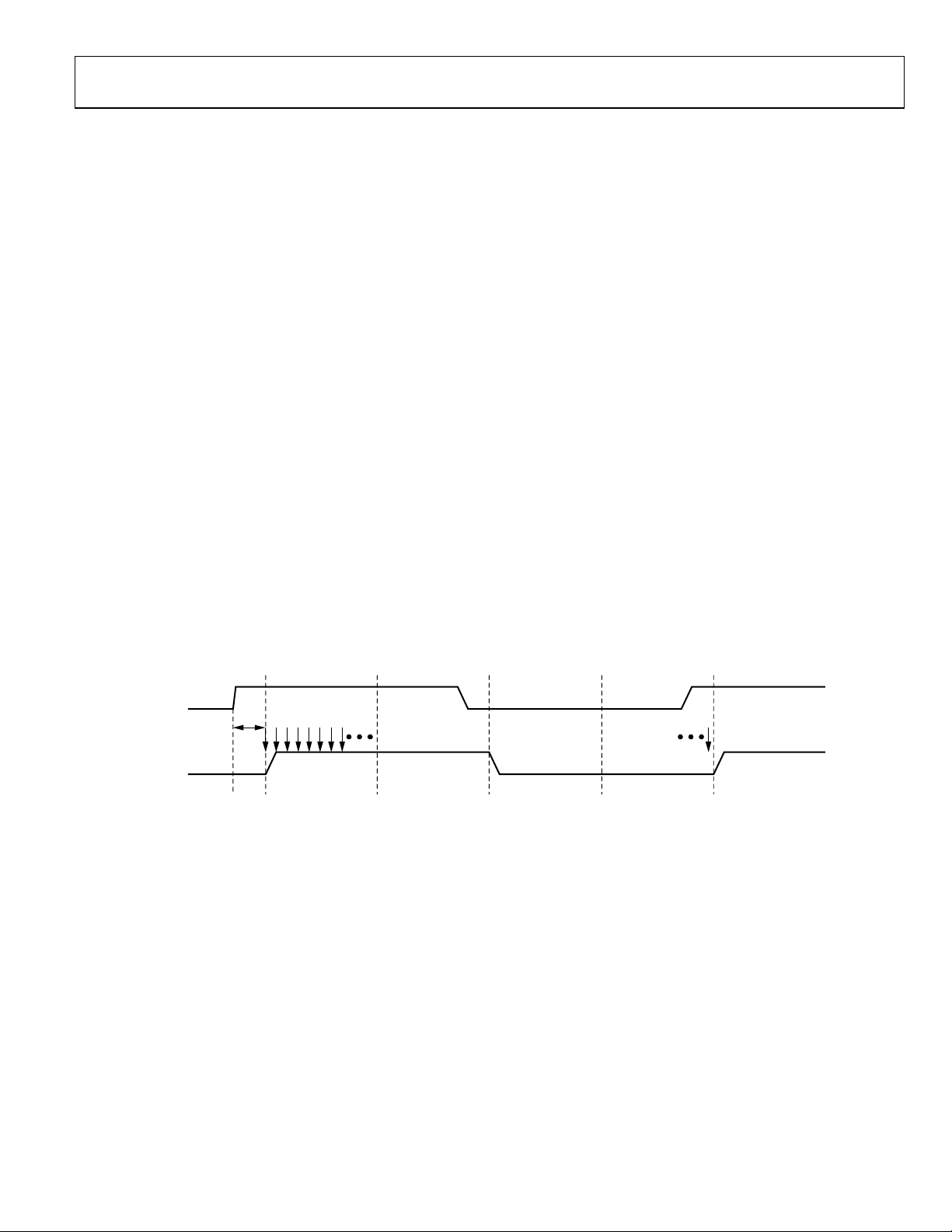

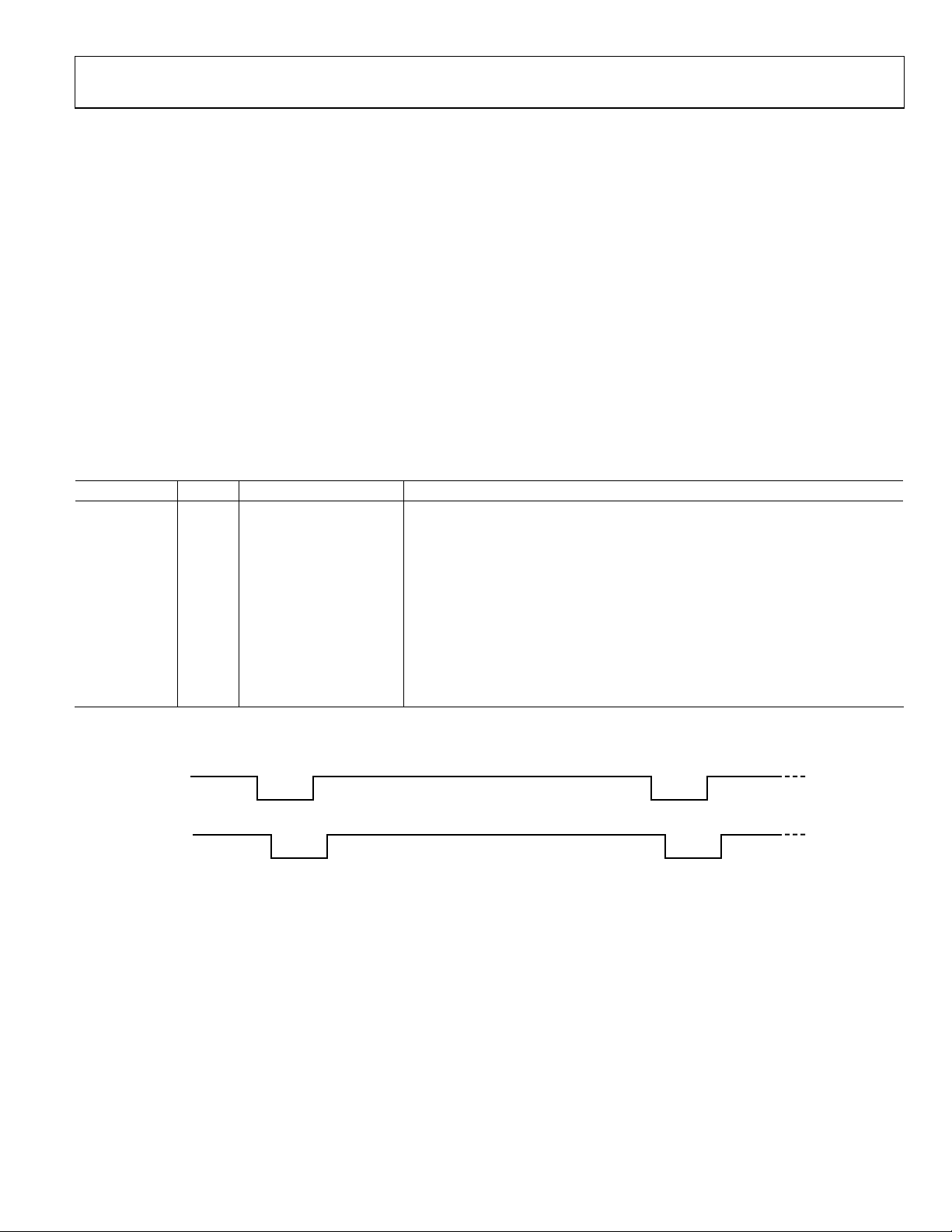

V-DRIVER

INPUT

V-DRIVER

OUTPUT

50%

10%

90%

t

PLM

t

RLM

,

t

PMH

50%

,

t

,

RMH

,

t

RLH

t

PLH

90%

10%

t

,

t

,

PML

t

PHM

PHL

t

,

t

,

FHM

t

FHL

04637-0-079

FML

Figure 2. Definition of V-Driver Timing Specifications

Rev. A | Page 5 of 96

AD9925

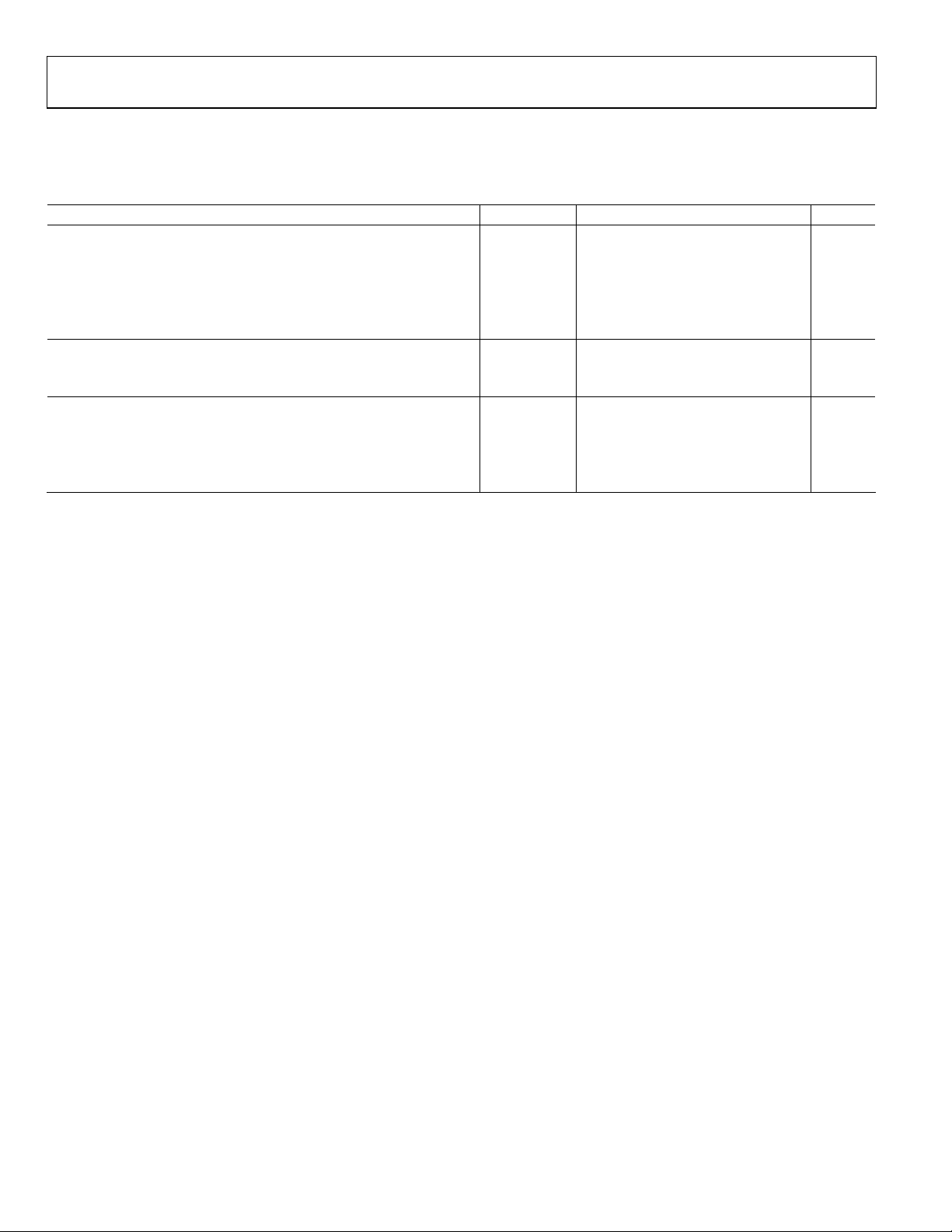

ANALOG SPECIFICATIONS

AVDD1 = 3.0 V, f

Table 4.

Parameter Min Typ Max Unit Test Conditions/Comments

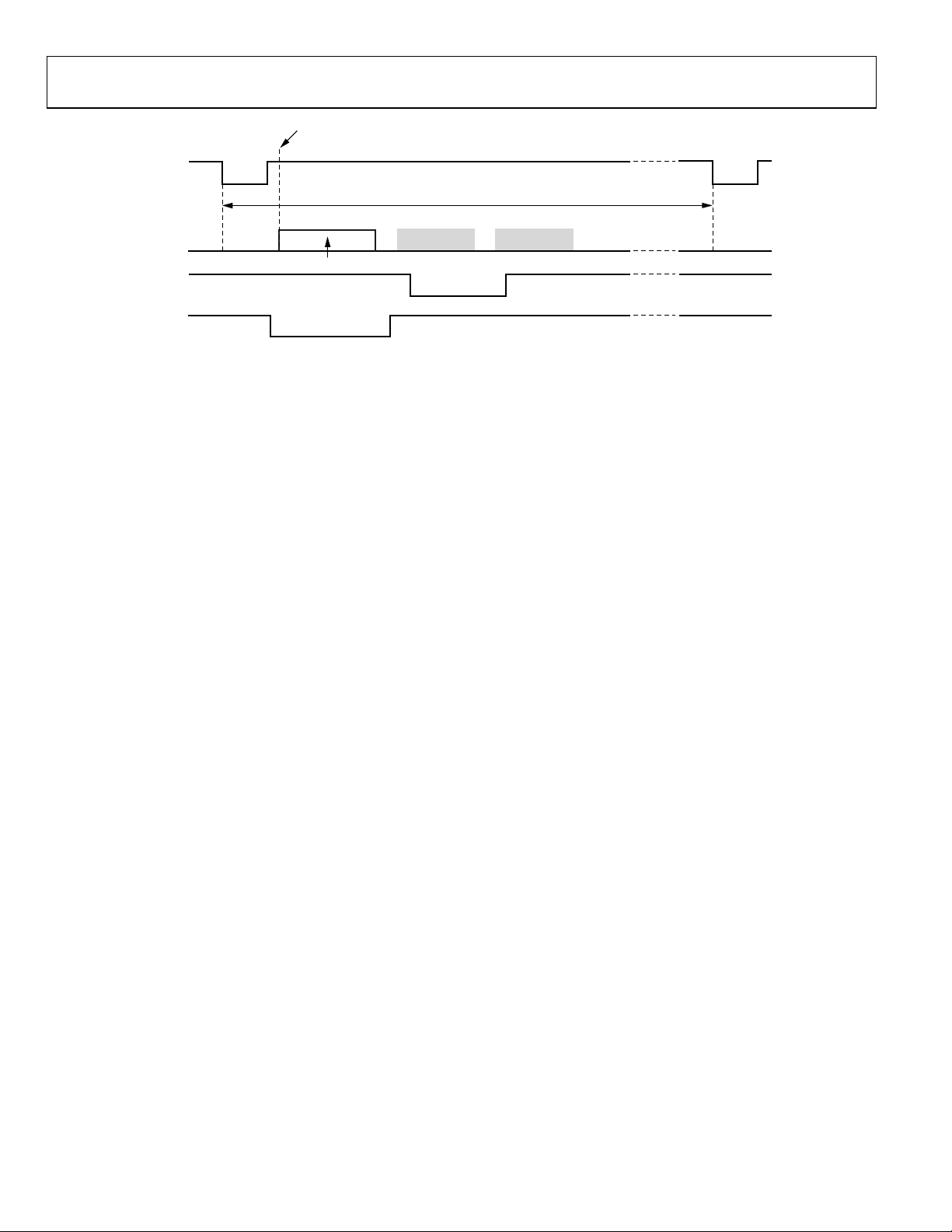

CDS Input Characteristics Definition.

Allowable CCD Reset Transient 500 mV

Maximum Input Range before Saturation

0 dB CDS Gain (Default Setting) 1.0 V p-p

−2 dB CDS Gain 1.25 V p-p

−4 dB CDS Gain 1.6 V p-p

Maximum CCD Black Pixel Amplitude +200/–100 mV Positive Offset Definition1

VARIABLE GAIN AMPLIFIER (VGA)

Gain Control Resolution 1024 Steps

Gain Monotonicity Guaranteed

Gain Range

Minimum Gain (VGA Code 0) 6 dB

Maximum Gain (VGA Code 1023) 42 dB

BLACK LEVEL CLAMP

Clamp Level Resolution 256 Steps

Clamp Level Measured at ADC Output.

Minimum Clamp Level (Code 0) 0 LSB

Maximum Clamp Level (Code 255) 255 LSB

ANALOG-TO-DIGITAL CONVERTER (ADC)

Resolution 12 Bits

Differential Nonlinearity (DNL) –1.0 ±0.5 +1.0 LSB

No Missing Codes Guaranteed

Full-Scale Input Voltage 2.0 V

VOLTAGE REFERENCE

Reference Top Voltage (REFT) 2.0 V

Reference Bottom Voltage (REFB) 1.0 V

SYSTEM PERFORMANCE Includes Entire Signal Chain.

Gain Accuracy

Low Gain (VGA Code 0) 5.0 5.5 6.0 dB Gain = (0.0351 × Code) + 5.5 dB.

Maximum Gain (VGA Code 1023) 40.5 41.5 42.5 dB

Peak Nonlinearity, 500 mV Input Signal 0.1 % 12 dB Gain Applied.

Total Output Noise 0.8 LSB rms

Power Supply Rejection (PSR) 50 dB

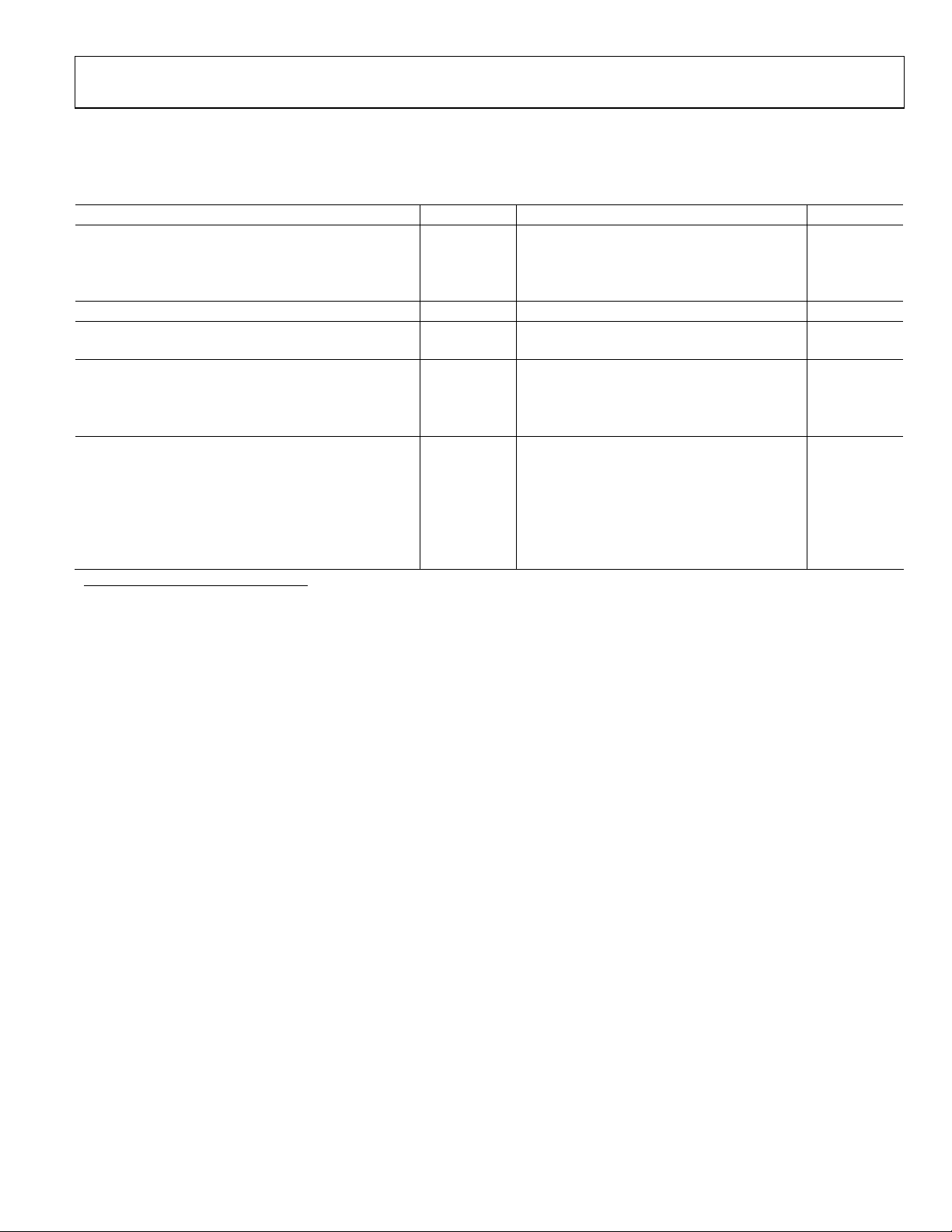

1

Input signal characteristics are defined as

= 36 MHz, typical timing specifications, T

CLI

MIN

to T

, unless otherwise noted.

MAX

1

AC Grounded Input, 6 dB Gain Applied.

Measured with Step Change on

Supply.

500mV TYP

RESET TRANSIENT

+200mV MAX

OPTICAL BLACK PIXEL

1V MAX

INPUT SIGNAL RANGE

(0dB CDS GAIN)

04637-0-002

Rev. A | Page 6 of 96

AD9925

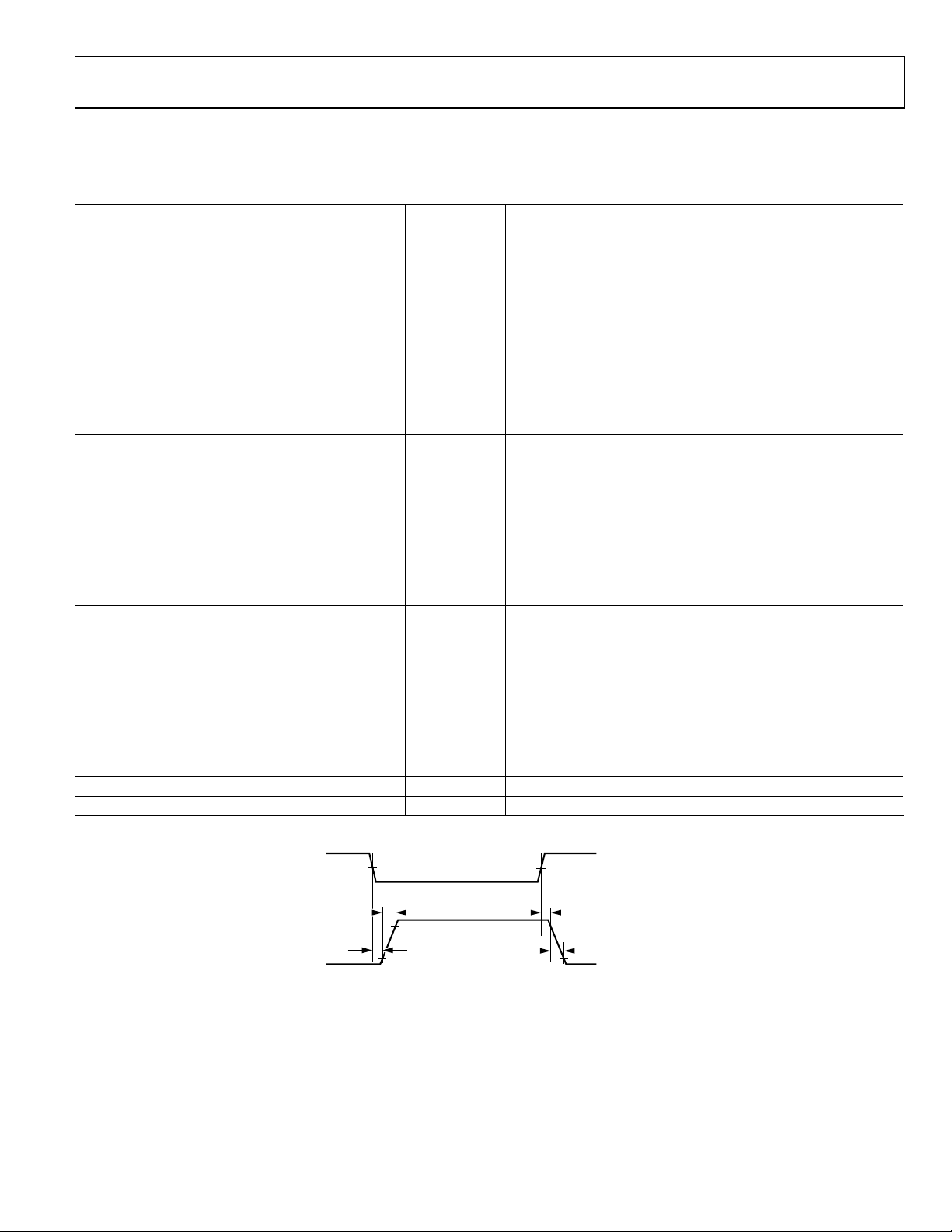

TIMING SPECIFICATIONS

CL = 20 pF, AVDD = DVDD = DRVDD = 3.0 V, f

Table 5.

Parameter Symbol Min Typ Max Unit

MASTER CLOCK, CLI (Figure 17)

CLI Clock Period t

CLI High/Low Pulse Width 11.2 13.9 16.6 ns

Delay from CLI Rising Edge to Internal Pixel Position 0 t

AFE CLPOB PULSE WIDTH

1, 2

(Figure 23 and Figure 29) 2 20 Pixels

AFE SAMPLE LOCATION1 (Figure 20)

SHP Sample Edge to SHD Sample Edge t

DATA OUTPUTS (Figure 21 and Figure 22)

Output Delay from DCLK Rising Edge, Default Value1 t

Inhibited Area for DOUTPHASE Edge Location1 t

Pipeline Delay from SHP/SHD Sampling to DOUT 11 Cycles

SERIAL INTERFACE (Figure 74 and Figure 75)

Maximum SCK Frequency f

SL to SCK Setup Time t

SCK to SL Hold Time t

SDATA Valid to SCK Rising Edge Setup t

SCK Falling Edge to SDATA Valid Hold t

SCK Falling Edge to SDATA Valid Read t

1

Parameter is register-programmable.

2

Minimum CLPOB pulse width is for functional operation only. Wider typical pulses are recommended to achieve good clamp performance.

= 36 MHz, unless otherwise noted.

CLI

CONV

CLIDLY

S1

OD

DOUTINH

SCLK

LS

LH

DS

DH

DV

27.8 ns

6 ns

12.5 13.9 ns

8 ns

SHDLOC SHDLOC + 11

36 MHz

10 ns

10 ns

10 ns

10 ns

10 ns

Rev. A | Page 7 of 96

AD9925

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter With

Respect To

VDVDD VDVSS

VL VDVSS

VH1, VH2 VDVSS

VM1, VM2 VDVSS

AVDD AVSS –0.3 +3.9 V

TCVDD TCVSS –0.3 +3.9 V

HVDD HVSS –0.3 +3.9 V

RGVDD RGVSS –0.3 +3.9 V

DVDD DVSS –0.3 +3.9 V

DRVDD DRVSS –0.3 +3.9 V

RG Output RGVSS –0.3

H1 to H4 Output HVSS –0.3

Digital Outputs DVSS –0.3

Digital Inputs DVSS –0.3

SCK, SL, SDATA DVSS –0.3

REFT/REFB, CCDIN AVSS –0.3

Junction Temperature

Lead Temperature,

10 s

150 °C

350 °C

Min Max Unit

VDVSS

– 0.3

VDVSS

– 10

VL –

0.3

VL –

0.3

VDVSS

+ 4

VDVSS

+ 0.3

VL +

27

VL +

27

RGVD

D + 0.3

HVDD

+ 0.3

DVDD

+ 0.3

DVDD

+ 0.3

DVDD

+ 0.3

AVDD

+ 0.3

V

V

V

V

V

V

V

V

V

V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only, and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

PACKAGE THERMAL CHARACTERISTICS

Thermal Resistance

CSPBGA Package: θJA = 40.3°C/W

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate

on the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation

or loss of functionality.

Rev. A | Page 8 of 96

AD9925

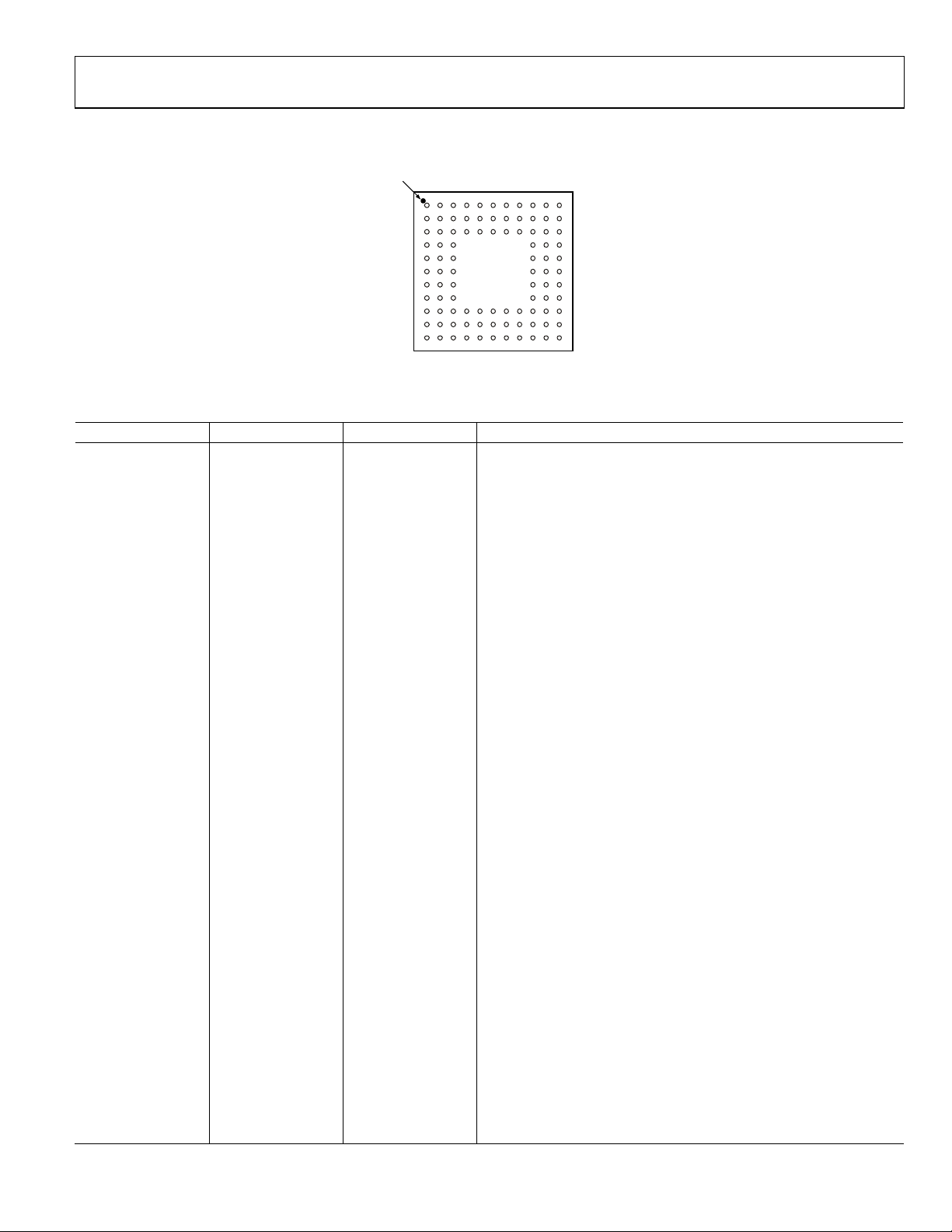

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

A1 CORNER

INDEX AREA

Figure 3. 96-Lead CSPBGA

le 7. Pin Function criptions

Tab Des

nic

Pin No. Mnemo Type Description2

E1, F2, F3 und HVSS P H1 to H4, HL Driver Gro

G2, G3 HVSS P H1 to H4, HL Driver Ground

F1 H1 DO CCD Horizontal Clock 1

G1 H2 DO CCD Horizontal Clock 2

H1, H2, H3 HVDD P H1 to H4, HL Driver Supply

J2, J3 HVDD P H1 to H4, HL Driver Supply

J1 H3 DO CCD Horizontal Clock 3

K1 H4 DO CCD Horizontal Clock 4

K2, L2 RGVSS P RG Driver Ground

L3 RG DO CCD Reset Gate Clock

L4 RGVDD P RG Driver Supply

K3, K4 TCVDD P Analog Supply for Timing Core

J4 CLO DO Clock Output for Crystal

J5 SYNC DI External System Sync Input

K5, L5 TCVSS P Analog Ground for Timing Core

J6 CLI DI Reference Clock Input

K6, L7 AVSS P Analog Ground for AFE

L6 CCDIN AI CCD Signal Input

K7 AVDD P Analog Supply for AFE

L8 REFT AO Voltage Reference Top Bypass

L9 REFB pass AO Voltage Reference Bottom By

J7 MSHUT DO Mechanical Shutter Pulse

J8 SUBCK DO CCD Substrate Clock (E Shutter)

K8 VL P V-Driver Low Supply

K9 VH2 P V-Driver High Supply 2

L10 RSTB DI Reset Bar, Active Low Pulse

K11 SL DI 3-Wire Serial Load Pulse

J11 SCK DI 3-Wire Serial Clock

J10 SDI DI 3-Wire Serial Data Input

J9 V8 VO2 sfer Clock CCD Vertical Tran

K10 V7 VO2 CCD Vertical Transfer Clock

H9 STROBE DO Strobe Pulse

H11 VM2 P V-Driver Mid Supply 2

H10 V6 VO2 CCD Vertical Transfer Clock

G10 V4 VO2 CCD Vertical Transfer Clock

G11 V2 VO2 CCD Vertical Transfer Clock

G9 VD DIO Vertical Sync Pulse (Input in Slave Mode, Output in Master Mode)

1234567 9108

1

11

AD9925

TO

PVIEW

(Not to Scale)

Package Pin Configuration

A

B

C

D

E

F

G

H

J

K

L

04637-0-003

Rev. A | Page 9 of 96

AD9925

Pin No. Mnemonic Type1 Description2

F9 HD DIO Horizontal Sync Pulse (Input in Slave Mode, Output in Master Mode)

F10 DVSS P Digital Ground

F11 DVDD ower Supply P Digital Logic P

E9 V5B VO3 CCD Vertical Transfer Clock

D9 V5A VO3 CCD Vertical Transfer Clock

E10 DCLK DO Data Clock Output

D11 D0 DO Data Output (LSB)

C10 D1 DO Data Output

C11 D2 DO Data Output

B10 D3 DO Data Output

B11 D4 DO Data Output

A10 D5 DO Data Output

A9 D6 DO Data Output

C9 V3B VO3 ck CCD Vertical Transfer Clo

B9 V3A 3 lock VO CCD Vertical Transfer C

B8 V1 VO3 CCD Vertical Transfer Clock

A8 D7 DO Data Output

B7 D8 DO Data Output

A7 D9 DO Data Output

B6 D10 DO Data Output

A6 D11 DO Data Output (MSB)

C8 VM1 P V-Driver Mid Supply 1

C7 VH1 P V-Driver High Supply 1

C6 VL P V-Driver Low Supply

C5 DRVDD P Data Output Driver Supply

B5 DRVSS P Data Output Driver Ground

A5 VSUB DO CCD Substrate Bias

A4 VDVDD P V-Driver Logic Supply

B4 VDVSS P V-Driver Logic Ground

A1, A2, A3 NC Not Internally Connected

B1, B2, B3 NC Not Internally Connected

C1, C NC Not Internally Connected 2, C3

C4, D1, D2 NC Not Internally Connected

D3, E2, E3 NC Not Internally Connected

D10, E11 NC Not Internally Connected

L1, L11, A11 NC Not Internally Connected

1

AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; DIO = Digital Input/Output; P = Power; VO2 = V-Driver Output 2-Level; VO3 = V-Driver

Output 3-Level.

2

See Figure 73 for circuit configuration.

Rev. A | Page 10 of 96

AD9925

TERMINOLOGY

Differential Nonlinearity (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Thus, every

code must have a finite width. No missing codes guaranteed to

12-bit resolution indicates that all 4096 codes, respectively, must

be present over all operating conditions.

Peak Nonlinearity

Peak nonlinearity, a full signal chain specification, refers to the

peak deviation of the output of the AD9925 from a true straight

line. The point used as zero scale occurs 0.5 LSB before the first

code transition. Positive full scale is defined as a Level 1 and is

0.5 LSB beyond the last code transition. The deviation is measured from the middle of each particular output code to the true

straight line. The error is then expressed as a percentage of the

2 V ADC full-scale signal. The input signal is always appropriately gained up to fill the ADC’s full-scale range.

Total Output Noise

The rms output noise is measured using histogram techniques.

The standard deviation of the ADC output codes is calculated

in LSB and represents the rms noise level of the total signal

chain at the specified gain setting. The output noise can be converted to an equivalent voltage, using the relationship 1 LSB =

ADC Full Scale/2

ADC. For the AD9925, 1 LSB is 0.488 mV.

Power Supply Rejection (PSR)

The PSR is measured with a step change applied to the supply

pins. The PSR specification is calculated from the change in the

data outputs for a given step change in the supply voltage.

n

codes, where n is the bit resolution of the

Rev. A | Page 11 of 96

AD9925

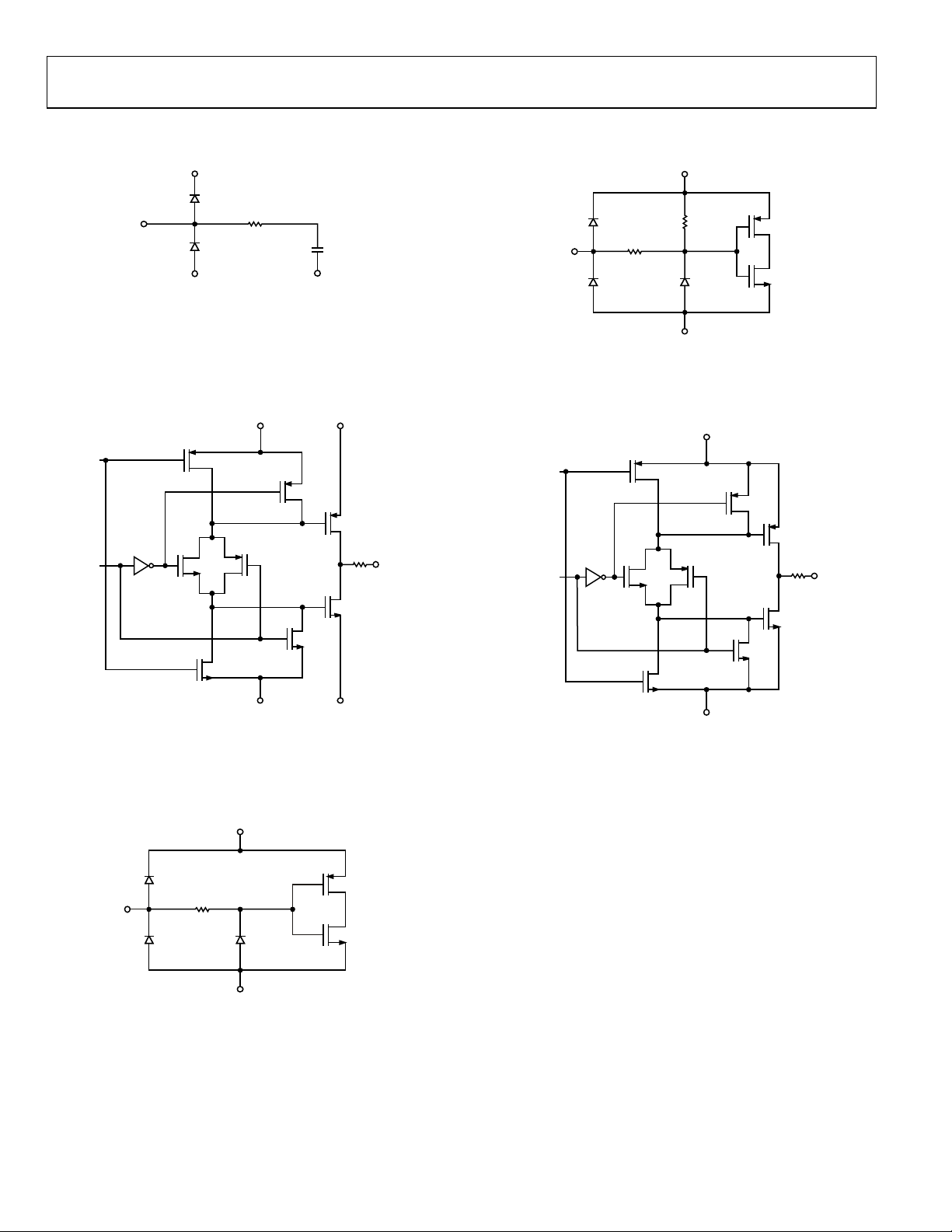

EQUIVALENT CIRCUITS

AVDD

DVDD

DATA

THREE-

STATE

R

AVSS AVSS

Figure 4. CCDIN

DVDD

04637-0-004

DRVDD

100kΩ

300Ω

DVSS

04637-0-075

Figure 7. SL and RSTB Inputs

HVDD OR

RGVDD

RG, H1 TO H4

DOUT

THREE-STATE

OUTPUT

DVSS DRVSS

Figure 5. Digital Data Outputs

DVDD

330Ω

DVSS

04637-0-006

04637-0-005

HVSS OR

RGVSS

Figure 8. H1 to H4, RG Drivers

04637-0-007

Figure 6. Digital Inputs

Rev. A | Page 12 of 96

AD9925

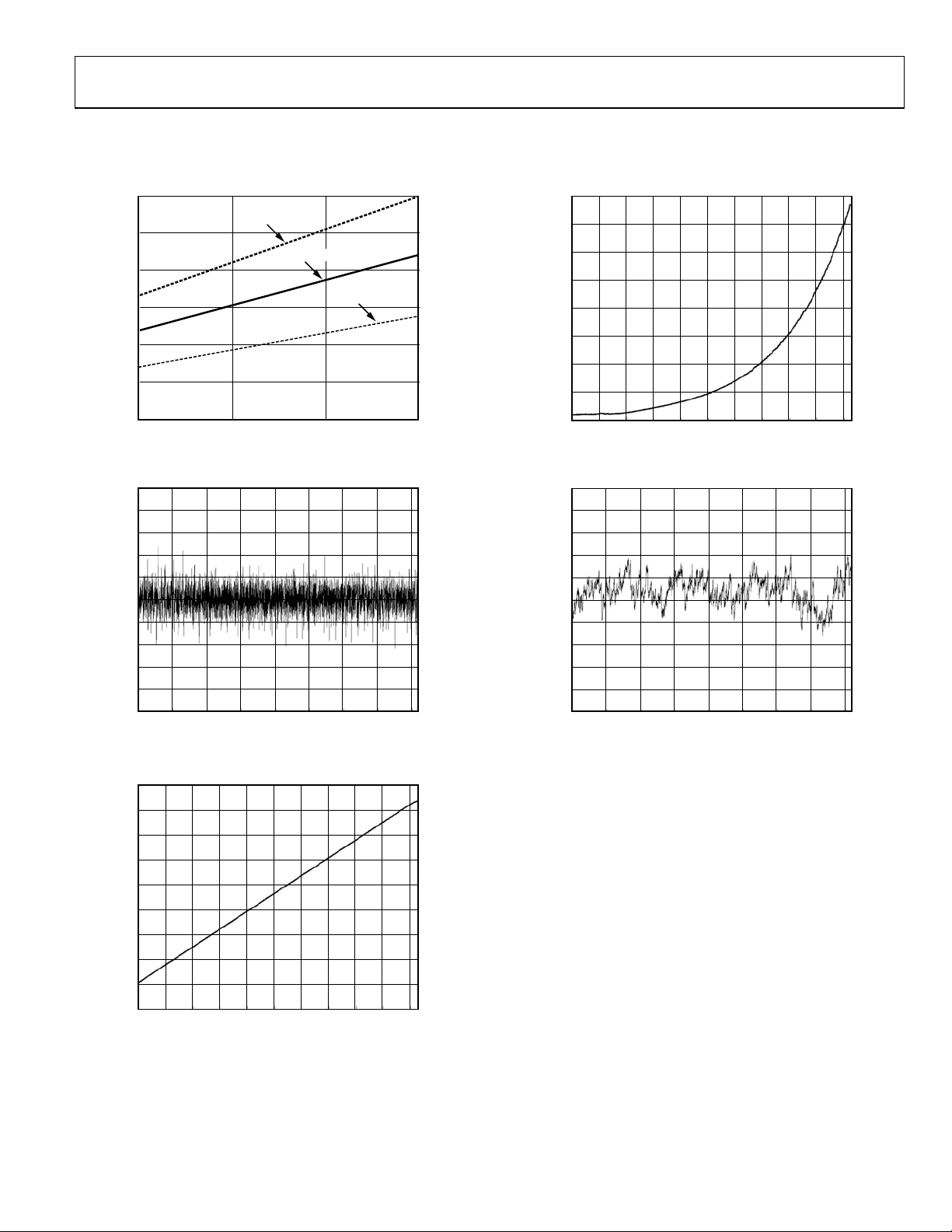

TYPICAL PERFORMANCE CHARACTERISTICS

450

400

350

300

250

POWER DISSIPATION (mW)

200

VDD = 3.3V

V

DD

= 3.0V

V

DD

= 2.7V

40

35

30

25

20

15

NOISE (LSB)

10

5

150

SAMPLE RATE (MHz)

Figure 9. Power vs. Sample Rate

1.0

0.8

0.6

0.4

0.2

0

LSB

–0.2

–0.4

–0.6

–0.8

–1.0

0 500 200015001000 2500 35003000 4000

ADC OUTPUT CODE

Figure 10. Typical DNL Performance

45

40

35

30

25

20

GAIN (dB)

15

10

5

0

0 100 500400200 300 600 900800700 1000

GAIN CODE (Decimal)

Figure 11. Typical VGA Gain Curve

0

3618 24 30

04637-0-084

04637-0-080

0 100 500400200 300 600 900800700 1000

GAIN CODE (Decimal)

Figure 12. Total Output Noise vs. VGA Gain

5

4

3

2

1

0

LSB

–1

–2

–3

–4

–5

0 500 200015001000 2500 35003000 4000

ADC OUTPUT CODE

Figure 13. Typical INL Performance

04637-0-083

04637-0-082

04637-0-081

Rev. A | Page 13 of 96

AD9925

SYSTEM OVERVIEW

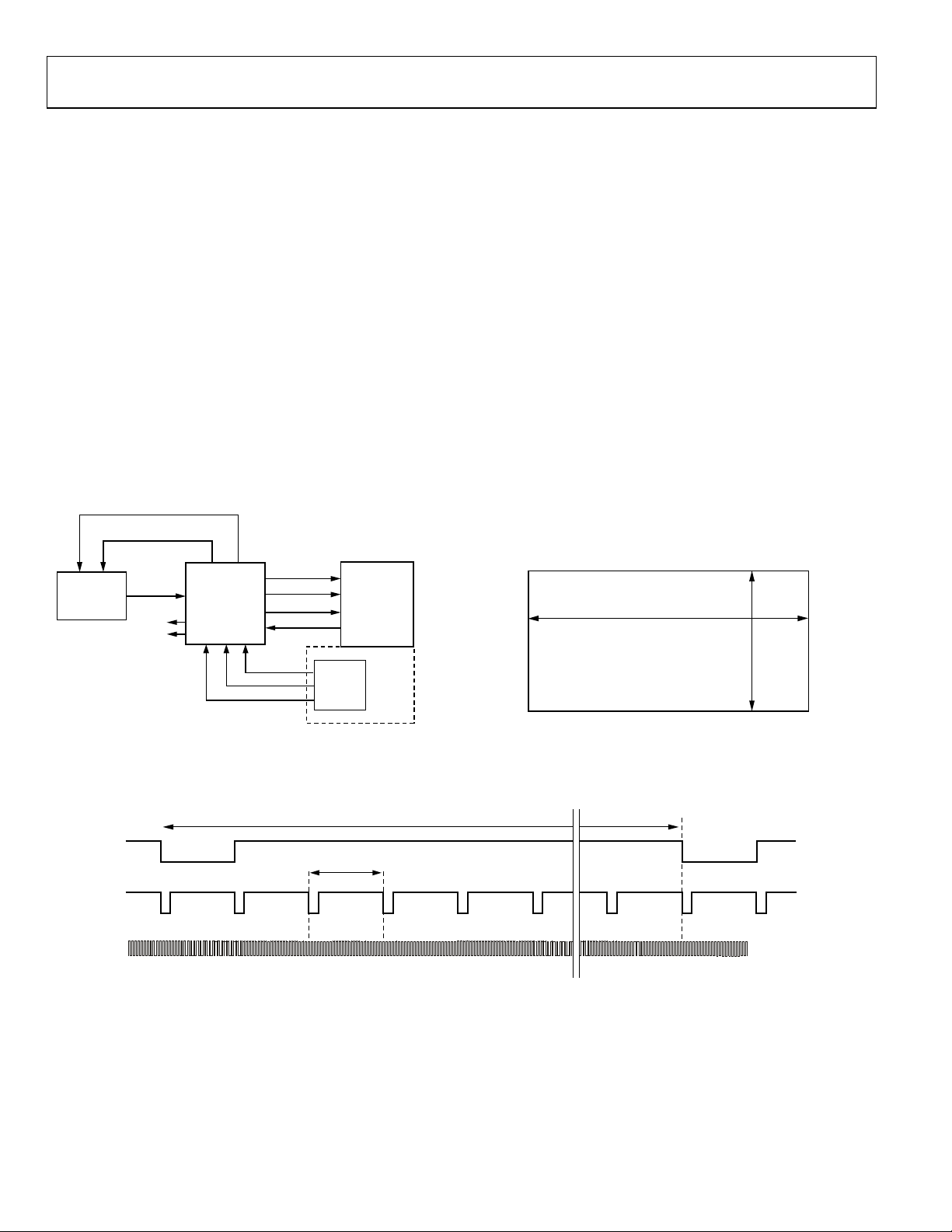

Figure 14 shows the typical system block diagram for the

AD9925 used in master mode. The CCD output is processed

the AD9925’s AFE circuitr

y, which consists of a CDS, VGA,

black level clamp, and ADC. The digitized pixel informa

sent to the digital image processor chip, which performs the

postprocessing and compression. To operate the CCD, all CCD

timing parameters are programmed into the AD9925 from the

system microprocessor through the 3-wire serial interface.

From the system master clock, CLI, provided by the image

processor or external crystal, the AD9925 generates the CCD’s

horizontal and vertical clocks and internal AFE clocks. E

synchronization is provided by a SYNC pulse from the micro

processor, which will reset internal counters and resync the VD

and HD outputs. The AD9925 also contains an optional reset

pin, RSTB, which may be used to perform an asynchronous

hardware reset function.

V1A, V2, V3A, V3B, V4, V5A,

V5B, V6, V7, V8, SUBCK, VSUB

H1 TO H4, RG

SERIAL

INTERFACE

DOUT

DCLK

HD, VD

CLI

DIGITAL

IMAGE

PROCESSING

ASIC

µP

CCD

CCDIN

MSHUT

STROBE

AD9925

AFETG

+

V-DRIVER

SYNC

RSTB

Figure 14. Typical System Block Diagram, Master Mode

by

tion is

xternal

-

04637-0-008

Alternatively, the AD9925 may be operated in slave mode, in

which the VD and HD are provided externally from the image

processor. In this mode, all AD9925 timing will be synchronized with VD and HD.

The H-drivers for H1 to H4 and RG are included in the

AD9925, allowing these clocks t directly connected to the

CCD. An H-d d. A high

rive voltage of up to 3.3 V is supporte

o be

voltage V-driver is also included for the vertical clocks, allowing

irect connection to the CCD. The SUBCK and VSUB signals

d

ay require external transistors, depending on the CCD used.

m

The AD9925 also includes programmable MSHUT and

STROBE outputs, which may be used to trigger mechanical

shutter and strobe (flash) circuitry.

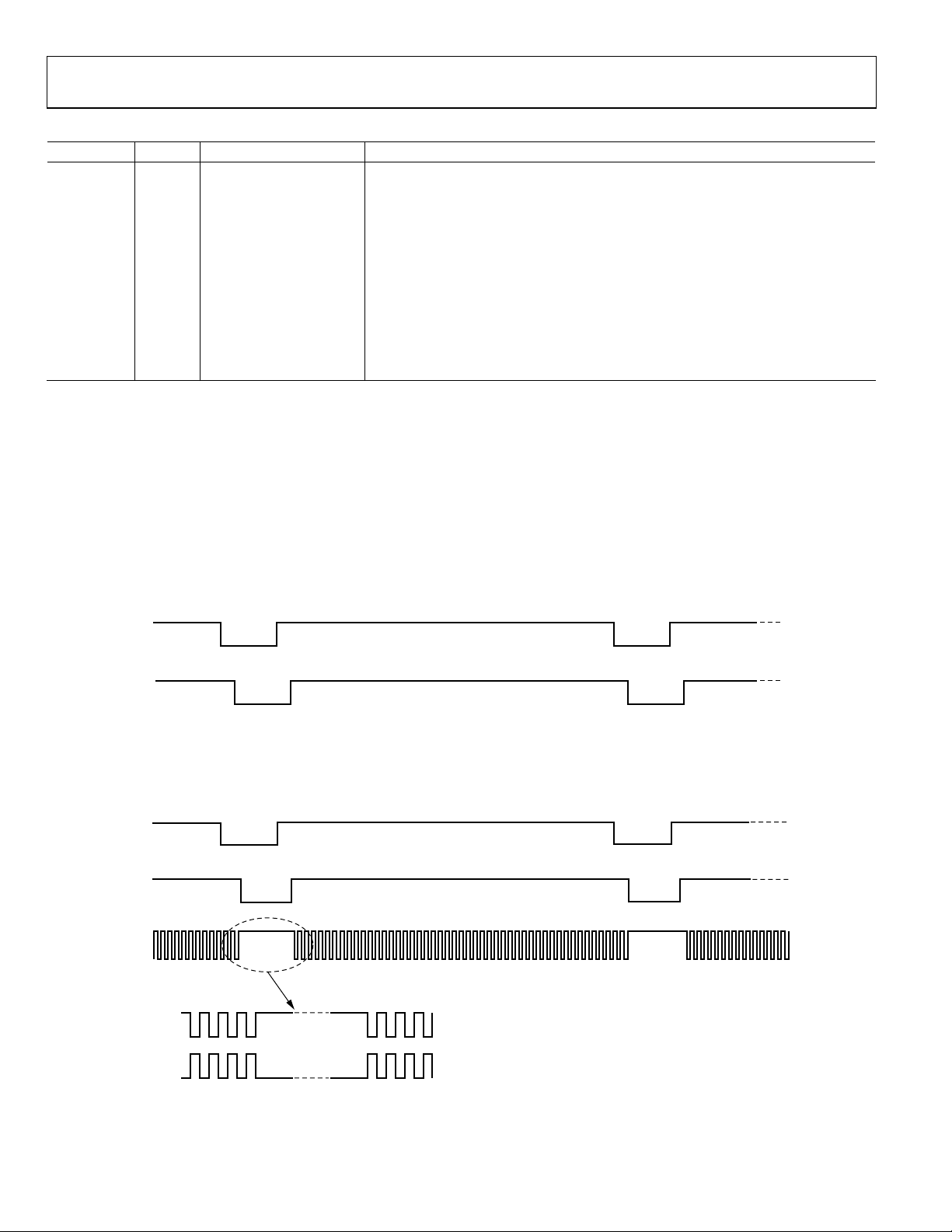

Figure 15 and Figure 16 show the maximum horizontal and

vertical counter dimensions for the AD9925. All internal horizontal and vertical clocking is controlled by these counters to

specify line and pixel locations. Maximum HD length is 8192

pixels per line, and maximum VD length is 4096 lines per field.

MAXIMUM

COUNTER

DIMENSIONS

13-BIT HORIZONTAL = 8192 PIXELS MAX

12-BIT VERTICAL = 4096 LINES MAX

04637-0-009

Figure 15. Vertical and Horizontal Counters

MAX VD LENGTH IS 4096 LINES

VD

HD

CLI

MAX HD LENGTH IS 8192 PIXELS

04637-0-010

Figure 16. Maximum VD/HD Dimensions

Rev. A | Page 14 of 96

AD9925

PRECISION TIMING HIGH SPEED TIMING GENERATION

The AD9925 generates high speed timing signals using the flexible Precision Timing core. This core is the foundation that gen-

erates the timing used for both the CCD and the AFE: the reset

gate (RG), horizontal drivers H1 to H4, and the SHP/SHD sample

clocks. The unique architecture provides precise control over

the horizontal CCD readout and the AFE correlated double sampling, allowing the system designer to optimize image quality.

The high speed timing of the AD9925 operates the same in

either master or slave mode configuration. For more information on synchronization and pipeline delays, see the Power-Up

and Synchronization section.

Timing Resolution

The Precision Timing core uses a 13 master clock input (CLI) as

a reference. This clock should be the same as the CCD pixel

clock frequency. Figure 17 illustrates how the internal timing

core divides the master clock period into 48 steps or edge positions. Using a 20 MHz CLI frequency, the edge resolution of the

Precision Timing core is 1 ns. If a 1× system clock is not available, it is also possible to use a 2× reference clock by programming the CLIDIVIDE register (Addr x30). The AD9925 will

then internally divide the CLI frequency by two.

crystal can be placed between the CLI and CLO pins to generate

the master clock for the AD9925. For more information on

using a crystal, see Figure 72.

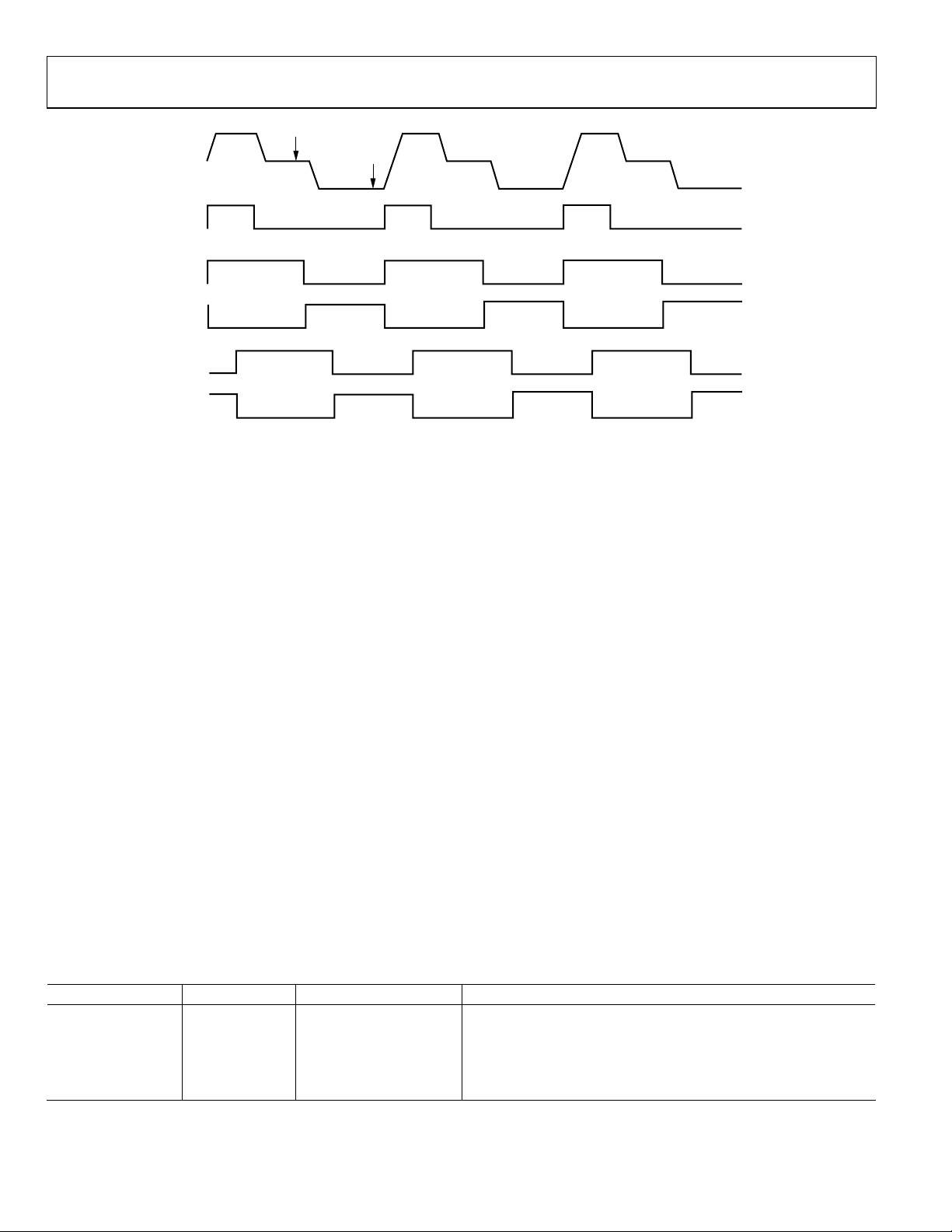

High Speed Clock Programmability

Figure 18 shows how the high speed clocks RG, H1 to H4, SHP,

and SHD are generated. The RG pulse has programmable rising

and falling edges and may be inverted using the polarity control.

The horizontal clocks, H1 and H3, have programmable rising

and falling edges and polarity control. The H2 and H4 clocks

are always inverses of H1 and H3, respectively. Table 8 summarizes the high speed timing registers and their parameters.

Figure 19 shows the typical 2-phase H-clock arrangement in

which H3 and H4 are programmed for the same edge location

as H1 and H2.

The edge location registers are 6 bits wide, but there are only

48 valid edge locations available. Therefore, the register values

are mapped into four quadrants, with each quadrant containing

12 edge locations. Table 9 shows the correct register values for

the corresponding edge locations.

The AD9925 also includes a master clock output, CLO, which is

the inverse of CLI. This output can be used as a crystal driver. A

POSITION

CLI

1 PIXEL

PERIOD

t

CLIDLY

NOTES

1. PIXEL CLOCK PERIOD IS DIVIDED INTO 48 POSITIONS, PROVIDING FINE EDGE RESOLUTION FOR HIGH SPEED CLOCKS.

2. THERE IS A FIXED DELAY FROM THE CLI INPUT TO THE INTERNAL PIXEL PERIOD POSITION (

P[0] P[48] = P[0]P[12] P[24] P[36]

Figure 17. High Speed Clock Resolution from CLI Master Clock Input

t

CLIDLY

= 6ns TYP).

04637-0-011

Rev. A | Page 15 of 96

AD9925

CCD

SIGNAL

1

RG

56

H1

H2

78

H3

H4

PROGRAMMABLE CLOCK POSITIONS:

1. RG RISING EDGE.

2. RG FALLING EDGE.

3. SHP SAMPLE LOCATION.

4. SHD SAMPLE LOCATION.

5. H1 RISING EDGE POSITION AND 6: H1 FALLING EDGE POSITION (H2 IS INVERSE OF H1).

7. H3 RISING EDGE POSITION AND 8: H3 FALLING EDGE POSITION (H4 I

2

3

4

S INVERSE OF H3).

Figure 18. High Speed Clock Programmable Locations

04637-0-012

Figure 20 sho fault timi ns for all

speed clo

H-Driver and puts

In addition to the pum tions, the AD9925

features on-chip o

puts. These driv

CD inputs. The H-driver and RG current can be adjusted for

C

ptimum rise/fall time with a particular load by using the

o

RVCONTROL register (Addr x35). The 3-bit drive setting for

D

ws the de ng locatio of the high

ck signals.

RG Out

rogra mable timing posi

tpu vers for the RG

t dri

ers are p erful enough to

ow

and H1 to H4 out-

directly drive the

each output is adjustable in 4.1 mA increments, with the minimum setting of 0 equal to OFF or three-state and the

etting of 7 equal to 30.1 mA.

s

As shown in Figure 18, Figure 19, and Figure

inverses of H1 and H3,outputs are respectively. The H1/H

ossover voltage is approximately e output swing. The

cr 50% of th

ssover voltage is not programm

cro able.

maximum

20, the H2 and H4

2

Digital Da

The AD9925 data output and DCLK phase are programmable

using the DOUTPHASE register (Addr

edge from 0 to 47 may be programmed, a

Normally, the DOUT and DCLK signals will track

based on the DOUTPHASE register contents. The DCLK o

put phase can also be held fixed with respect to the data outputs

by changing the DCLKMODE register high (Addr x37, Bit [6]).

In this mode, the DCLK output will remain at a fixed phase

equal to CLO (the inverse of CLI), while the data output phase

is still programmable.

There is a fixed output delay from the DCLK rising edge to the

DOUT transition, called t

four values between 0 ns and 12 ns by using the DOUTDELAY

register (Addr x37, he default value is 8 ns

The pi AD9925 is shown in

After t by SHD, there is an

delay u

ta Outputs

x37, Bits [5:0]). Any

s shown in Figure 21.

in phase,

ut-

. This delay can be programmed to

OD

Bits [8:7]). T .

peline delay through the Figure 22.

he CCD input is sampled 11 cycle

ntil the data is available.

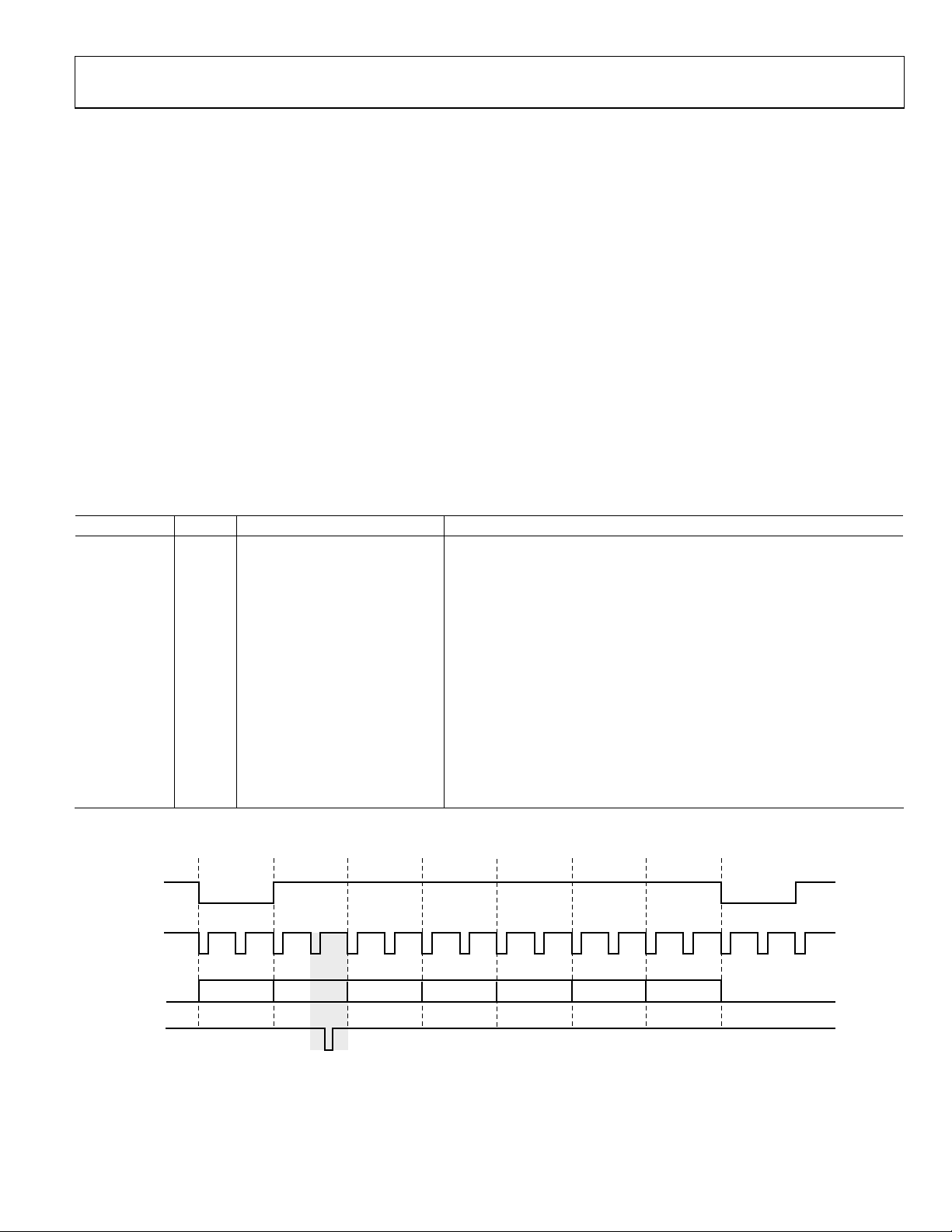

Table 8. Timing Core Register Parameters for H1, H3, RG, SHP/SHD

arameter Length Range Description

P

Polarity 1 b High/Low Polarity Control for H1, H3, and RG (0 = No Inversion, 1 = Inversion)

Positive Edge 6 b 0 to 47 Edge Location Positive Edge Location for H1, H3, and RG

Negative Edge 6 b 0 to 47 Edge Location Negative Edge Location for H1, H3, and RG

Sampling Location 6 b 0 to 47 Edge Location Sampling Location for Internal SHP and SHD Signals

Drive Strength 3 b 0 to 47 Current Steps Drive Current for H1 to H4 and RG Outputs (4.1 mA per Step)

Rev. A | Page 16 of 96

AD9925

CCD

SIGNAL

RG

H1/H3

H2/H4

NOTE

1. USING THE SAME TOGGLE POSITIONS FOR H1 AND H3 GENERATES STANDARD 2-PHASE H-CLOCKING.

04637-0-013

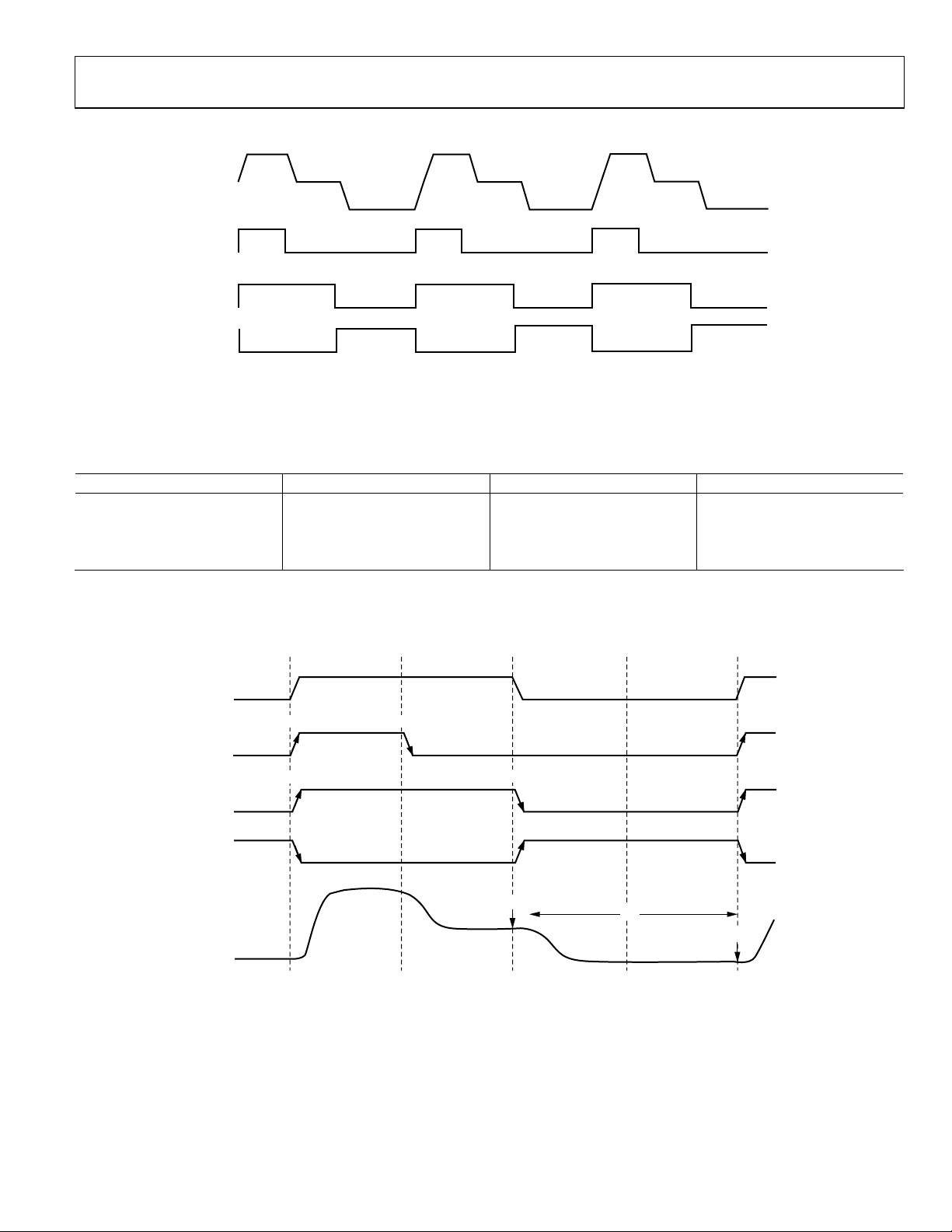

Figure 19. 2-Phase H-Clock Operation

Table 9. Precision Timing Edge Locations

Quadrant Edge Location (Dec) Register Value (Dec) Register Value (Bin)

I 0 to 11 0 to 11 000000 to 001011

II 12 to 23 010000 to 011011 16 to 27

I 24 to 35 32 to 43 100000 to 101011 II

IV 36 to 47 48 to 59 110000 to 111011

POSITION

PIXEL

PERIOD

RG

H1/H3

P[0]

RGr[0] RGf[12]

Hr[0] Hf[24]

P[24]P[12] P[36]

P[48] = P[0]

H2/H4

SHP[24]

CCD

SIGNAL

NOTES

1. ALL SIGNAL EDGES ARE FULLY PROGRAMMABLE TO ANY OF THE 48 POSITIONS WITHIN ONE PIXEL PERIOD.

2. DEFAULT POSITIONS FOR EACH SIGNAL ARE SHOWN.

t

S1

SHD[48]

04637-0-014

Figure 20. High Speed Timing Default Locations

Rev. A | Page 17 of 96

AD9925

.

2

.

3

(

CLI

CCDIN

SHD

(INTERNAL)

P[0]

PIXEL

PERIOD

DCLK

t

OD

DOUT

NOTES

1. DATA OUTPUT (DOUT) AND DCLK PHASE IS ADJUSTABLE WITH RESPECT TO THE PIXEL PERIOD

. WITHIN 1 CLOCK PERIOD, THE DATA TRANSITION CAN BE PROGRAMMED TO 48 DIFFERENT LOCATIONS

. OUTPUT DELAY

t

) FROM DCLK RISING EDGE TO DOUT RISING EDGE IS PROGRAMMABLE.

OD

P[12]

P[24]

P[36]

Figure 21. Digi tal Output Phase Adjustment

t

CLIDLY

N– 1

N N + 1

SAMPLE PIXEL N

N + 2

N + 3

N + 4

P[48] = P[0]

04637-0-015

N + 12N + 11N + 10N + 9N + 8N + 7 6 N + 13N +N + 5

ADC DOUT

(INTERNAL)

DCLK

DOUT

HORIZ CLAM ING AND BLANKING

ONTAL P

The AD9925’s rizon amping and blanking pu are fully

N – 13

N – 12

t

DOUTINH

N – 13

N – 12

NOTES

1. TIMING VALUES SHOWN ARE SHDLOC = 0, WITH DCLKMOD

2. HIGHER VALUES OF SHD AND/OR DOUTPHASE WILL SHI

3. INHIBIT TIME FOR DOUT PHASE IS DEFINED BY t

11 EDGE LOCATIONS FOLLOWING SHDLOC NOT BE USED

4. RECOMMENDED VALUE FOR DOUT PHASE IS TO USE THE

ECOMMENDED VALUE FOR

5. R

6. THE DOUT LATCH CAN BE BYPASSED U

DOUT PINS. THIS CONFIGURATION IS R

t

(DOUT DLY) IS 4ns.

OD

ho tal cl lses

programmable to suit a variety of applications. Individu

trol is provided for CLPOB, PBLK, and HBLK during th

ent regions of each fiel is allows th ping

d. Th e dark pixel clam

and blanking patterns to be changed at each stage of the

out, which accommodates the different image transfer t

N– 8N– 9N – 10N – 11

PIPELINE LATENC

N– 8N– 9N – 10N – 11

, W

DOUTINH

SING REGISTER 0x03, BIT [4] = 1, SO THAT THE ADC DATA OUTPUTS APPEAR DIRECTLY AT THE

ECOMMENDED IF ADJUSTABLE DOUT PHASE IS NOT REQUIRED.

Figure utput Pipeline Delay

22. Digital Data O

al con-

e differ-

read-

iming

and high speed line shifts.

Individual CLPOB and PBLK Patterns

he AFE horizontal timing consists of CLPOB and PBLK, as

T

wn in Figure 23. These two signals are independently pro-

sho

rammed using the registers in Table 10. SPOL is the start po-

g

larity for the signal, and TOG1 and TOG2 are the first and second toggle positions of the pulse. Both signals ar

e active low

and should be programmed accordingly.

N– 6N– 7

Y = 11 CYCLES

NN– 7 N– 3N– 4N– 5– 6 N– 2

E = 0.

FT DOUT TRA

HICH IS EQ

FOR THE DOUTPHASE LOCATION.

SHPLOC EDGE OR THE 11 EDGES FOLLOWING SHPLOC.

NSITION TO THE RIGHT, WITH RESPECT TO CLI LOCATION.

UAL TO SHDLOC PLUS 11 EDGES. IT IS RECOMMENDED THAT THE

N– 3N– 4N– 5 N– 2

N– 1

A separate pattern for CLPOB and PBLK may be programmed

for every 10 vertical sequences. As described in the Vertical

Timing Generation section, up to 10 separa

can be created, each containing a unique pulse pattern for

CLPOB and PBLK. Figure 37 shows how the sequence change

positions divide the readout field into different regions. A different vertical sequence can be assigned to each region, allowing

the CLPOB and PBLK signals to

each change in the vertical timing.

CLPOB Masking Area

Additionally, the AD9925 allows the CLPOB signal to be disabled during certain lines in the field without changing any of

the existing CLPO

B pattern settings. There are two ways to use

CLPOB masking. First, the six CLPOBMASK registers can be used

N + 1NN + 2

N + 1

N– 1

N

N + 2

04637-A-001

te vertical sequences

be changed accordingly with

Rev. A | Page 18 of 96

AD9925

to specify six individual lines within th

contain an e CLPOB ulse. CLP ow for this

mode of oper ion.

Second, th

of adjacent

activ p MASKTYPE is set l

at

e CLPMA

lines e CLPMAS ue

SK re cif

gisters can be used to spe

. Th

grammed to specify the starting and ending lines in the f

the CLPOB patterns will be ignored. There are three sets

and end valu allowi to three CLPOB masking eas to be

created. CLP ASKTYP is set high for this mode of o eration.

The CLPOB asking sters are not specific to a ce ain vertical

sequence; the are alw active for any existing field timing.

To disable th CLPO sking feature, these regist should

es, ng up ar

M E p

m regi rt

y ays of

e B ma ers

be set to the maximum value of 0xFFF (default value).

Table 10. CLPOB and PBLK Pattern Registers

Register Length Range Descr

SPOL 1 b High/Low Starting Polarity of CLPOB/PBLK for Vertical Sequence 0 to 9.

TOG1 12 b 0 to 4095 Pixel Location First Toggle Position within Line for Vertical Sequence 0 to 9.

TOG2 12 b 0 to 4095 Pixel Location Second Toggle Position within Line for Vertical Sequence 0 to 9.

CLPOBMASK 12 b 0 to 4095 Line Location

CLPMASKTYPE 1 b High/Low

e field. These lines will not

K start and end line val

Individual HBLK Patterns

The HBLK programmable timing shown in Figure 24 is similar

olarity control. Only

itionally, there is a polarity

2 = H4 = High

he CLPOB

ach vertical

e used with

y blocks

s are pro-

ield, where

of start

to CLPOB and PBLK, but there is no start p

the toggle positions are used to designate the start and the stop

positions of the blanking period. Add

control HBLKMASK that

clock signals H1 to H4 durin

designates the polarity of the horizontal

g the blanking period. Setting

HBLKMASK high will set H1 = H3 = Low and H

during the blanking, as shown in Figure 25. As with t

and PBLK signals, HBLK registers are available in e

sequence, which allow different blanking signals to b

different vertical timing sequences.

One additional feature is the ability to enable th

e H3/H4 signals

to remain active during HBLK. To do this, set register Bit D6 in

Addr 0xE7 equal to 1. This feature is usef

ul if the H3 output is

used to drive the HL (last horizontal gate) input of the CCD.

iption

CLPOBMASK0 thr e

CLPOB pulse to be ed to specify

three ranges of ad

ough CLPOBMASK5 specify six individual lines in the field for th

temporarily disabled. These registers can also be us

jacent lines, rather than six individual lines.

When set low (default), the CLPOBMASK registers select individual lines in the field

to disable the CLPOB pulse. When set high, the range masking is enabled, allowing

up to three blocks of adjacent lines to have the CLPOB signal masked. CLPOBMASK0 and CLPOBMASK1 are the start/end of the first block of lines, CLPOBMASK2

and CLPOBMASK3 are the start/end of the second block, and CLPOBMASK4 and

CLPOBMASK5 are the start/end of the third block.

HD

CLPOB

1

PBLK

NOTES

PROGRAMMABLE SETTINGS:

1. START POLARITY (CLAMP AND BLANK REGION ARE ACTIVE LOW).

2. FIRST TOGGLE POSITION.

3. SECOND TOGGLE POSITION.

ACTIVE

32

ACTIVE

04637-0-017

Figure 23. Clamp and Preblank Pulse Placement

Rev. A | Page 19 of 96

AD9925

K

Table 11. HBLK Pattern Registers

Register Length Range Description

HBLKMASK 1 b High/Low Masking Polarity for H1/H3 (0 = H1/H3 Low, 1 = H1/H3 High).

H3HBLKOFF 1 b High/Low Addr 0xE7, Bit [6]. Set = 1 to keep H3/H4 active during HBLK pulse. Normal set to 0.

HBLKALT 2 b 0 to 3 Alternation Mode

HBLKTOG1 12 b 0 to 4095 Pixel Location First Toggle Position within Line for Each Vertical Sequence 0 to 9.

HBLKTOG2 12 b 0 to 4095 Pixel Location Second Toggle Position within Line for Each Vertical Sequence 0 to 9.

HBLKTOG3 12 b 0 to 4095 Pixel Location Third Toggle Position within Line for Each Vertical Sequence 0 to 9.

HBLKTOG4 12 b 0 to 4095 Pixel Location Fourth Toggle Posit ch Vertical Sequence 0 to 9. ion within Line for Ea

HBLKTOG5 12 b 0 to 4095 Pixel Location Fifth Toggle Position within Line for Each Vertical Sequence 0 to 9.

HBLKTOG6 12 b 0 to 4095 Pixel Location Sixth Toggle Position within Line for Each Vertical Sequence 0 to 9.

Enables Odd/Even A

0 = Disable Alternat

G1 to TOG2 O

1 = TO

2 = 3 = TO

G1to TOG

lternation of HBLK Toggle Positions.

ion.

dd, TOG3 to TOG6 Even.

2 Even, TOG3 to TOG6 Odd.

Generating S Bpecial H LK Patterns

There are six oggle ions availab for HBLK. Normally,

only two of the toggle positions are use

dard HBLK interval. However, the addi

may be used to generate special HBLK

Figure 26. The pattern in this example

tions to generate two extra groups of pu

interval. By changing the toggle positio atterns can

t posit le

d to generate the stan-

tional toggle positions

patterns, as shown in

uses all six toggle posi-

lses during the HBLK

ns, different p

be created.

HD

12

HBL

PROGRAMMABLE SETTINGS:

1. FIRST TOGGLE POSITION = START OF BLANKING.

2. SECOND TOGGLE POSITION = END OF BLANKING.

HD

BLANK BLANK

Figure 24. Horizontal Blanking (HBLK) Pulse Placement

Generating HBLK Line Alternation

One further feature of the AD9925 is the ability to alternate different HBLK toggle positions on odd and even lines. This may be

used in conjunction with vertical pattern odd/even alternation or

on its own. When a 1 is writte

n to the HBLKALT register, TOG1

and TOG2 are used on odd lines, while TOG3 to TOG6 are

used on even lines. Writing a 2 to the HBLKALT register give

the opposite result: TOG1 and TOG2 are used on even lines,

while TOG3 to TOG6 are

used on odd lines. See the Vertical

Timing Generation section for more information.

04637-0-018

s

HBLK

H1/H3

H1/H3

H2/H4

NOTE

1. THE POLARITY OF H1 DURING BLANKING IS PROGRAMMABLE (H2 IS OPPOSITE POLARITY OF H1).

Figure 25. HBLK Masking Control

Rev. A | Page 20 of 96

04637-0-019

AD9925

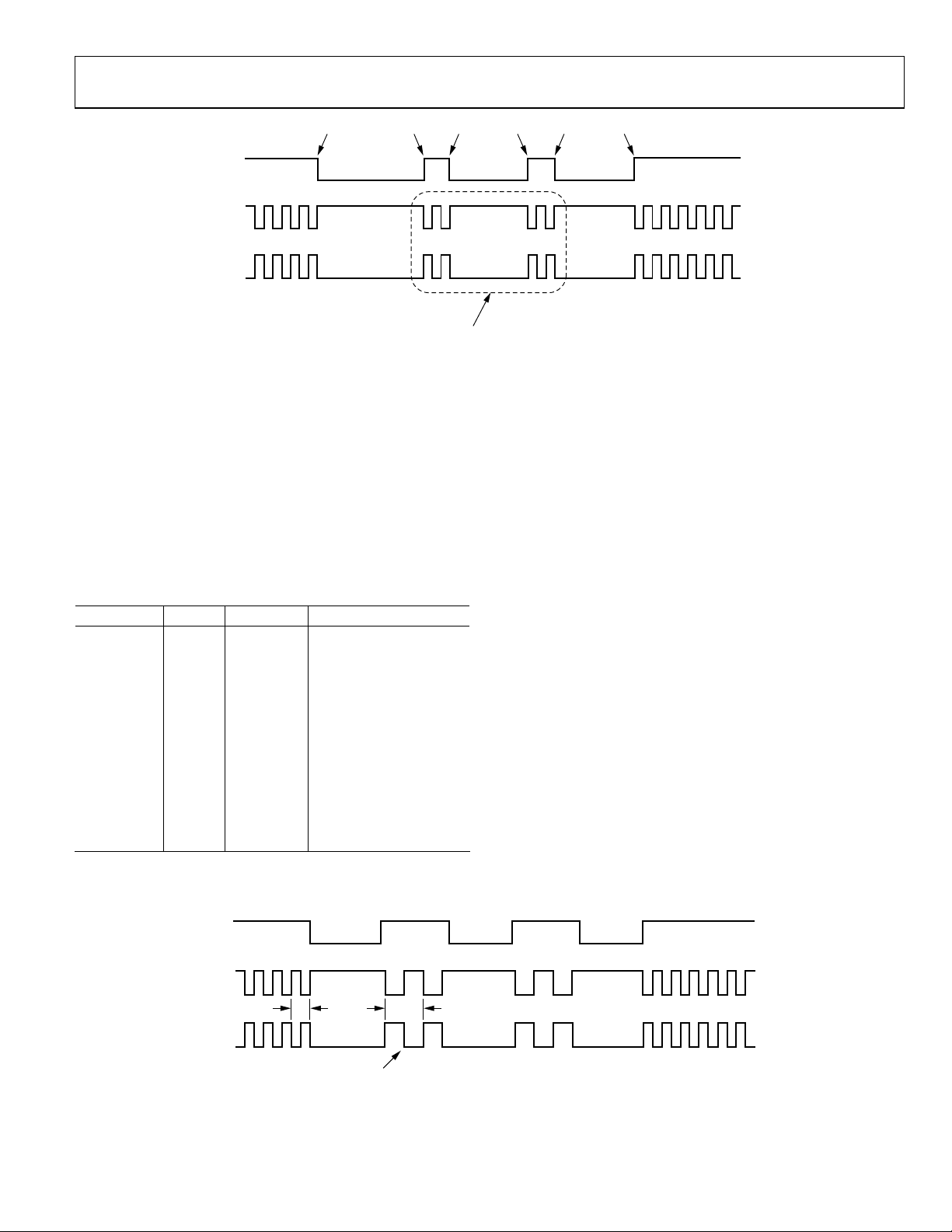

HBLK

H1/H3

H2/H4

TOG1 TOG2 TOG3 TOG4 TOG5 TOG6

SPECIAL H-BLANK PATTERN IS CREATED USING MULTIPLE HBLK TOGGLE POSITIONS

Figure 26. Generating Special HBLK Patterns

Increasing H-Clock Width during HBLK

The AD9925 will also allow the H1 to H4 pulse width to be

increased during the HBLK interval. The H-clock pu

lse width

can increase by reducing the H-clock frequency (see Figure 27).

he HBLKWIDTH register, at Bank 1 Address 0x38, is a 3-bit

T

register that allows the H-clock frequency to be reduced by 1/2,

1/4, 1/6, 1/8, 1/10, 1/12, or 1/14. The reduced frequen

only occur for H1 to H4 pulses that are located within t

BLK area.

H

cy will

he

Table 12. HBLK Width Register

Register Length Range Description

HBLKWIDTH 3 b 1 to 1/14

Controls H1 to H4 widt

h

during HBLK as a fraction of pixel rate

0: same frequency as

pixel rate

1: 1/2 pixel frequency,

i.e., doubles the H1 to H4

pulse width

2: 1/4 pixel frequency

3: 1/6 pixel frequency

4: 1/8 pixel frequency

5: 1/10 pixel frequency

6: 1/12 pixel frequency

7: 1/14 pixel frequency

04637-0-020

HORIZONTAL TIMING SEQUENCE EXAMPLE

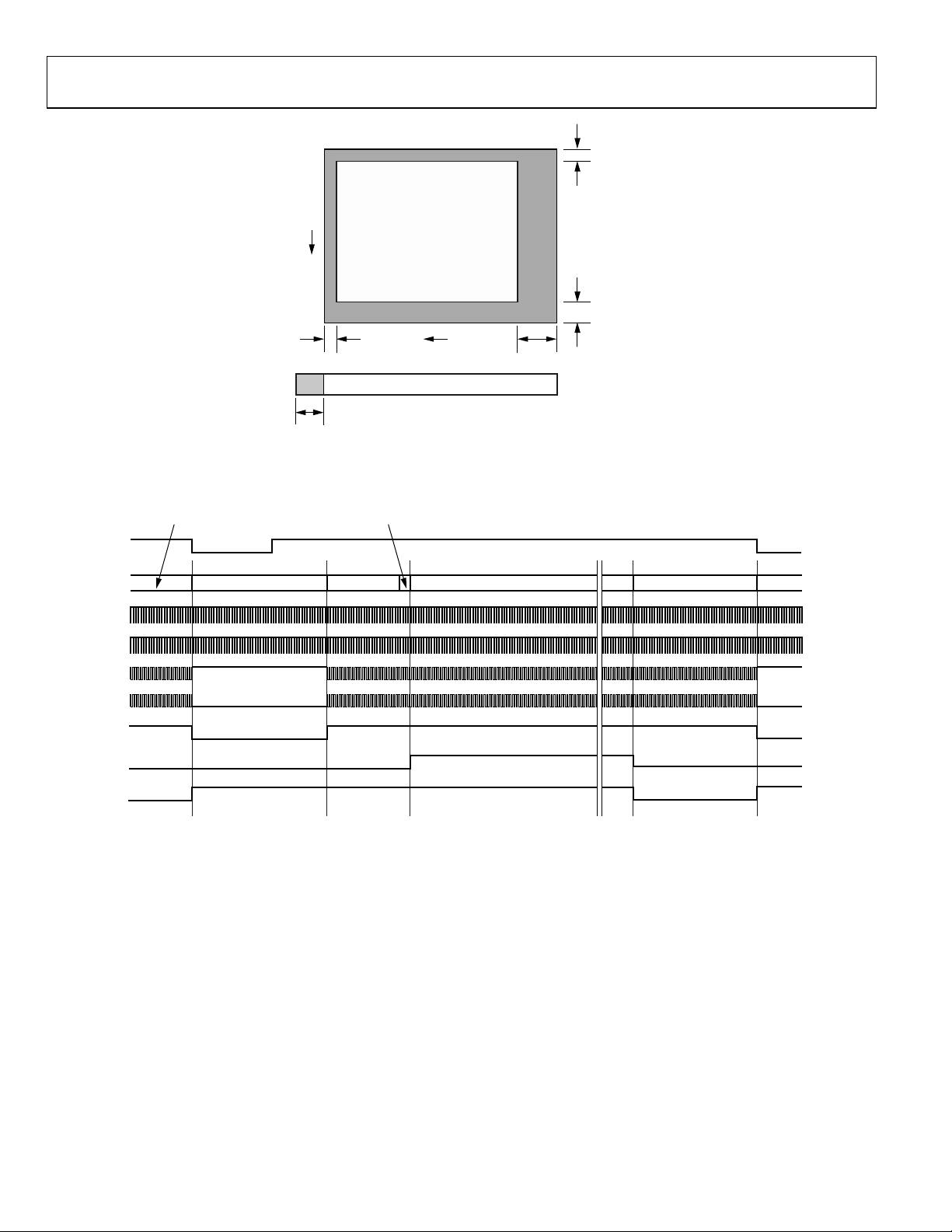

Figure 28 shows an exampl CCD layout. The horizontal register

contains 28 d

ummy pixels, which will occur on each line clocked

from the CCD. In the vertical direction, there are 10 optical black

(OB) lines at the front of the readout and 2 at the back of the

readout. The horizontal direction has 4 OB pixels in the front

and 48 in the

back.

Figure 29 shows the basic sequence layout to be used during the

effective pixel readout. The 48 OB pixels at the end of each

are used for the CLPOB signals. PBLK is optional and is often

used to blank the digital outputs during the noneffective CCD

pixels. HBLK is used during the vertical shift interval. The

HBLK, CLPOB, and PBLK parameters are programmed in the

vertical sequence registers.

More elaborate clamping schemes may be used, such as addin

in a separate sequence to clamp during the entire shield OB

lines. This requires configuring a separate vertical sequence for

reading out the OB lines.

e

line

g

HBLK

H1/H3

H2/H4

1/F

PIX

H-CLOCK FREQUENCY CAN BE REDUCED DURING HBLK BY 1/2 (AS

SHOWN), 1/4, 1/6, 1/8, 1/10, 1/12, OR 1/14 USING HBLKWIDTH REGISTER

Figure 27. Generating Wide H-Clock Pulses during HBLK Interval

2 × (1/F

PIX

)

04637-0-070

Rev. A | Page 21 of 96

AD9925

C

V

4 OB PIXELS

EFFECTIVE IMAGE AREA

H

HORIZONTAL CCD REGISTER

48 OB PIXELS

2 VERTICAL

OB LINES

10 VERTICAL

OB LINES

28 DUMMY PIXELS

Figure 28. Example CCD Configuration

HD

CCDIN

SHP

SHD

H1/H3

H2/H4

HBLK

PBLK

LPOB

OPTICAL BLACK

VERTICAL SHIFT VERT SHIFT

OB

DUMMY EFFECTIVE PIXELS

Figure 29. Horizontal Sequence Example

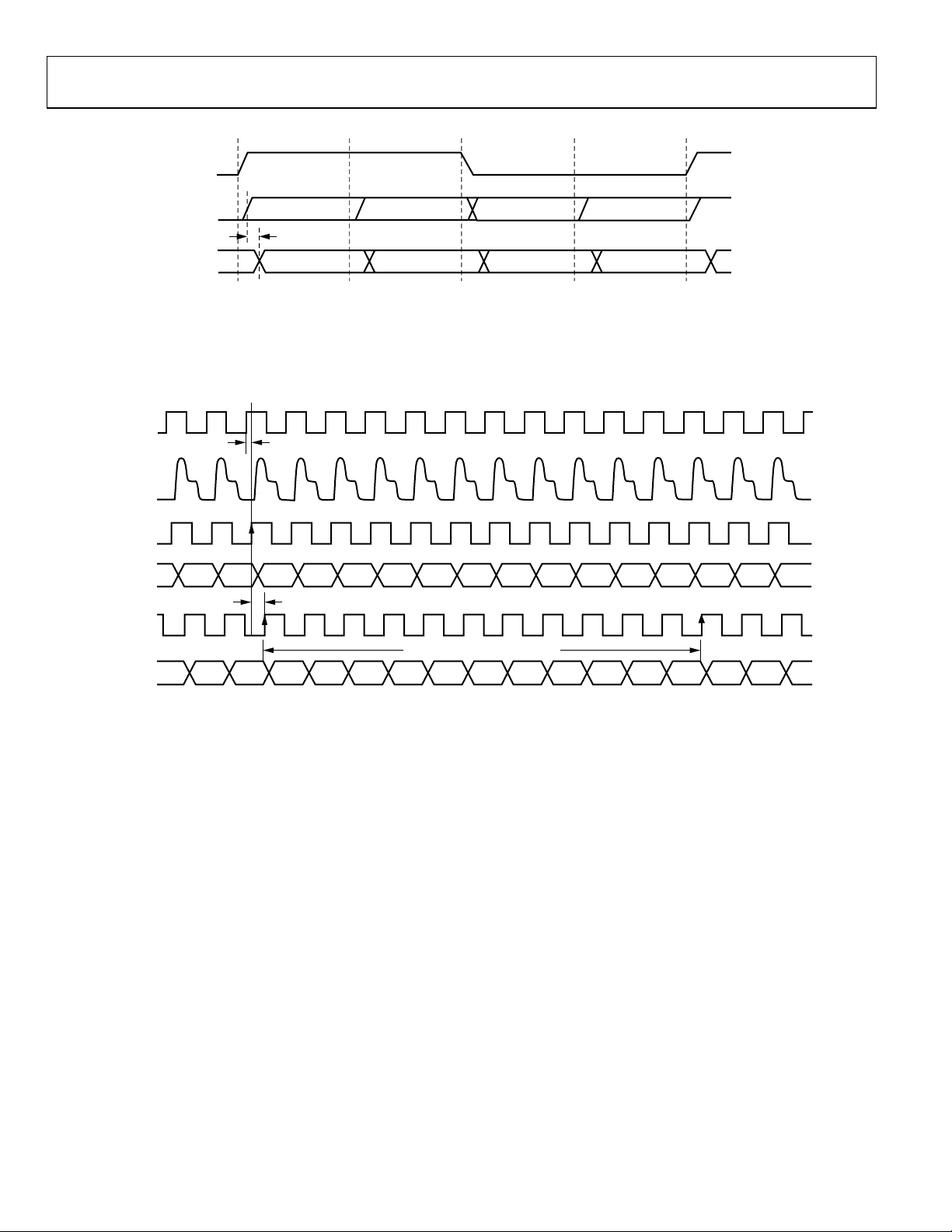

VERTICAL TIMING GENERATION

The AD9925 provides a very flexible solution for generating

vertical CCD timing and can support multiple CCDs and different system architectures. The vertical transfer clocks XV1 to

XV8 are used to shift each line of pixels into the

ut register of the CCD. The AD9925 allows these outputs to be

p

individually programmed into various readout configurations,

sing a 4-step process.

u

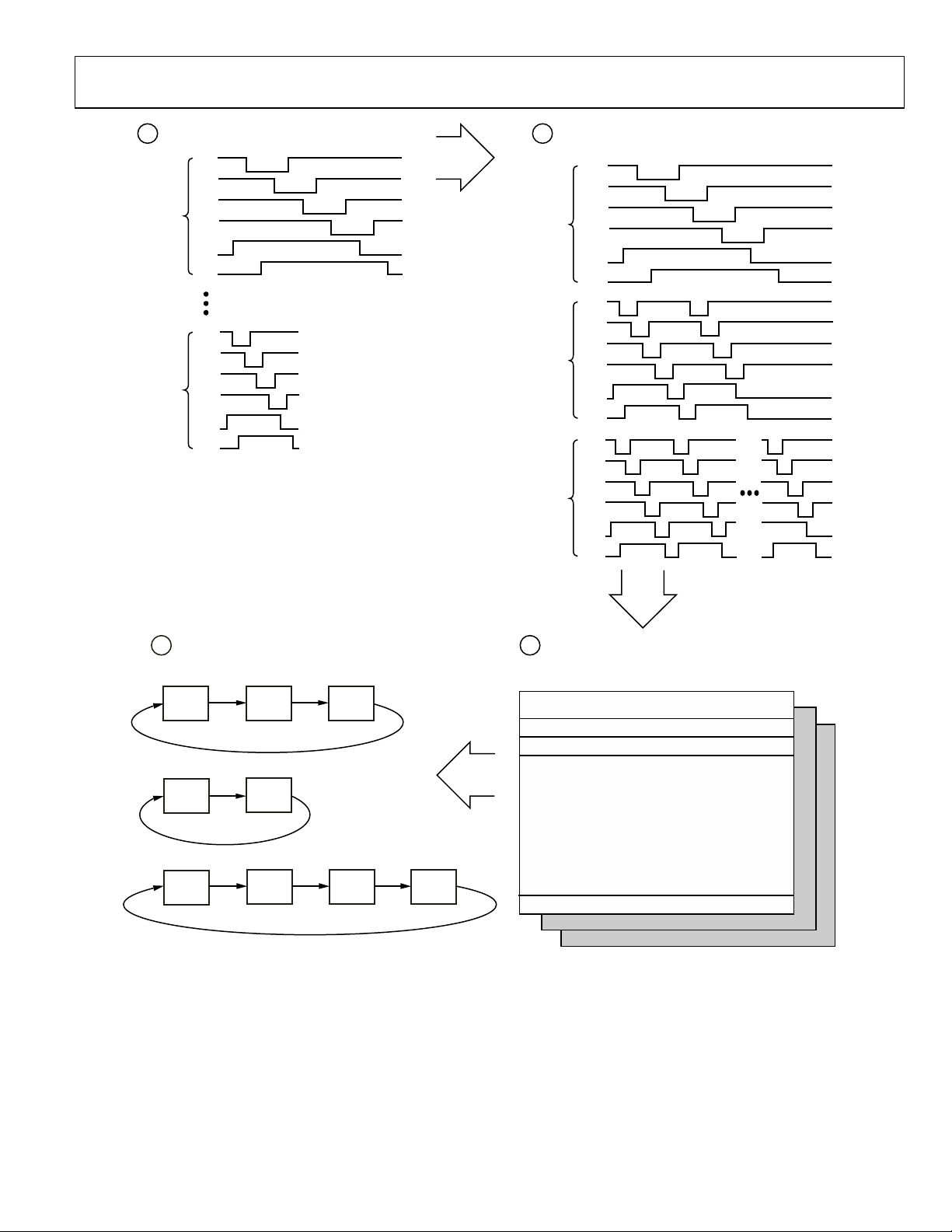

Figure 30 shows an overview of how the vertical timing is generated in four steps. First, the individual pulse patterns for XV1

to XV8 are created by using the vertical pattern group registers.

horizontal out-

04637-0-021

OPTICAL BLACK

05637-0-022

Second, the vertical pattern groups are used to build the

sequences, where additional information is added. Third, the

readout for an entire field is constructed by dividing the field

into different regions and then assigning a sequence to ea

region. Each field

can contain up to seven different regions to

ch

accommodate the different steps of the readout, such as high

speed line shifts and unique vertical line transfers. Up to six

different fields may be created. Finally, the MODE register allows the different fields to be combined into any order for various readout configurations.

Rev. A | Page 22 of 96

AD9925

CREATE THE VERTICAL PAT

1 2

(MAXIMUM OF 10 GROUPS)

XV1

XV2

VPAT 0

VPAT 9

XV3

XV4

XV5

XV6

XV1

XV2

XV3

XV4

XV5

XV6

TERN GROUPS

ERTICAL SE

V QUENCE 0

(VPAT0, 1 REP)

VERTICAL SEQUENCE 1

(VPAT9, 2 REP)

VERTICAL SEQUENCE 2

(VPAT9, N REP)

BUILD THE VERTICAL SEQUENCES BY ADDING LINE START

POSITION, # OF REPEATS, AND HBLK/CLPOB PULSES

(MAXIMUM OF 10 VERTICAL SEQUENCES)

XV1

XV2

XV3

XV4

XV5

XV6

XV1

XV2

XV3

XV4

XV5

XV6

XV1

XV2

XV3

XV4

XV5

XV6

USE THE MODE REGISTER TO CONTROL WHICH FIELDS

ARE USED, AND IN WHAT ORDER

(MAXIMUM OF 7 FIELDS MAY BE COMBINED IN ANY ORDER)

FIELD 0

FIELD 3

FIELD 5

FIELD 1 FIELD 2

FIELD 4

FIELD 1 FIELD 4

FIELD 2

BUILD EACH FIELD BY DIVIDING INTO DIFFERENT REGIONS

33

AND ASSIGNING A DIFFERENT VERTICAL SEQUENCE TO EACH

(MAXIMUM OF 7 REGIONS IN EACH FIELD)

(MAXIMUM OF 6 FIELDS)

FIELD 0

REGION 0: USE VERTICAL SEQUENCE 2

REGION 1: USE VERTICAL SEQUENCE 0

REGION 2: USE VERTICAL SEQUENCE 3

REGION 3: USE VERTICAL SEQUENCE 0

REGION 4: USE VERTICAL SEQUENCE 2

FIELD 1

REGION 0: USE V-SEQUENCE 3

REGION 0: USE V-SEQUENCE 3

REGION 1: USE V-SEQUENCE 2

REGION 1: USE V-SEQUENCE 2

REGION 2: USE V-SEQUENCE 1

REGION 2: USE V-SEQUENCE 1

FIELD 2

04637-0-023

Figure 30. Summary of Vertical Timing Generation

Rev. A | Page 23 of 96

AD9925

X

:

2

.

4

X

X

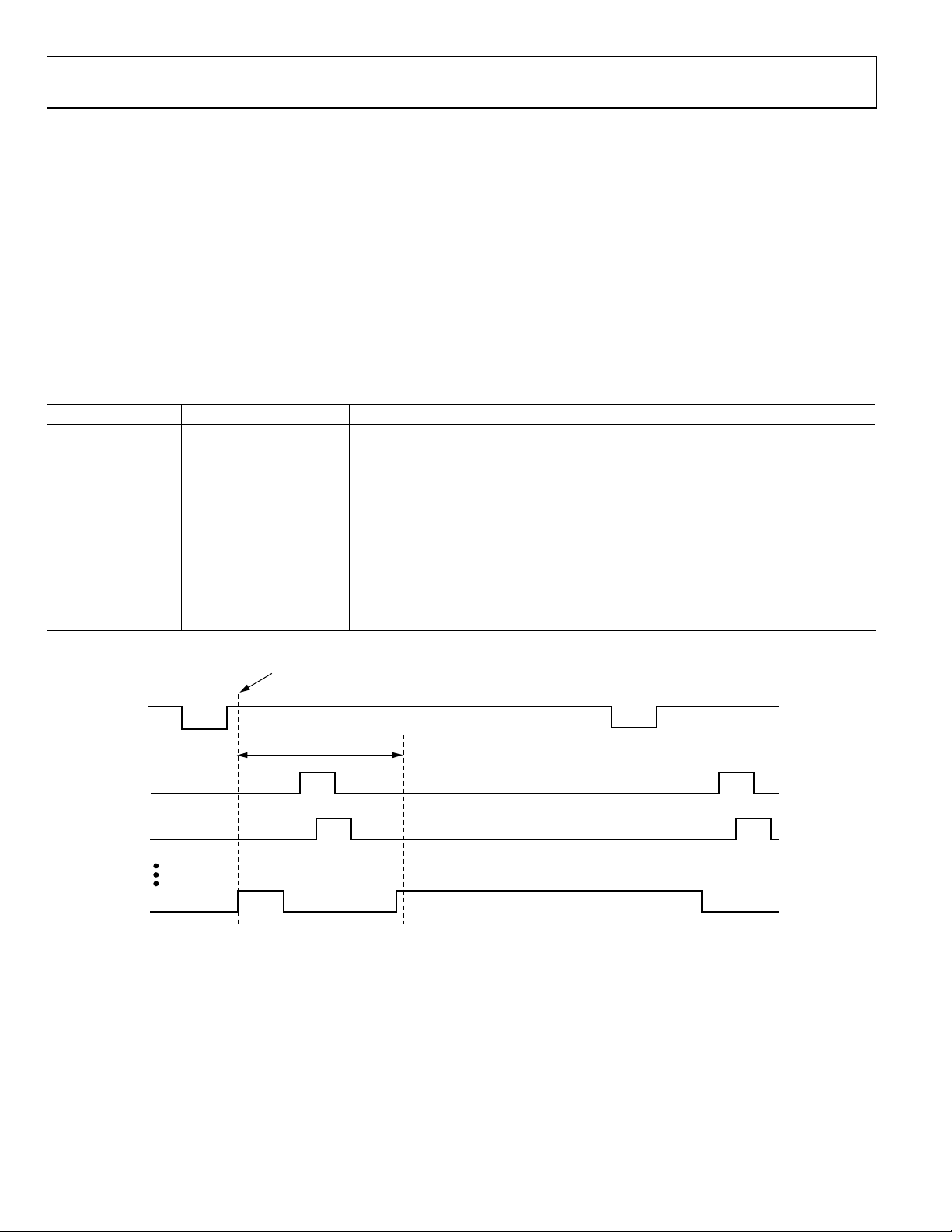

Vertical Pattern Groups (VPAT)

The vertical pattern groups define the individual pulse patterns

for each XV1 to XV6 output signal. Table 13 summarizes the

registers available for generating each of the 10 vertical pattern

groups. The start polarity (VPOL) determines the starting

polarity of the vertical sequence and can be programmed high

or low for each XV1 to XV6 output. The first, second, and third

toggle positions (XVTOG1, XVTOG2, and XVTOG3) are the

ixel locations within the line where the pulse transitions. A

p

ourth toggle position (XVTOG4) is also available for vertical

f

pattern groups 8 and 9. All toggle positions are 12-bit values,

allowing their placement anywhere in the horizontal line. A

Table 13. Vertical Pattern Group Registers

Register Length Range Description

XVPOL 1 b High/Low Starting Polarity of Each XV Output

XVTOG1 12 b 0 to 4096 Pixel Location First To for Each XV Output ggle Position within Line

XVTOG2 12 b 0 to 4096 Pixel Location Second To Line for Each XV Output ggle Position within

XVTOG3 12 b 0 to 4096 Pixel Location Third Toggle Position within Line for Each XV Output

XVTOG4 12 b 0 to 4096 Pixel Location

Fourth Toggle Po rtical Pattern Groups 8 and 9 and Also in

XV7 and XV8 Vertical Pattern Groups

VPATLEN 12 b 0 to 4096 Pixels

Total Length of Each Vertical Pattern Group

FREEZE1 12 b 0 to 4096 Pixel Location Holds the XV Outputs at Their Current Levels (Static DC)

RESUME1 12 b 0 to 4096 Pixel Location Resumes Operation of the XV Outputs to Finish Their Pattern

FREEZE2 12 b 0 to 4096 Pixel Location Holds the XV Outputs at Their Current Levels (Static DC)

RESUME2 12 b 0 to 4096 Pixel Location Resumes Operation of the XV Outputs to Finish Their Pattern

START POSITION OF VERTICAL PATTERN GROUP IS PROGRAMMABLE IN VERTICAL SEQUENCE REGISTERS

separate register, VPATSTART, specifies the start position of

vertical pattern groups within the line (see the Vertical Sequen

(VSEQ) section). The VPATLEN register designates the total

length of the vertical pattern group, which determines the number

of pixels between each of the pattern repetitions when repetitions

are used (see the Vertical Sequences (VSEQ) section).

Additional VPAT groups are provided in Register Bank 3 for t

XV7 and XV8 outputs. This a

llows the AD9925 to remain backward-compatible with the AD9995 register settings while still

providing additional flexibility with XV7 and XV8 for new CCDs.

sition, Only Available in Ve

the

ces

he

HD

4

V1

V2

V6

PROGRAMMABLE SETTINGS FOR EACH VERTICAL PATTERN

1. START POLARITY.

. FIRST TOGGLE POSITION.

3. SECOND TOGGLE POSITION (THIRD TOGGLE POSITION ALSO AVAILABLE,

FOURTH TOGGLE POSITION AVAILABLE FOR VERTICAL PATTERN GROUPS 8 AND 9)

. TOTAL PATTERN LENGTH FOR ALL XV OUTPUTS.

1

23

1

2

3

1

23

Figure 31. Vertical Pattern Group Programmability

04637-0-024

Rev. A | Page 24 of 96

AD9925

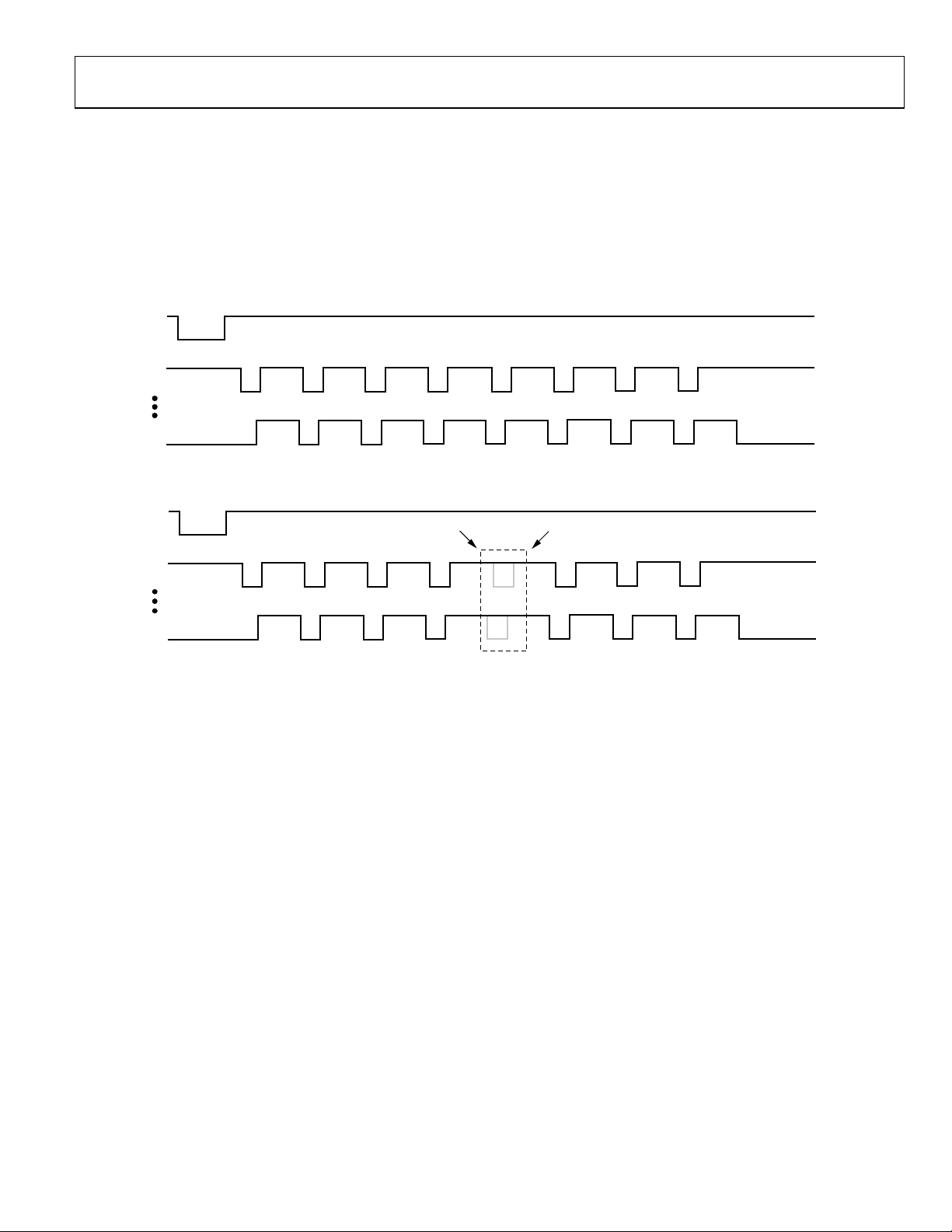

Masking Using FREEZE/RESUME Registers

As shown in Figure 33, the FREEZE/RESUME registers are us

ed

to temporarily mask the XV outputs. The pixel locations to

begin the masking (FREEZE) and end the masking (RESUME)

create an area in which the vertical toggle positions are ignored

At the pixel location specified in the FREEZE register, the XV

outputs will be held static at their current dc state, high or low

.

The XV outputs are held until the pixel location specified by the

.

RESUME register is reached, at which point the signals will

ontinue with any remaining toggle positions. Two sets of

c

FREEZE/RESUME registers are provided, allowing the vertical

utputs to be interrupted twice in the same line. The FREEZE

o

nd RESUME positions are programmed in the vertical pattern

a

roup registers, but are enabled separately using the VMASK

g

gisters. The VMASK registers are described in the Vertical

re

Sequences (VSEQ) section.

HD

XV1

XV8

NO MASKING AREA

Figure 32. No Vertical Masking

04637-0-025

HD

XV1

XV8

NOTES

1. ALL TOGGLE POSITIONS WITHIN THE FREEZE/RESUME MASKING AREA ARE IGNORED. H-COUNTER CONTINUES TO COUNT DURING MASKING.

2. TWO SEPARATE MASKING AREAS ARE AVAILABLE FOR EACH VPAT GROUP, USING FREEZE1/RESUME1 AND FREEZE2/RESUME2 REGISTERS.

Figure 33. Vertical Masking Using the FREEZE/RESUME Registers

FREEZE

MASKING AREA

FOR XV1 TO XV8

RESUME

04637-0-026

Rev. A | Page 25 of 96

AD9925

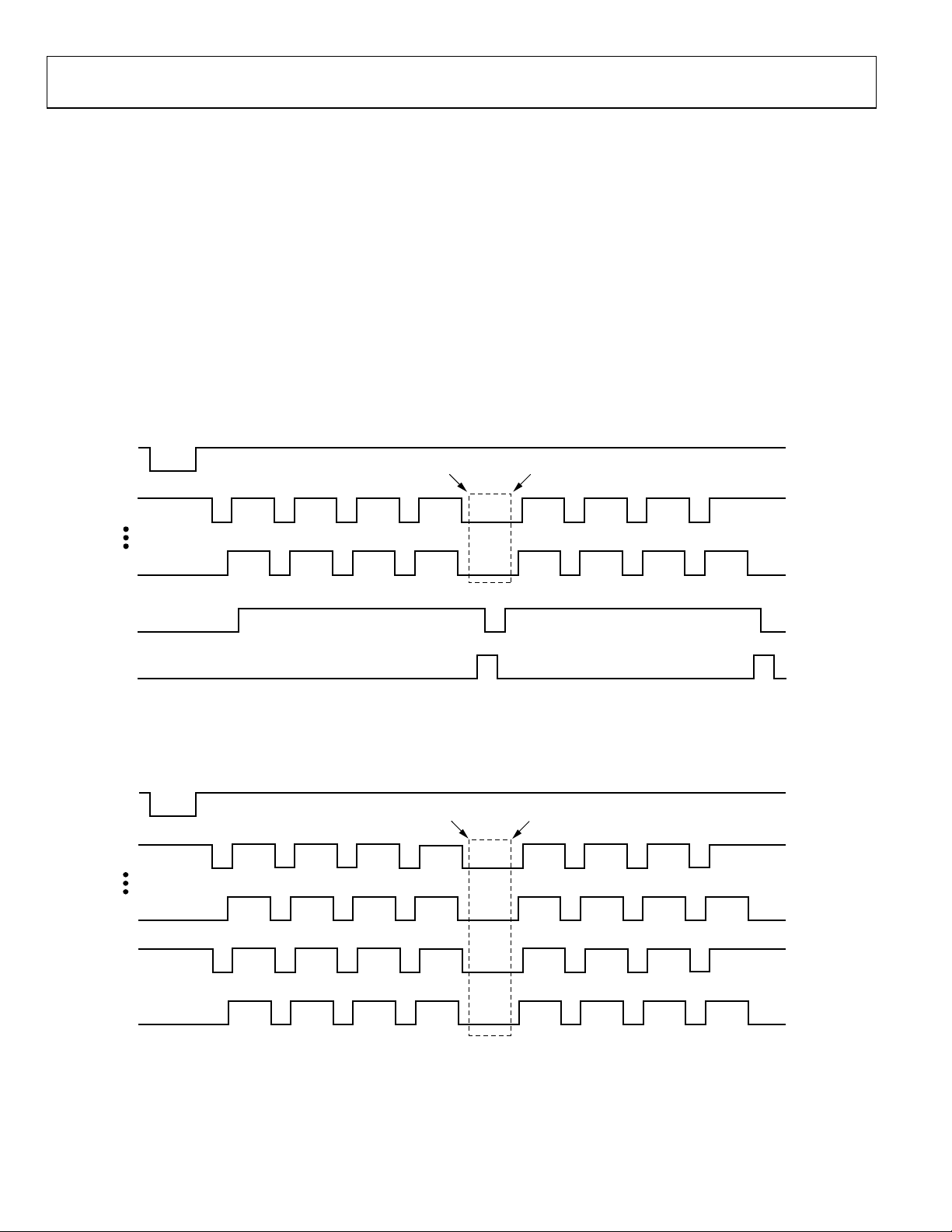

Hold Area Using FREEZE/RESUME Registers

The FREEZE/RESUME registers can also be used to create a

hold area, in which the XV outputs are temporarily held and

then later continued starting at the point where they were held

As shown in Figure 34 and Figure 35, this is different than the

VMASK, because the XV outputs continue from where they

stopped rather than continuing from where they would have

been. The ho

XV outputs, while the v-masking allows the counter to continue

uring the masking area.

d

XV7 and XV8 may or may not use the hold area, as shown in

Figure 34 a ure 35. The hold op

Bank 3 ver quen gisters, described in the Vertical

Sequence ) sec

ld area temporarily stops the pixel counter for the

nd Fig eration is controlled in the

tical se ce re

s (VSEQ tion.

.

HD

FREEZE

XV1

XV6

XV7

XV8

NOTES

1. WHEN HOLD = 1 FOR ANY V-SEQUENCE, THE FREEZE AND RESUME REGISTERS ARE USED TO SPECIFY THE HOLD AREA BOUNDRIES.

2. WHEN XV78HOLDEN = 0, XV7 AND XV8 DO NOT USE THE HOLD AR V6. H-COUNTER FOR XV1–XV6 WILL STOP DURING HOLD AREA.

HOLD AREA

FOR XV1–XV6

EA, ONLY XV1–X

RESUME

NO HOLD

AREA FOR

XV7–XV8

04637-0-072

Figure 34. Vertical Hold Area Using the FREEZE/RESUME Registers

HD

FREEZE

XV1

HOLD AREA

FOR XV1 TO XV8

RESUME

XV6

XV7

XV8

NOTES

1. WHEN HOLD = 1 FOR ANY VERTICAL SEQUENCE, THE FREEZE AND RESUME REGISTERS ARE USED TO SPECIFY THE HOLD AREA BOUNDRIES.

2. WHEN XV78HOLDEN = 1, XV7 AND XV8 ALSO USE THE HOLD AREA. H-COUNTER FOR XV1 TO XV8 WILL STOP DURING HOLD AREA.

04637-0-028

Figure 35. Apply Hold Area to XV7 and XV8

Rev. A | Page 26 of 96

AD9925

Vertical Sequences (VSEQ)

The vertical sequences are created by selecting one of the 10 ver-

cal pattern groups and adding repeats, the start position, and

ti

horizontal clamping and blanking information. Up to 10 vertical sequences may be programmed, each using the registers

shown in Table 14. Figure 36 shows how the different registers

are used to generate each vertical sequence.

The VPATSEL register selects which vertical pattern group will

be used in a given vertical sequence. The basic vertical pattern

group can have repetitions added for high speed line shifts or

line binning by using the VPATREPO and VPATREPE registers.

Generally, the same number of repetitions is programmed into

both registers, but if a different number of repetitions is required on odd and even lines, separate values may be used for

each register (see the Generating Line Alternation for Vertical

Sequence and HBLK section). The VPATSTART register specifies the pixel location where the vertical pattern group will start.

The VMASK register is used in conjunction with the FREEZE/

RESUME registers to enable optional masking of the vertical

outputs. Either or both of the FREEZE1/RESUME1 and

FREEZE2/RESUME2 registers can be enabled using the

The line length

registers. Each vertical sequence can have a different line length

to accommodate the various image readout techniques. The

maximum number of pixels per line is 8192. Note that the 13

(MSB) of the line length is located in a separate register. Also

note that the last line of the field is separately programmable

using the HDLAST register, located in the field register section.

Additional vertical sequences are provided in Register Bank 3

for the XV7 and XV8 outputs. This allows the AD9925 to remain backward-compatible with the AD9995 register settings

while still providing additional flexibility with XV7 and XV8 for

new CCDs.

As described in the Hold Area Using FREEZE/RESUME Registers section, the hold registers in Bank 3 are used to specify a

hold area instead of vertical masking. The FREEZE/RESUME

registers are used to define the hold area. The XV78HOLDEN

registers are used to specify whether XV7 and XV8 will use the

hold area or not.

VMASK register.

Table 14. Vertical Sequence Registers (See Table 10 and Table 11 for the HBLK, CLPOB, and PBLK registers)

Register Length Range Description

VPATSEL 4 b 0 to 9 Vertical Pattern Group No. Selected Vertical Pattern Group for Each Vertical Sequence.

VMASK 2 b 0 to 3 Mask Mode

VPATREPO 12 b 0 to 4095 Number of Repeats

VPATREPE 12 b 0 to 4095 Number of Repeats

VPATSTART 12 b 0 to 4095 Pixel Location Start Position for the Selected Vertical Pattern Group.

HDLEN 13 b 0 to 8191 Number of Pixels

1

HOLD

1 b High/Low

Enables the Masking of V1 to V6 Outputs at the Locations Specified by the

FREEZE/RESUME Registers.

0 = No Mask.

1 = Enable Freeze1/Resume1.

2 = Enable Freeze2/Resume2.

3 = Enable Both 1 and 2.

Number of Repetitions for the Vertical Pattern Group for Odd Lines. If no

odd/even alternation is required, set equal to VPATREPE.

Number of Repetitions for the Vertical Pattern Group for Even Lines. If no

odd/even alternation is required, set equal to VPATREPO.

HD Line Length for Lines in Each Vertical Sequence. Note that 13

of the line length is located in a separate register to maintain compatibility

with AD9995.

Enable Hold Area Instead of Vertical Masking, Using FREEZE/RESUME

Registers.

XV78HOLDEN1 1 b High/Low

Enable XV7 and XV8 to Use Hold Area.

0 = Disable.

1 = Enable.

1

Located in Bank 3, vertical sequence registers for XV7 and XV8.

(in pixels) is programmable using the HDLEN

th

bit

th

bit (MSB)

Rev. A | Page 27 of 96

AD9925

1

HD

2

XV1 TO XV6

CLPOB

PBLK

HBLK

3

VERTICAL PATTERN GROUP

6

PROGRAMMABLE SETTINGS FOR EACH VERTICAL SEQUENCE:

1. START POSITION IN THE LINE OF SELECTED VERTICAL PATTE

2. HD LINE LENGTH.

3. VERTICAL PATTERN SELECT (VPATSEL) TO SELEC

4. NUMBER OF REPETITIONS OF THE VERTICAL PATT

5. START POLARITY AND TOGGLE POSITIONS FO

6. MASKING POLARITY AND TOGGLE POSITIONS FOR

4

AT REP 2

VP

5

T ANY VERT

ERN GROU

R CLPOB AND P

HBLK SIGN

RN GROUP.

P (IF NEEDED).

4

VPAT REP 3

ICAL PATTERN GROUP.

BLK SIGNALS.

AL.

04637-0-029

Programmability Figure 36. Vertical Sequence

Rev. A | Page 28 of 96

AD9925

X

Complete Field: Combining Vertical Sequences

After the vertical sequences have been created, they are combined

to create different readout fields. A field consists of up to seven

different regions, and within each region, a different vertic

al

sequence can be selected. Figure 37 shows how the sequence

change positions (SCP) designate the line boundary for each

region, and how the VSEQSEL registers select which vertical

sequence is used during each region. Registers to control the

XSG outputs are also included in the field registers.

Table 15 summarizes the registers used to create the different

fields. Up to six different fields can be preprogrammed using

the field registers.

The VEQSEL registers, one for each region, select which of the

10 vertical sequences will be active during each region. The

SWEEP registers are used to enable the sweep mode during any

region. The MULTI registers are used to enable the multiplier

mode during any region. The SCP registers create the line

Table 15. Field Registers

Register Length Range Description

VSEQSEL 4 b 0 to 9 V Sequence Number Selected Vertical Sequence for Each Region in the Field.

SWEEP 1 b High/L n Set High. ow Enables Sweep Mode for Each Region, Whe

MULTI 1 b High/Low Enabl ultiplier Mode for Each Region, When Set High. es M

SCP 12 b 0 to 4095 Line Number Sequence Change Position for Each Region.

VDLEN 12 b 0 to 4095 Number of Lines Total Number of Lines in Each Field.

HDLAST 13 b 0 to 8191 Num

ber of Pixels

Length in Pixels of the Last HD Line in

in a separate register to maintain compatibility with the AD9995.

VPATSECOND 4 b

0 to 9 Vertical Pattern Group

Selected Vertical Pattern Group for Second Pattern Applied During SG Line.

Number

SGMASK 6 b High/Low, Each XSG

Set High to Mask Each Individual XSG Output.

XSG1 [0], XSG2 [1], XSG3 [2], XSG4 [3], XSG5 [4], XSG6 [5].

SGPATSEL 12 b 0 to 3 Pattern Number, Each XSG

Selects the SG Pattern Number for Each XSG Output.

XSG1 [1:0], XSG2 [3:2], XSG3 [5:4], XSG4 [7:6], XSG5 [9:8], XSG6 [11:10].

SGLINE1 12 b 0 to 4095 Line Number Selects the Line in the Field Where the SG Signals Are Active.

SGLINE2 12 b 0 to 4095 Line Number Selects a Second Line in the Field to Repeat the SG Signals.

SCP 1

SCP 2

SCP 3

boundaries for each region. The VDLEN register specifies the

total number of lines in the field. The total number of pixels per

line (HDLEN)

he HDLAST register specifies the number of pixels in the last

t

ne of the field. Note that the 13

li

is specified in the vertical sequence registers, but

th

bit (MSB) of the last line

length is located in a separate register. During the sensor gate

(SG) line, the VPATSECOND register is used to add a second

vertical pattern group to the XV outputs.

The SGMASK register is used to enable or disable each individual

VSG output. There is a single bit for each XSG output, setting

the bit high will mask the output and setting it low will enable

the output. The SGPAT register assigns one of the four different

SG patterns to each VSG output. The individual SG patterns are

created separately using the SG pattern registers. The SGLINE1

register specifies which line in the field will contain the XSG

outputs. The optional SGLINE2 register allows the same SG pulses

to be repeated on a different line.

th

bit (MSB) is located

SCP 4

SCP 5

Each Field. The13

SCP 6

VD

REGION 0

HD

V1 TO XV6

XSG

VSEQSEL0

FIELD SETTINGS:

1. SEQUENCE CHANGE POSITIONS (SCP1 TO SCP6) DEFINE EACH OF THE SEVEN REGIONS IN THE FIELD.

2. VSEQSEL0 TO VSEQSEL6 SELECTS THE DESIRED VERTICAL SEQUENCE

3. SGLINE1 REGISTER SELECTS WHICH HD LINE IN THE FIELD WILL CONTAIN THE SENSOR GATE PULSE(S).

REGION 1

VSEQSEL1

SGLINE

REGION 2

VSEQSEL2

Figure 37. Compl ete Field I s Divided into Regions

REGION 3

VSEQSEL3

Rev. A | Page 29 of 96

REGION 4

VSEQSEL4

(0–9) FOR EACH REGION.

REGION 5

VSEQSEL5 VSEQSEL6

REGION 6

04637-0-030

AD9925

Generating Line Alternat

HBLK

During low resolution readout, some CCDs require a different

number of vertical clocks on alternate lines. The AD9925 can

support this by using the VPATREPO and VPATREPE registers

This allows a different number of VPAT repetitions to be programmed on odd and even lines. Note that only the number of

repeats can be different in odd and even lines, but the VPAT

group remains the same.

Additionally, the HBLK signal can also be alternated for odd

and even lines. When the HBLKALT register is set high, the

HBLK TOG1 and HBLK TOG2 positions will be used on odd

lines, and the HBLK TOG3 to HBLK TOG6 positions will be

used on even lines. This allows the HBLK interval to be adjusted

on odd and even lines if needed.

Figure 38 shows an example of a VPAT repetition alternation

and a HBLK alter

nation used together. It is also possible to use

the VPAT and HBLK alternation separately.

HD

XV1

ion for Vertical Sequence and

VPATREPO = 2

VPATREPE = 5

Second Vertical P

Most CCDs require additional vertical timing during the senso

attern Group during VSG Active Line

r

gate (SG) line. The AD9925 supports the option to output a

second vertical pattern group for XV1 to XV8 during the line

.

when the sensor gates XSG1 to XSG6 are active. Figure 39 shows

a typical SG line that includes two separate sets of vertical pattern

group for XV1 to XV6. The vertical pattern group at the start of

the SG line is selected in the same manner as the other regions,

using the appropriate VSEQSEL register. The second vertical

pattern group, unique to the SG line, is selected using the

VPATSECOND register, located with the field registers. The

start position of the second VPAT group uses the VPATLEN

register from the selected VPAT registers. Because the VPATLE

register is used as the start position and not as the VPAT lengt

it is not possible to program multiple repet

itions for the second

N

h,

VPAT group.

VPATREPO = 2

XV2

XV6

TOG1 TOG2

HBLK

NOTES

1. THE NUMBER OF REPEATS FOR THE VERTICAL PATTERN GROUP MAY B

2. THE HBLK TOGGLE POSITIONS MAY BE ALTERNATED BETWEEN ODD AN

GENERATE DIFFERENT HBLK PATTERNS FOR ODD/EVEN LINES.

Figure 38. Odd/Even Line Alteration of VPAT Repetitions and HBLK Toggle Positions

HD

XSG

XV1

XV2

TOG3

START POSITION F

USES VPATLEN RE

E ALTERN

ATED ON ODD AND EVEN LINES.

D EVEN LI

NES, IN ORDER TO

OR SECOND VPAT GROUP

GISTER

TOG4

TOG1 TOG2

04637-0-031

XV6

SECOND VPAT GROUP

Figure 39. Example of Second VPAT Group during Sensor Gate Line

Rev. A | Page 30 of 96

04637-0-032

AD9925

×

Sweep Mode Operation

The AD9925 contains an additional mode of vertical timing

operation called sweep mode. This mode is used to generate a

large number of repetitive pulses that span across multiple HD

lines. One example of where this mode is needed is at the start

of the CCD readout operation. At the end of the image exposure,

but before the image is transferred by the sensor gate pulses, the

vertical interline CCD registers should be free of all charge. This

can be accomplished by quickly shifting out any charge using a

long series of pulses from the XV outputs. Depending on the

vertical resolution of the CCD, up to two or three thousand clock

cycles will be needed to shift the charge out of each vertical CCD

line. This operation will span across multiple HD line lengths.

Normally, the AD9925 vertical timing must be contained within

one HD line length, but when sweep mode is enabled, the HD

boundaries will be ignored until the region is finished. To enable

sweep mode within any region, program

gister to high.

re

Figure 40 shows an example of the sweep mode

number of vertical pulses needed depends on the vertical resolution of the CCD. The XV output signals are generated using

the vertical pattern registers (shown in Table 15). A single pulse

is created using the polarity and toggle position registers. The

number of repetitions is then programmed to match the number of vertical shifts required by the CCD. Repetitions are programmed in th

registers. This produces a pulse train of the appropriate length.

Normally, the pulse train is truncated at the end of the HD line

length, but with sweep mode enabled for this region, the HD

boundaries are ignored. In Figure 40, the sweep region occupies

23 HD lines. After the sweep mode region is completed in the

next region, normal sequence operation will resume. When usi

sweep mode, be sure to set the region boundaries to the appropriate lines (using the sequence change positions) to pre

eep operation from overlapping the next vertical sequence.

sw

e vertical sequence registers using the VPATREP

the appropriate SWEEP

operation. The

ng

vent the

Multiplier Mode

To generate very wide vertical timing pulses, a vertical region

may be configured into a multiplier region. This mode uses the

vertical pattern registers in a slightly different manner. Multiplier

mode can be used to support unusual CCD timing requirements,

such as vertical pulses that are wider than a single HD line length.

The start polarity and toggle positions are still used in the same

manner as the standard VPAT group programming, but the

VPATLEN is used differently. Instead of using the pixel counter

(HD counter) to specify the toggle position locations (VTOG1,

2, 3) of the VPAT group, the VPATLEN is multiplied with the

VTOG position to allow very long pulses to be generated. To

calculate the exact toggle position, counted in pixels after the

start position, use the following equation:

=

Because the VTOG register is multiplied by VPATLEN, the

resolution of the toggle position placement is reduced. If

VPATLEN = 4, then the toggle position accuracy will be reduc

to a 4-pixel step size, instead of a single pixel step size. Table 1

summarizes how the VPAT group registers are used in multiplier mode operation. In multiplier mode, the VPATREPO and

VPATREPE registers should always be programmed to the sam

value as the highest toggle position.

The example shown in Figure 41 illustrates this o

first toggle position is two, and the second toggle position is nine.

In nonmultiplier mode, this would cause the vertical sequence

to toggle at pixel 2 and then pixel 9 within a single HD line

ever, now toggle positions are multiplied by the VTPLEN = 4, so

the first toggle occurs at pixel count = 8, and the second toggle

occurs at pixel count = 36. Sweep mode has also been enable

to allow the toggle positions to cross the HD line boundaries.

VPATLENVTOGPositionToggleModeMultiplier

ed

peration. The

. How-

d

6

e

Table 16. Multiplier MODE Register Parameters

Register Length Range Description

MULTI 1 b High/Low High Enables Multiplier Mode.

XVPOL 1 b High/Low Starting Polarity of XV Signal in Each VPAT Group.

XVTOG1 12 b 0 to 4095 Pixel Location First Toggle Position for XV Signal in Each VPAT Group.

XVTOG2 12 b 0 to 4095 Pixel Location Second Toggle Position for XV Signal in Each VPAT Group.

XVTOG3 12 b 0 to 4095 Pixel Location Third Toggle Position for XV Signal in Each VPAT Group.

VPATLEN 10 b 0 to 1023 Pixels Used as Multiplier Factor for Toggle Position Counter.

VPATREP 12 b 0 to 4095 VPATREPE/VPATREPO Should Be Set to the Same Value as TOG2 or TOG3.