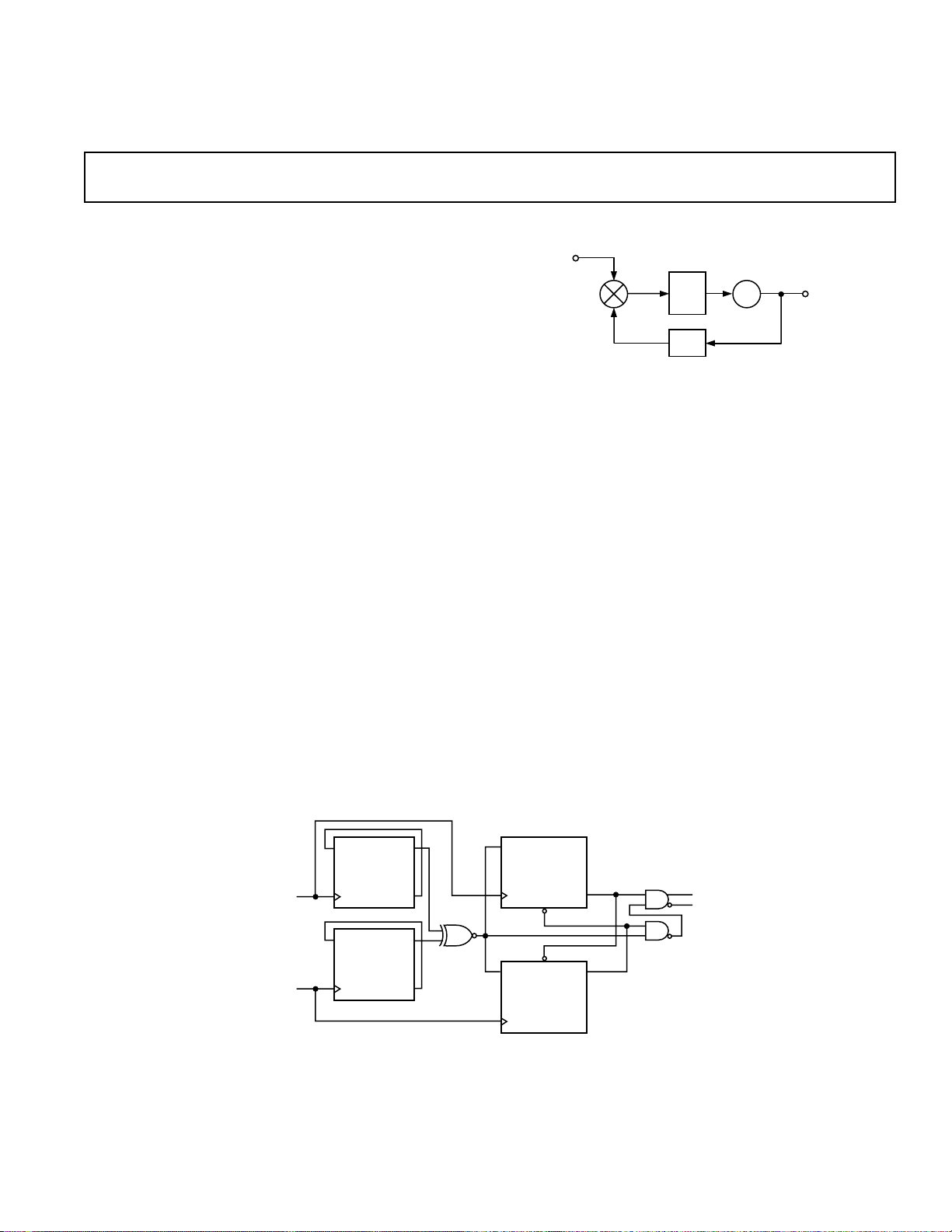

Ultrahigh Speed

LOWPASS

FILTER

1/N

VCO

AD9901

REFERENCE

INPUT

OSCILLATOR

OUTPUT

OPTIONAL 1/N PRESCALER

TYPICAL OF DIGITAL PLLs

a

FEATURES

Phase and Frequency Detection

ECL/TTL/CMOS Compatible

Linear Transfer Function

No “Dead Zone”

MIL-STD-883 Compliant Versions Available

APPLICATIONS

Low Phase Noise Reference Loops

Fast-Tuning “Agile” IF Loops

Secure “Hopping” Communications

Coherent Radar Transmitter/Receiver Chains

GENERAL DESCRIPTION

The AD9901 is a digital phase/frequency discriminator capable

of directly comparing phase/frequency inputs up to 200 MHz.

Processing in a high speed trench-oxide isolated process, combined with an innovative design, gives the AD9901 a linear

detection range, free of indeterminate phase detection zones

common to other digital designs.

With a single +5 V supply, the AD9901 can be configured to

operate with TTL or CMOS logic levels; it can also operate

with ECL inputs when operated with a –5.2 V supply. The

open-collector outputs allow the output swing to be matched to

post-filtering input requirements. A simple current setting resistor controls the output stage current range, permitting a reduction in power when operated at lower frequencies.

Phase/Frequency Discriminator

AD9901

PHASE-LOCKED LOOP

A major feature of the AD9901 is its ability to compare

phase/frequency inputs at standard IF frequencies without

prescalers. Excessive phase uncertainty which is common with

standard PLL configurations is also eliminated. The AD9901

provides the locking speed of traditional phase/frequency discriminators, with the phase stability of analog mixers.

The AD9901 is available as a commercial temperature range

device, 0°C to +70°C, and as a military temperature device,

–55°C to +125°C. The commercial versions are packaged in a

14-lead ceramic DIP and a 20-lead PLCC.

The AD9901 Phase/Frequency Discriminator is available in

versions compliant with MIL-STD-883. Refer to the Analog

Devices Military Products Databook or current AD9901/883B

data sheet for specifications.

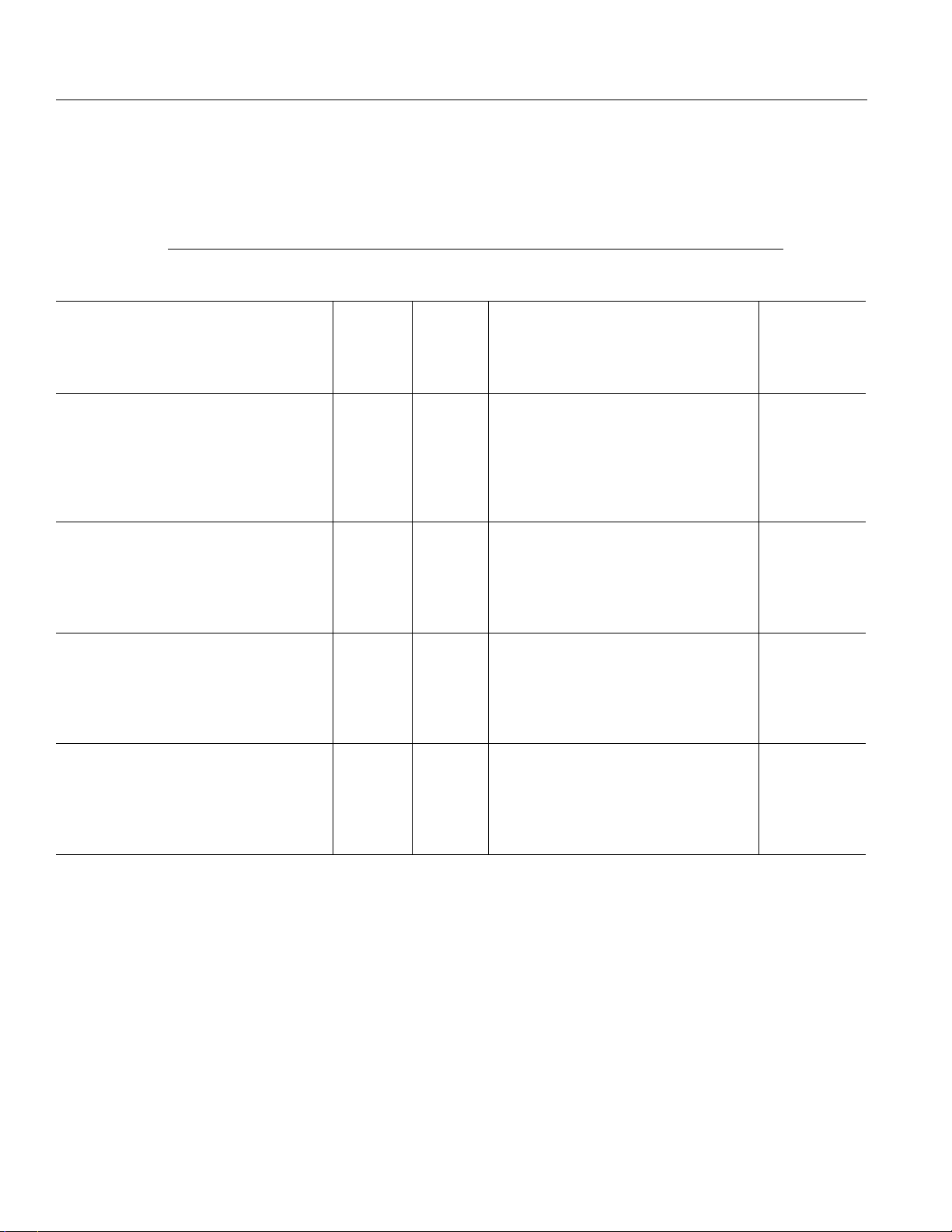

FUNCTIONAL BLOCK DIAGRAM

DQ

REFERENCE

INPUT

REFERENCE

INPUT

OSCILLATOR

INPUT

FLIP-FLOP

DQ

OSCILLATOR

FLIP-FLOP

Q

XOR

INPUT

Q

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

DQ

REFERENCE

FREQUENCY

DISCRIMINATOR

FLIP-FLOP

DQ

OSCILLATOR

FREQUENCY

DISCRIMINATOR

FLIP-FLOP

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

Q

R

S

Q

OUTPUT

OUTPUT

AD9901–SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

1

Positive Supply Voltage (+VS for TTL Operation) . . . . . +7 V

Negative Supply Voltage (–V

for ECL Operation) . . . . . –7 V

S

Input Voltage Range (TTL Operation) . . . . . . . 0 V to +5.5 V

Differential Input Voltage (ECL Operation) . . . . . . . . . .4.0 V

Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 mA

I

SET

Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 mA

ELECTRICAL CHARACTERISTICS

(ⴞVS = +5.0 V [for TTL] or –5.2 V [for ECL], unless otherwise noted)

Operating Temperature Range

AD9901KQ/KP . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature

2

Plastic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+150°C

Ceramic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+175°C

Lead Soldering Temperature (10 sec) . . . . . . . . . . . . .+300°C

Commercial Temperature

0ⴗC to +70ⴗC

AD9901KQ/KP

Test

Temp Level Min Typ Max Units

INPUT CHARACTERISTICS

TTL Input Logic “1” Voltage Full VI 2.0 V

TTL Input Logic “0” Voltage Full VI 0.8 V

TTL Input Logic “1” Current

TTL Input Logic “0” Current

3

3

Full VI 0.6 mA

Full VI 1.6 mA

ECL Differential Switching Voltage Full VI 300 mV

ECL Input Current Full VI 20 µA

OUTPUT CHARACTERISTICS

Peak-to-Peak Output Voltage Swing

4

Full VI 1.6 1.8 2.0 V

TTL Output Compliance Range Full V 3–7 V

ECL Output Compliance Range Full V ±2V

Range Full V 0.9–11 mA

I

OUT

Internal Reference Voltage Full VI 0.42 0.47 0.52 V

AC CHARACTERISTICS

Linear Phase Detection Range

4

40 kHz +25°C V 360 Degrees

30 MHz +25°C V 320 Degrees

70 MHz +25°C V 270 Degrees

Functionality @ 70 MHz +25°C I Pass/Fail

POWER SUPPLY CHARACTERISTICS

TTL Supply Current (+5.0 V)

ECL Supply Current (–5.2 V)

5, 6

5, 6

+25°C I 43.5 54.0 mA

Full I 43.5 54.0 mA

+25°C I 42.5 52.5 mA

Full I 42.5 52.5 mA

Nominal Power Dissipation +25°C V 218 mW

NOTES

1

Absolute maximum ratings are limiting values, to be applied individually, and beyond which the service ability of the circuit may be impaired. Functional operability

is not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

2

Maximum junction temperature should not exceed +175 °C for ceramic packages, +150°C for plastic packages. Junction temperature can be calculated by:

t

= PD (θ

J

where:

PD = power dissipation

θJA = thermal impedance from junction to air (°C/W)

θJC = thermal impedance from junction to case (°C/W)

t

= ambient temperature (°C)

A

t

= case temperature (°C)

C

typical thermal impedances:

AD9901 Ceramic DIP = θJA = 74°C/W; θJC = 21°C/W

AD9901 LCC = θJA = 80°C/W; θJC = 19°C/W

AD9901 PLCC = θJA = 88.2°C/W; θJC = 45.2°C/W

3

VL = +0.4 V; VH = +2.4 V.

4

R

= 47.5 Ω; RL = 182 Ω.

SET

5

lncludes load current of 10 mA (load resistors = 182 Ω).

6

Supply should remain stable within ±5% for normal operation.

Specifications subject to change without notice.

) +t

= PD (θ

JA

A

) +t

JC

C

REV. B–2–

S

+5.0V

0.47V

REFERENCE

TTL MODE = GROUND

ECL MODE = V

S

(–5.2V)

R

SET

TTL MODE = +VS (+5.0V)

ECL MODE = GROUND

AD9901

INPUT/OUTPUT EQUIVALENT CIRCUITS

(Based on DIP Pinouts)

VCO/REF, INPUT

DA3

V

MID

1kV

AD9901

5/12

VCO/REF, INPUT

VCO/REF, INPUT

4/13

3/14

–5.2V

TTL Input ECL Input Output

AD9901 BURN-IN CIRCUIT

(Based on DIP ECL Pinouts)

180V

50V

REG

0.01mF

–V

(–5.2V)

S

DIE LAYOUT AND MECHANICAL INFORMATION

GND (REFERENCE IN)

GND (REFERENCE IN)

GND (VCO IN)

REFERENCE IN (–VS)+VS (GND) OUTPUT

GND (–V

)

S

VS (–VS)

VCO IN (–V

)GND (VCO IN)

OUTPUT

R

SET

GND (–VS)

(GND)

+V

S

MID

180V

ALL RESISTORS 65%

ALL CAPACITORS 620%

ALL SUPPLY VOLTAGES 65%

V

= –1.3V 65%

MID

STATIC: DA2 = ECL HIGH; DA3 = ECL LOW

DYNAMIC: ECL HIGH

ORDERING GUIDE

Temperature Package Package

DA2

ECL HIGH

DA2

ECL LOW

ECL HIGH

DA3

ECL LOW

1kV

V

Model Ranges Descriptions Options

AD9901KQ 0°C to +70°C 14-Lead Cerdip Q-14

AD9901KP 0°C to +70°C 20-Lead Plastic Leaded Chip Carrier P-20A

AD9901TQ/883

AD9901TE/883

NOTE

1

For specifications, refer to Analog Devices Military Products Databook.

1

–55°C to +125°C 14-Lead Cerdip Q-14

1

–55°C to +125°C 20-Terminal Ceramic Leadless Chip Carrier E-20A

REV. B –3–

Die Dimensions . . . . . . . . . . . . . . . . . 63 × 118 × 16 (±2) mils

Pad Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 × 4 mils

Metalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Aluminum

Backing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . None

Substrate Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –V

Passivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Nitride

Die Attach . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Gold Eutectic

Bond Wire . . . . . . . . 1.25 mil Aluminum; Ultrasonic Bonding

S

AD9901

TTL/CMOS MODE FUNCTIONAL PIN DESCRIPTIONS

GROUND Ground connections for AD9901. Connect

all grounds together and to low impedance

ground plane as close to the device as

possible.

+V

S

Positive supply connection; nominally +5.0 V

for TTL operation.

BIAS Connect to +V

(+5 V) for TTL operation.

S

VCO INPUT TTL compatible input; normally connected

to the VCO output signal. VCO INPUT and

REFERENCE INPUT are equivalent to one

another.

OUTPUT The noninverted output. In TTL/CMOS

mode, the output swing is approximately

+3.2 V to +5 V.

R

SET

External R

through the R

mum full-scale output current. R

connection. The current

SET

resistor is equal to the maxi-

SET

SET

should

be connected to ground through an external

resistor in TTL mode. I

(max).

I

LOAD

= 0.47 V/R

SET

SET

=

OUTPUT The inverted output. In TTL/CMOS mode,

the output swing is approximately +3.2 V to

+5 V.

REFERENCE TTL compatible input, normally connected

INPUT to the reference input signal. The VCO

INPUT and the REFERENCE INPUT are

equivalent.

+V

S

R1

REFERENCE

OUTPUT

+V

S

OUTPUT

R2

R

SET

ECL MODE FUNCTIONAL PIN DESCRIPTIONS

–V

S

Negative supply connection, nominally

–5.2 V for ECL operation.

BIAS Connect to –5.2 V for ECL operation.

VCO INPUT Inverted side of ECL compatible differential

input, normally connected to the VCO output

signal.

VCO INPUT Noninverted side of ECL-compatible

differential input, normally connected to the

VCO output signal.

OUTPUT The noninverted output. In ECL mode, the

output swing is approximately 0 V to –1.8 V.

GROUND Ground connections for AD9901. Connect

all grounds together and to low-impedance

ground plane as close to the device as

possible.

R

SET

External R

through the R

mum full-scale output current. R

be connected to –V

resistor in ECL mode. I

(max).

I

LOAD

connection. The current

SET

resistor is equal to the maxi-

SET

through an external

S

SET

SET

= 0.47 V/R

should

SET

=

OUTPUT The inverted output. In ECL mode, the out-

put swing is approximately 0 V to –1.8 V.

REFERENCE Noninverted side of ECL-compatible

INPUT differential input, normally connected to the

reference input signal. The VCO INPUT and

the REFERENCE INPUT are equivalent to

one another.

REFERENCE Inverted side of ECL-compatible differential

INPUT input, normally connected to the reference

input signal. The VCO INPUT and the

REFERENCE INPUT are equivalent.

–V

S

R1

REFERENCE

INPUT

REFERENCE

INPUT

–V

S

OUTPUT

R2

R

SET

AD9901

REG

BIAS

+V

S

VCO

INPUT

OUTPUT

+V

R3

+V

S

S

Figure 1. TTL Mode (Based on DIP Pinouts)

AD9901

REG

BIAS

–V

S

VCO

INPUT

VCO

INPUT

–V

OUTPUT

S

R3

Figure 2. ECL Mode (Based on DIP Pinouts)

REV. B–4–

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

II – 100% production tested at +25°C, and sample tested

at specified temperatures.

III – Sample tested only.

IV – Parameter is guaranteed by design and characteriza-

tion testing.

PIN CONFIGURATIONS

AD9901

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C. 100%

production tested at temperature extremes for extended

temperature devices; sample tested at temperature extremes for commercial/industrial devices.

GROUND

BIAS

GROUND

GROUND

VCO INPUT

OUTPUT

+V

S

4

GROUND

NC

5

6

GROUND

7

NC

VCO INPUT

8

NC = NO CONNECT

TTL DIP Pinouts

1

2

3

AD9901

4

TOP VIEW

(Not to Scale)

5

6

7

14

GROUND

13

GROUND

12

REFERENCE INPUT

11

+V

10

OUTPUT

9

R

SET

8

GROUND

TTL LCC Pinouts

BIASOUTPUT

GROUNDNCGROUND

GROUND

20 19123

AD9901

TOP VIEW

(Not to Scale)

910111213

S

NC

+V

SET

R

GROUND

S

18

REFERENCE INPUT

NC

17

16

+V

S

15

NC

14

OUTPUT

ECL DIP Pinouts

1

–V

S

2

BIAS

–V

S

3

4

(Not to Scale)

5

6

7

VCO INPUT

VCO INPUT

OUTPUT

GROUND

ECL LCC Pinouts

VCO INPUT

VCO INPUT

NC = NO CONNECT

4

NC

5

6

7

NC

8

–V

S

AD9901

TOP VIEW

BIASOUTPUT

–VSNC

AD9901

TOP VIEW

(Not to Scale)

910111213

GROUND

14

REFERENCE INPUT

13

REFERENCE INPUT

12

–V

S

11

GROUND

10

OUTPUT

9

R

SET

8

–V

S

REFERENCE INPUT

REFERENCE INPUT

20 19123

18

17

16

15

14

S

NC

SET

–V

R

–V

S

NC

GROUND

NC

OUTPUT

TTL PLCC Pinouts

BIAS

GROUND

NC

GROUND

PIN 1

IDENTIFIER

NC

GROUND

18

17

16

15

14

SET

R

S

OUTPUT

3 2 1 20 19

GROUND REFERENCE INPUT

GROUND NC

VCO INPUT +V

NC = NO CONNECT

4

5

AD9901

6

TOP VIEW

(Not to Scale)

7

OUTPUT NC

8

NC

9 10 11 12 13

S

NC

+V

GROUND

REV. B –5–

ECL PLCC Pinouts

S

BIAS

–V

NC

REFERENCE INPUT

3 2 1 20 19

VCO INPUT

VCO INPUT NC

NC = NO CONNECT

4

5

6

(Not to Scale)

7

8

9 10 11 12 13

AD9901

TOP VIEW

–V

S

OUTPUT NC

NC

NC

GROUND

REFERENCE INPUT

PIN 1

IDENTIFIER

S

NC

SET

–V

R

18

–V

17

GROUND

16

15

14

OUTPUT

S

AD9901

THEORY OF OPERATION

A phase detector is one of three basic components of a phaselocked loop (PLL); the other two are a filter and a tunable oscillator. A basic PLL control system is shown in Figure 3.

REFERENCE

INPUT

LOWPASS

FILTER

VCO

OSCILLATOR

OUTPUT

AD9901

1/N

OPTIONAL 1/N PRESCALER

TYPICAL OF DIGITAL PLLs

Figure 3. Phase-Locked Loop Control System

The function of the phase detector is to generate an error signal

that is used to retune the oscillator frequency whenever its output deviates from a reference input signal. The two most common methods of implementing phase detectors are (1) an analog

mixer and (2) a family of sequential logic circuits known as

digital phase detectors.

The AD9901 is a digital phase detector. As illustrated in the

block diagram of the unit, straightforward sequential logic design is used. The main components include four “D” flip-flops,

an exclusive-OR gate (XOR) and some combinational output

logic. The circuit operates in two distinct modes: as a linear

phase detector and as a frequency discriminator.

When the reference and oscillator are very close in frequency,

only the phase detection circuit is active. If the two inputs are

substantially different in frequency, the frequency discrimination circuit overrides the phase detector portion to drive the

oscillator frequency toward the reference frequency and put it

within range of the phase detector.

Input signals to the AD9901 are pulse trains, and its output

duty cycle is proportional to the phase difference of the oscillator and reference inputs. Figures 4, 5 and 6 illustrate, respectively, the input/output relationships at lock; with the

REFERENCE

INPUT

OSCILLATOR

INPUT

REFERENCE

FLIP-FLOP

OUTPUT

OSCILLATOR

FLIP-FLOP

OUTPUT

XORGATE

OUTPUT

DC MEAN VALUE

Figure 4. AD9901 Timing Waveforms at “Lock”

REFERENCE

INPUT

OSCILLATOR

INPUT

REFERENCE

FLIP-FLOP

OUTPUT

OSCILLATOR

FLIP-FLOP

OUTPUT

XORGATE

OUTPUT

Figure 5. Timing Waveforms (

DC MEAN VALUE

φ

OUT

Leads

φ

)

IN

REFERENCE

INPUT

OSCILLATOR

INPUT

REFERENCE

FLIP-FLOP

OUTPUT

OSCILLATOR

FLIP-FLOP

OUTPUT

XORGATE

OUTPUT

Figure 6. Timing Waveforms (

DC MEAN VALUE

φ

OUT

Lags

φ

)

IN

oscillator leading the reference frequency; and with the oscillator

lagging. This output pulse train is low-pass filtered to extract the

dc mean value [K

(φI – φ

φ

)] where Kφ is a proportionality con-

O

stant (phase gain).

At or near lock (Figures 4, 5 and 6), only the two input flipflops and the exclusive-OR gate (the phase detection circuit) are

active. The input flip-flops divide both the reference and oscillator frequencies by a factor of two. This insures that inputs to the

exclusive-OR are square waves, regardless of the input duty

cycles of the frequencies being compared. This division-by-two

also moves the nonlinear detection range to the ends of the

range rather than near lock, which is the case with conventional

digital phase detectors.

Figure 7 illustrates the constant gain near lock.

2

FO = 70MHz

1

OUTPUT VOLTAGE SWING

0

–2p

PHASE DIFFERENCE AT INPUTS

FO = 200MHz

TYPICAL PHASE DETECTOR

GAIN IS 0.2865V/RAD

–p

DV

OUT

FO = 50MHz

= 1.8V

0

Figure 7. Phase Gain Plot

When the two square waves are combined by the XOR, the

output has a 50% duty cycle if the reference and oscillator in-

puts are exactly 180° out of phase; under these conditions, the

AD9901 is operating in a locked mode. Any shift in the phase

relationship between these input signals causes a change in the

output duty cycle. Near lock, the frequency discriminator flipflops provide constant HIGH levels to gate the XOR output to

the final output.

The duty cycle of the AD9901 is a direct measure of the phase

difference between the two input signals when the unit is near

lock. The transfer function can be stated as [K

where K

is the allowable output voltage range of the AD9901

φ

(φI – φ

φ

](V/RAD),

O

divided by 2 π.

For a typical output swing of 1.8 V, the transfer function can be

stated as (1.8 V/2 π = 0.285 V/RAD). Figure 7 shows the rela-

tionship of the dc mean value of the AD9901 output as a function of the phase difference of the two inputs.

REV. B–6–

AD9901

10

0%

100

90

500mV

5ns

VARACTORS TUNING VOLTAGE – Volts

165

–1

VCO FREQUENCY – MHz

155

145

135

125

115

105

95

85

75

65

0

12 3 4 5 6

REV. B –7–

500mV

100

90

10

0%

200ns

Figure 8. AD9901 Output Waveform

(F

<< FI)

O

500mV

100

90

10

0%

Figure 9. AD9901 Output Waveform

(F

>> FI)

O

It is important to note that the slope of the transfer function is

constant near its midpoint. Many digital phase comparators have

an area near the lock point where their gain goes to zero, resulting in a “dead zone.” This causes increased phase noise (jitter) at

the lock point.

The AD9901 avoids this dead zone by shifting it to the endpoints of the transfer curve, as indicated in Figure 7. The increased gain at either end increases the effective error signal to

pull the oscillator back into the linear region. This does not

affect phase noise, which is far more dependent upon lock region

characteristics.

It should be noted, however, that as frequency increases, the

linear range is decreased. At the ends of the detection range, the

reference and oscillator inputs approach phase alignment. At this

point, slew rate limiting in the detector effectively increases

phase gain. This decreases the linear detection by nominally

3.6 ns. Therefore, the typical detection range can be found by

calculating [(1/F – 3.6 ns)/(1/F)] × 360°. As an example, at

200 MHz the linear phase detection range is ±50°.

Away from lock, the AD9901 becomes a frequency discriminator. Any time either the reference or oscillator input occurs twice

before the other, the Frequency High or Frequency Low flip-flop

is clocked to logic LOW. This overrides the XOR output and

holds the output at the appropriate level to pull the oscillator

toward the reference frequency. Once the frequencies are within

the linear range, the phase detector circuit takes over again.

Combining the frequency discriminator with the phase detector

eliminates locking to a harmonic of the reference.

Figure 8 shows the effect of the “Frequency Low” flip-flop when

the oscillator frequency is much lower than the reference input.

The narrow pulses, which result from cycles when two positive

reference-input transitions occur before a positive VCO edge,

increase the dc mean value. Figure 9 illustrates the inverse effect

when the “Frequency High” flip-flop reacts to a much higher

VCO frequency.

Figure 10 shows the output waveform at lock for 50 MHz operation. This output results when the phase difference between

reference and oscillator is approximately – πRad.

AD9901 APPLICATIONS

The figure below illustrates a phase-locked loop (PLL) system

utilizing the AD9901. The first step in designing this type of

circuit is to characterize the VCO’s output frequency as a function of tuning voltage. The transfer function of the oscillator in

the diagram is shown in Figure 11.

200ns

Figure 10. AD9901 Output Waveform

(F

= FI = 50 MHz)

O

Figure 11. VCO Frequency vs. Voltage

Next, the range of frequencies over which the VCO is to operate

is examined to assure that it lies on a linear portion of the transfer

curve. In this case, frequencies from 100 MHz to 120 MHz

result from tuning voltages of approximately +1.5 V to +2.5 V.

Because the nominal output swing of the AD9901 is 0 V to –1.8 V,

an inverting amplifier with a gain of 2 follows the loop filter.

As shown in the illustration, a simple passive RC low-pass filter

made up of two resistors and a tantalum capacitor eliminates the

need for an expensive high speed op amp active-filter design. In

this passive-filter second-order-loop system, where n = 2, the

damping factor is equal to:

δ = 0.5 [K

OKd

and the values for τ

/n(τ

and

1

1/2

+

τ

)]

[τ

1

2

τ

2

+ (n/KOKd)]

2

are the low-pass filter’s time constants R1C and R2C. The gain of 2 of the inverting stage, when

combined with the phase detector’s gain, gives:

K

= 0.572 V/RAD

d

With K

3.11 × 10

= 115.2 MRAD/s/V, τ1 equals 1.715s, and τ

O

–4

s for the required damping factor of 0.7. The illus-

equals

2

trated values of 30 Ω (R1), 160 Ω (R2), and 10 µF (C) in the

diagram approximate these time constants.

The gain of the RC filter is:

V

= (1 + sR2C)/[1 + s(R1 + R2)C].

O/VI

Where K

ω

n

>> ω

OKd

= [KOKd/n(

, the system’s natural frequency:

n

1

+

1/2

τ

)]

2

= 4.5 kHz.

τ

For general information about phase-locked loop design, the

user is advised to consult the following references: Gardner,

Phase-Lock Techniques (Wiley); or Best, Phase Locked Loops

(McGraw-Hill).

AD9901

3

PIN 1

IDENTIFIER

4

19

18

8

9

14

13

TOP VIEW

(PINS DOWN)

0.395 (10.02)

0.385 (9.78)

SQ

0.356 (9.04)

0.350 (8.89)

SQ

0.048 (1.21)

0.042 (1.07)

0.048 (1.21)

0.042 (1.07)

0.020

(0.50)

R

0.050

(1.27)

BSC

0.021 (0.53)

0.013 (0.33)

0.330 (8.38)

0.290 (7.37)

0.032 (0.81)

0.026 (0.66)

0.180 (4.57)

0.165 (4.19)

0.040 (1.01)

0.025 (0.64)

0.056 (1.42)

0.042 (1.07)

0.025 (0.63)

0.015 (0.38)

0.110 (2.79)

0.085 (2.16)

+V

AD9901

DIP

PINOUTS

ALTERNATE HIGH LEVEL

OUTPUT CIRCUIT

TYPICALLY +15V TO +60V)

(6V

S

REFERENCE

INPUT

S

OUTPUT

OUTPUT

55MHz

+5.0V

–5.2V

–5.2V

AD96685

OSC OSC

50V

–2V

REFREF

AD9901

47.5V

50V

OUT

OUT

–5.2V

DIVIDE-

BY-TWO

–5.2V

R

SET

182V

160kV

30V

10mF

LOOP

FILTER

OSCILLATOR

OUTPUT

110MHz

50V

–2V

OSCILLATOR

MC1648

–5.2V

AD741

OFFSET

1kV 2kV

1kV

390V

100nH

–5.2V

AD741

C1272b–0–1/99

MV1404

51kV

MV1404

Figure 12. Phased-Locked Loop Using AD9901

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

14-Lead Cerdip

(Q-14)

0.005 (0.13) MIN 0.098 (2.49) MAX

0.200 (5.08)

MAX

0.200 (5.08)

0.125 (3.18)

14

1

PIN 1

0.785 (19.94) MAX

0.023 (0.58)

0.014 (0.36)

0.100

(2.54)

BSC

8

0.310 (7.87)

0.220 (5.59)

7

0.060 (1.52)

0.015 (0.38)

0.070 (1.78)

0.030 (0.76)

0.150

(3.81)

MIN

SEATING

PLANE

0.320 (8.13)

0.290 (7.37)

15°

0°

0.015 (0.38)

0.008 (0.20)

0.358 (9.09)

0.342 (8.69)

20-Terminal Ceramic Leadless Chip Carrier 20-Lead Plastic Leaded Chip Carrier

(E-20A) (P-20A)

0.200 (5.08)

BSC

0.075

(1.91)

REF

0.055 (1.40)

0.045 (1.14)

REF

19

18

14

13

20

1

BOTTOM

VIEW

0.150 (3.81)

0.100 (2.54) BSC

0.015 (0.38)

3

MIN

4

0.050 (1.27)

8

BSC

9

45° TYP

BSC

0.028 (0.71)

0.022 (0.56)

SQ

0.100 (2.54)

0.064 (1.63)

0.358

(9.09)

MAX

SQ

0.088 (2.24)

0.054 (1.37)

0.095 (2.41)

0.075 (1.90)

0.011 (0.28)

0.007 (0.18)

R TYP

0.075 (1.91)

PRINTED IN U.S.A.

REV. B–8–

Loading...

Loading...