Analog Devices AD9879 Datasheet

Mixed-Signal Front End

a

FEATURES

Low Cost 3.3 V MxFE

DOCSIS EURO DOCSIS DVB DAVIC Compliant

Set-Top Box and Cable Modem Applications

232 MHz Quadrature Digital Upconverter

12-Bit Direct IF DAC (TxDAC+

Up to 65 MHz Carrier Frequency DDS

Programmable Sampling Clock Rates

16 Upsampling Interpolation LPF

Single-Tone Frequency Synthesis

Analog Tx Output Level Adjust

Direct Cable Amp Interface

12-Bit, 33 MSPS Direct IF ADC

with Optional Video Clamping Input

10-Bit, 33 MSPS Direct IF ADC

Dual 7-Bit, 16.5 MSPS Sampling I/Q ADC

12-Bit Sigma-Delta Auxiliary DAC

APPLICATIONS

Cable Modem and Satellite Systems

Set-Top Boxes

Power Line Modem

PC Multimedia

Digital Communications

Data and Video Modems

QAM, OFDM, FSK Modulation

™ for

™)

TX DATA

SPORT

RXIQ[3:0]

RXIF[11:0]

Set-Top Box, Cable Modem

AD9879

FUNCTIONAL BLOCK DIAGRAM

I

16

Tx

Q

4

CONTROL REGISTERS

MUX

MUX

AD9879

DDS

8

10

12

SINC

ADC

ADC

ADC

12

–1

DAC

--_OUT

PLL

XM/N

MUX

MUX

CLAMP

2

2

TX

CAPORT

MCLK

RXI

RXQ

RX10

RX12

VIDEO

GENERAL DESCRIPTION

The AD9879 is a single-supply cable modem/set-top box mixed

signal front end. The device contains a transmit path interpolation

filter, a complete quadrature digital upconverter, and a transmit

DAC. The receive path contains a 12-bit ADC, a 10-bit ADC,

and dual 7-Bit ADCs. All internally required clocks and an output

system clock are generated by the PLL from a single crystal or

clock input.

The transmit path interpolation filter provides an upsampling

factor of 16× with an output signal bandwidth as high as 8.3 MHz.

Carrier frequencies up to 65 MHz with 26 bits of frequency tuning

resolution can be generated by the direct digital synthesizer

(DDS). The transmit DAC resolution is 12 bits and can run at

sampling rates as high as 232 MSPS. Analog output scaling from

0 dB to 7.5 dB in 0.5 dB steps is available to preserve SNR when

reduced output levels are required.

MxFE and TxDAC are trademarks of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

The 12-bit and 10-bit IF ADCs can convert direct IF inputs up

to 70 MHz and run at sample rates up to 33 MSPS. A video

input with an adjustable signal clamping level, along with the

10-bit ADC, allow the AD9879 to process an NTSC and a

QAM channel simultaneously.

The programmable sigma-delta DAC can be used to control

external components, such as variable gain amplifiers (VGAs) or

voltage controlled tuners. The CA PORT provides an interface to

the AD8321/AD8323 or AD8322/AD8327 programmable gain

amplifier (PGA) cable drivers enabling host processor control via

the MxFE SPORT. The AD9879 is available in a 100-lead

MQFP package. It offers enhanced receive path undersampling

performance and lower cost when compared with the pin compatible AD9873. The AD9879 is specified over the commercial

(–40°C to +85°C) temperature range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

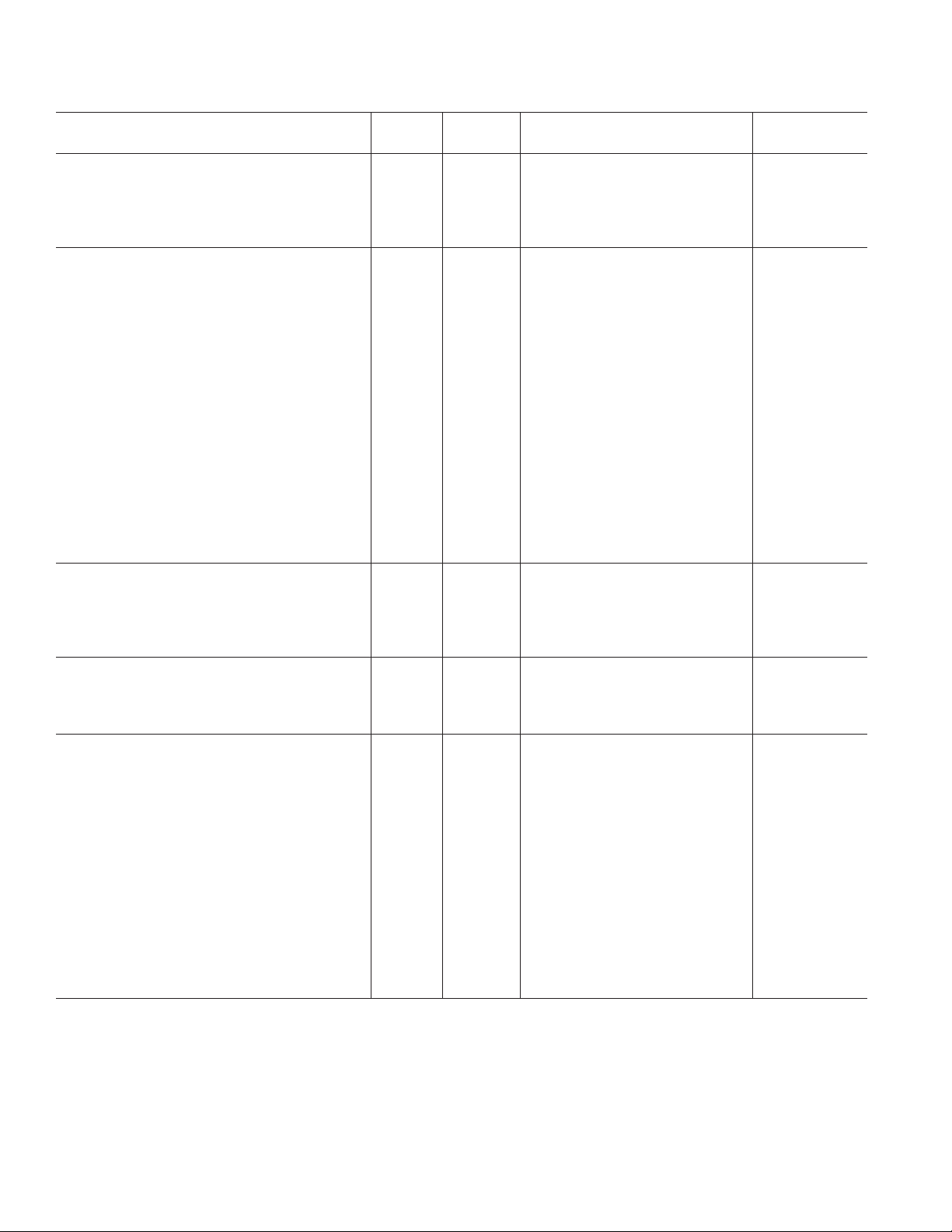

AD9879–SPECIFICATIONS

(VAS = 3.3 V 5%, VDS = 3.3 V 10%, f

f

= 54 MHz (M = 8), ADC Clock from OSCIN, R

MCLK

= 27 MHz, f

OSCIN

= 216 MHz,

SYSCLK

= 4.02 k, 75 DAC Load)

SET

Test

Parameter Temp Level Min Typ Max Unit

OSCIN AND XTAL CHARACTERISTICS

Frequency Range Full II 3 29 MHz

Duty Cycle Full II 35 50 65 %

Input Impedance 25ºC III 100

||

3MΩ||pF

MCLK Cycle to Cycle Jitter 25ºC III 6 ps rms

Tx DAC CHARACTERISTICS

Resolution N/A N/A 12 Bits

Maximum Sample Rate Full II 232 MHz

Full-Scale Output Current Full II 4 10 20 mA

Gain Error (Using Internal Reference) Full II –2.0 –1.0 +2.0 %FS

Offset Error 25ºC III ±1.0 %FS

Reference Voltage (REFIO Level) 25ºC III 1.23 V

Differential Nonlinearity (DNL) 25ºC III ±2.5 LSB

Integral Nonlinearity (INL) 25ºC III ± 8 LSB

Output Capacitance 25ºC III 5 pF

Phase Noise @ 1 kHz Offset, 42 MHz

Crystal and OSCIN Multiplier Enabled at 16 25ºC III –110 dBc/Hz

Output Voltage Compliance Range Full II –0.5 +1.5 V

Wideband SFDR

5 MHz Analog Out, I

65 MHz Analog Out, I

= 10 mA Full I 60.8 66.9 dBc

OUT

= 10 mA Full I 44.0 46.2 dBc

OUT

Narrow-band SFDR (±1 MHz Window):

5 MHz Analog Out, I

= 10 mA Full I 65.4 72.3 dBc

OUT

Tx MODULATOR CHARACTERISTICS

I/Q Offset Full II 50 55 dB

Pass-Band Amplitude Ripple (f < f

Pass-Band Amplitude Ripple (f < f

Stop-Band Response (f > f

3/4) Full II –63 dB

IQCLK

/8) Full II ±0.1 dB

IQCLK

/4) Full II ±0.5 dB

IQCLK

Tx GAIN CONTROL

Gain Step Size 25ºC III 0.5 dB

Gain Step Error 25ºC III <0.05 dB

Settling Time to 1% (Full-Scale Step) 25ºC III 1.8 s

IQ ADC CHARACTERISTICS

Resolution* N/A N/A 6 Bits

Maximum Conversion Rate Full III 14.5 MHz

Pipeline Delay N/A N/A 3.5 ADC Cycles

Offset Matching between I and Q ADCs ±4.0 LSBs

Gain Matching between I and Q ADCs ±2.0 LSBs

Analog Input

Input Voltage Range* Full III 1 Vppd

Input Capacitance 25ºC III 2.0 pF

Differential Input Resistance 25ºC III 4 kΩ

AC Performance (A

= 0.5 dBFS, fIN = 5 MHz)

IN

Effective Number of Bits (ENOB) Full I 5.25 5.8 Bits

Signal-to-Noise Ratio (SNR) Full I 36.5 dB

Total Harmonic Distortion (THD) Full I –50 dB

Spurious-Free Dynamic Range (SFDR) Full I 51 dB

*IQ ADC in Default Mode. ADC Clock Select Register 8, Bit 3 set to “0.”

REV. 0–2–

AD9879

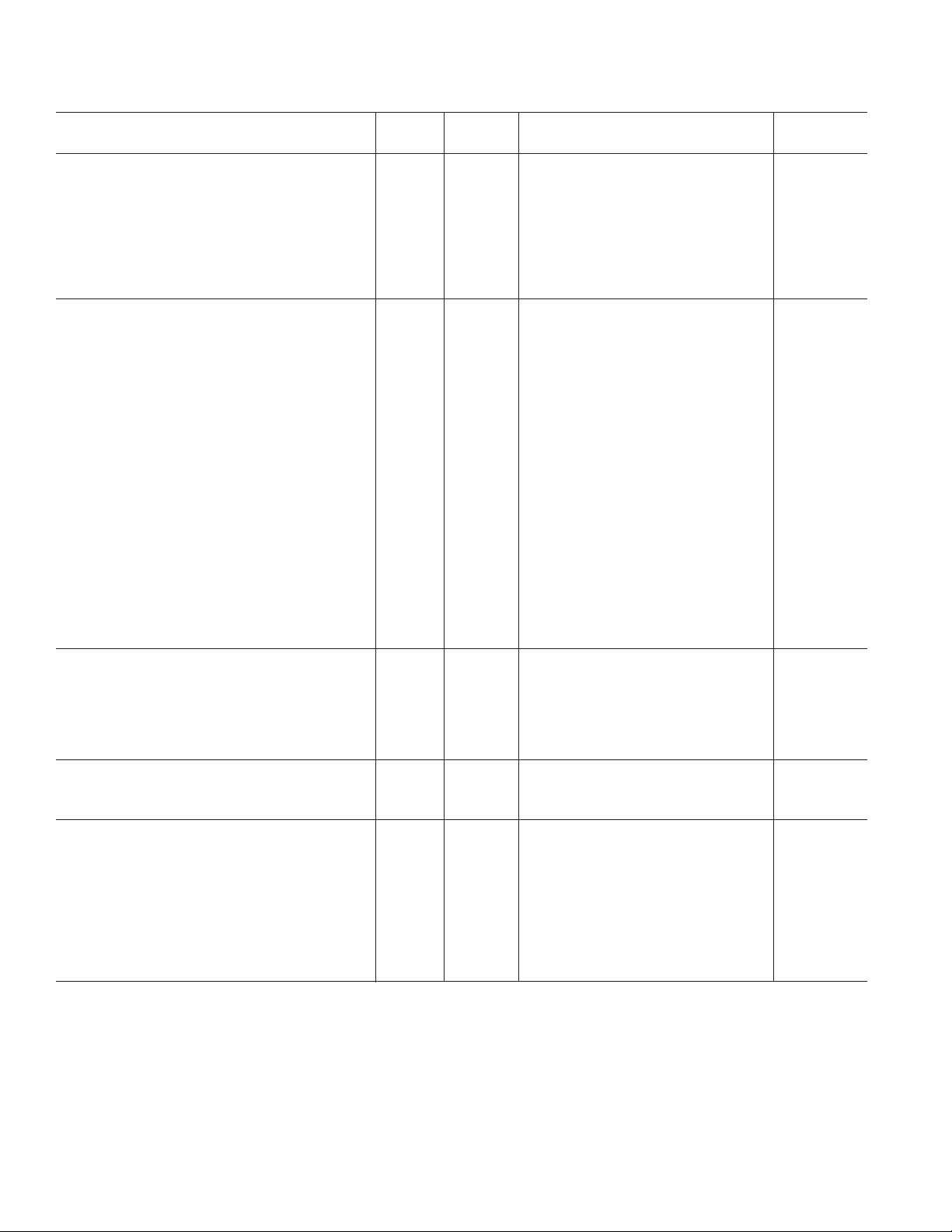

Test

Parameter Temp Level Min Typ Max Unit

10-BIT ADC CHARACTERISTICS

Resolution N/A N/A 10 Bits

Maximum Conversion Rate Full II 29 MHz

Pipeline Delay N/A N/A 4.5 ADC Cycles

Analog Input

Input Voltage Range Full III 2.0 Vppd

Input Capacitance 25ºC III 2 pF

Differential Input Resistance 25ºC II 4 kΩ

Reference Voltage Error

(REFT10–REFB10) –1 V Full I ± 4 ±200 mV

AC Performance (A

ADC Sample Clock Source = OSCIN

Signal-to-Noise and Distortion (SINAD) Full I 58.3 59.9 dB

Effective Number of Bits (ENOB) Full I 9.4 9.65 Bits

Signal-to-Noise Ratio (SNR) Full I 58.6 60 dB

Total Harmonic Distortion (THD) Full I –73 –62 dB

Spurious-Free Dynamic Range (SFDR) Full I 65.7 76 dB

AC Performance (A

ADC Sample Clock Source = OSCIN

Signal-to-Noise and Distortion (SINAD) Full II 57.7 59.0 dB

Effective Number of Bits (ENOB) Full II 9.29 9.51 Bits

Signal-to-Noise Ratio (SNR) Full II 57.8 59.1 dB

Total Harmonic Distortion (THD) Full II +57 –75 dB

Spurious-Free Dynamic Range (SFDR) Full II 64 78 dB

12-BIT ADC CHARACTERISTICS

Resolution N/A N/A 12 Bits

Maximum Conversion Rate Full II 29 MHz

Pipeline Delay N/A N/A 5.5 ADC Cycles

Analog Input

Input Voltage Range Full III 2 Vppd

Input Capacitance 25ºC III 2 pF

Differential Input Resistance 25ºC III 4 kΩ

Reference Voltage Error

(REFT12–REFB12) –1 V Full I ± 16 ± 200 mV

AC Performance (A

ADC Sample Clock Source = OSCIN

Signal-to-Noise and Distortion (SINAD) Full I 60.0 65.2 dB

Effective Number of Bits (ENOB) Full I 9.67 10.53 Bits

Signal-to-Noise Ratio (SNR) Full I 60.3 65.6 dB

Total Harmonic Distortion (THD) Full I –76.6 –58.7 dB

Spurious-Free Dynamic Range (SFDR) Full I 64.7 79 dB

AC Performance (A

ADC Sample Clock Source = OSCIN

Signal-to-Noise and Distortion (SINAD) Full II 59.5 62.7 dB

Effective Number of Bits (ENOB) Full II 9.59 10.1 Bits

Signal-to-Noise Ratio (SNR) Full II 59.7 63.0 dB

Total Harmonic Distortion (THD) Full II –75.5 –60.5 dB

Spurious-Free Dynamic Range (SFDR) Full II 63.8 79 dB

= –0.5 dBFS, fIN = 5 MHz)

IN

= –0.5 dBFS, fIN = 50 MHz)

IN

= –0.5 dBFS, fIN = 5 MHz)

IN

= –0.5 dBFS, fIN = 50 MHz)

IN

REV. 0

–3–

AD9879

Test

Parameter Temp Level Min Typ Max Unit

CHANNEL-TO-CHANNEL ISOLATION

Tx DAC-to-ADC Isolation (A

Isolation between Tx and IQ ADCs 25ºC III >60 dB

Isolation between Tx and 10-Bit ADC 25ºC III >80 dB

Isolation between Tx and 12-Bit ADC 25ºC III >80 dB

ADC-to-ADC (AIN = –0.5 dBFS, f = 5 MHz)

Isolation between IF10 and IF12 ADCs 25ºC III >85 dB

Isolation between Q and I Inputs 25ºC III >50 dB

TIMING CHARACTERISTICS (10 pF Load)

Minimum RESET Pulsewidth Low (tRL) N/A N/A 5 t

Digital Output Rise/Fall Time Full II 2.8 4 ns

Tx/Rx Interface

MCLK Frequency (f

MCLK

TxSYNC/TxIQ Setup Time (t

TxSYNC/TxIQ Hold Time (t

MCLK Rising Edge to

RxSYNC/RxIQ/IF Valid Delay (t

OSCOUT Rising or Falling Edge to

RxSYNC/RxIQ/IF Valid Delay (t

OSCOUT Edge to MCLK Falling Edge (t

Serial Control Bus

Maximum SCLK Frequency (f

Minimum Clock Pulsewidth High (t

Minimum Clock Pulsewidth Low (t

Maximum Clock Rise/Fall Time Full II 1 ms

Minimum Data/Chip-Select Setup Time (t

Minimum Data Hold Time (t

Maximum Data Valid Time (tDV) Full II 30 ns

CMOS LOGIC INPUTS

Logic “1” Voltage 25ºC II V

Logic “0” Voltage 25ºC II 0.4 V

Logic “1” Current 25ºC II 12 A

Logic “0” Current 25ºC II 12 A

Input Capacitance 25ºC II 3 pF

CMOS LOGIC OUTPUTS (1 mA Load)

Logic “1” Voltage 25ºC II V

Logic “0” Voltage 25ºC II 0.4 V

POWER SUPPLY

Supply Current, IS (Full Operation) 25CII 163 178 mA

Analog Supply Current, I

Digital Supply Current, I

Supply Current, I

S

Standby (PWRDN Pin Active) 25ºC II 119 123 mA

Full Power-Down (Register 2 = 0xF9) 25ºC III 16 mA

Power-Down Tx Path (Register 2 = 0x60) 25ºC III 113 mA

Power-Down Rx Paths (Register 2 = 0x19) 25ºC III 110 mA

= 5 MHz)

OUT

MCLK

) Full II 66 MHz

) Full II 3 ns

SU

) Full II 3 ns

HD

) Full II 0 1.0 ns

MD

) Full II T

OD

SCLK

) Full II 0 ns

DH

AS

DS

) Full II –1.0 +1.0 ns

EE

) Full II 15 MHz

) Full II 30 ns

PWH

) Full II 30 ns

PWL

) Full II 25 ns

DS

25ºC III 95 mA

25ºC III 68 mA

/4 – 2.0 T

OSC

– 0.7 V

DRVDD

– 0.6 V

DRVDD

OSC

/4 + 3.0 ns

Cycles

REV. 0–4–

AD9879

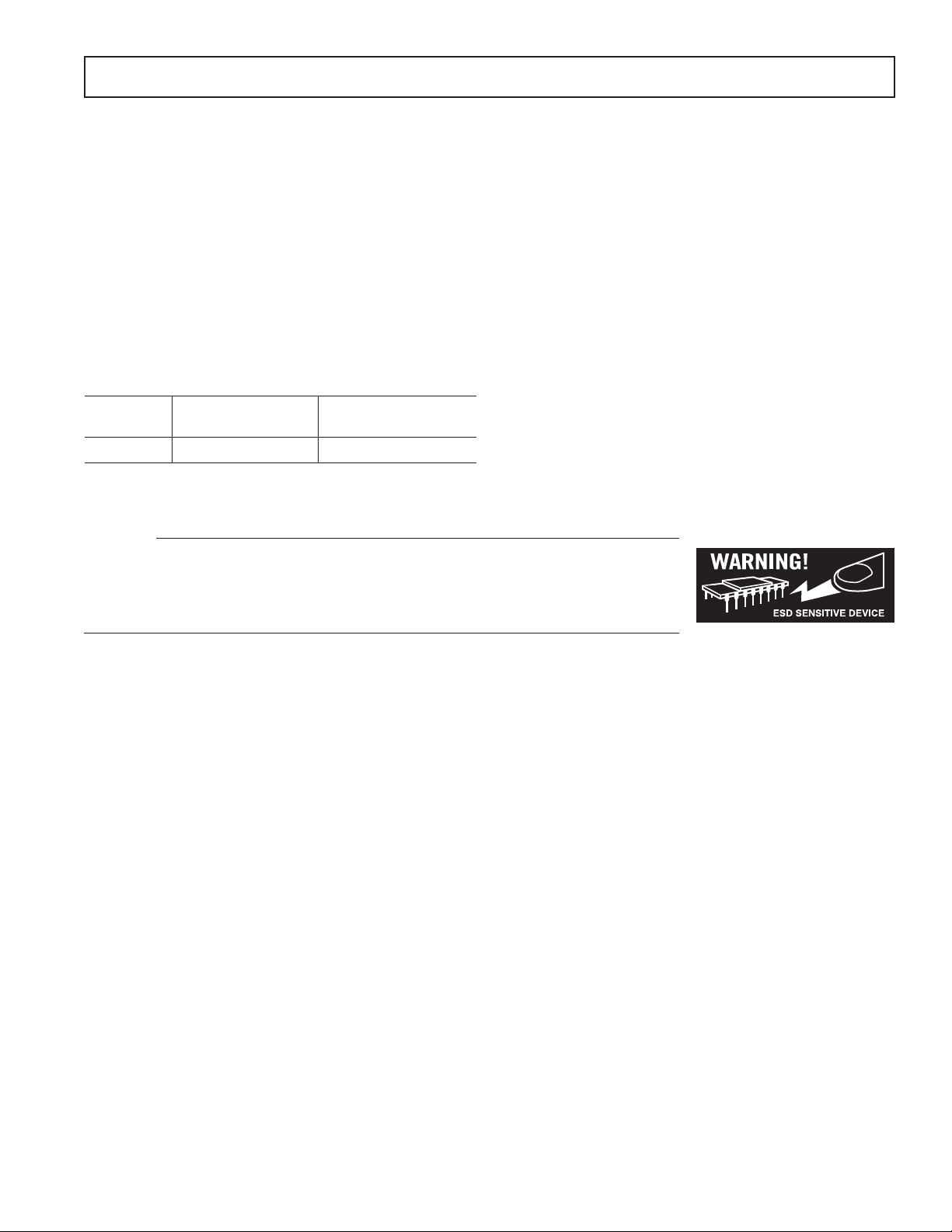

ABSOLUTE MAXIMUM RATINGS*

Power Supply (V

AVDD,VDVDD,VDRVDD

) . . . . . . . . . . . . . . 3.9 V

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . 5 mA

Digital Inputs . . . . . . . . . . . . . . . . . –0.3 V to V

Analog Inputs . . . . . . . . . . . . . . . . . . –0.3 V to V

DRVDD

AVDD

+ 0.3 V

+ 0.3 V

Operating Temperature . . . . . . . . . . . . . . . . . –40ºC to +85ºC

Maximum Junction Temperature . . . . . . . . . . . . . . . . . 150ºC

Storage Temperature . . . . . . . . . . . . . . . . . . –65ºC to +150ºC

Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . . . 300ºC

*Absolute Maximum Ratings are limiting values, to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability under any of these conditions is not necessarily implied. Exposure to

absolute maximum rating conditions for extended periods may affect device

reliability.

ORDERING GUIDE

Temperature Package

Model Range Description

AD9879BS –40ºC to +85ºC 100-Lead MQFP

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD9879 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

EXPLANATION OF TEST LEVELS

I. Devices are 100% production tested at +25ºC and guaranteed

by design and characterization testing for commercial

operating temperature range (–40ºC to +85ºC).

II. Parameter is guaranteed by design and/or characterization

testing.

III. Parameter is a typical value only.

N/A Test level definition is not applicable.

THERMAL CHARACTERISTICS

Thermal Resistance

100-Lead MQFP

= 40.5ºC/W

JA

REV. 0

–5–

AD9879

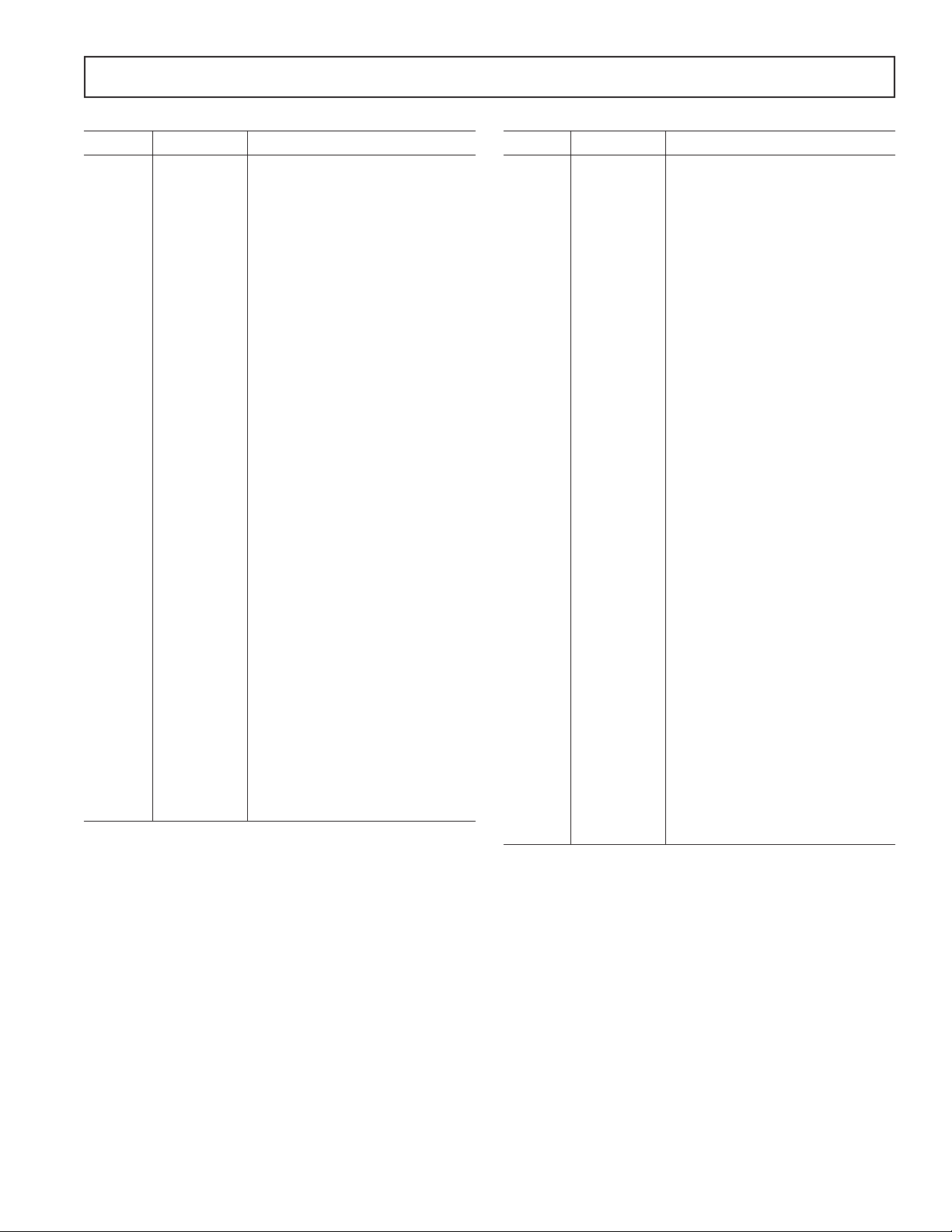

PIN CONFIGURATION

DNC

DRGND

DRVDD

IF(11)

IF(10)

IF(9)

IF(8)

IF(7)

IF(6)

IF(5)

IF(4)

IF(3)

IF(2)

IF(1)

IF(0)

RXIQ(3)

RXIQ(2)

RXIQ(1)

RXIQ(0)

RXSYNC

DRGND

DRVDD

MCLK

DVDD

DGND

TXSYNC

TXIQ(5)

TXIQ(4)

TXIQ(3)

TXIQ(2)

IF12+

AGND

VIDEO IN

99989796959493

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

33

31

32

34

DVDD

DGND

TXIQ(1)

TXIQ(0)

35

DNC

37

36

RESET

PROFILE

REFB12

AD9879

100-LEAD MQFP

38

DVDD

IF10+

AGND

AVDD

929190

TOP VIEW

39

40

41

SCLK

DGND

DGND

IF10–

89

42

CS

REFT12

AVDD

AGND

IF12–

REFT10

AVDD

AGND

8786858483

88

45

43

44

SDO

SDIO

DGNDTX

REFB10

AVDD

46

47

PWRDN

DVDDTX

Q+

AGND

82

49

48

REFIO

FSADJ

Q–

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

AGNDTX

DNC

I+

I–

DNC

DNC

DNC

AGNDIQ

AVDDIQ

DRVDD

REFCLK

DRGND

DGND -

-_OUT

FLAG1

DVDD -

CA_EN

CA_DATA

CA_CLK

DVDDOSC

OSCIN

XTAL

DGNDOSC

AGNDPLL

PLLFILT

AVDDPLL

DVDDPLL

DGNDPLL

AVDDTX

TX+

TX–

REV. 0–6–

PIN FUNCTION ASSIGNMENTS

Pin No. Mnemonic Pin Function

1, 35, DNC Do Not Connect. Pins are not

75–77, 80 bonded to die.

2, 21, 70 DRGND Pin Driver Digital Ground

3, 22, 72 DRVDD Pin Driver Digital 3.3 V Supply

4–15 IF[11:0] 12-Bit ADC Digital Output

16–19 RXIQ[3:0] Muxed I and Q ADCs Output

20 RXSYNC Sync Output, IF, I and Q ADCs

23 MCLK Master Clock Output

24, 33, 38 DVDD Digital 3.3 V Supply

25, 34, DGND Digital Ground

39, 40

26 TXSYNC Sync Input for Transmit Port

27–32 TXIQ[5:0] Digital Input for Transmit Port

36 PROFILE Profile Selection Inputs

37 RESET Chip Reset Input (Active Low)

41 SCLK SPORT Clock

42 CS SPORT Chip Select

43 SDIO SPORT Data I/O

44 SDO SPORT Data Output

45 DGNDTX Tx Path Digital Ground

46 DVDDTX Tx Path Digital 3.3 V Supply

47 PWRDN Power-Down Transmit Path

48 REFIO TxDAC Decoupling (to AGND)

49 FSADJ DAC Output Adjust (External Res.)

50 AGNDTX Tx Path Analog Ground

51, 52 TX–, TX+ Tx Path Complementary Outputs

53 AVDDTX Tx Path Analog 3.3 V Supply

54 DGNDPLL PLL Digital Ground

55 DVDDPLL PLL Digital 3.3 V Supply

AD9879

Pin No. Mnemonic Pin Function

56 AVDDPLL PLL Analog 3.3 V Supply

57 PLLFILT PLL Loop Filter Connection

58 AGNDPLL PLL Analog Ground

59 DGNDOSC Oscillator Digital Ground

60 XTAL Crystal Oscillator Inv. Output

61 OSCIN Oscillator Clock Input

62 DVDDOSC Oscillator Digital 3.3 V Supply

63 CA_CLK Serial Clock to Cable Driver

64 CA_DATA Serial Data to Cable Driver

65 CA_EN Serial Enable to Cable Drive

66 DVDD ⌺-⌬ Sigma Delta Digital 3.3 V Supply

67 FLAG1 Digital Output Flag 1

68 ⌺-⌬ _OUT Sigma-Delta DAC Output

69 DGND ⌺-⌬ Sigma-Delta Digital Ground

71 REFCLK Oscillator Clock Output

73 AVDDIQ 7-Bit ADCs Analog 3.3 V Supply

74 AGNDIQ 7-Bit ADCs Analog Ground

78, 79 I–, I+ Differential Input to I ADC

81, 82 Q–, Q+ Differential Input to Q ADC

83, 88, AGND 12-Bit ADC Analog Ground

91, 96, 99

84, 87, AVDD 12-Bit ADC Analog 3.3 V Supply

92, 95

85 REFB10 10-Bit ADC Decoupling Node

86 REFT10 10-Bit ADC Decoupling Node

89, 90 IF10–, IF10+ Differential Input to 10-Bit ADC

93 REFB12 12-Bit ADC Decoupling Node

94 REFT12 12-Bit ADC Decoupling Node

97, 98 IF12–, IF12+ Differential Input to IF ADC

100 VIDEO IN Video Clamp Input, 12-Bit ADC

REV. 0

–7–

AD9879

DEFINITIONS OF SPECIFICATIONS

Differential Nonlinearity Error (DNL, NO MISSING CODES)

An ideal converter exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Guaranteed

no missing codes to 10-bit resolution indicates that all 1024 codes,

respectively, must be present over all operating ranges.

Integral Nonlinearity Error (INL)

Linearity error refers to the deviation of each individual code

from a line drawn from negative full scale through positive full

scale. The point used as negative full scale occurs 1/2 LSB

before the first code transition. Positive full scale is defined as a

level 1 1/2 LSB beyond the last code transition. The deviation is

measured from the middle of each particular code to the true

straight line.

Phase Noise

Single-sideband phase noise power is specified relative to the carrier (dBc/Hz) at a given frequency offset (1 kHz) from the carrier.

Phase noise can be measured directly in single-tone transmit mode

with a spectrum analyzer that supports noise marker measurements. It detects the relative power between the carrier and the

offset (1 kHz) sideband noise and takes the resolution bandwidth

(rbw) into account by subtracting 10log(rbw). It also adds a

correction factor that compensates for the implementation of the

resolution bandwidth, log display, and detector characteristic.

Output Compliance Range

The range of allowable voltage at the output of a current output

DAC. Operation beyond the maximum compliance limits may

cause either output stage saturation or breakdown, resulting in

nonlinear performance.

Spurious-Free Dynamic Range (SFDR)

The difference, in dB, between the rms amplitude of the DAC

output signal (or the ADC input signal) and the peak spurious

signal over the specified bandwidth (Nyquist bandwidth unless

otherwise noted).

Pipeline Delay (Latency)

The number of clock cycles between conversion initiation and

the associated output data being made available.

Offset Error

First transition should occur for an analog value 1/2 LSB above

–FS. Offset error is defined as the deviation of the actual transition from that point.

Gain Error

The first code transition should occur at an analog value 1/2 LSB

above full scale. The last transition should occur at an analog

value 1 1/2 LSB below the nominal full scale. Gain error is the

deviation of the actual difference between the first and last code

transitions and the ideal difference between the first and last

code transitions.

Aperture Delay

The aperture delay is a measure of the sample-and-hold amplifier (SHA) performance and specifies the time delay between

the rising edge of the sampling clock input to when the input

signal is held for conversion.

Aperture Uncertainty (Jitter)

Aperture jitter is the variation in aperture delay for successive

samples and is manifested as noise on the input to the ADC.

Input Reference Noise

The rms output noise is measured using histogram techniques.

The ADC output codes’ standard deviation is calculated in LSB

and converted to an equivalent voltage. This results in a noise

figure that can directly be referred to the input of the MxFE.

Signal-To-Noise and Distortion (S/N+D, SINAD) Ratio

SINAD is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the

Nyquist frequency, including harmonics but excluding dc. The

value for SINAD is expressed in decibels.

Effective Number of Bits (ENOB)

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula:

N = (SINAD – 1.76)dB/6.02

it is possible to get a performance measurement expressed as N,

the effective number of bits. Thus, effective number of bits for a

device for sine wave inputs at a given input frequency can be

calculated directly from its measured SINAD.

Signal-To-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured input signal to

the rms sum of all other spectral components below the Nyquist

frequency, excluding harmonics and dc. The value for SNR is

expressed in decibels.

Total Harmonic Distortion (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is

expressed as a percentage or in decibels.

Power Supply Rejection

Power supply rejection specifies the converter’s maximum fullscale change when the supplies are varied from nominal to

minimum and maximum specified voltages.

Channel-To-Channel Isolation (Crosstalk)

In an ideal multichannel system, the signal in one channel will

not influence the signal level of another channel. The channelto-channel isolation specification is a measure of the change that

occurs to a grounded channel as a full-scale signal is applied to

another channel.

REV. 0–8–

Loading...

Loading...