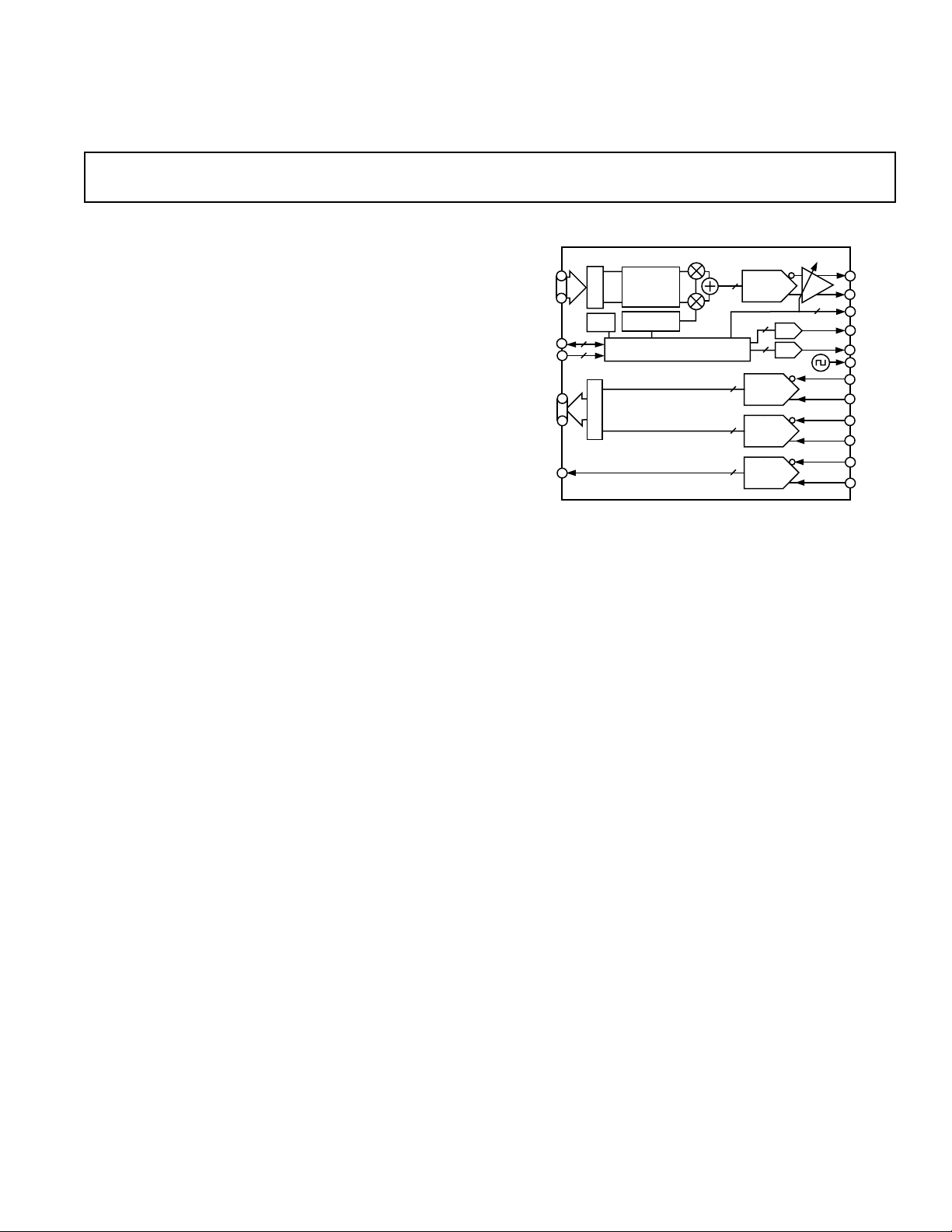

Mixed-Signal Front End

a

FEATURES

Low Cost 3.3 V CMOS MxFE™ for

MCNS-DOCSIS, DVB-, DAVIC-Compliant

Set-Top Box and Cable Modem Applications

232 MHz Quadrature Digital Upconverter

12-Bit Direct IF DAC (TxDAC+

Up to 65 MHz Carrier Frequency DDS

Programmable Sampling Clock Rates

Selectable Interpolation Filter

Analog Tx Output Level Adjust

12-Bit, 33 MSPS Direct IF ADC

Dual 8-Bit, 16.5 MSPS Sampling IQ ADCs

Two 12-Bit ⌺-⌬ Auxiliary DACs

Direct Interface to AD8321/AD8325 or AD8322/AD8327

PGA Cable Driver

APPLICATIONS

Cable Modems

Set-Top Boxes

Wireless Modems

®

)

Tx DATA

SPORT

PROFILE

RxIQ DATA

RxIF DATA

Set-Top Box, Cable Modem

AD9877

FUNCTIONAL BLOCK DIAGRAM

COS

SIN

12

DAC

12

⌺-⌬

12

⌺-⌬

8

ADC

8

ADC

12

ADC

Tx

3

CA

SDELTA0

SDELTA1

OSCOUT

I IN

Q IN

IF IN

Tx

PLL

4

2

Rx

AD9877

INTER-

POLATOR

FILTER

DDS

CONTROL FUNCTIONS

GENERAL DESCRIPTION

The AD9877 is a single-supply cable modem/set-top box

mixed-signal front end. The device contains a transmit path

interpolation filter, a complete quadrature digital upconverter,

and a transmit DAC. The receive path contains a 12-bit ADC

and dual 8-bit ADCs. All internally required clocks and an output

system clock are generated by the PLL from a single crystal or

clock input.

The transmit path interpolation filter provides upsampling factors

of 12⫻ or 16⫻ with an output signal bandwidth as high as 5.8 MHz.

Carrier frequencies up to 65 MHz with 26 bits of frequency tuning

resolution can be generated by the direct digital synthesizer (DDS).

The transmit DAC resolution is 12 bits and can run at sampling

rates as high as 232 MSPS. Analog output scaling from 0 dB to

7.5 dB in 0.5 dB steps is available to preserve SNR when reduced

output levels are required.

The 12-bit ADC has excellent undersampling performance,

allowing it to deliver better than 10 ENOBs with IF inputs up to

70 MHz. The 12-bit IF ADC can sample at a rate up to 33 MHz,

allowing it to process wideband signal inputs.

Two programmable sigma-delta DACs are available and can be used

to control external components, such as variable gain amplifiers

(VGAs) or voltage-controlled tuners.

The AD9877 integrates a CA port that enables a host processor

to control the AD8321/AD8325 or AD8322/AD8327 programmable gain amplifier (PGA) cable drivers via the MxFE SPORT.

The AD9877 is available in a 100-lead MQFP package. It offers

enhanced receive path undersampling performance and lower cost,

compared to the pin-compatible AD9873. The AD9877 is specified

over the extended industrial (–40

o

C to +85oC) temperature range.

MxFE is a trademark of Analog Devices, Inc.

TxDAC+ is a registered trademark of Analog Devices, Inc.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

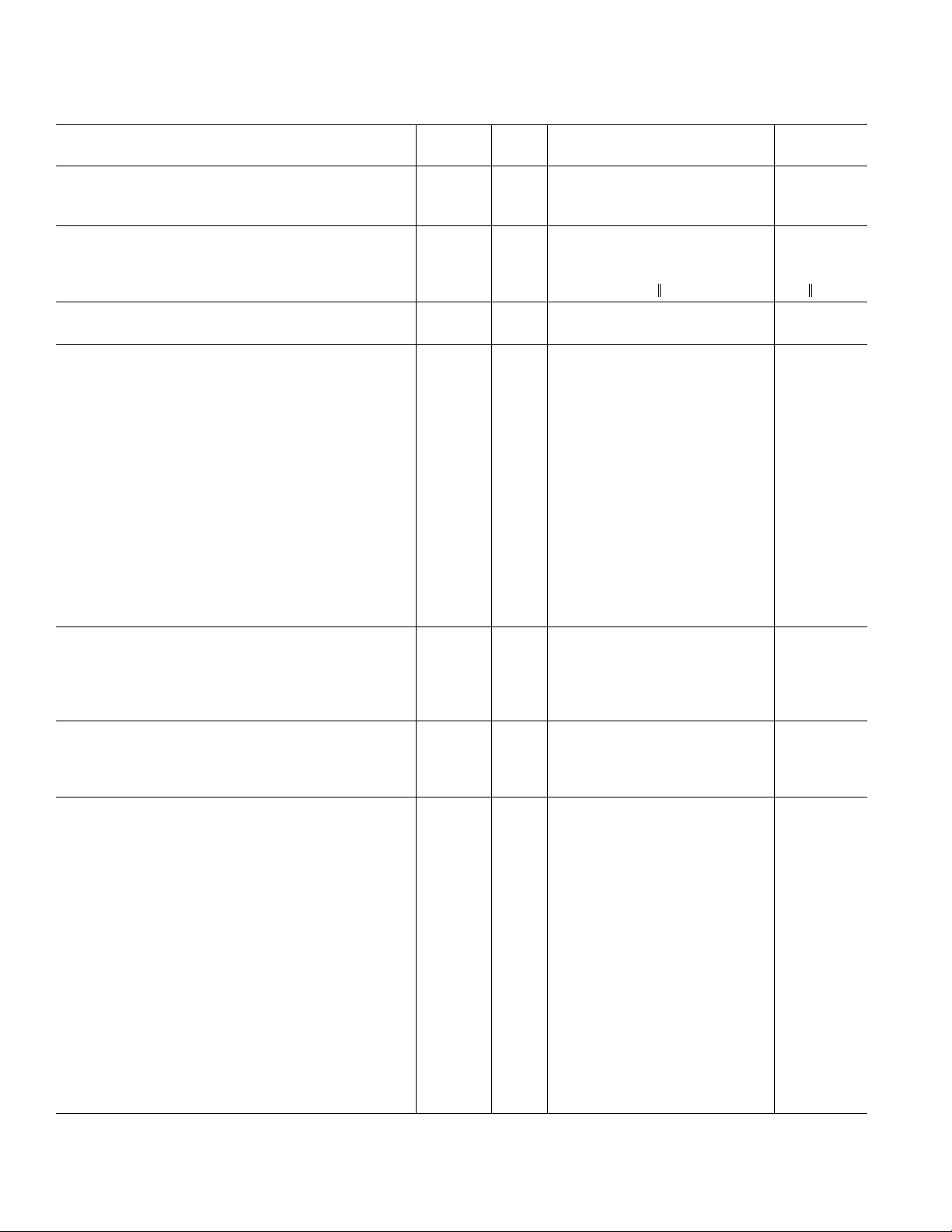

AD9877–SPECIFICATIONS

f

= 54 MHz (M = 8 and N = 4). ADC sample frequencies derived from PLL (f

MCLK

(VAS = 3.3 V ⴞ 5%, V

= 3.3 V ⴞ 10%, f

DS

), R

MCLK

= 4.02 k⍀, max. fine gain, 75 ⍀ DAC load.)

SET

= 27 MHz, f

OSCIN

SYSCLK

= 216 MHz,

Test

Parameter Temp Level Min Typ Max Unit

SYSTEM CLOCK DAC SAMPLING, f

SYSCLK

Frequency Range (N = 4) Full II 232 MHz

Frequency Range (N = 3) Full II 177 MHz

OSCIN and XTAL CHARACTERISTICS

Frequency Range Full II 3 33 MHz

Duty Cycle 25ºC II 35 50 65 %

Input Impedance 25ºC III 100 3 MΩ pF

MCLK JITTER

Cycle to Cycle (f

derived from PLL) 25ºC III 6 ps rms

MCLK

Tx DAC CHARACTERISTICS

Resolution N/A N/A 12 Bits

Full-Scale Output Current Full II 4 10 20 mA

Gain Error (using internal reference) Full II –2.5 –1 +2.5 %FS

Offset Error 25ºC III ±1.0 %FS

Reference Voltage (REFIO Level) 25ºC III 1.23 V

Differential Nonlinearity (DNL) 25ºC III ±2.5 LSB

Integral Nonlinearity (INL) 25ºC III ±8 LSB

Output Capacitance 25ºC III 5 pF

Phase Noise @ 1 kHz Offset, 42 MHz Carrier 25ºC III –110 dBc/Hz

Output Voltage Compliance Range Full II –0.5 +1.5 V

Wideband SFDR

5 MHz Analog Out, I

65 MHz Analog Out,

= 10 mA Full I 48 55 dBc

OUT

I

= 10 mA Full I 48 51 dBc

OUT

Narrow-Band SFDR (±1 MHz Window):

65 MHz Analog Out, I

= 10 mA Full I 53 69 dBc

OUT

Tx MODULATOR CHARACTERISTICS

I/Q Offset Full II 50 55 dB

Pass-Band Amplitude Ripple (f < f

Pass-Band Amplitude Ripple (f < f

Stop-Band Response (f > f

× 3/4) Full II –63 dB

IQCLK

/8) Full II ±0.1 dB

IQCLK

/4) Full II ±0.5 dB

IQCLK

Tx GAIN CONTROL

Gain Step Size 25ºC III 0.5 dB

Gain Step Error 25ºC III 0.05 dB

Settling Time, 1% (Full-Scale Step) 25ºC III 1.8 µs

8-BIT ADC CHARACTERISTICS

Resolution N/A N/A 8 Bits

Conversion Rate Full II 16.5 MHz

Pipeline Delay N/A N/A 3.5 ADC Cycles

Offset Matching between I and Q ADCs ±8.0 LSBs

Gain Matching between I and Q ADCs ±2.0 LSBs

Analog Input

Input Voltage Range Full II 1 Vppd

Differential Input Impedance 25ºC III 42kΩpF

Full Power Bandwidth 25ºC III 90 MHz

Input Referred Noise 25ºC III 600 µV

Dynamic Performance (A

= –0.5 dBFS, f = 5 MHz)

IN

Signal-to-Noise and Distortion (SINAD) Full I 40.8 47.3 dB

Effective Number of Bits (ENOB) Full I 6.5 7.6 Bits

Total Harmonic Distortion (THD) Full I –60.1 –50.0 dB

Spurious-Free Dynamic Range (SFDR) Full I 52.0 63.0 dB

Reference Voltage Error

REFT8-REFB8 (0.5 V) Full I –100 ±10 +100 mV

–2–

REV. A

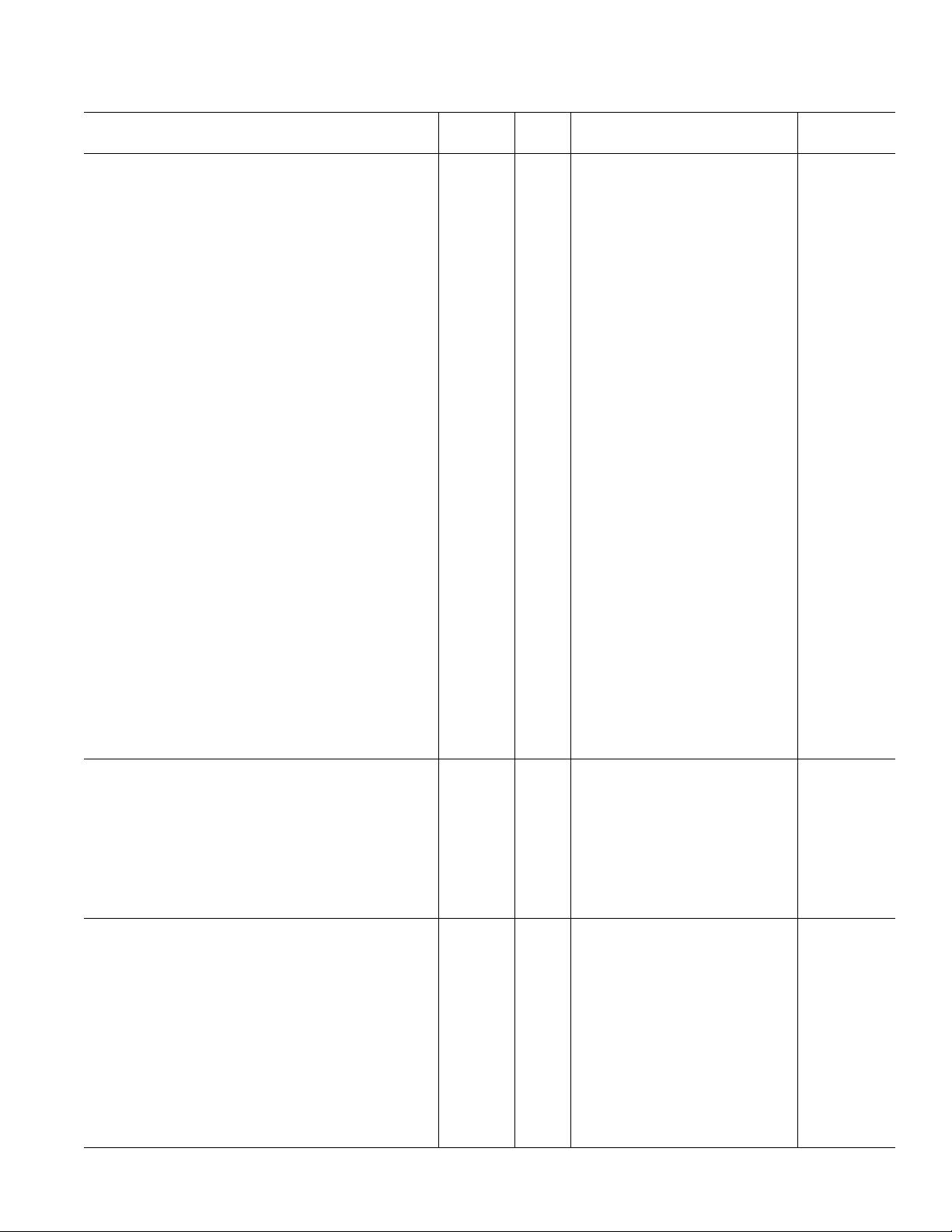

AD9877

Test

Parameter Temp Level Min Typ Max Unit

12-BIT ADC CHARACTERISTICS

Resolution N/A N/A 12 Bits

Conversion Rate Full II 33 MHz

Pipeline Delay N/A N/A 5.5 ADC Cycles

Analog Input

Input Voltage Range Full III 2 Vppd

Differential Input Impedance 25ºC III 4.2 kΩ, pF

Aperture Delay 25ºC III 2.0 ns

Aperture Uncertainty (Jitter) 25ºC III 1.2 ps rms

Full Power Bandwidth 25ºC III 85 MHz

Input Referred Noise 25ºC III 75 µV

Reference Voltage Error

REFT12-REFB12 (1 V) Full I –200 ±16 +200 mV

Dynamic Performance (A

ADC Sample Clock = OSCIN

Signal-to-Noise and Distortion (SINAD) Full I 63.2 65.9 dB

Effective Number of Bits (ENOBs) Full I 10.2 10.7 Bits

Signal-to-Noise Ratio (SNR) Full I 63.7 66.2 dB

Total Harmonic Distortion (THD) Full I –79.1 –68.3 dB

Spurious-Free Dynamic Range (SFDR) Full I 72.5 79.3 dB

ADC Sample Clock = PLL

Signal-to-Noise and Distortion (SINAD) Full II 62.0 64.6 dB

Effective Number of Bits (ENOBs) Full II 10.0 10.4 Bits

Signal-to-Noise Ratio (SNR) Full II 62.5 64.8 dB

Total Harmonic Distortion (THD) Full II –78 –67.8 dB

Spurious-Free Dynamic Range (SFDR) Full II 72.5 79.3 dB

Dynamic Performance (A

ADC Sample Clock = OSCIN

Signal-to-Noise and Distortion (SINAD) Full II 61.1 63.1 dB

Effective Number of Bits (ENOB) Full II 9.9 10.2 Bits

Signal-to-Noise Ratio (SNR) Full II 61.5 63.3 dB

Total Harmonic Distortion (THD) Full II –77 –67.9 dB

Spurious-Free Dynamic Range (SFDR) Full II 69.9 79.6 dB

Differential Phase 25ºC III <0.1 Degrees

Differential Gain 25ºC III <1 LSB

CHANNEL-TO-CHANNEL ISOLATION

Tx DAC-to-ADC Isolation

(5 MHz Analog Output)

Isolation between Tx and 8-Bit ADCs 25ºC III 80 dB

Isolation between Tx and 12-Bit ADCs 25ºC III 90 dB

ADC-to-ADC Isolation

= –0.5 dBFS, f = 5 MHz)

(A

IN

Isolation between I/Q in and IF12 25ºC III 70 dB

Isolation between Q and I Inputs 25ºC III 65 dB

TIMING CHARACTERISTICS (10 pF Load)

Wake-Up Time N/A N/A 200 t

Minimum RESET Pulsewidth Low (t

Digital Output Rise/Fall Time Full II 2.8 4 ns

Tx/Rx Interface

MCLK Frequency (f

TxSYNC/TxIQ Setup Time (t

TxSYNC/TxIQ Hold Time (t

MCLK Rising Edge to RxSYNC/RxIQ/IF Valid

Delay (t

) Full II 0 1.0 ns

MD

OSCOUT Rising or Falling Edge to RxSYNC/

RxIQ/IF Valid Delay (t

OSCOUT Edge to MCLK Falling Edge (tEE) Full II –1.0 +1.0 ns

= –0.5 dBFS, f = 5 MHz)

IN

= –0.5 dBFS, f = 50 MHz)

IN

) N/A N/A 5 t

RL

) Full II 66 MHz

MCLK

OD

) Full II 3 ns

SU

) Full II 3 ns

HD

) Full II T

/4 – 2.0 T

OSC

OSC

/4 + 3.0 ns

MCLK

MCLK

Cycles

Cycles

REV. A

–3–

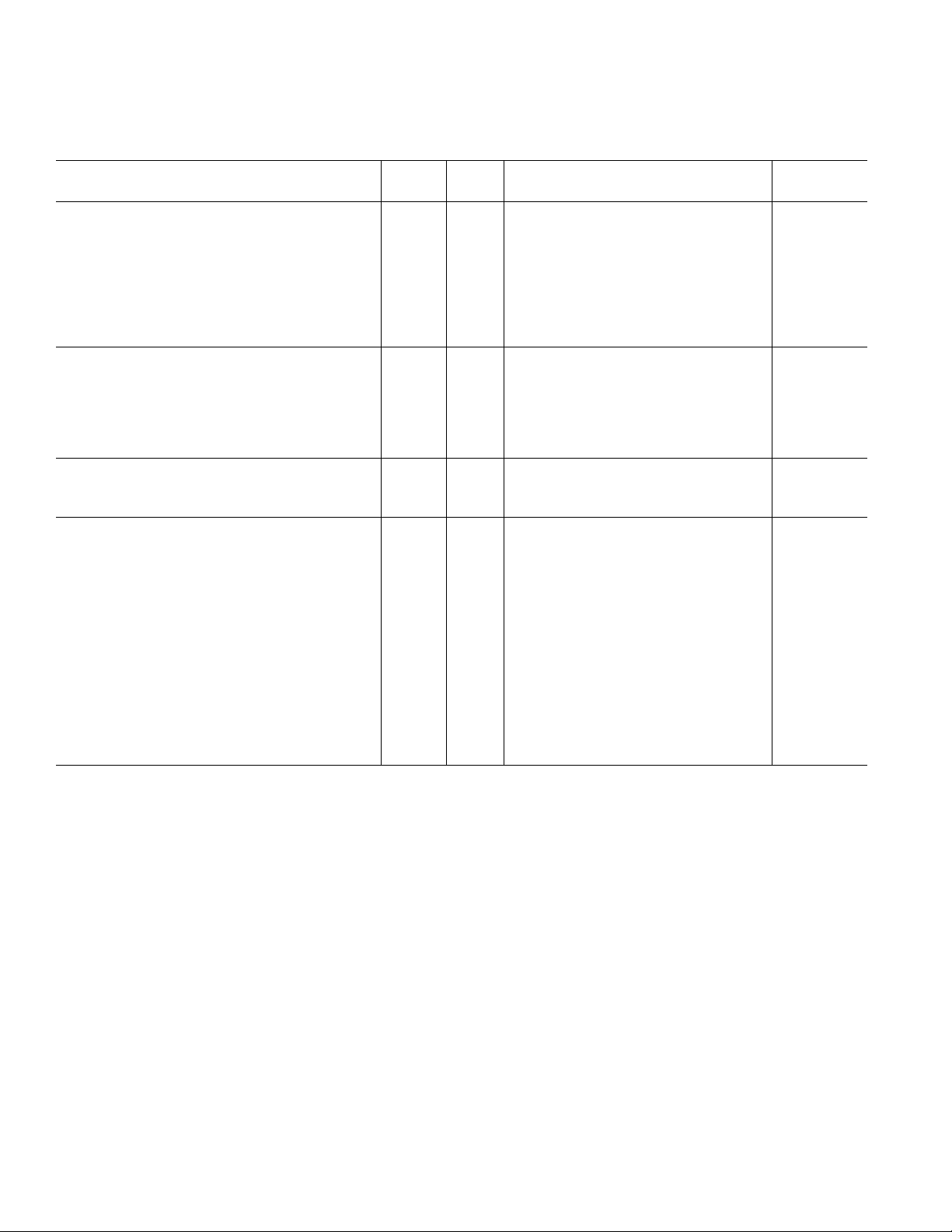

AD9877

SPECIFICATIONS

(continued)

Test

Parameter Temp Level Min Typ Max Unit

Serial Control Bus (continued)

Maximum SCLK Frequency (f

Minimum Clock Pulsewidth High (t

Minimum Clock Pulsewidth Low (t

) Full II 15 MHz

SCLK

) Full II 30 ns

PWH

) Full II 30 ns

PWL

Maximum Clock Rise/Fall Time Full II 1 µs

Minimum Data/Chip-Select Setup Time (t

Minimum Data Hold Time (t

) Full II 0 ns

DH

) Full II 25 ns

DS

Maximum Data Valid Time (tDV) Full II 30 ns

CMOS LOGIC INPUTS

Logic “1” Voltage 25ºC II DRVDD – 0.7 V

Logic “0” Voltage 25ºC II 0.4 V

Logic “1” Current 25ºC II 12 µA

Logic “0” Current 25ºC II 12 µA

Input Capacitance 25ºC III 3 pF

CMOS LOGIC OUTPUTS (1 mA Load)

Logic “1” Voltage 25ºC II DRVDD – 0.6 V

Logic “0” Voltage 25ºC II 0.4 V

POWER SUPPLY

Supply Current, IS (Full Operation) 25oCII 313 355 mA

Analog Supply Current I

Digital Supply Current I

Supply Current, I

S

AS

DS

25ºC III 85 mA

25ºC III 228 mA

Standby (PWRDN Pin Active) 25ºC II 104 113 mA

Full Power-Down (Register 02h = 0xF9) 25ºC III 10 mA

Power-Down Tx Path (Register 2 = 0x20) 25ºC III 60 mA

Power-Down Rx Paths (Register 2 = 0x19) 25ºC III 265 mA

Reset (RESET Pin Active) 25ºC III 85 mA

Power Supply Rejection (Differential Signal)

Tx DAC 25ºC III <0.25 % FS

8-Bit ADC 25ºC III <0.004 % FS

12-Bit ADC 25ºC III <0.0004 % FS

Specifications subject to change without notice.

–4–

REV. A

AD9877

ABSOLUTE MAXIMUM RATINGS

Power Supply (V

AVDD

, V

DVDD

, V

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 5 mA

Digital Inputs . . . . . . . . . . . . . . . –0.3 V to DRVDD + 0.3 V

Analog Inputs . . . . . . . . . . . . . . . . . –0.3 V to AVDD + 0.3 V

Operating Temperature . . . . . . . . . . . . . . . . . –40ºC to +85ºC

Maximum Junction Temperature . . . . . . . . . . . . . . . . 150ºC

Storage Temperature . . . . . . . . . . . . . . . . . . –65ºC to +150ºC

Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . . 300ºC

*Absolute maximum ratings are limiting values, to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability under any of these conditions is not necessarily implied. Exposure to

absolute maximum rating conditions for extended periods of time may affect

device reliability.

*

) . . . . . . . . . . . . 3.9 V

DRVDD

EXPLANATION OF TEST LEVELS

I Devices are 100% production tested at 25ºC and guaranteed

by design and characterization testing for industrial operating

temperature range (–40ºC to +85ºC).

II Parameter is guaranteed by design and/or characterization

testing.

III Parameter is a typical value only.

N/A Test level definition is not applicable.

THERMAL CHARACTERISTICS

Thermal Resistance

100-Lead MQFP

= 40.5ºC/W

JA

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD9877ABS –40ºC to +85ºC 100-MQFP S-100C

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD9877 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. A

–5–

AD9877

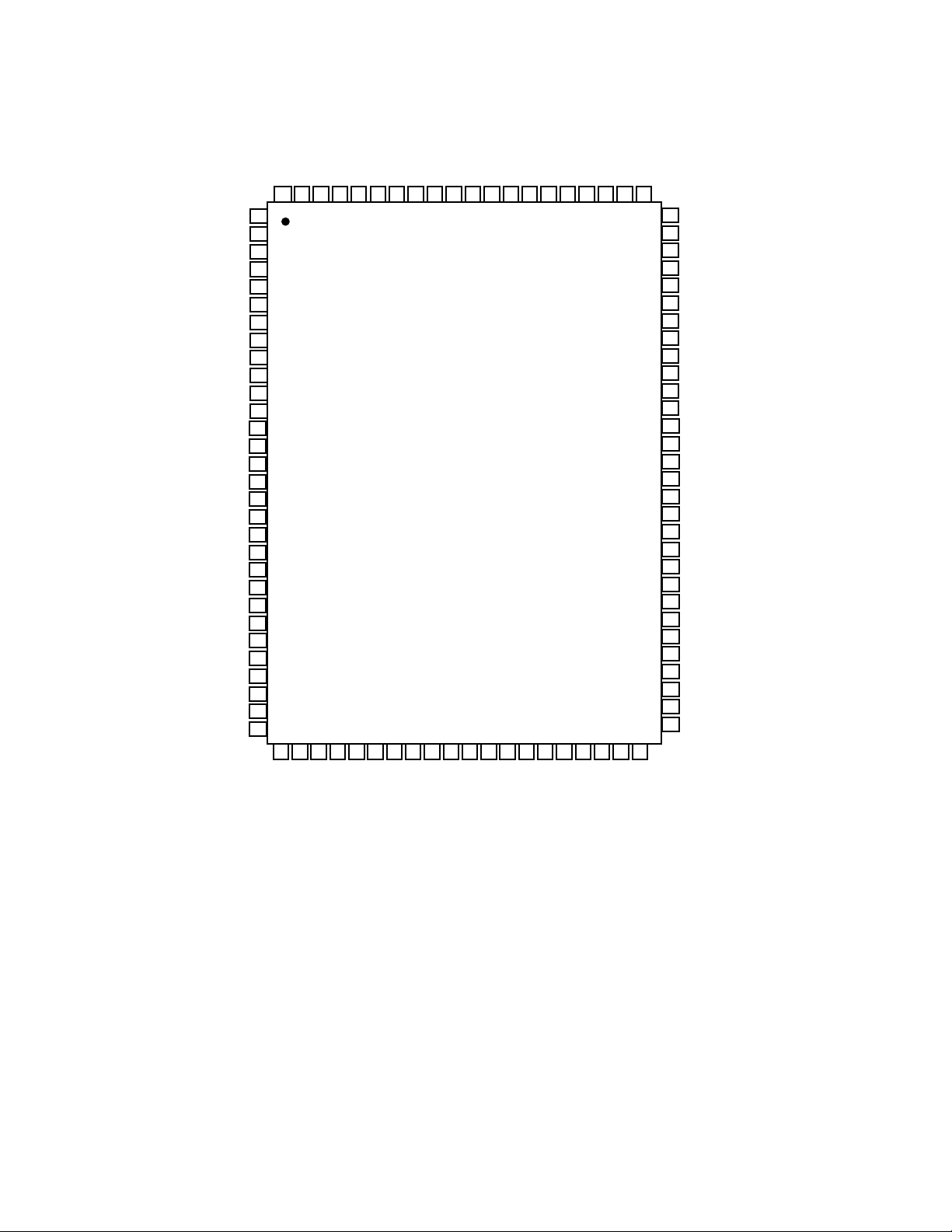

AVDD

DRGND

DRVDD

IF(11)

IF(10)

IF(9)

IF(8)

IF(7)

IF(6)

IF(5)

IF(4)

IF(3)

IF(2)

IF(1)

IF(0)

RxIQ(3)

RxIQ(2)

RxIQ(1)

RxIQ(0)

RxSYNC

DRGND

DRVDD

MCLK

DVDD

DGND

TxSYNC

TxIQ(5)

TxIQ(4)

TxIQ(3)

TxIQ(2)

IF12–

IF12+

AGND

NC

1009998

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

313233 34 353637 38 39

TxIQ(1)

TxIQ(0)

97 96

DVDD

AGND

95 94

DGND

PROFILE(1)

PIN CONFIGURATION

REFB12

REFT12

AVDD

RESET

PROFILE(0)

AVDD

93

92

91 90

AD9877

TOP VIEW

100-Lead MQFP

40

DVDD

DGND

AGND

41 42

DGND

NC

SCLK

AGND

NC

89

87

88

43

44 45

CS

SDIO

AVDD

SDO

REFT8

86

85

46 47

DGNDTx

REFB8

AVDD

848382

PWRDN

DVDDTx

48

AGND

49

REFIO

Q IN+

81

50

FSADJ

Q IN–

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

AGNDTx

AGNDIQ

I IN+

I IN–

AGNDIQ

NC

NC

AGNDIQ

AVDDIQ

DRVDD

OSCOUT

DRGND

DGNDSD

SDELTA0

SDELTA1

DVDDSD

CA_EN

CA_DATA

CA_CLK

DVDDOSC

OSCIN

XTAL

DGNDOSC

AGNDPLL

PLLFILT

AVDDPLL

DVDDPLL

DGNDPLL

AVDDTx

Tx+

Tx–

NC = NO CONNECT

–6–

REV. A

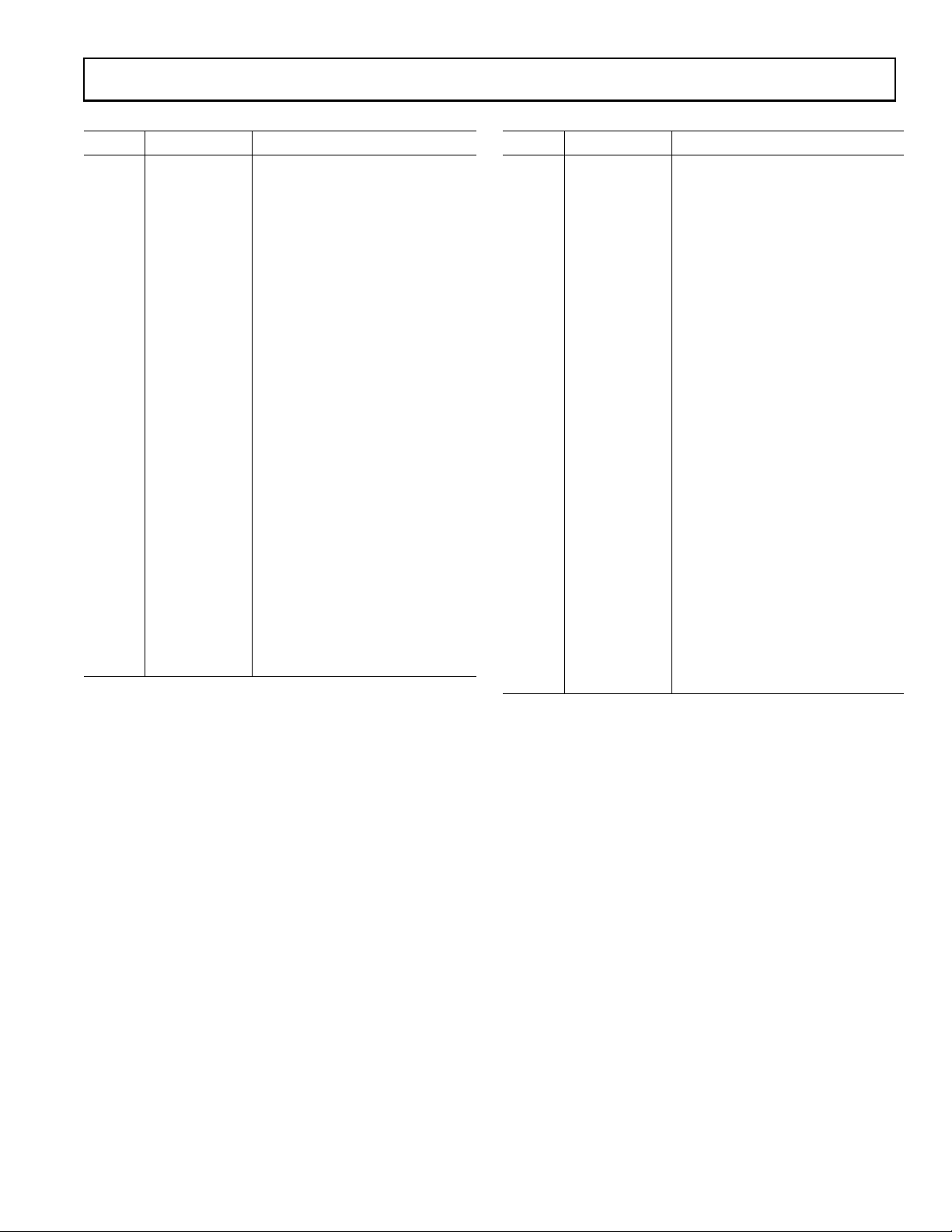

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Pin Function

1, 84, 87, AVDD 12-Bit ADC Analog 3.3 V Supply

92, 95

2, 21, 70 DRGND Pin Driver Digital Ground

3, 22, 72 DRVDD Pin Driver Digital 3.3 V Supply

25, 34, DGND Digital Ground

39, 40

24, 33, DVDD Digital 3.3 V Supply

38

45 DGNDTx Tx Path Digital Ground

46 DVDDTx Tx Path Digital 3.3 V Supply

50 AGNDTx Tx Path Analog Ground

53 AVDDTx Tx Path Analog 3.3 V Supply

54 DGNDPLL PLL Digital Ground

55 DVDDPLL PLL Digital 3.3 V Supply

56 AVDDPLL PLL Analog 3.3 V Supply

58 AGNDPLL PLL Analog Ground

59 DGNDOSC Oscillator Digital Ground

62 DVDDOSC Oscillator Digital 3.3 V Supply

66 DVDDSD Sigma-Delta Digital 3.3 V Supply

69 DGNDSD Sigma-Delta Digital Ground

73 AVDDIQ 8-Bit ADC Analog 3.3 V Supply

74, 77, AGNDIQ 8-Bit ADC Analog Ground

80

83, 88, AGND 12-Bit ADC Analog Ground

91, 96,

99

4:15 IF[11:0] 12-Bit ADC Digital Output

16:19 RxIQ[3:0] Muxed I and Q ADC Output

20 RxSYNC Sync Output, IF, I, and Q ADCs

23 MCLK Master Clock Output

AD9877

Pin No. Mnemonic Pin Function

26 TxSYNC Sync Input for Transmit Port

27:32 TxIQ[5:0] Digital Input for Transmit Port

35, 36 PROFILE[1:0] Profile Selection Inputs

37 RESET Chip Reset Input

41 SCLK SPORT Clock

42 CS SPORT Chip Select

43 SDIO SPORT Data I/O

44 SDO SPORT Data Output

47 PWRDN Power-Down Transmit Path

48 REFIO TxDAC Decoupling (to AGND)

49 FSADJ DAC Output Adjust (External Res.)

51, 52 Tx–, Tx+ Tx Path Complementary Outputs

57 PLLFILT PLL Loop Filter Connection

60 XTAL Crystal Oscillator Inv. Output

61 OSCIN Oscillator Clock Input

63 CA_CLK Serial Clock to Cable Driver

64 CA_DATA Serial Data to Cable Driver

65 CA_EN Serial Enable to Cable Driver

67 SDELTA1 Sigma-Delta Output Stream 1

68 SDELTA0 Sigma-Delta Output Stream 0

71 OSCOUT Oscillator Clock Output

75, 76 NC No Connect (Leave Floating)

78, 79 I IN–, I IN+ Differential Input to I ADC

81, 82 Q IN–, Q IN+ Differential Input to Q ADC

85 REFB8 8-Bit ADC Decoupling Node

86 REFT8 8-Bit ADC Decoupling Node

89, 90 NC No Connect (Leave Floating)

93 REFB12 12-Bit ADC Decoupling Node

94 REFT12 12-Bit ADC Decoupling Node

97, 98 IF12–, IF12+ Differential Input to IF ADC

100 NC No Connect (Leave Floating)

REV. A

–7–

AD9877

DEFINITIONS OF SPECIFICATIONS

APERTURE DELAY

The aperture delay is a measure of the sample-and-hold amplifier (SHA) performance and specifies the time delay between the

rising edge of the sampling clock input to when the input signal

is held for conversion.

APERTURE UNCERTAINTY (JITTER)

Aperture jitter is the variation in aperture delay for successive

samples and is manifested as noise on the input to the ADC.

CHANNEL-TO-CHANNEL ISOLATION (CROSSTALK)

In an ideal multichannel system, the signal in one channel

will not influence the signal level of another channel. The

channel-to-channel isolation specification is a measure of the

change that occurs to a grounded channel as a full-scale signal is

applied to another channel.

DIFFERENTIAL NONLINEARITY ERROR (DNL, NO MISSING CODES)

An ideal converter exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Guaranteed no

missing codes to 10-bit resolution indicates that all 1,024 codes,

respectively, must be present over all operating ranges.

EFFECTIVE NUMBER OF BITS (ENOB)

For a sine wave, SINAD can be expressed in terms of the number

of bits. Using the following formula:

N SINAD dB=−

()

It is possible to get a measure of performance expressed as N,

the effective number of bits. Thus, the effective number of bits

for a device for sine wave inputs at a given input frequency can

be calculated directly from its measured SINAD.

GAIN ERROR

The first code transition should occur at an analog value one-half

LSB above full scale. The last transition should occur for an

analog value 1 1/2 LSB below the nominal full scale. Gain error

is the deviation of the actual difference between the first and last

code transitions and the ideal difference between the first and

last code transitions.

INPUT REFERRED NOISE

The rms output noise is measured using histogram techniques.

The ADC output code’s standard deviation is calculated in LSB

and converted to an equivalent voltage. This results in a noise

figure that can be directly referred to the input of the MxFE.

INTEGRAL NONLINEARITY ERROR (INL)

Linearity error refers to the deviation of each individual code

from a line drawn from the negative full scale through the positive

full scale. The point used as the negative full scale occurs

1/2 LSB before the first code transition. The positive full scale is

defined as a level 1 1/2 LSB beyond the last code transition. The

deviation is measured from the middle of each particular code to

the true straight line.

176 602..

OFFSET ERROR

First transition should occur for an analog value 1/2 LSB above

–FS. Offset error is defined as the deviation of the actual transition from that point.

OUTPUT COMPLIANCE RANGE

The range of allowable voltage at the output of a current-output

DAC. Operation beyond the maximum compliance limits may

cause either output stage saturation or breakdown, resulting in

nonlinear performance.

PHASE NOISE

Single sideband phase noise power is specified relative to the

carrier (dBc/Hz) at a given frequency offset (1 kHz) from the

carrier. Phase noise can be measured directly in single-tone

transmit mode with a spectrum analyzer that supports noise

marker measurements. It detects the relative power between the

carrier and the offset (1 kHz) sideband noise and takes the resolution bandwidth (rbw) into account by subtracting 10 log(rbw).

It also adds a correction factor that compensates for the implementation of the resolution bandwidth, log display, and detector

characteristic.

PIPELINE DELAY (LATENCY)

The number of clock cycles between conversion initiation and

the associated output data being made available.

POWER SUPPLY REJECTION

Power supply rejection specifies the converter’s maximum

full-scale change when the supplies are varied from nominal

to minimum and maximum specified voltages.

SIGNAL-TO-NOISE AND DISTORTION (SINAD) RATIO

SINAD is the ratio of the rms value of the measured input signal

to the rms sum of all other spectral components below the

Nyquist frequency, including harmonics but excluding dc. The

value for SINAD is expressed in decibels.

SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the measured input signal to

the rms sum of all other spectral components below the Nyquist

frequency, excluding harmonics and dc. The value for SNR is

expressed in decibels.

SPURIOUS-FREE DYNAMIC RANGE (SFDR)

The difference, in dB, between the rms amplitude of the DAC’s

output signal (or ADC’s input signal) and the peak spurious

signal over the specified bandwidth (Nyquist bandwidth unless

otherwise noted).

TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic

components to the rms value of the measured input signal and is

expressed as a percentage or in decibels.

–8–

REV. A

AD9877

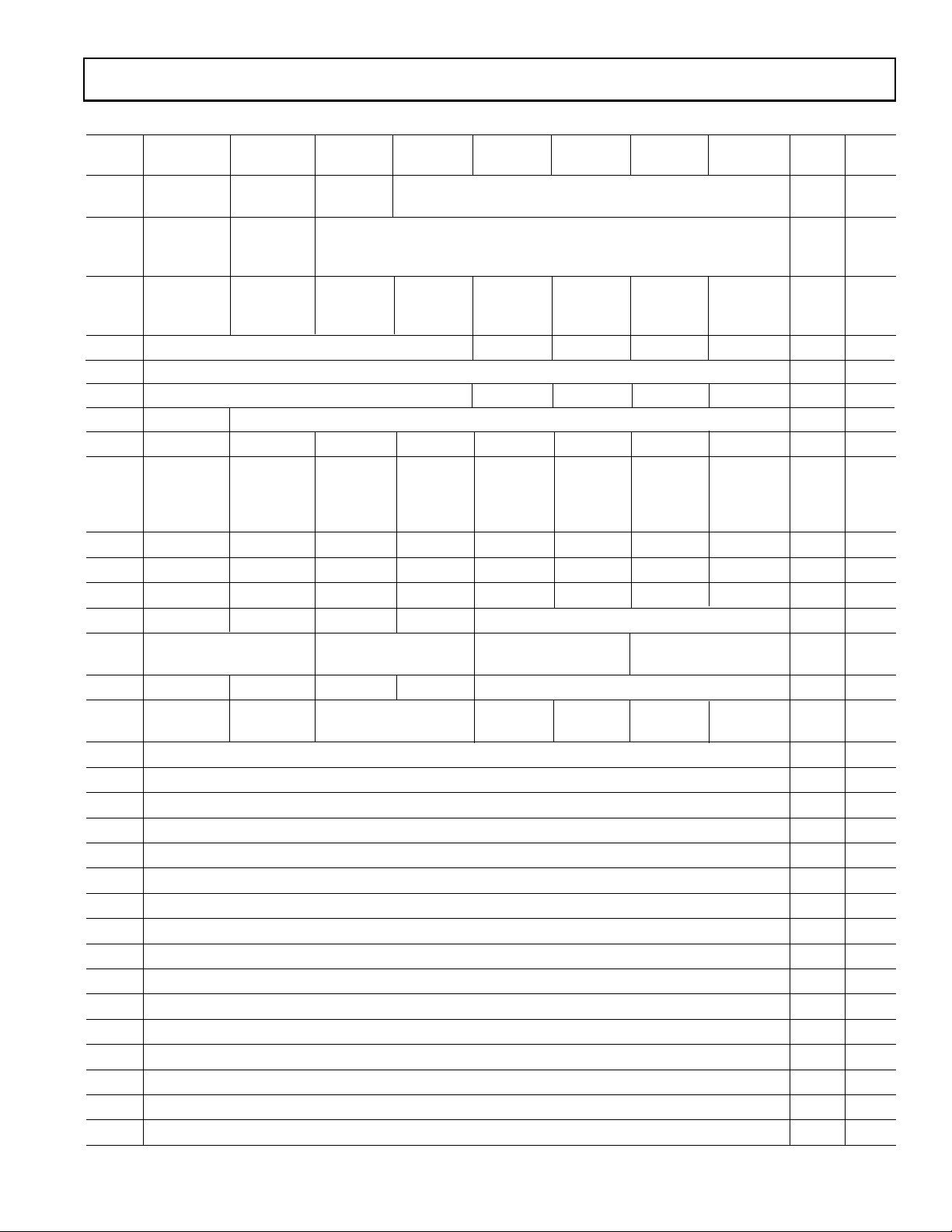

Table I. Register Map*

Address Default

(Hex) Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 (Hex) Type

00 SDIO LSB First RESET OSCIN Multiplier M [4] 08 rw

Bidirectional

01 PLL Lock SYSCLK MCLK Divider R [5:0] 00 rw

Detect Divider N = 3

(N = 4 Default)

02 Power-Down Power-Down Power-Down Power-Down Power-Down Power-Down 00 rw

PLL DAC Tx Digital Tx 12-Bit ADC 12-Bit ADC 0 0 8-Bit ADC

Reference

03 Sigma-Delta Output [0] Control Word [3:0] LSB 0 0 0

04 Flag [0] Sigma-Delta Output 0 Control Word [11:4] MSB 00 rw ⌺-⌬

05 Sigma-Delta Output [0] Control Word [3:0] LSB 0 0 0

06 Flag [1] Sigma-Delta Output 1 Control Word [11:4] MSB 00 rw ⌺-⌬

07 0000000000rw Tx

08 ADC Clock 0 0 Power-Down 0 0 0 0 80 rw ADC

Select RxSYNC and

8-Bit ADC

CLOCK

09 0000000000rw

0A 0000000000r

0B 0000000000rw

0C 0 0 0 1 Version [3:0] 10 r

0D Tx Frequency Tuning Tx Frequency Tuning Tx Frequency Tuning Tx Frequency Tuning 00 rw Tx

Word Profile 3 LSBs [1:0] Word Profile 2 LSBs [1:0] Word Profile 1 LSB [1:0] Word Profile 3 LSBs [1:0]

0E 0 0 0 0 DAC Gain Control [3:0] 00 rw Tx

0F 0 0 Profile Select [1:0] CA Interface 0 Spectral Single-Tone 00 rw Tx

Mode Select Inversion Tx Tx Mode

10 Tx Frequency Turning Word Profile 0 [9:2] 00 rw Tx

11 Tx Frequency Turning Word Profile 0 [17:10] 00 rw Tx

12 Tx Frequency Turning Word Profile 0 [25:18] 00 rw Tx

13 CA Interface Transmit Word Control Profile 0 [7:4] DAC Gain Control Profile 0 [3:0] 00 rw Tx

14 Tx Frequency Turning Word Profile 1 [9:2] 00 rw Tx

15 Tx Frequency Turning Word Profile 1 [9:2] 00 rw Tx

16 Tx Frequency Turning Word Profile 1 [9:2] 00 rw Tx

17 CA Interface Transmit Word Control Profile 1 [7:4] DAC Gain Control Profile 1 [3:0] 00 rw Tx

18 Tx Frequency Turning Word Profile 2 [9:2] 00 rw Tx

19 Tx Frequency Turning Word Profile 2 [9:2] 00 rw Tx

1A Tx Frequency Turning Word Profile 2 [9:2] 00 rw Tx

1B CA Interface Transmit Word Control Profile 2 [7:4] DAC Gain Control Profile 2 [3:0] 00 rw Tx

1C Tx Frequency Turning Word Profile 3 [9:2] 00 rw Tx

1D Tx Frequency Turning Word Profile 3 [9:2] 00 rw Tx

1E Tx Frequency Turning Word Profile 3 [9:2] 00 rw Tx

1F CA Interface Transmit Word Control Profile 3 [7:4] DAC Gain Control Profile 3 [3:0] 00 rw Tx

*Register bits denoted with “0” must be programmed with a “0” every time that register is written.

Flag [0] Enable

Flag [1] Enable

00 rw ⌺-⌬

00 rw ⌺-⌬

REV. A

–9–

3

AD9877

REGISTER BIT DEFINITIONS

REGISTER 00—Initialization

Bits 0 to 4: OSCIN Multiplier

This register field is used to program the on-chip multiplier (PLL)

that generates the chip’s high frequency system clock f

For example, to multiply the external crystal clock f

SYSCLK

OSCIN

.

by

16 decimals, program Register 0, Bits 4:0 as 0x10. The default

value of M is 0x08. Valid entries range from M = 1–31. When M

is chosen equal to 1, the PLL is disabled. All internal clocks are

derived directly from OSCIN.

The PLL requires 200 MCLK cycles to regain frequency lock after

a change in M, the clock multiplier value. After the recapture time of

the PLL, the frequency of f

SYSCLK

is stable.

For timing integrity, certain restrictions on the values of M and N

apply when both AD9877 transmit and receive paths are used.

The supported modes are:

ADC Clock Select N M

1, f

OSCIN

36

48

0, f

(PLL Derived) 3 12

MCLK

416

Bit 5: RESET

Writing a 1 to this bit resets the registers to their default values

and restarts the chip. The RESET Bit always reads back 0. The

bits in Register 0 are not affected by this software reset. However,

a low level at the RESET pin would force all registers, including

all bits in Register 0, to their default state.

Bit 6: LSB First

Active high indicates SPI serial port access of instruction byte

and data registers is least significant bit (LSB) first. Default low

indicates most significant bit (MSB) first format.

Bit 7: SDIO Bidirectional

Active high configures serial port as a three-signal port with the

SDIO pin used as a bidirectional input/output pin. Default low

indicates the serial port uses four signals with SDIO configured

as an input and SDO configured as an output.

REGISTER 01—Clock Configuration

Bits 0 to 5: MCLK Divider

This register determines the output clock on the OSCOUT pin.

At default zero (R = 0), OSCOUT provides a buffered version of

the OSCIN clock signal for other chips.

The register can also be used to divide the chip’s master clock,

f

, by R, where R is an integer between 2 and 63. The generated

MCLK

reference clock on the OSCOUT pin can be used for external

frequency controlled devices.

Bit 6: SYSCLK Divider

The OSCIN multiplier output clock, f

, can be divided

SYSCLK

by 4 or 3 to generate the chip’s master clock. Active high

indicates a divide ratio of N = 3. Default low configures a

divide ratio of N = 4.

Bit 7: PLL Lock Detect

When this bit is set low, the OSCOUT pin functions in its default

mode and provides an output clock with frequency f

MCKL/R

as

described above.

If this bit is set to 1, the OSCOUT pin is configured to indicate

whether the PLL is locked to f

. In this mode, the OSCOUT

OSCIN

pin should be low-pass filtered with an RC filter of 1.0 kΩ and

0.1 µF. A high output on OSCOUT indicates the PLL has

achieved lock with f

REGISTER 02—Power-Down

OSCIN

.

Sections of the chip that are not used can be powered down

when the corresponding bits are set high. This register has a

default value of 0x00; all sections active.

Bit 0: Power-Down 8-Bit ADC

Active high powers down the 8-bit ADC.

Bit 3: Power-Down 12-Bit ADC Reference

Active high powers down the 12-bit ADC reference.

Bit 4: Power-Down 12-Bit ADC

Active high powers down the 12-bit ADC.

Bit 5: Power-Down Digital Tx

Active high powers down the digital transmit section of the chip,

similar to the function of the PWRDN pin.

Bit 6: Power-Down DAC Tx

Active high powers down the DAC.

Bit 7: Power-Down PLL

Active high powers down the OSCIN multiplier.

REGISTER 03 to 06—Sigma-Delta Control Words

The sigma-delta control words are 12 bits wide and split in

MSB Bits [11:4] and LSB Bits [3:0]. Changes to the sigma-delta

control words take effect immediately for every MSB or LSB

register write. Sigma-delta output control words have a default

value of “0.” The control words are in straight binary format, with

0x000 corresponding to the bottom of the scale and 0xFFF

corresponding to the top of the scale (see Figure 5 for details).

If Flag Enable (Bit 0 of Register 3 or 5) is set high, the SDELTA

pins will maintain a fixed logic level determined directly by the

MSB of the sigma-delta control word.

REGISTER 08—ADC Clock Configuration

Bit 4: Power-Down RxSYNC and 8-Bit ADC Clock

Setting this bit to 1 powers down the 8-bit ADC’s sampling clock

and stops the RxSYNC output pin. It can be used for additional

power-saving on top of the power-down selections in Register 2.

Bit 7: ADC Clock Select

When set high, the input clock at OSCIN is used directly as

the ADC sampling clock. When set low, the internally generated

master clock, MCLK, is used as the ADC sampling clock.

Best ADC performance is achieved when the ADCs are sampled

directly from f

using an external crystal or low jitter

OSCIN

crystal oscillator.

REGISTER 0C—Die Revision

Bits 0 to 3: Version

The die version of the chip can be read from this register.

–10–

REV. A

AD9877

REGISTER 0D—Tx Frequency Tuning Words LSBs

This register accommodates two least significant bits for each of

the four frequency tuning words (see description of Burst

Parameter below).

REGISTER 0E—DAC Gain Control

This register allows the user to program the DAC gain if Tx Gain

Control Select Bit 3 in Register F is set to 0.

Bits [3:0] DAC Gain

0000 0.0 dB (Default)

0001 0.5 dB

0010 1.0 dB

0011 1.5 dB

... ...

1110 7.0 dB

1111 7.5 dB

REGISTER 0F—Tx Path Configuration

Bit 0: Single-Tone Tx Mode

Active high configures the AD9877 for single-tone applications

(e.g., FSK). The AD9877 will supply a single frequency output

as determined by the frequency tuning word selected by the

active profile. In this mode, the TxIQ input data pins are

ignored but should be tied to a valid logic voltage level. Default

value is 0 (inactive).

Bit 1: Spectral Inversion Tx

When set to 1, inverted modulation is performed.

MODULATOR OUT I t Q t_ cos sin=

ωω

()+()

[]

Default is logic zero, noninverted modulation.

MODULATOR OUT I t Q t_ cos sin=

Bit 3: CA Interface Mode Select

ωω

()−()

[]

This bit changes the manner in which transmit gain control is

performed. Typically, either AD8321/AD8325 (default 0) or

AD8322/AD8327 (default 1) variable gain cable amplifiers

are programmed over the chip’s 3-wire cable amplifier (CA)

interface. The Tx gain control select changes the interpretation

of the bits in Registers 13, 17, 1B, and 1F (see Cable Driver

Gain Control section).

Bit 4 and 5: Profile Select

The AD9877 quadrature digital upconverter is capable of storing

four preconfigured modulation modes called profiles. Each profile

defines a transmit frequency tuning word and cable driver amplifier

gain (/DAC gain) setting. Profile Select [1:0] Bits or PROFILE [1:0]

pins program the current register profile to be used. Profile Select

bits should always be “0” if PROFILE[1:0] pins are used to switch

between profiles. Using the Profile Select Bits as a means of

switching between different profiles requires the PROFILE [1:0]

pins to be tied low.

REGISTERS 10 through 1F: Burst Parameter

Tx Frequency Tuning Words

The frequency tuning word (FTW) determines the DDS-generated

carrier frequency (f

) and is formed via a concatenation of

C

register addresses.

The 26-bit FTW is spread over four register addresses. Bit 25 is

the MSB and Bit 0 is the LSB.

The carrier frequency equation is given as:

f FTW f

=×

[]

CSYSCLK

where f

SYSCLK

= M ⫻ f

26

2

and FTW < 0x2000000.

OSCIN

Changes to FTW bytes take effect immediately.

Cable Driver Gain Control

The AD9877 has a three-pin interface to the AD832x family of

programmable gain cable driver amplifiers. This allows direct

control of the cable driver’s gain through the AD9877.

In its default mode, the complete 8-bit register value is transmitted

over the 3-wire CA interface.

If Bit 3 of Register F is set high, Bits [7:4] determine the 8-bit

word sent over the CA interface according to the table below.

Bits [7:4] CA Interface Transmit Word

0000 0000 0000 (Default)

0001 0000 0001

0010 0000 0010

0011 0000 0100

0100 0000 1000

0101 0001 0000

0110 0010 0000

0111 0100 0000

1000 1000 0000

In this mode, the lower bits determine the fine gain setting of

the DAC output.

Bits [3:0] DAC Fine Gain

0000 0.0 dB (Default)

0001 0.5 dB

0010 1.0 dB

0011 1.5 dB

... ...

1110 7.0 dB

1111 7.5 dB

New data is automatically sent over the 3-wire CA interface

(and DAC gain adjust) whenever the value of the active gain

control register changes or a new profile is selected. The default

value is 0x00 (lowest gain).

The formula for the combined output level calculation of the

AD9877 fine gain and the AD8327 or AD8322 coarse gain is:

VV fine coarse

8327

9877 0

9877 0

()

()

VV fine coarse

8322

26 19=+

()+()

26 14=+

()+()

−

−

where

fine = the decimal value of Bits [3:0].

coarse = the decimal value of Bits [7:8].

V

: the level at AD9877 output in dBmV for fine = 0.

9877(0)

: the level at output of the AD8327 in dBmV.

V

8327

: the level at output of the AD8322 in dBmV.

V

8322

REV. A

–11–

AD9877

–Typical Performance Characteristics

54 MHz (M = 8 and N = 4). ADC sample rate derived directly from f

OSCIN

, R

= 4.02 k⍀ (I

SET

(VAS = 3.3 V, V

= 3.3 V, f

DS

= 10 mA), and 75 ⍀ DAC load, unless otherwise noted.)

OUT

OSCIN

= 27 MHz, f

= 216 MHz, f

SYSCLK

TYPICAL POWER CONSUMPTION CHARACTERISTICS (Transmitted 20 MHz single tone, unless otherwise noted.)

340

310

MCLK

=

320

300

280

260

POWER

240

220

200

180

120 240140 160 180 200 220

f

SYSCLK

– MHz

TPC 1. Power Consumption vs. Clock Speed, f

SYSCLK

TPC 2. Power Consumption vs. Transmit Burst Duty Cycle

300

290

280

POWER

270

260

250

0 10010 30 50 60 70

20 40 9080

DUAL SIDEBAND TRANSMIT SPECTRUM (see Table II for Dual-Tone Generation)

0

–10

–20

–30

–40

–50

MAGNITUDE – dB

–60

–70

–80

–90

020261012 14

48 1816

FREQUENCY – MHz

TPC 3. Dual Sideband Spectral Plot, fC = 5 MHz, f = 1 MHz,

R

= 4.02 k⍀, DAC Gain = 7.5 dB, RBW = 1 kHz

SET

0

–10

–20

–30

–40

–50

MAGNITUDE – dB

–60

–70

–80

–90

55 7561 65 67 69

59 63 7371

57

TPC 4. Dual Sideband Spectral Plot, fC = 65 MHz,

f = 1 MHz, R

= 4.02 k⍀ (I

SET

% DUTY CYCLE

FREQUENCY – MHz

= 10 mA), RBW = 1 kHz

OUT

SINGLE SIDEBAND TRANSMIT SPECTRUM

0

–10

–20

–30

–40

–50

MAGNITUDE – dB

–60

–70

–80

–90

0 11030 50 60 70

20 40 9080

10 100

FREQUENCY – MHz

TPC 5. Single Sideband @ 65 MHz, RBW = 2 kHz,

= 66 MHz, f = 1 MHz, R

f

C

= 4.02 k⍀, DAC Gain = 7.5 dB

SET

0

–10

–20

–30

–40

–50

MAGNITUDE – dB

–60

–70

–80

–90

0 11030 50 60 70

20 40 9080

10 100

FREQUENCY – MHz

TPC 6. Single Sideband @ 42 MHz, RBW = 2 kHz,

fC = 43 MHz, f = 1 MHz, R

= 4.02 k⍀, DAC Gain = 7.5 dB

SET

–12–

REV. A

AD9877

f

IN

– MHz

59555

90

dB

80

70

65

60

15 45 75

75

85

25 35 65 85 105

PLL

f

OSCIN

0

–10

–20

–30

–40

–50

MAGNITUDE – dB

–60

–70

–80

–90

0 11030 50 60 70

20 40 9080

10 100

FREQUENCY – MHz

TPC 7. Single Sideband @ 5 MHz, RBW = 2 kHz,

= 6 MHz, f = 1 MHz, R

f

C

70

65

60

55

dB

= 4.02 k⍀, DAC Gain = 7.5 dB

SET

f

OSCIN

0

–10

–20

–30

–40

–50

MAGNITUDE – dB

–60

–70

–80

–90

62.5 67.564.0 65.0 65.5

63.5 64.5 66.566.0

63.0 67.0

FREQUENCY – MHz

TPC 8. Single Sideband @ 65 MHz, RBW = 500 Hz,

= 66 MHz, f = 1 MHz, R

f

C

= 4.02 k⍀, DAC Gain = 7.5 dB

SET

50

45

40

15 45 75

59555

25 35 65 85 105

TPC 9. 12-Bit ADC SNR vs. Input Frequency

11.0

10.5

10.0

9.5

9.0

8.5

ENOB

8.0

7.5

7.0

6.5

6.0

59555

15 45 75

25 35 65 85 105

TPC 11. 12-Bit ADC ENOBs vs. Input Frequency

PLL

f

PLL

f

IN

f

OSCIN

– MHz

IN

– MHz

TPC 10. 12-Bit ADC SFDR vs. Input Frequency

–60

–65

–70

f

PLL

f

IN

OSCIN

– MHz

–75

dB

–80

–85

–90

15 45 75

59555

25 35 65 85 105

TPC 12. 12-Bit ADC THD vs. Input Frequency

REV. A

–13–

AD9877

THEORY OF OPERATION

To gain a general understanding of the AD9877, it is helpful to

refer to Figure 1, which displays a block diagram of the device

architecture. The following is a general description of the device

functionality. Later sections will detail each of the data path

building blocks.

Transmit Section

Modulation Mode Operation

The AD9877 accepts 6-bit words that are strobed synchronous

to the master clock, MCLK, into the data assembler. A high

level on TxSYNC signals the start of a transmit symbol. Two

successive 6-bit words form a 12-bit symbol component. The

incoming data is assumed to be complex, in that alternating 12-bit

words are regarded as the in-phase (I) and quadrature (Q)

components of a symbol. Symbol components are assumed to

be in two’s complement format. The rate at which the TxIQ

data is read will be referred to as the master clock rate (f

TxIQ

TxSYNC

MCLK

REF CLK

RxIQ

RxSYNC

Rx IF

DATA

ASSEMBLER

6

(

f

)(f

MCLK

3

2

BURST PROFILE CTRL

4

4

DATA

12

HALF-BAND

FILTER #1

12

I

12

Q

)

IQCLK

AD832x CTRL

SERIAL INTERFACE

RxIQ

HALF-BAND

FILTER #2

12

12

R = 2, 3, ..., 63

MCLK

ⴜ2ⴜ2

ⴜR

).

CIC

FILTER

12

12

MUX

The data assembler receives the multiplexed IQ data and creates

two parallel 12-bit paths with I and Q data pairs, which comprise

a complex symbol. The rate at which the I and Q data word pairs

appear at the output of the data assembler will be referred to as

the IQ sample rate (f

at the TxIQ input to read a full 24-bit complex symbol, f

4 times the IQ sample rate (f

). Because four 6-bit reads are required

IQCLK

MCLK

= 4 ⫻ f

IQCLK

).

MCLK

is

Once through the data assembler, the IQ data streams are fed

through two half-band filters (half-band filters #1 and #2).

The combination of these two filters results in the sample rate

increasing by a factor of 4. Thus, at the output of half-band

filter #2, the sample rate is 4 ⫻ f

. In addition to the sample

IQCLK

rate increase, the half-band filters provide the low-pass filtering

characteristic necessary to suppress the spectral images produced

by the upsampling process.

QUADRATURE

MODULATOR

DDS

N = 3, 4

ⴜN

ⴜ8

ⴜ2

(f

)

OSCIN

ⴜ2

(f

)

OSCIN

COS

12

SIN

CONTROL WORD 0

CONTROL WORD 1

ⴜ2

REF8

DAC GAIN CONTROL

DAC

(

f

)

SYSCLK

OSCIN

MULTIPLIER ⴛ M

M = 1, 2, ..., 31

ADC

ADC

ADC

(

f

OSCIN

12

⌺-⌬

12

⌺-⌬

FSADJ

Tx

)

XTAL

OSCIN

SDELTA0

SDELTA1

I INPUT

Q INPUT

IF12 INPUT

AD9877

Figure 1. Block Diagram

–14–

REF12

REV. A

AD9877

After passing through the half-band filter stages, the IQ data

streams are fed to a cascaded integrator-comb (CIC) filter.

This filter is configured as an interpolating filter, which allows

further upsampling rates of 3 or 4. The CIC filter, like the

half-bands, has a built-in low-pass characteristic. Again, this

provides for suppression of the spectral images produced by

the upsampling process.

The digital quadrature modulator stage following the CIC filters

is used to frequency shift (upconvert) the baseband spectrum of

the incoming data stream up to the desired carrier frequency.

The carrier frequency is controlled numerically by a direct

digital synthesizer (DDS). The DDS uses the internal system

clock (f

) to generate the desired carrier frequency with a

SYSCLK

high degree of precision. The carrier is applied to the I and Q

multipliers in quadrature fashion (90° phase offset) and summed to

yield a data stream that is the modulated carrier.

It should be noted at this point that the incoming data has been

converted from an input sample rate of f

rate of f

(see Figure 1). The modulated carrier becomes

SYSCLK

to an output sample

MCLK

the 12-bit samples sent to the DAC.

Single-Tone Output Transmit Operation

The AD9877 can be configured for frequency synthesis applications by writing the single-tone bit true. In single-tone

mode, the AD9877 disengages the modulator and preceding

data path logic to output a spectrally pure single frequency sine

wave. The AD9877 provides for a 26-bit frequency tuning

word, which results in a tuning resolution of 3.2 Hz at a f

SYSCLK

rate of 216 MHz. A good rule of thumb when using the

AD9877 as a frequency synthesizer is to limit the fundamental

output frequency to 30% of f

. This avoids generating

SYSCLK

aliases too close to the desired fundamental output frequency,

thus minimizing the cost of filtering the aliases.

Frequency hopping via the PROFILE inputs and associated

tuning word is also supported in single-tone mode, which allows

frequency shift keying (FSK) modulation.

OSCIN Clock Multiplier

As mentioned earlier, the output data is sampled at the rate of

. The AD9877 has a built-in programmable clock

f

SYSCLK

multiplier and an oscillator circuit. This allows the use of a

relatively low frequency, thus less expensive, crystal or oscillator to generate the OSCIN signal. The low frequency OSCIN

signal can then be multiplied in frequency by an integer factor of

between 1 and 31, inclusive, to become the f

SYSCLK

clock.

For DDS applications, the carrier is typically limited to about

30% of f

. For a 65 MHz carrier, the system clock required is

SYSCLK

above 216 MHz.

The OSCIN multiplier function maintains clock integrity as

evidenced by the AD9877’s excellent phase noise characteristics

and low clock-related spur in the output spectrum. External loop

filter components consisting of a series resistor (1.3 kΩ) and

capacitor (0.01 µF) provide the compensation zero for the OSCIN

multiplier PLL loop. The overall loop performance has been

optimized for these component values.

Receive Section

The AD9877 includes three high speed, high performance

ADCs. Two matched 8-bit ADCs are optimized for analog IQ

demodulated signals and can be sampled at rates up to

16.5 MSPS. A direct IF 12-bit ADC can sample signals at rates

up to 33 MSPS.

The ADC sampling frequency can be derived directly from the

OSCIN signal or from the on-chip OSCIN multiplier. For

highest dynamic performance, it is recommended to choose an

OSCIN frequency that can be directly used as the ADC sampling

clock. Digital 8-bit ADC outputs are multiplexed to one 4-bit

bus, clocked by the master clock (MCLK). The 12-bit ADC

uses a nonmultiplexed 12-bit interface with an output data rate

of half f

frequency.

MCLK

REV. A

–15–

AD9877

Clock and Oscillator Circuitry

The AD9877’s internal oscillator generates all sampling clocks

from a simple, low cost, parallel resonance, fundamental frequency

quartz crystal. Figure 2 shows how the quartz crystal is connected

between OSCIN (Pin 61) and XTAL (Pin 60) with parallel

resonant load capacitors as specified by the crystal manufacturer.

The internal oscillator circuitry can also be overdriven by a

clock applied to OSCIN with XTAL left unconnected.

ffNM

=×

OSCIN MCLC

An internal phase-locked loop (PLL) generates the DAC sampling

frequency, f

The MCLK signal (Pin 23) f

, by multiplying OSCIN frequency M times.

SYSCLK

is derived by dividing this

MCLK

PLL output frequency by N (Register Address 01h).

ffM

ffMN

MCLK OSCIN

(MSB )

(MSB)

(MSB)

=×

SCYCLK OSCIN

=×

1

AVDD

2

DRGND

3

DRVDD

4

IF(11)

IF(10)

5

IF(9)

6

IF(8)

7

IF(7)

8

IF(6)

9

IF(5)

10

IF(4)

11

12

IF(3)

IF(2)

13

14

IF(1)

IF(0)

15

RxIQ(3)

16

17

RxIQ(2)

RxIQ(1)

18

RxIQ(0)

DRGND

DRVDD

MLCK

DVDD

DGND

TxSYNC

TxIQ(5)

TxIQ(4)

TxIQ(3)

TxIQ(2)

19

20

21

22

23

24

25

26

27

28

29

30

RxSYNC

CP1

10F

C1

0.1FC20.1FC30.1F

IF12+

IF12–

AGND

AGND

AVDD

AVDD

REFT12

NC

99989796959493929190898887868584838281

100

REFB12

C4

0.1FC50.1FC60.1F

NC

NC

AGND

AGND

AD9877

TOP VIEW

(Pins Down)

An external PLL loop filter (Pin 57) consisting of a series resistor and

ceramic capacitor (Figure 2, R1 = 1.3 kΩ, C12 = 0.01 µF) is

required for stability of the PLL. Also, a shield surrounding

these components is recommended to minimize external noise

coupling into the PLL’s voltage-controlled oscillator input

(guard trace connected to AVDDPLL).

Figure 1 shows that ADCs are either sampled directly by a low

jitter clock at OSCIN or by a clock that is derived from the

PLL output. Operating modes can be selected in Register 8.

Sampling the ADCs directly with the OSCIN clock requires

MCLK to be programmed at twice the OSCIN frequency.

CP2

10F

Q IN+

AVDD

REFT8

REFB8

Q IN–

AVDD

AGND

AGNDIQ

80

I IN+

79

I IN–

78

AGNDIQ

77

NC

76

NC

75

AGNDIQ

74

AVDDIQ

73

DRVDD

72

OSCOUT

71

DRGND

70

DGNDSD

69

SDELTA0

68

SDELTA1

67

DVDDSD

66

65

CA_EN

CA_DATA

64

CA_CLK

63

DVDDOSC

62

OSCIN

61

XTAL

60

59

DGNDOSC

AGNDPLL

58

PLLFILTER

57

AVDDPLL

56

DVDDPLL

55

DGNDPLL

54

AVDDTx

53

Tx+

52

Tx–

51

C10

20pF

C11

20pF

GUARD TRACE

C12

R1

1.3k⍀

0.01F

31

3233343536

DVDD

TxIQ(1)

TxIQ(0)

38394041424344454647484950

37

CS

SDO

SDIO

SCLK

PROFILE(1)

RESET

PROFILE(0)

DVDD

DGND

DGND

NC = NO CONNECT

DVDDTx

DGNDTx

C13

0.1F

REFIO

PWRDN

FSADJ

DGND

Figure 2. Basic Connections Diagram

–16–

AGNDTx

R

SET

2k⍀

REV. A

AD9877

P

PWRDN

1ms

5 MCLK

RESET

V

S

PROGRAMMABLE CLOCK OUTPUT REF CLK

The AD9877 provides a frequency-programmable clock output

OSCOUT (Pin 71). OSCIN or MCLK (f

) and the master

MCLK

clock divider ratio R stored in Register Address 01h determine

its frequency:

ffRorf

= /

OSCOUT MCLC OSCIN

In its default setting (0x00 in Register 1), the OSCOUT pin

provides a buffered output of f

OSCIN

.

RESET AND TRANSMIT POWER-DOWN

Power-Up Sequence

On initial power-up, the RESET pin should be held low until

the power supply is stable.

Once RESET is de-asserted, the AD9877 can be programmed

over the serial port. It is recommended that the PWRDN pin

be held low during the reset. Changes to ADC Clock Select

(Register 08h) or SYS Clock Divider N (Register 01) should be

programmed before the rising edge of PWRDN. Changes to the

multiplier (M) will require the PLL to reacquire the new

frequency and may take up to 1 ms.

Once the PLL is frequency-locked and after the PWRDN pin is

brought high, transmit data can be sent reliably.

If the PWRDN pin cannot be held low throughout the reset and

PLL settling time period, then the Power-Down Digital Tx Bit

or the PWRDN pin should be pulsed after the PLL has settled.

This will ensure correct transmit filter initialization.

RESET

To initiate hardware reset, the RESET pin should be held low for

at least 100 ns. All internally generated clocks but OSCOUT

stop during reset. The MCLK signal begins transmission three

clock cycles after reset. The rising edge of RESET reinitializes

the programmable registers to their default values. The same

sequence as described in the Power-Up Sequence section should

be followed after a reset or change in M.

A software reset (writing a 1 into Bit 5 of Register 00) is

functionally equivalent to the hardware reset but does not force

Register 00 to its default value.

Figure 3. Power-Up Sequence for Tx Data Path

Transmit Power-Down

A low level on the PWRDN pin stops all clocks linked to the

digital transmit data path and resets the CIC filter. De-asserting

PWRDN reactivates all clocks. The CIC filter is held in a reset

state for 80 MCLK cycles after the rising edge of PWRDN to

allow for flushing of the half-band filters with new input data.

Transmit data bursts should be padded with at least 20 symbols

of null data directly before the PWRDN pin is asserted. Immediately after the PWRDN pin is de-asserted, the transmit burst

should start with a minimum of 20 null data symbols. This

avoids unintended DAC output samples caused by the transmit

path latency and filter settling time.

Software Power-Down Digital Tx (Bit 5 in Register 02) is

functionally equivalent to the hardware PWRDN pin and takes

effect immediately after the last register bit has been written over

the serial port.

WRDN

TxIQ

TxSYNC

5 MCLK

20 NULL SYMBOLS

00 00 0 000

DATA SYMBOLS 20 NULL SYMBOLS

Figure 4. Timing Sequence to Flush Tx Data Path

REV. A

–17–

AD9877

SIGMA-DELTA OUTPUTS

The AD9877 contains two independent sigma-delta outputs

that provide a digital logic bit stream with an average duty cycle

that varies between 0% and 4095/40.96%, depending on the

programmed code, as shown in Figure 5.

000h

001h

002h

800h

FFFh

8 t

8 t

MCLK

MCLK

4096 ⴛ 8

4096 ⴛ 8

t

MCLK

t

MCLK

Figure 5. Sigma-Delta Output Signals

These bitstreams can be low-pass filtered to generate programmable dc voltages of:

V Sigma DeltaCode V V

DC H L

where VH = V

AD9877

MCLK

ⴜ8

=−

()()

– 0.6 V and VL = 0.4 V.

DRVDD

SIGMA-DELTA 0

CONTROL

WORD 0

CONTROL

WORD 1

12

⌺-⌬

12

⌺-⌬

SIGMA-DELTA 1

TYPICAL: R = 50k⍀

C = 0.01F

f

= 1/(2RC) = 318Hz

–3dB

+4096

R

R

C

C

DC (0.4 TO

DRVDD – 0.6V)

DC (0.4 TO

DRVDD – 0.6V)

Figure 6. Sigma-Delta RC Filter

In cable modem set-top box applications, the outputs can be

used to control external variable gain amplifiers and RF tuners.

A simple single-pole RC low-pass filter provides sufficient filtering

(Figure 6).

In more demanding applications where additional gain, level shift,

or drive capability is required, a first or second order active filter

might be considered for each sigma-delta output (Figure 7).

C

R1

R

OFFSET

R

V

OUT

OP250

= (VSD + V

V

OUT

TYPICAL: R = 50k⍀

C = 0.01F

f

–3dB

) (1 + R/R1)/2

OFFSET

= 1/(2RC) = 318Hz

AD9877

SIGMA-DELTA

⌺-⌬

R

V

SD

C

V

Figure 7. Sigma-Delta Active Filter with Gain and Offset

SERIAL INTERFACE FOR REGISTER CONTROL

The AD9877 serial port is a flexible, synchronous serial communications port allowing easy interface to many industry-standard

microcontrollers and microprocessors. The interface allows

read/write access to all registers that configure the AD9877.

Single or multiple byte transfers are supported. Also, the interface

can be programmed to read words either MSB first or LSB first.

The AD9877’s serial interface port I/O can be configured to

have one bidirectional I/O (SDIO) pin or two unidirectional I/O

(SDIO/SDO) pins.

General Operation of the Serial Interface

There are two phases to a communication cycle with the AD9877.

Phase 1 is the instruction cycle, which is the writing of an instruction

byte into the AD9877, coincident with the first eight SCLK rising

edges. The instruction byte provides the AD9877 serial port controller with information regarding the data transfer cycle, Phase 2 of the

communication cycle. The Phase 1 instruction byte defines whether

the upcoming data transfer is read or write, the number of bytes in

the data transfer, and the starting register address for the first byte

of the data transfer. The first eight SCLK rising edges of each

communication cycle are used to write the instruction byte into

the AD9877.

The eight remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the AD9877

and the system controller. Phase 2 of the communication cycle is a

transfer of 1 to 4 data bytes as determined by the instruction byte.

Registers change immediately upon writing to the last bit of each

transfer byte.

Instruction Byte

The Instruction Byte contains the following information:

MSB LSB

I7 I6 I5 I4 I3 I2 I1 I0

R/W N1 N0 A4 A3 A2 A1 A0

The R/W Bit of the Instruction Byte determines whether a read

or a write data transfer will occur after the Instruction Byte write.

Logic high indicates a read operation. Logic zero indicates a

write operation. The N1:N0 Bits determine the number of bytes

to be transferred during the data transfer cycle. The bit decodes

are shown in the table below:

N1 N0 Description

00Transfer 1 Byte

01Transfer 2 Bytes

10Transfer 3 Bytes

11Transfer 4 Bytes

The Bits A4:A0 determine which register is accessed during the

data transfer portion of the communications cycle. For multibyte

transfers, this address is the starting byte address. The remaining

register addresses are generated by the AD9877.

Serial Interface Port Pin Description

SCLK—Serial Clock. The serial clock pin is used to synchronize

data transfers from the AD9877 and to run the serial port state

machine. The maximum SCLK frequency is 15 MHz. Input data

to the AD9877 is sampled on the rising edge of SCLK. Output

data changes on the falling edge of SCLK.

–18–

REV. A

AD9877

CS

CS—Chip Select. Active low input starts and gates a communication cycle. It allows multiple devices to share a common serial

port bus. The SDO and SDIO pins go to a high impedance state

when CS is high. Chip select should stay low during the entire

communication cycle.

SDIO—Serial Data I/O. Data is always written into the AD9877

on this pin. However, this pin can be used as a bidirectional data

line. The configuration of this pin is controlled by Bit 7 of

Register 0. The default is logic 0, which configures the SDIO

pin as unidirectional.

SDO—Serial Data Out. Data is read from this pin for protocols

that use separate lines for transmitting and receiving data. In the

case where the AD9877 operates in a single bidirectional I/O mode,

this pin does not output data and is set to a high impedance state.

MSB/LSB Transfers

The AD9877 serial port can support both the most significant

bit (MSB) first or the least significant bit (LSB) first data formats.

This functionality is controlled by the LSB first bit in Register 0.

The default is MSB first.

When this bit is set active high, the AD9877 serial port is in

LSB first format. In LSB first mode, the instruction byte and

data bytes must be written from the least significant bit to the

most significant bit. In LSB first mode, the serial port internal

byte address generator increments for each byte of the multibyte

communication cycle.

When this bit is set default low, the AD9877 serial port is in

MSB first format. In MSB first mode, the instruction byte and

data bytes must be written from the most significant bit to

the least significant bit. In MSB first mode, the serial port internal

byte address generator decrements for each byte of the multibyte

communication cycle.

When incrementing from 0x1F, the address generator changes

to 0x00. When decrementing from 0x00, the address generator

changes to 0x1F.

Notes on Serial Port Operation

The AD9877 serial port configuration bits reside in Bit 6 and

Bit 7 of Register Address 00h. It is important to note that the

configuration changes immediately upon writing to the last bit

of the register. For multibyte transfers, writing to this register

may occur during the middle of the communication cycle.

Care must be taken to compensate for this new configuration

for the remaining bytes of the current communication cycle.

The same considerations apply to setting the RESET Bit in Register

Address 00h. All other registers are set to their default values, but

the software reset does not affect the bits in Register Address 00h.

It is recommended to use only single byte transfers when

changing serial port configurations or initiating a software reset.

A write to Bits 1, 2, and 3 of Address 00h with the same logic

levels as Bits 7, 6, and 5 (bit pattern: XY1001YX binary) allows

the host processor to reprogram a lost serial port configuration

and to reset the registers to their default values. A second write

to Address 00h with RESET Bit low and serial port configuration as specified above (XY) reprograms the OSCIN multiplier

setting. A changed f

of 200 f

CS

SCLK

SDIO

SDO

cycles.

MCLK

INSTRUCTION CYCLE

R/W N0 A4 A3 A2 A1 A0

N1

frequency is stable after a maximum

SYSCLK

DATA TRANSFER CYCLE

D6

D7

n

n

D7

D6

n

n

D2

D2

D10D0

0

D1

0

0

D0

0

0

Figure 8a. Serial Register Interface Timing MSB First

SCLK

SDIO

SDO

CS

INSTRUCTION CYCLE

A4A3A2A1A0

N0 N1 R/W

DATA TRANSFER CYCLE

D2

D1

0

0D00

D2

D1

0

0D00

D6

D7

n

n

D6

D7

n

n

Figure 8b. Serial Register Interface Timing LSB First

f

CS

SCLK

SDIO

t

DS

t

DS

INSTRUCTION BIT 7 INSTRUCTION BIT 6

SCLK

t

PWH

t

t

PWL

DH

Figure 9. Timing Diagram for Register WRITE to AD9877

SCLK

t

SDIO

SDO

DATA BIT N DATA BIT N – 1

DV

Figure 10. Timing Diagram for Register READ from AD9877

REV. A

MCLK

TxSYNC

TxIQ

TxI[11:6]

t

SU

t

HD

TxI[5:0] TxQ[5:0]TxQ[11:6] TxI[11:6] TxI[5:0] TxQ[5:0]TxQ[11:6] TxI[5:0]TxI[11:6]

Figure 11. Transmit Timing Diagram

–19–

AD9877

TRANSMIT PATH (TX)

Transmit Timing

The AD9877 provides a master clock MCLK and expects 6-bit

multiplexed TxIQ data on each rising edge. Transmit symbols

are framed with the TxSYNC input. TxSYNC high indicates

the start of a transmit symbol. Four consecutive 6-bit data

packages form a symbol (I MSB, I LSB, Q MSB, and Q LSB).

Data Assembler

The input data stream is representative complex data. Two 6-bit

words form a 12-bit symbol component (two’s complement

format). Four input samples are required to produce one I/Q

data pair. The I/Q sample rate f

half-band filter is a quarter of the input data rate f

The I/Q sample rate f

puts a bandwidth limit on the maximum

IQCLK

at the input to the first

IQCLK

MCLK

.

transmit spectrum. This is the familiar Nyquist limit and is equal

to one-half f

, which hereafter will be referred to as f

IQCLK

NYQ

.

Half-Band Filters (HBFs)

HBF 1 and HBF 2 are both interpolating filters, each of which

doubles the sampling rate. Together, HBF 1 and HBF 2 have

26 taps and provide a factor of 4 increase in the sampling rate

(4 ⫻ f

IQCLK

or 8 ⫻ f

NYQ

).

In relation to phase response, both HBFs are linear phase filters.

As such, virtually no phase distortion is introduced within the

pass band of the filters. This is an important feature, since phase

distortion is generally intolerable in a data transmission system.

Cascaded Integrator-COMB (CIC) Filter

A CIC filter is unlike a typical FIR filter in that it offers the flexibility to handle differing input and output sample rates in any integer

ratios. In the AD9877, the CIC filter is configured as a programmable interpolator and provides a sample rate increase by a factor

of R = 3 or R = 4. In addition to the ability to provide a change in

the sample rate between the input and the output, a CIC filter also

has an intrinsic low pass frequency response characteristic. The

frequency response of a CIC filter is dependent on three factors:

1. The rate change ratio, R.

2. The order of the filter, n.

3. The number of unit delays per stage, m.

It can be shown that the system function H(z) of a CIC filter is

given by:

Hz

()=

11

R

1

n

Rm

−

z

−

−

=

−

1

zR

Rm

1

∑

k

n

−

1

k

−

z

=

0

The form on the far right has the advantage of providing a result

for z = 1 (corresponding to zero frequency or dc). The alternate

form yields an indeterminate form (0/0) for z = 1 but is otherwise

identical. The only variable parameter for the AD9877’s CIC

filter is R; m and n are fixed at 1 and 3, respectively. Thus, the

CIC system function for the AD9877 simplifies to:

Hz

()=

3

R

−

11

R

z

−

−

1

=

1

−

zR

R

1

k

3

1

−

k

−

z

∑

0

=

The transfer function is given by:

Hf

()

3

jfR

()

−

2

11

=

R

π

e

−

jf

−

2

π

eR

−

1

sin( )

1

=

sin( )

π

π

fR

f

3

The frequency response in this form is such that f is scaled to the

output sample rate of the CIC filter. That is, f = 1 corresponds to

the frequency of the output sample rate of the CIC filter. H(z) will

yield the frequency response with respect to the input sample of

the CIC filter.

Combined Filter Response

The combined frequency response of HBF 1, HBF 2, and CIC

is shown in Figures 12a to 12c and Figures 13a to 13c.

The usable bandwidth of the filter chain puts a limit on the maximum data rate that can be propagated through the AD9877. A look

at the pass band detail of the combined filter response (Figures 12d

and 13d) indicates that in order to maintain an amplitude error of

no more than 1 dB, we are restricted to signals having a bandwidth

of no more than about 60% of f

. Thus, in order to keep the

NYQ

bandwidth of the data in the flat portion of the filter pass band, the

user must oversample the baseband data by at least a factor of 2

prior to representing it to the AD9877. Note that without oversampling, the Nyquist bandwidth of the baseband data corresponds to

the f

. As such, the upper end of the data bandwidth will suffer

NYQ

6 dB or more of attenuation due to the frequency response of the

digital filters.

Furthermore, if the baseband data applied to the AD9877 has been

pulse shaped, there is an additional concern. Typically, pulse

shaping is applied to the baseband data via a filter having a raised

cosine response. In such cases, an ␣ value is used to modify the

bandwidth of the data where the value of ␣ is such that 0 ⱕ ␣ ⱕ 1.

A value of 0 causes the data bandwidth to correspond to the

Nyquist bandwidth. A value of 1 causes the data bandwidth to

be extended to twice the Nyquist bandwith. Thus, with 2⫻ over-

sampling of the baseband data and ␣ = 1, the Nyquist bandwidth

of the data will correspond with the I/Q Nyquist bandwidth. As

stated earlier, this results in problems near the upper edge of the

data bandwidth due to the frequency response of the filters. The

maximum value of ␣ that can be implemented is 0.45. This is

because the data bandwidth becomes:

12 1 0725+

()

=α ff

NYQ NYQ

.

which puts the data bandwidth at the extreme edge of the flat

portion of the filter response.

If a particular application requires an α value between 0.45 and 1,

the user must oversample the baseband data by at least a factor

of 4. The combined HB1, HB2, and CIC filter introduces, over the

frequency range of the data to be transmitted, a worst-case droop

of less than 0.2 dB.

–20–

REV. A

AD9877

FREQUENCY –

f

S

/2

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

10

0

MAGNITUDE – dB

–10

–20

–30

–40

–50

–60

–70

–80

10

0

–10

–20

–30

–40

MAGNITUDE – dB

–50

–60

–70

–80

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

FREQUENCY –

f

/2

S

Figure 12a. Cascaded Filter 12x Interpolator (N = 3)

10

0

–10

–20

–30

–40

MAGNITUDE – dB

–50

–60

–70

–80

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

Figure 12b. Input Signal Spectrum (N = 3),

FREQUENCY –

f

/2

S

α

= 0.25

10

0

–10

–20

–30

–40

MAGNITUDE – dB

–50

–60

–70

–80

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

FREQUENCY – fS/2

Figure 13a. Cascaded Filter 16x Interpolator (N = 4)

10

0

–10

–20

–30

–40

MAGNITUDE – dB

–50

–60

–70

–80

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

Figure 13b. Input Signal Spectrum (N = 4), α = 0.25

FREQUENCY – fS/2

10

0

–10

–20

–30

–40

MAGNITUDE – dB

–50

–60

REV. A

–70

–80

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

Figure 12c. Response to Input Signal Spectrum (N = 3)

FREQUENCY –

f

/2

S

Figure 13c. Response to Input Signal Spectrum (N = 4)

–21–

AD9877

1

0

–1

–2

–3

MAGNITUDE – dB

–4

–5

–6

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

FREQUENCY RELATIVE TO I/Q NYQUIST BW

Figure 12d. Cascaded Filter Pass-Band Detail (N = 3)

Q

Z

X

I

X

1

0

–1

–2

–3

MAGNITUDE – dB

–4

–5

–6

0 1.00.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

FREQUENCY RELATIVE TO I/Q NYQUIST BW

Figure 13d. Cascaded Filter Pass-Band Detail (N = 4)

12

COMPLEX DATA INPUT

12IO

+0.2dB

HBF + CIC

INTERPOLATOR

+0.2dB

HBF + CIC

INTERPOLATOR

–3dB

I

ATTENUATOR

OO

ATTENUATOR

–3dB

I

MODULATOR

3dB MAX

DAC

TWO'S COMPLEMENT FORMAT

Figure 15. Signal Level Contribution

Figure 14. 16-Quadrature Modulation

The following example assumes a Pk/rms level of 10 dB:

Tx Signal Level Considerations

The quadrature modulator itself introduces a maximum gain of

3 dB in the signal level. To visualize this, assume that both the I data

and Q data are fixed at the maximum possible digital value, x.

Then the output of the modulator, z, is:

zx tx t=

cos sinωω

()−()

[]

It can be shown that

zxxx=+

()

z

assumes a maximum value of:

22

=

2

(a gain of +3 dB)

However, if the same number of bits were used to represent

z

the

values as is used to represent the x values, an overflow

would occur. To prevent this possibility, an effective –3 dB

attenuation is internally implemented on the I and Q data path.

zx=+

12 12//

()

=

Maximum Symbol Component Input Value

±

LSBs dB LSBs

()

Maximum Complex Input rmsValue

LSBs dB Pk rms dB LSBs rms

Maximum Complex Input rms Value calculation uses both I

+

=±2047 0 2 2000–.

=

=2000 6 1265–

()

and Q symbol components, which adds a factor of 2 (= 6 dB) to

the formula.

Table II shows typical IQ input test signals with amplitude

levels related to 12-bit full scale (FS).

Tx Throughput and Latency

Data inputs effect the output fairly quickly but remain effective

due to AD9877’s filter characteristics. Data transmit latency

through the AD9877 is easiest to describe in terms of f

clock cycles (4 f

). The numbers quoted are when an effect

MCLK

is first seen after an input value change.

=

SYSCLK

Table II. IQ Input Test Signals

Analog Output Digital Input Input Level Modulator Output Level

Single Tone (f

– f) I = cos(f) FS – 0.2 dB FS – 3.0 dB

C

Q = cos(f + 90⬚) = –sin(f) FS – 0.2 dB

Single Tone (f

+ f) I = cos(f) FS – 0.2 dB FS – 3.0 dB

C

Q = cos(f + 270ⴗ) = +sin(f) FS – 0.2 dB

Dual Tone (f

ⴞ f) I = cos(f) FS – 0.2 dB FS

C

Q = cos(f + 180ⴗ) = –cos(f) or Q = +cos(f) FS – 0.2 dB

–22–

REV. A

AD9877

Latency of I/Q data entering the data assembler (AD9877 input)

to the DAC output is 119 f

clock cycles (29.75 f

SYSCLK

MCLK

cycles). DC values applied to the data assembler input will take

up to 176 f

clock cycles (44 f

SYSCLK

cycles) to propagate

MCLK

and settle at the DAC output.

Frequency hopping is accomplished via changing the PROFILE

input pins. The time required to switch from one frequency to

another is less than 232 f

cycles (58.5 f

SYSCLK

MCLK

cycles).

D/A Converter

A 12-bit digital-to-analog converter (DAC) is used to convert

the digitally processed waveform into an analog signal. The

worst-case spurious signals due to the DAC are the harmonics of

the fundamental signal and their aliases (please see Analog Devices’

DDS Tutorial at www.analog.com/dds). The conversion

process will produce aliased components of the fundamental

signal at n ⫻ f

SYSCLK

± f

(n = 1, 2, and 3). These are

CARRIER

typically filtered with an external RLC filter at the DAC output.

It is important for this analog filter to have a sufficiently flat gain

and linear phase response across the bandwidth of interest to avoid

modulation impairments. A relatively inexpensive seventh order

elliptical low-pass filter is sufficient to suppress the aliased components for HFC network applications.

The AD9877 provides true and complement current outputs.

The full-scale output current is set by the R

resistor at Pin 49

SET

and the DAC gain register. Assuming maximum DAC gain, the