T

Broadband Modem Mixed-Signal Front End

FEATURES

Low cost 3.3 V CMOS MxFETM for broadband modems

10-bit D/A converter

2×/4× interpolation filter

200 MSPS DAC update rate

Integrated 23 dBm line driver with 19.5 dB gain control

10-bit, 80 MSPS A/D converter

−12 dB to +48 dB low noise RxPGA (< 3.0 nV/rtHz)

Third order, programmable low-pass filter

Flexible digital data path interface

Half- and full-duplex operation

Backward-compatible with AD9975 and AD9875

Various power-down/reduction modes

Internal clock multiplier (PLL)

2 auxiliary programmable clock outputs

Available in 64-lead chip scale package or bare die

APPLICATIONS

Powerline networking

VDSL and HPNA

PWR DWN

MODE

XEN/SYNC

TXCLK

ADIO[9:4]/

Tx[5:0]

ADIO[3:0]/

Rx[5:0]

RXE/SYNC

RXCLK

AGC[5:0]

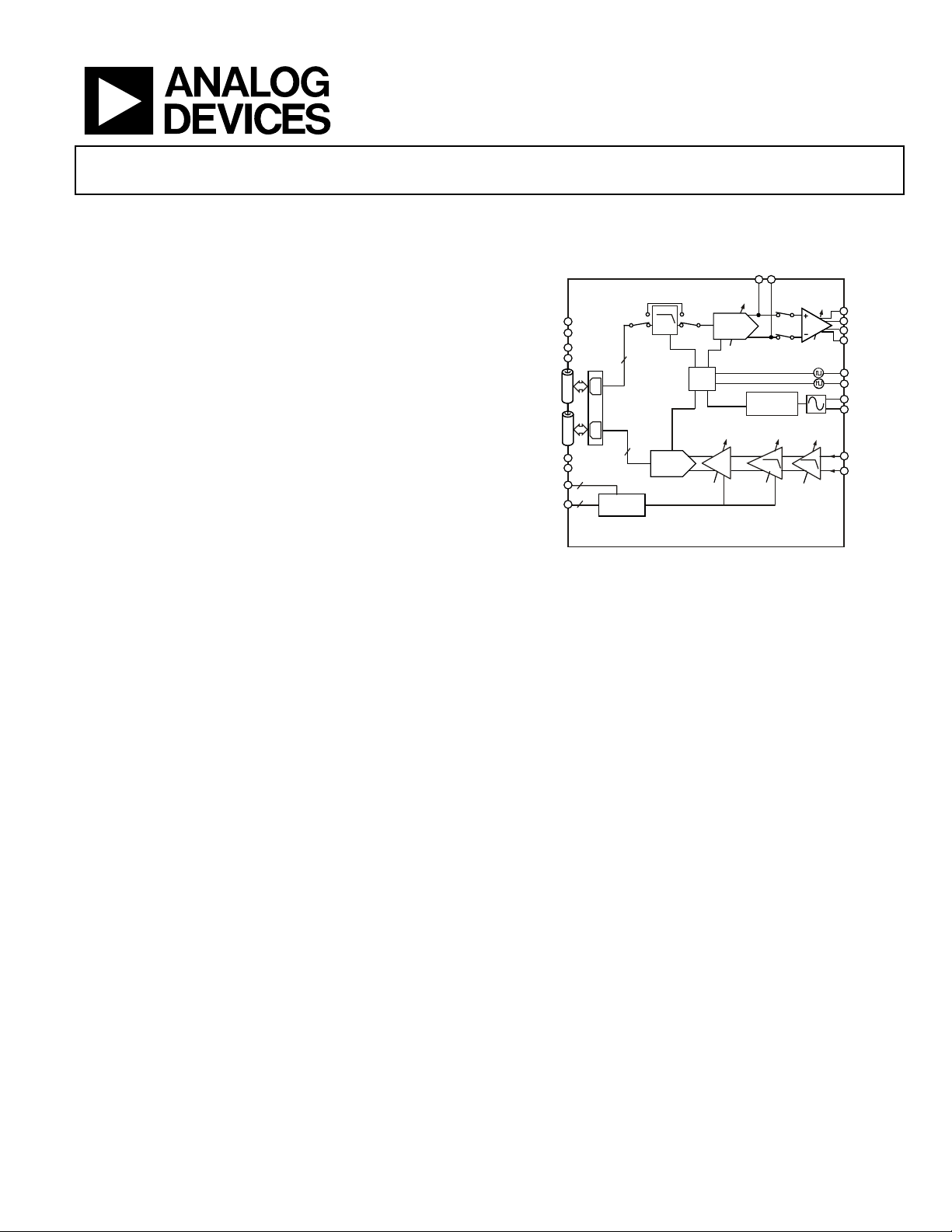

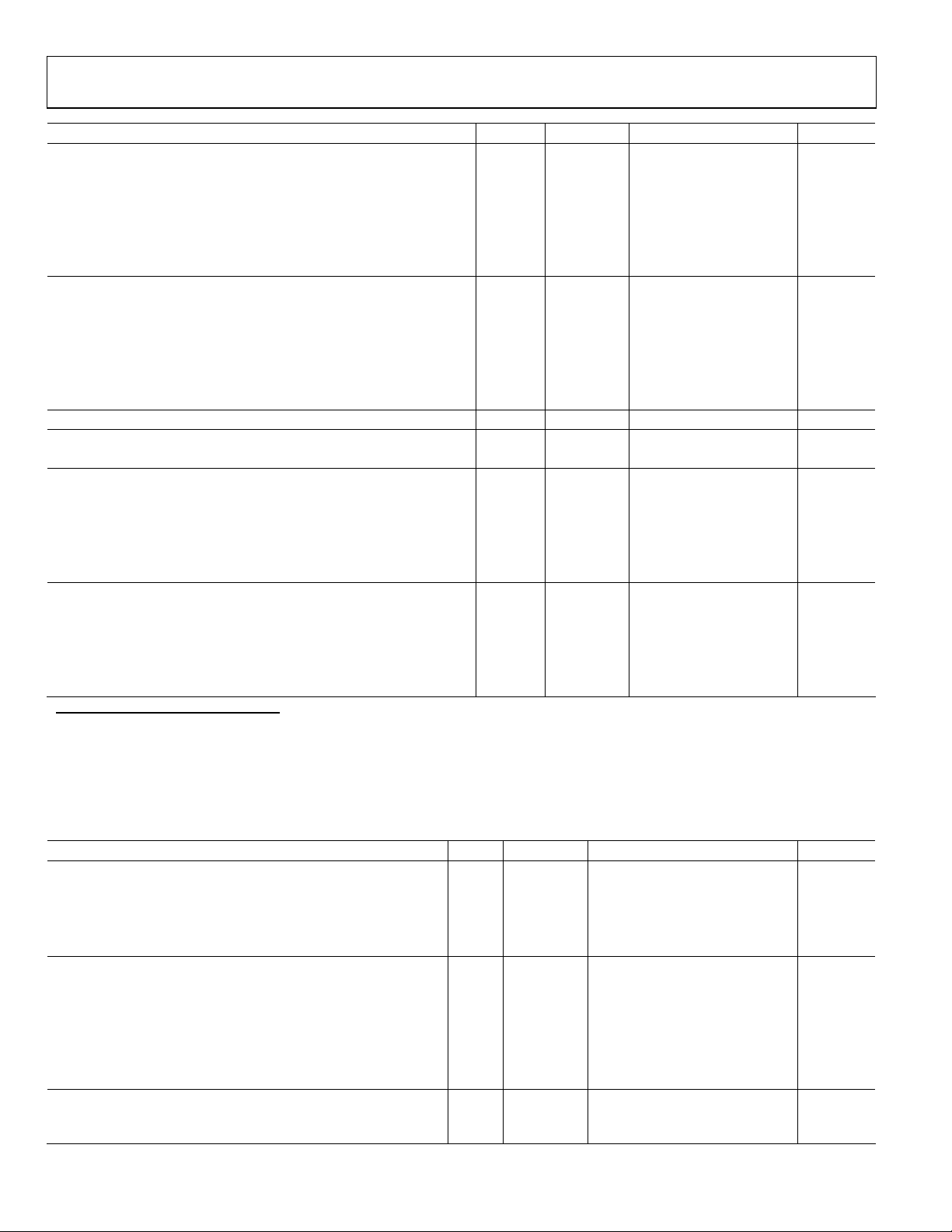

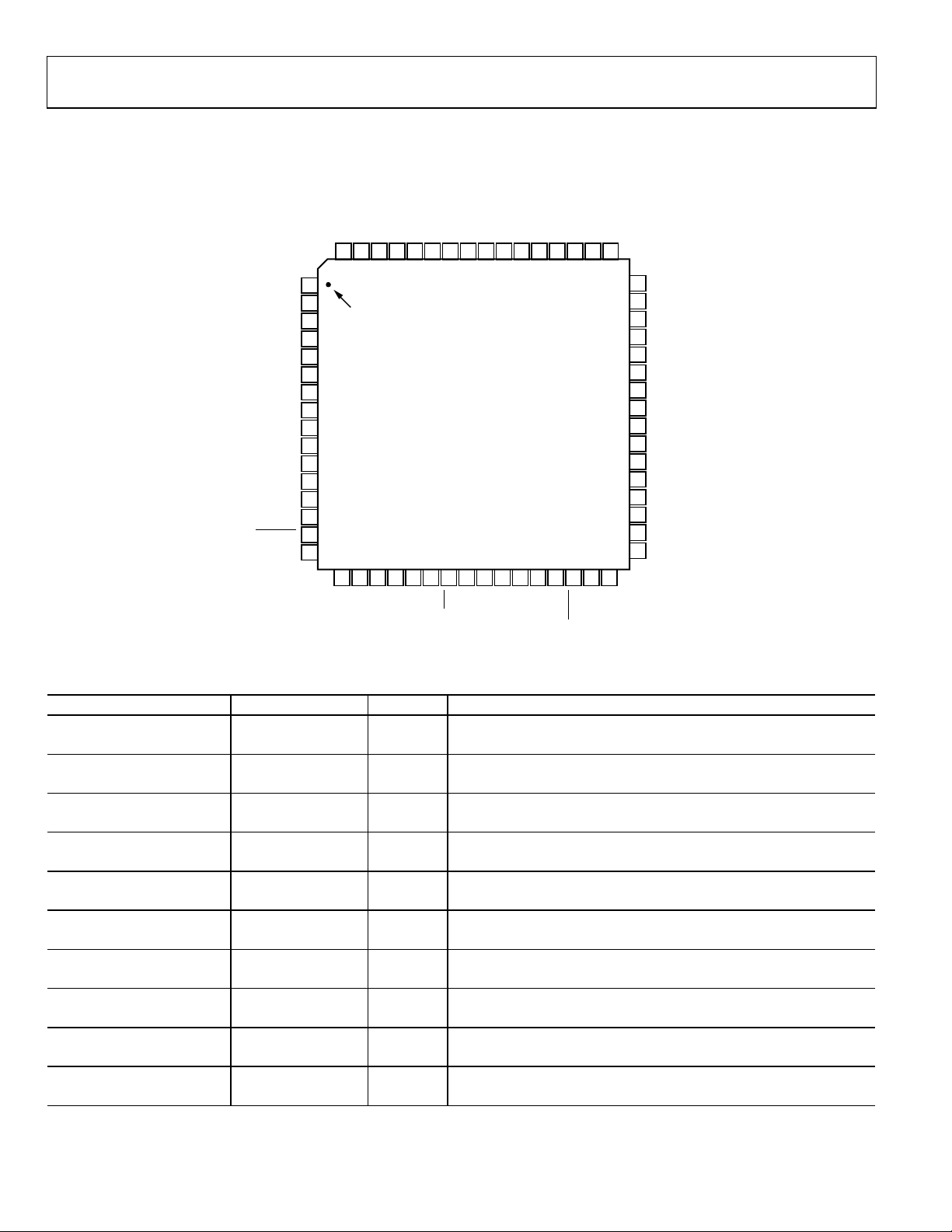

FUNCTIONAL BLOCK DIAGRAM

AD9865

6

4

SPI

REGISTER

CONTROL

2-4X

10

10

ADC

80MSPS

CLK

SYN.

0 TO 6dB

∆ = 1dB

TxDAC

0 TO –7.5dB

– 6 TO 18dB

∆ = 6dB

Figure 1.

IOUT_P+

IOUT_P–

2M CLK

MULTIPLIER

2-POLE

LPF

–6 TO 24dB

∆ = 6dB

AD9865

IOUT_G+

IAMP

0 TO –12dB

1-POLE

LPF

IOUT_N+

IOUT_N–

IOUT_G–

CLKOUT_1

CLKOUT_2

OSCIN

XTAL

RX+

RX–

04493-0-001

GENERAL DESCRIPTION

The AD9865 is a mixed-signal front end (MxFE) IC for

transceiver applications requiring Tx and Rx path functionality

with data rates up to 80 MSPS. Its flexible digital interface,

power saving modes, and high Tx-to-Rx isolation make it well

suited for half- and full-duplex applications. The digital interface is extremely flexible allowing simple interfaces to digital

back ends that support half- or full-duplex data transfers, thus

often allowing the AD9865 to replace discrete ADC and DAC

solutions. Power saving modes include the ability to reduce

power consumption of individual functional blocks, or to power

down unused blocks in half-duplex applications. A serial port

interface (SPI®) allows software programming of the various

functional blocks. An on-chip PLL clock multiplier and

synthesizer provide all the required internal clocks, as well as

two external clocks from a single crystal or clock source.

The Tx signal path consists of a bypassable 2×/4× low-pass

interpolation filter, a 10-bit TxDAC, and a line driver. The

transmit path signal bandwidth can be as high as 34 MHz at an

input data rate of 80 MSPS. The TxDAC provides differential

current outputs that can be steered directly to an external load

or to an internal low distortion current amplifier. The current

amplifier (IAMP) can be configured as a current- or voltagemode line driver (with two external npn transistors) capable of

delivering in excess of 23 dBm peak signal power. Tx power can

be digitally controlled over a 19.5 dB range in 0.5 dB steps.

The receive path consists of a programmable amplifier

(RxPGA), a tunable low-pass filter (LPF), and a 10-bit ADC.

The low noise RxPGA has a programmable gain range of

−12 dB to +48 dB in 1 dB steps. Its input referred noise is less

than 3 nV/rtHz for gain settings beyond 36 dB. The receive path

LPF cutoff frequency can be set over a 15 MHz to 35 MHz

range or simply bypassed. The 10-bit ADC achieves excellent

dynamic performance over a 5 MSPS to 80 MSPS span. Both

the RxPGA and the ADC offer scalable power consumption

allowing power/performance optimization.

The AD9865 provides a highly integrated solution for many

broadband modems. It is available in a space saving 64-pin chip

scale package and is specified over the commercial (−40°C to

+85°C) temperature range.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

AD9865

TABLE OF CONTENTS

Specifications..................................................................................... 3

TxDAC and IAMP Architecture .............................................. 28

Tx Path Specifications.................................................................. 3

Rx Path Specifications.................................................................. 4

Power Supply Specifications ....................................................... 5

Digital Specifications ................................................................... 6

Serial Port Timing Specifications............................................... 7

Half-Duplex Data Interface (ADIO Port) Timing

Specifications

................................................................................ 7

Full-Duplex Data Interface (Tx and Rx Port) Timing

Specifications

................................................................................ 8

Explanation of Test Levels........................................................... 8

Absolute Maximum Ratings............................................................ 9

Thermal Characteristics .............................................................. 9

ESD Caution.................................................................................. 9

Pin Configuration and Function Descriptions........................... 10

Typical Performance Characteristics ........................................... 12

Rx Path Typical Performance Characteristics ........................ 12

TxDAC Path Typical Performance Characteristics ...............16

IAMP Path Typical Performance Characteristics.................. 18

Serial Port ........................................................................................19

Register Map Description .........................................................21

Serial Port Interface (SPI) ......................................................... 21

Digital Interface ..............................................................................23

Half-Duplex Mode..................................................................... 23

Full-Duplex Mode ...................................................................... 24

RxPGA Control .......................................................................... 25

TxPGA Control ..........................................................................27

Transmi t P a t h .................................................................................. 28

Tx Programmable Gain Control.............................................. 30

TxDAC Output Operation........................................................ 30

IAMP Current-Mode Operation.............................................. 30

IAMP Voltage-Mode Operation .............................................. 31

IAMP Current Consumption Considerations........................ 32

Receive Path .................................................................................... 33

Rx Programmable Gain Amplifier........................................... 33

Low-Pass Filter ........................................................................... 34

Analog-to-Digital Converter (ADC)....................................... 35

AGC Timing Considerations.................................................... 36

Clock Synthesizer........................................................................... 37

Power Control and Dissipation .................................................... 39

Power-Down ............................................................................... 39

Half-Duplex Power Savings ...................................................... 39

Power Reduction Options ......................................................... 40

Power Dissipation ...................................................................... 42

Mode Select upon Power-Up and Reset.................................. 42

Analog and Digital Loop-Back Test Modes............................ 43

PCB Design Considerations.......................................................... 44

Component Placement.............................................................. 44

Power Planes and Decoupling .................................................. 44

Ground Planes ............................................................................ 44

Signal Routing ............................................................................ 44

Evaluation Board ............................................................................ 46

Outline Dimensions ....................................................................... 47

Ordering Guide .......................................................................... 47

Digital Interpolation Filters ......................................................28

REVISION HISTORY

11/04—Data Sheet Changed from Rev. 0 to Rev. A

Changes to Specifications Tables.................................................... 3

Changes to Serial Table.................................................................. 19

Changes to Full Duplex Mode section......................................... 24

Change to TxDAC and IAMP Architecture section.................. 29

Rev. A | Page 2 of 48

Change to TxDAC Output Operation section............................ 30

Insert equation................................................................................ 37

Change to Figure 84 caption ......................................................... 42

11/03—Revision 0: Initial Version

AD9865

SPECIFICATIONS

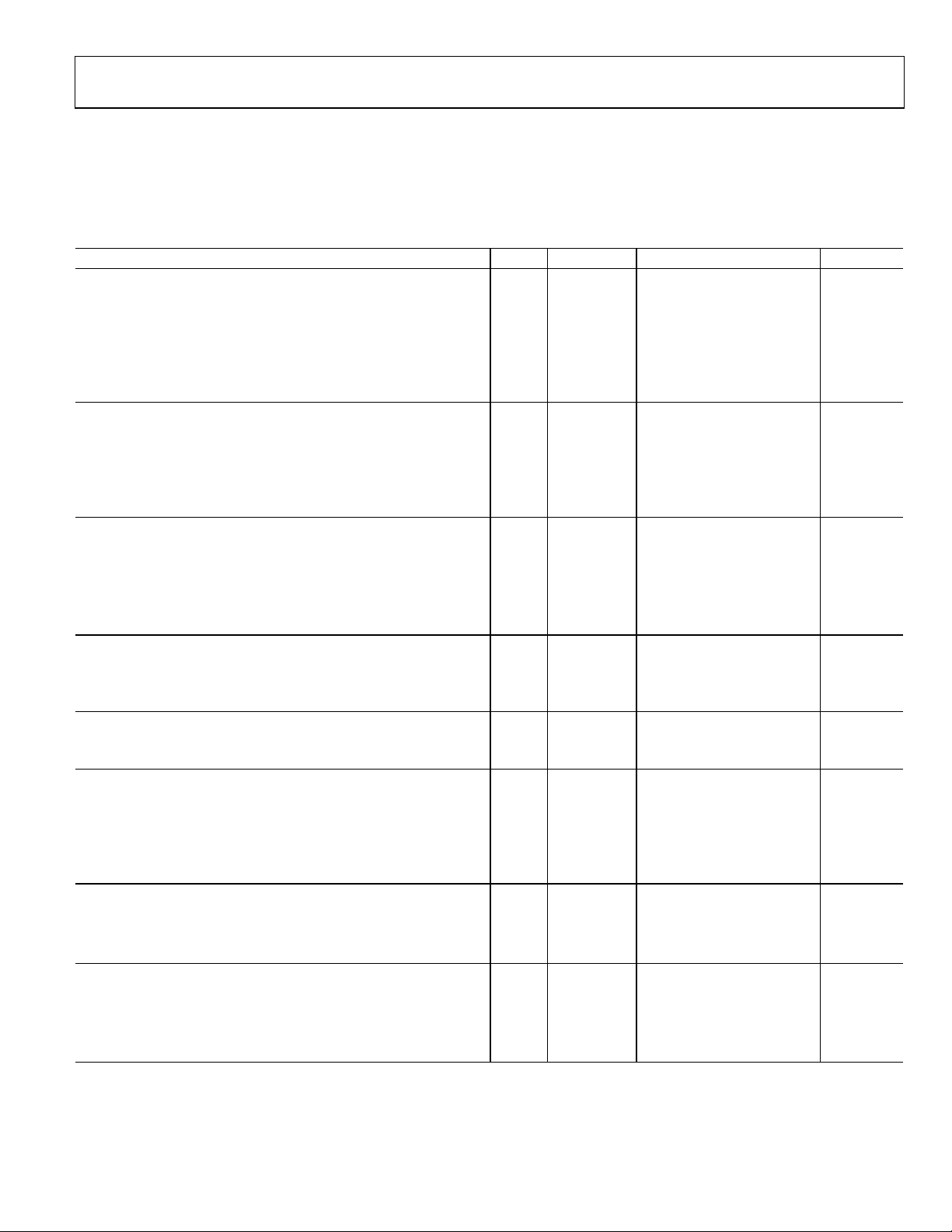

Tx PATH SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%; f

noted.

Table 1.

Parameter Temp Test Level Min Typ Max Unit

TxDAC DC CHARACTERISTICS

Resolution Full 10 Bits

Update Rate Full II 200 MSPS

Full-Scale Output Current (IOUTP_FS) Full IV 2 25 mA

Gain Error

1

Offset Error 25°C V 2 µA

Voltage Compliance Range Full −1 +1.5 V

TxDAC GAIN CONTROL CHARACTERISTICS

Minimum Gain 25°C V −7.5 dB

Maximum Gain 25°C V 0 dB

Gain Step Size 25°C V 0.5 dB

Gain Step Accuracy 25°C IV Monotonic

Gain Range Error 25°C V ±2 dB

TxDAC AC CHARACTERISTICS

2

Fundamental 0.5 dBm

Signal-to-Noise and Distortion (SINAD) Full IV 62.0 63.1 dBc

Signal-to-Noise Ratio (SNR) Full IV 62.5 63.2 dBc

Total Harmonic Distortion (THD) Full IV −77.7 −67.0 dBc

Spurious-Free Dynamic Range (SFDR) Full IV 67.1 79.3 dBc

IAMP DC CHARACTERISTICS

IOUTN Full-Scale Current = IOUTN+ + IOUTN− Full IV 2 105 mA

IOUTG Full-Scale Current = IOUTG+ + IOUTG− Full IV 2 150 mA

AC Voltage Compliance Range Full IV 1 7 V

IAMPN AC CHARACTERISTICS

3

Fundamental 25°C 13 dBm

IOUTN SFDR (Third Harmonic) Full IV 43.3 45.2 dBc

IAMP GAIN CONTROL CHARACTERISTICS

Minimum Gain 25°C V −19.5 dB

Maximum Gain 25°C V 0 dB

Gain Step Size 25°C V 0.5 dB

Gain Step Accuracy 25°C IV Monotonic dB

IOUTN Gain Range Error 25°C V 0.5 dB

REFERENCE

Internal Reference Voltage

4

Reference Error Full V 0.7 3.4 %

Reference Drift Full V 30 ppm/oC

Tx DIGITAL FILTER CHARACTERISTICS (2× Interpolation)

Latency (Relative to 1/f

) Full V 43 Cycles

DAC

−0.2 dB Bandwidth Full V 0.2187 f

−3 dB Bandwidth Full V 0.2405 f

Stop-Band Rejection (0.289 f

to 0.711 f

DAC

) Full V 50 dB

DAC

= 50 MHz, f

OSCIN

= 200 MHz, R

DAC

= 2.0 kΩ, unless otherwise

SET

25°C I ±2 % FS

25°C I 1.23 V

OUT/fDAC

OUT /fDAC

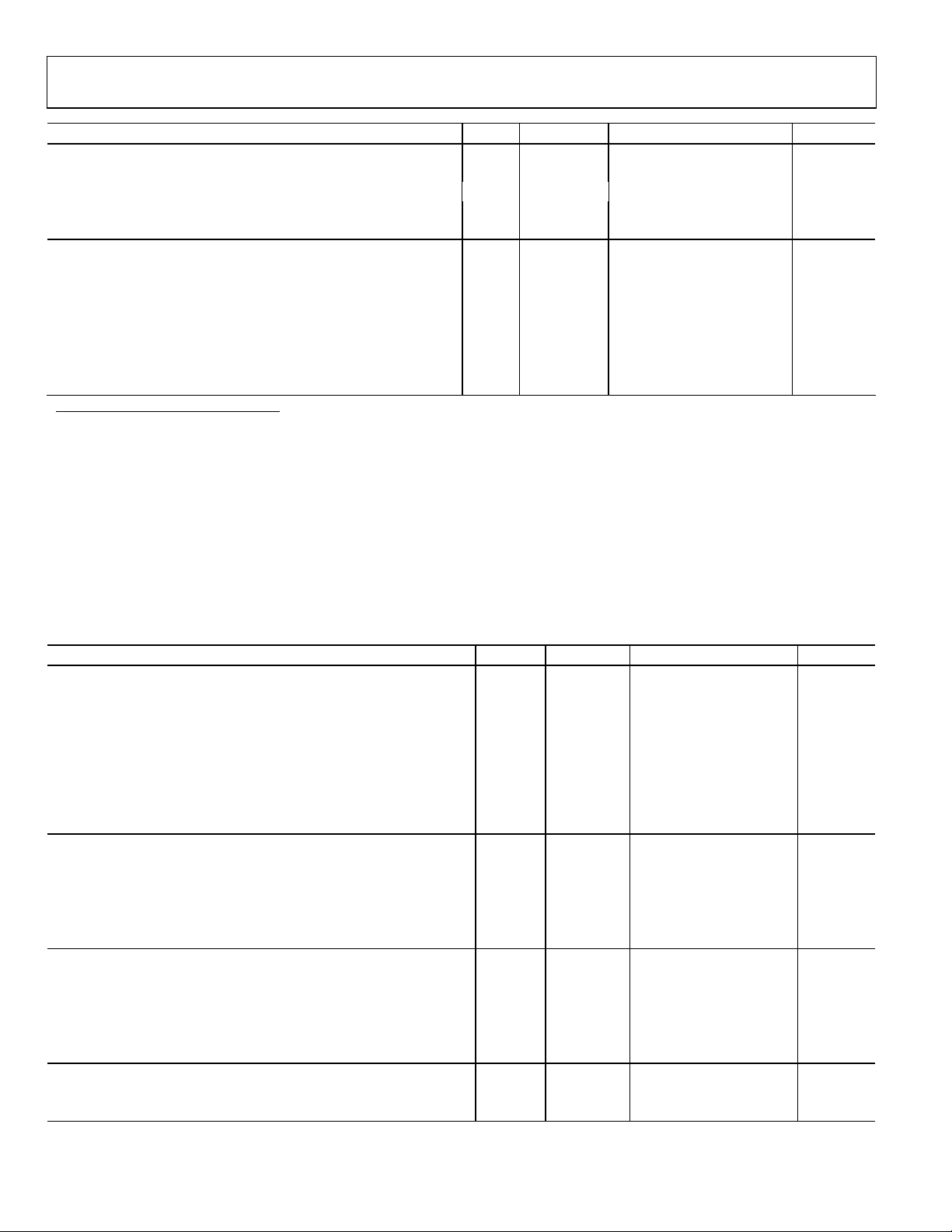

Rev. A | Page 3 of 48

AD9865

Parameter Temp Test Level Min Typ Max Unit

Tx DIGITAL FILTER CHARACTERISTICS (4× Interpolation)

Latency (Relative to 1/ F

−0.2 dB Bandwidth Full V 0.1095 f

−3 dB Bandwidth Full V 0.1202 f

Stop Band Rejection (0.289 f

PLL CLK MULTIPLIER

OSCIN Frequency Range Full IV 5 80 MHz

Internal VCO Frequency Range Full IV 20 200 MHz

Duty Cycle Full II 40 60 %

OSCIN Impedance 25°C V 100//3 ΜΩ/pF

CLKOUT1 Jitter

CLKOUT2 Jitter

5

6

CLKOUT1 and CLKOUT2 Duty Cycle

1

Gain error and gain temperature coefficients are based on the ADC only (with a fixed 1.23 V external reference and a 1 V p-p differential analog input).

2

TxDAC IOUTFS = 20 mA, differential output with 1:1 transformer with source and load termination of 50 Ω, F

3

IOUN full-scale current = 80 mA, f

4

Use external amplifier to drive additional load.

5

Internal VCO operates at 200 MHz , set to divide-by-1.

6

Because CLKOUT2 is a divided down version of OSCIN, its jitter is typically equal to OSCIN.

7

CLKOUT2 is an inverted replica of OSCIN, if set to divide-by-1.

) Full V 96 Cycles

DAC

OUT/fDAC

OUT /fDAC

OSCIN

to 0.711 f

) Full V 50 dB

OSCIN

25°C III 12 ps rms

25°C III 6 ps rms

= 80 MHz, f

OSCIN

7

=160 MHz, 2x interpolation.

DAC

Full III 45 55 %

= 5 MHz, 4x interpolation.

OUT

Rx PATH SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%; half- or full-duplex operation with CONFIG = 0 default power bias

settings, unless otherwise noted.

Table 2.

Parameter Temp Test Level Min Typ Max Unit

Rx INPUT CHARACTERISTICS

Input Voltage Span (RxPGA Gain = −10 dB) Full III 6.33 V p-p

Input Voltage Span (RxPGA Gain = +48 dB) Full III 8 mV p-p

Input Common-Mode Voltage 25°C III 1.3

Differential Input Impedance 25°C III

400

4.0

Input Bandwidth (with RxLPF Disabled, RxPGA = 0 dB) 25°C III 53 MHz

Input Voltage Noise Density (RxPGA Gain = 36 dB, f

Input Voltage Noise Density (RxPGA Gain = 48 dB, f

= 26 MHz) 25°C III 3.0 nV/rtHz

−3 dBF

−3 dBF

= 26 MHz)

25°C III 2.4 nV/rtHz

RxPGA CHARACTERISTICS

Minimum Gain 25°C III −12 dB

Maximum Gain 25°C III 48 dB

Gain Step Size 25°C III 1 dB

Gain Step Accuracy 25°C III Monotonic dB

Gain Range Error 25°C III 0.5 dB

RxLPF CHARACTERISTICS

Cutoff Frequency (f

Attenuation at 55.2 MHz with f

) Range Full III 15 35 MHz

−3 dBF

= 21 MHz 25°C III 20 dB

−3 dBF

Pass-Band Ripple 25°C III ±1 dB

Settling Time to 5 dB RxPGA Gain Step @ f

Settling Time to 60 dB RxPGA Gain Step @ f

= 50 MSPS 25°C III 20 ns

ADC

= 50 MSPS 25°C III 100 ns

ADC

ADC DC CHARACTERISTICS

Resolution NA NA 10 Bits

Conversion Rate Full II 5 80 MSPS

V

Ω

pF

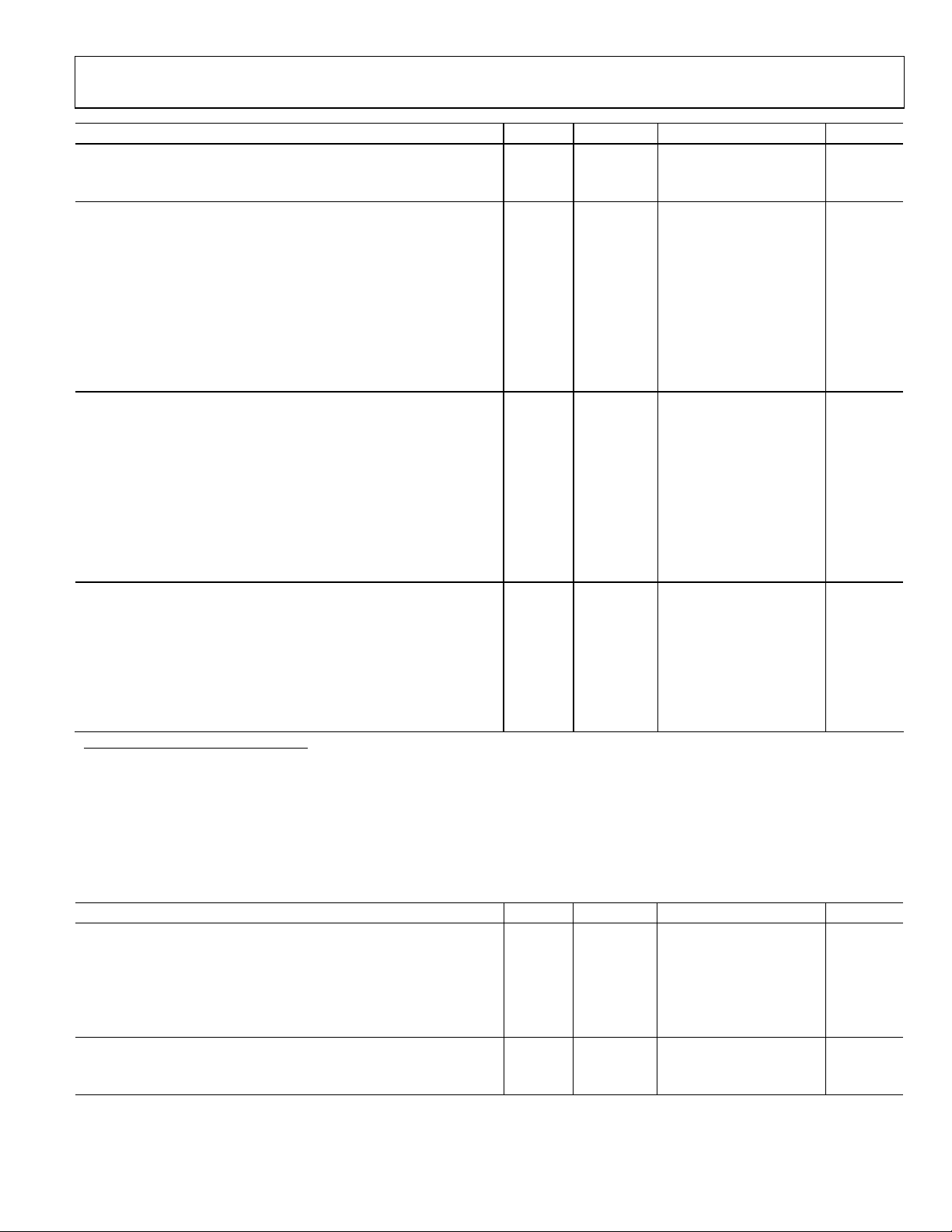

Rev. A | Page 4 of 48

AD9865

Parameter Temp Test Level Min Typ Max Unit

Rx PATH LATENCY1

Full-Duplex Interface Full V 10.5 Cycles

Half-Duplex Interface Full V 10.0 Cycles

Rx PATH COMPOSITE AC PERFORMANCE @ f

= 50 MSPS

ADC

RxPGA Gain = 48 dB (Full-Scale = 8.0 mV p-p)

Signal-to-Noise and Distortion (SNR) 25°C III 43.7 dBc

Total Harmonic Distortion (THD) 25°C III −71 dBc

RxPGA Gain = 24 dB (Full-Scale =126 mV p-p)

Signal-to-Noise (SNR) 25°C III 59 dBc

Total Harmonic Distortion (THD) 25°C III −67.2 dBc

RxPGA Gain = 0 dB (Full-Scale = 2.0 V p-p)

Signal-to-Noise and Distortion (SINAD) Full IV 58 59 dBc

Total Harmonic Distortion (THD) Full IV −66 −62.9 dBc

Rx PATH COMPOSITE AC PERFORMANCE @ f

= 80 MSPS3

ADC

RxPGA Gain = 48 dB (Full-Scale = 8.0 mV p-p)

Signal-to-Noise (SNR) 25°C III 41.8 dBc

Total Harmonic Distortion (THD) 25°C III −67 dBc

RxPGA Gain = 24 dB (Full-Scale = 126 mV p-p)

Signal-to-Noise (SNR) 25°C III 58.6 dBc

Total Harmonic Distortion (THD) 25°C III −62.9 dBc

RxPGA Gain = 0 dB (Full-Scale = 2.0 V p-p)

Signal-to-Noise (SNR) 25°C II 58.9 59.6 dBc

Total Harmonic Distortion (THD) 25°C II −69.7 −59.8 dBc

Rx-to-Tx PATH FULL-DUPLEX ISOLATION

(1 V p-p, 10 MHz Sine Wave Tx Output)

RxPGA Gain = 40 dB

IOUTP± Pins to RX± Pins 25°C III 83 dBc

IOUTG± Pins to RX± Pins 25°C III 37 dBc

RxPGA Gain = 0 dB

IOUTP± Pins to RX± Pins 25°C III 123 dBc

IOUTG± Pins to RX± Pins 25°C III 77 dBc

1

Includes RxPGA, ADC pipeline, and ADIO bus delay relative to f

2

fIN = 5 MHz, AIN = −1.0 dBFS , LPF cutoff frequency set to 15.5 MHz with Reg. 0x08 = 0x80.

3

fIN = 5 MHz, AIN = −1.0 dBFS , LPF cutoff frequency set to 26 MHz with Reg. 0x08 = 0x80.

POWER SUPPLY SPECIFICATIONS

AVDD = 3.3 V, DVDD = CLKVDD = DRVDD = 3.3 V; R

Table 3.

Parameter Temp Test Level Min Typ Max Unit

SUPPLY VOLTAGES

AVDD Full V 3.135 3.3 3.465 V

CLKVDD Full V 3.0 3.3 3.6 V

DVDD Full V 3.0 3.3 3.6 V

DRVDD Full V 3.0 3.3 3.6 V

IS_TOTAL (Total Supply Current) Full II 406 475 mA

POWER CONSUMPTION

I

+ I

AVDD

I

+ I

DVDD

(Analog Supply Current)

CLKVDD

(Digital Supply Current) Full IV 95 133 mA

DRVDD

2

.

ADC

= 2 kΩ, full-duplex operation with f

SET

= 80 MSPS,1 unless otherwise noted.

DATA

IV 311 342 mA

Rev. A | Page 5 of 48

AD9865

Parameter Temp Test Level Min Typ Max Unit

POWER CONSUMPTION (Half-Duplex Operation with f

Tx Mode

I

+ I

AVDD

CLKVDD

I

+ I

DVDD

DRVDD

Rx Mode

I

+ I

AVDD

CLKVDD

I

+ I

DVDD

DRVDD

POWER CONSUMPTION OF FUNCTIONAL BLOCKS1 (I

RxPGA and LPF 25°C III 87 mA

ADC 25°C III 108 mA

TxDAC 25°C III 38 mA

IAMP (Programmable) 25°C III 10 120 mA

Reference 25°C III 170 mA

CLK PLL and Synthesizer 25°C III 107 mA

MAXIMUM ALLOWABLE POWER DISSIPATION Full IV 1.66 W

STANDBY POWER CONSUMPTION

IS_TOTAL (Total Supply Current) Full

POWER DOWN DELAY (USING PWR_DWN PIN)

RxPGA and LPF 25°C III 440 ns

ADC 25°C III 12 ns

TxDAC 25°C III 20 ns

IAMP 25°C III 20 ns

CLK PLL and synthesizer 25°C III 27 ns

POWER UP DELAY (USING PWR_DWN PIN)

RxPGA and LPF 25°C III 7.8 µs

ADC 25°C III 88 ns

TxDAC 25°C III 13 µs

IAMP 25°C III 20 ns

CLK PLL and Synthesizer 25°C III 20 µs

1

Default power-up settings for MODE = HIGH and CONFIG = LOW, IOUTP_FS = 20 mA, does not include IAMP’s current consumption, which is application dependent.

2

Default power-up settings for MODE = LOW and CONFIG = LOW.

DIGITAL SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%; R

Table 4.

Parameter Temp Test Level Min Typ Max Unit

CMOS LOGIC INPUTS

High Level Input Voltage Full VI DRVDD – 0.7 V

Low Level Input Voltage Full VI 0.4 V

Input Leakage Current 12 µA

Input Capacitance Full VI 3 pF

CMOS LOGIC OUTPUTS (C

High Level Output Voltage (IOH = 1 mA) Full VI DRVDD – 0.7 V

Low Level Output Voltage (IOH = 1 mA) Full VI 0.4 V

Output Rise/Fall Time (High Strength Mode and C

Output Rise/Fall Time (Low Strength Mode and C

Output Rise/Fall Time (High Strength Mode and C

Output Rise/Fall Time (Low Strength Mode and C

RESET

Minimum Low Pulse Width (Relative to f

= 5 pF)

LOAD

) 1

ADC

= 50 MSPS)2

DATA

25°C IV 112 130 mA

25°C IV 46 49.5 mA

25°C IV 225 253 mA

25°C IV 36.5 39 mA

+ I

AVDD

= 15 pF) Full VI 1.5/2.3 ns

LOAD

= 15 pF) Full VI 1.9/2.7 ns

LOAD

= 5 pF) Full VI 0.7/0.7 ns

LOAD

= 5 pF) Full VI 1.0/1.0 ns

LOAD

)

CLKVDD

= 2 kΩ, unless otherwise noted.

SET

13 mA

Clock

cycles

Rev. A | Page 6 of 48

AD9865

SERIAL PORT TIMING SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%, unless otherwise noted.

Table 5.

Parameter Temp Test Level Min Typ Max Unit

WRITE OPERATION (See Figure 46)

SCLK Clock Rate (f

SCLK Clock High (tHI) Full IV 14 ns

SCLK Clock Low (t

SDIO to SCLK Setup Time (tDS) Full IV 14 ns

SCLK to SDIO Hold Time (tDH) Full IV 0 ns

SEN to SCLK Setup Time (tS)

SCLK to SEN Hold Time (tH)

READ OPERATION (See Figure 47 and Figure 48)

SCLK Clock Rate (f

SCLK Clock High (tHI) Full IV 14 ns

SCLK Clock Low (t

SDIO to SCLK Setup Time (tDS) Full IV 14 ns

SCLK to SDIO Hold Time (tDH) Full IV 0 ns

SCLK to SDIO (or SDO) Data Valid Time (tDV) Full IV 14 ns

SEN to SDIO Output Valid to Hi-Z (tEZ)

) Full IV 32 MHz

SCLK

) Full IV 14 ns

LOW

Full IV 14 ns

Full IV 0 ns

) Full IV 32 MHz

SCLK

) Full IV 14 ns

LOW

Full IV 2 ns

HALF-DUPLEX DATA INTERFACE (ADIO PORT) TIMING SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%, unless otherwise noted.

Table 6.

Parameter Temp Test Level Min Typ Max Unit

READ OPERATION1 (See Figure 50)

Output Data Rate Full II 5 80 MSPS

Three-State Output Enable Time (t

Three-State Output Disable Time (t

) Full II 3 ns

PZL

) Full II 3

PLZ

Rx Data Valid Time (tVT) Full II 1.5 ns

Rx Data Output Delay (tOD) Full II 4 ns

WRITE OPERATION (See Figure 49)

Input Data Rate (1× Interpolation) Full II 20 80 MSPS

Input Data Rate (2× Interpolation) Full II 10 80 MSPS

Input Data Rate (4× Interpolation) Full II 5 50 MSPS

Tx Data Setup Time (tDS) Full II 1 ns

Tx Data Hold Time (tDH) Full II 2.5 ns

Latch Enable Time (tEN) Full II 3 ns

Latch Disable Time (t

) Full II 3 ns

DIS

1

C

= 5 pF for digital data outputs.

LOAD

ns

Rev. A | Page 7 of 48

AD9865

FULL-DUPLEX DATA INTERFACE (Tx AND Rx PORT) TIMING SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%, unless otherwise noted.

Table 7.

Parameter Temp Test Level Min Typ Max Unit

Tx PATH INTERFACE (See Figure 53)

Input Nibble Rate (2× Interpolation) Full II 20 160 MSPS

Input Nibble Rate (4× Interpolation) Full II 10 100 MSPS

Tx Data Setup Time (tDS) Full II 2.5 ns

Tx Data Hold Time (tDH) Full II 1.5 ns

Rx PATH INTERFACE1 (See Figure 54)

Output Nibble Rate Full II 10 160 MSPS

Rx Data Valid Time (tDV) Full II 3 ns

Rx Data Hold Time (tDH) Full II 0 ns

1

C

=5 pF for digital data outputs.

LOAD

EXPLANATION OF TEST LEVELS

I 100% production tested.

II 100% production tested at 25°C and guaranteed by design and characterization at specified temperatures.

III Sample tested only.

IV Parameter is guaranteed by design and characterization testing.

V Parameter is a typical value only.

VI 100% production tested at 25°C and guaranteed by design and characterization for industrial temperature range.

Rev. A | Page 8 of 48

AD9865

ABSOLUTE MAXIMUM RATINGS

Table 8.

Parameter Rating

ELECTRICAL

AVDD, CLKVDD Voltage 3.9 V maximum

DVDD, DRVDD Voltage 3.9 V maximum

RX+, RX−, REFT, REFB −0.3 V to AVDD + 0.3 V

IOUTP+, IOUTP− −1.5 V to AVDD + 0.3 V

IOUTN+, IOUTN−, IOUTG+,

IOUTG−

OSCIN, XTAL −0.3 V to CLVDD + 0.3 V

REFIO, REFADJ −0.3 V to AVDD + 0.3 V

Digital Input and Output Voltage −0.3 V to DRVDD + 0.3 V

Digital Output Current 5 mA maximum

ENVIRONMENTAL

Operating Temperature Range

(Ambient)

Maximum Junction Temperature 125°C

Lead Temperature (Soldering, 10 s) 150°C

Storage Temperature Range

(Ambient)

−0.3 V to +7 V

−40°C to +85°C

−65°C to +150°C

Stresses above those listed under the Absolute Maximum

Ratings may cause permanent damage to the device. This is a

stress rating only; functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

Thermal Resistance: 64-lead LFCSP (4-layer board).

= 24°C/W (paddle soldered to ground plane, 0 LPM air).

θ

JA

= 30.8°C/W (paddle not soldered to ground plane,

θ

JA

0 LPM air).

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. A | Page 9 of 48

AD9865

T

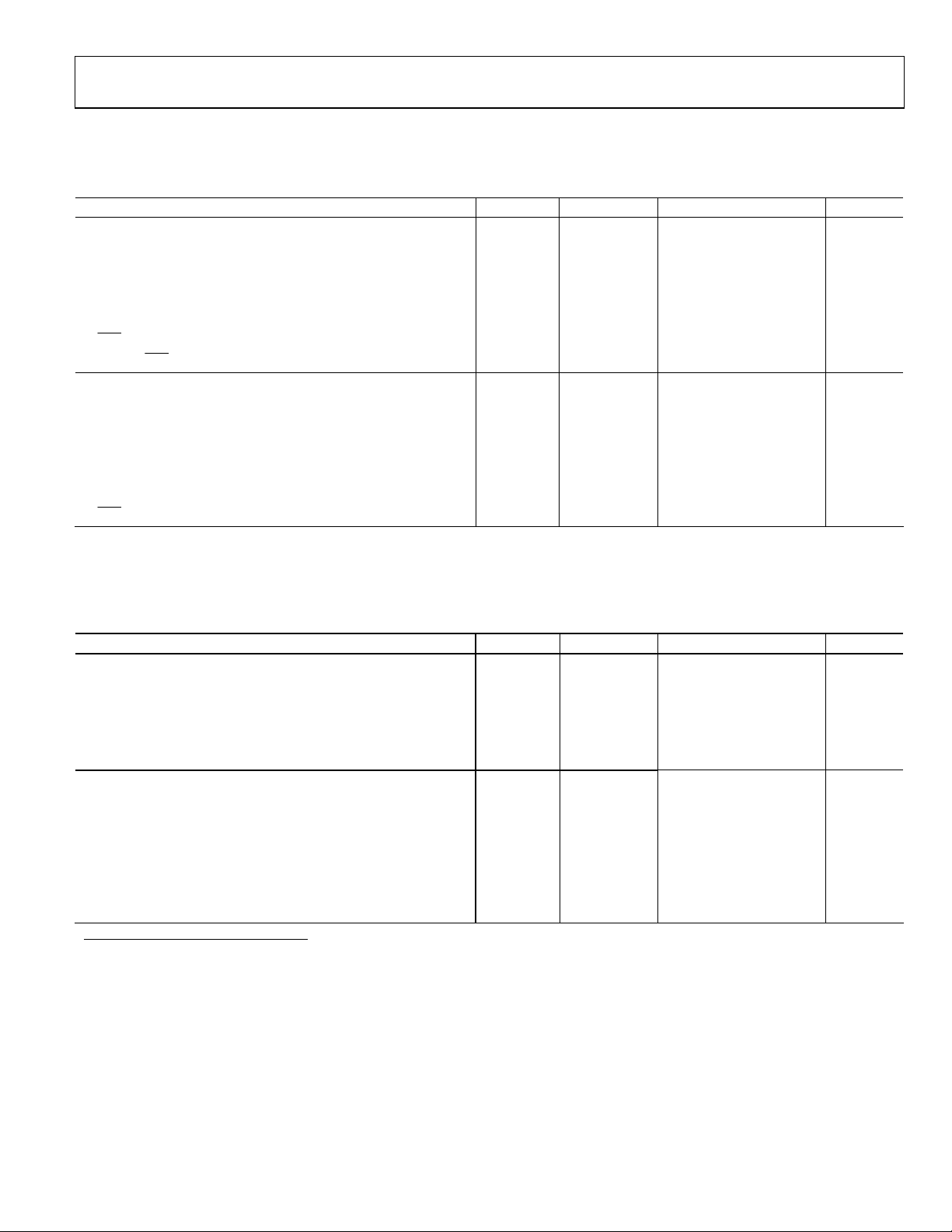

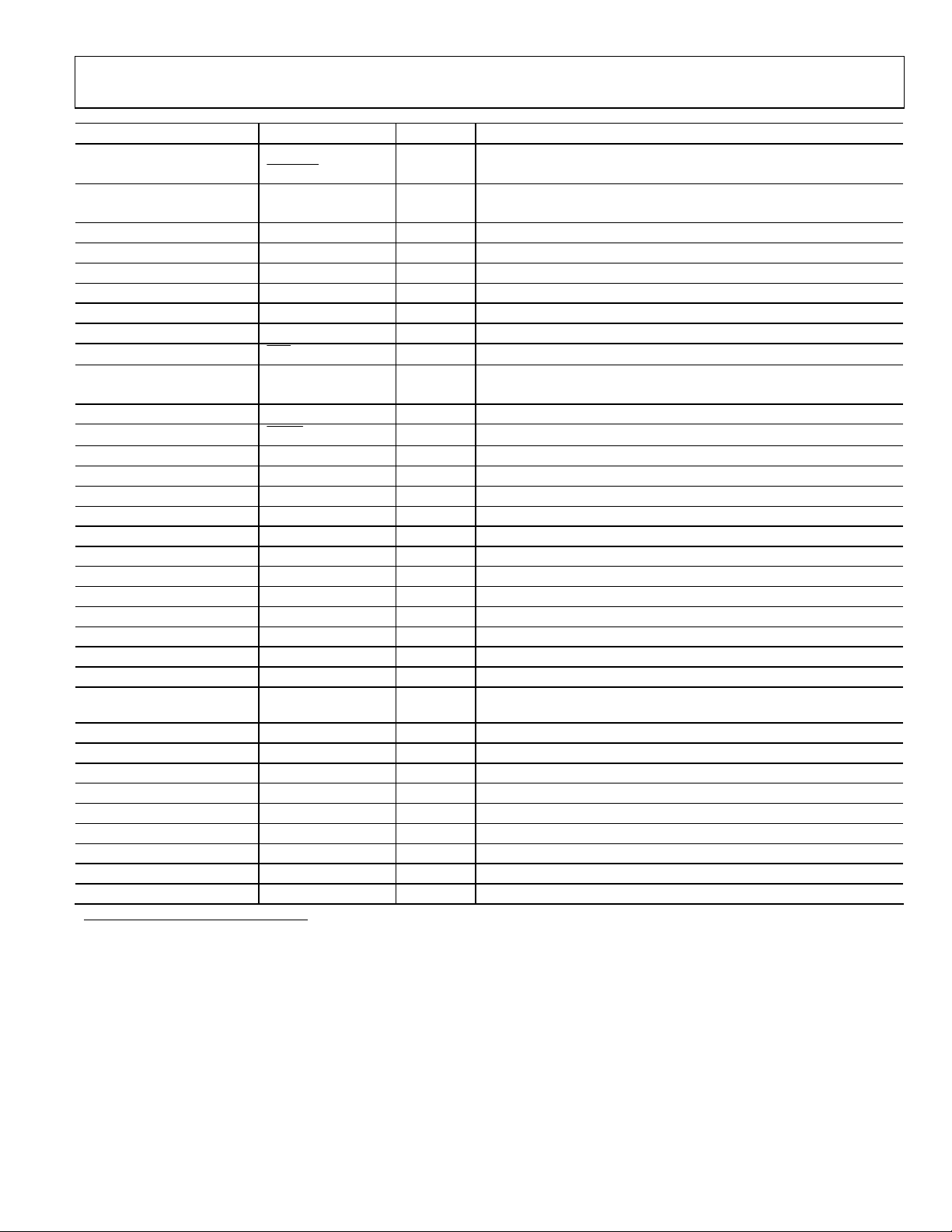

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

DRVDD

DRVSS

PWR_DWN

CLKOUT2

DVDD

DVSS

CLKVDD

OSCIN

XTAL

CLKVSS

CONFIG

ADIO9/Tx[5]

ADIO8/Tx[4]

ADIO7/Tx[3]

ADIO6/Tx[2]

ADIO5/Tx[1]

ADIO4/Tx[0]

ADIO3/Rx[5]

ADIO2/Rx[4]

ADIO1/Rx[3]

ADIO0/Rx[2]

NC/Rx[1]

NC/Rx[0]

RXEN/RXSYNC

TXEN/TXSYNC

XCLK/TXQUIET

RXCLK

64

63 62 61 60 595857 56 55 54 535251 50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

PIN 1

IDENTIFIER

AD9865

TOP VIEW

(Not to Scale)

MODE

IOUT_P–

IOUT_P+

IOUT_G+

IOUT_N+

49

3217 18 19 20 21 22 23 24 25 26 27 282930 31

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

AVSS

AVSS

IOUT_N–

IOUT_G–

AVSS

AVDD

REFIO

REFADJ

AVDD

AVSS

RX+

RX–

AVSS

AVDD

AVSS

REFT

DRVDD

DRVSS

CLKOUT1

SCLK

PGA[4]

PGA[3]

GAIN/PGA[5]

PGA[0]

PGA[2]

PGA[1]

RESET

AVSS

REFB

SEN

SDO

SDIO

Figure 2. Pin Configuration

Table 9. Pin Function Descriptions

Pin No. Mnemonic Mode

1

Description

1 ADIO9 HD MSB of ADIO Buffer

Tx[5] FD MSB of Tx Nibble Input

2 to 5 ADIO8 to 5 HD Bits 8 to 5 of ADIO Buffer

Tx[4 to 1] FD Bits 4 to 1 of Tx Nibble Input

6 ADIO4 HD Bit 4 of ADIO Buffer

Tx[0] FD LSB of Tx Nibble Input

7 ADIO3 HD Bit 3 of ADIO Buffer

Rx[5] FD MSB of Rx Nibble Output

8, 9 ADIO2, 1 HD Bits 2 to 1 of ADIO Buffer

Rx[4, 3] FD Bits 4 to 3 of Rx Nibble Output

10 ADIO0 HD LSB of ADIO Buffer

Rx[2] FD Bit 2 of Rx Nibble Output

11 NC HD No Connect

Rx[1] FD Bit 1 of Rx Nibble Output

12 NC HD No Connect

Rx[0] FD LSB of Rx Nibble Output

13 RXEN HD ADIO Buffer Control Input

RXSYNC FD Rx Data Synchronization Output

14 TXEN HD Tx Path Enable Input

TXSYNC FD Tx Data Synchronization Input

4493-0-002

Rev. A | Page 10 of 48

AD9865

Pin No. Mnemonic Mode

1

Description

15 TXCLK HD ADIO Sample Clock Input

TXQUIET

FD Fast TxDAC/IAMP Power-Down

16 RXCLK HD ADIO Request Clock Input

FD Rx and Tx Clock Output at 2 x f

ADC

17, 64 DRVDD Digital Output Driver Supply Input

18, 63 DRVSS Digital Output Driver Supply Return

19 CLKOUT1

f

/N Clock Output (L = 1, 2, 4, or 8)

ADC

20 SDIO Serial Port Data Input/Output

21 SDO Serial Port Data Output

22 SCLK Serial Port Clock Input

23

SEN

Serial Port Enable Input

24 GAIN FD Tx Data Port (Tx[5:0]) Mode Select

PGA[5] HD or FD MSB of PGA Input Data Port

25 to 29 PGA[4 to 0] HD or FD Bits 4 to 0 of PGA Input Data Port

30

RESET

Reset Input (Active Low)

31, 34, 36, 39, 44, 47, 48 AVSS Analog Ground

32, 33 REFB, REFT ADC Reference Decoupling Nodes

35, 40, 43 AVDD Analog Power Supply Input

37, 38 RX−, RX+ Receive Path − and + Analog Inputs

41 REFADJ TxDAC Full-Scale Current Adjust

42 REFIO TxDAC Reference Input/Output

45 IOUT_G− −Tx Amp Current Output_Sink

46 IOUT_N− −Tx Mirror Current Output_Sink

49 IOUT_G+ +Tx Amp Current Output_Sink

50 IOUT_N+ +Tx Mirror Current Output_Sink

51 IOUT_P− −TxDAC Current Output_Source

52 IOUT_P+ +TxDAC Current Output_Source

53 MODE

Digital Interface Mode Select Input

LOW = HD, HIGH = FD

54 CONFIG Power-Up SPI Register Default Setting Input

55 CLKVSS Clock Oscillator/Synthesizer Supply Return

56 XTAL Crystal Oscillator Inverter Output

57 OSCIN Crystal Oscillator Inverter Input

58 CLKVDD Clock Oscillator/Synthesizer Supply

59 DVSS Digital Supply Return

60 DVDD Digital Supply Input

61 CLKOUT2

f

/L Clock Output, (L = 1, 2, or 4)

OSCIN

62 PWR_DWN Power-Down Input

1

HD = half-duplex mode; FD = full-duplex mode.

Rev. A | Page 11 of 48

AD9865

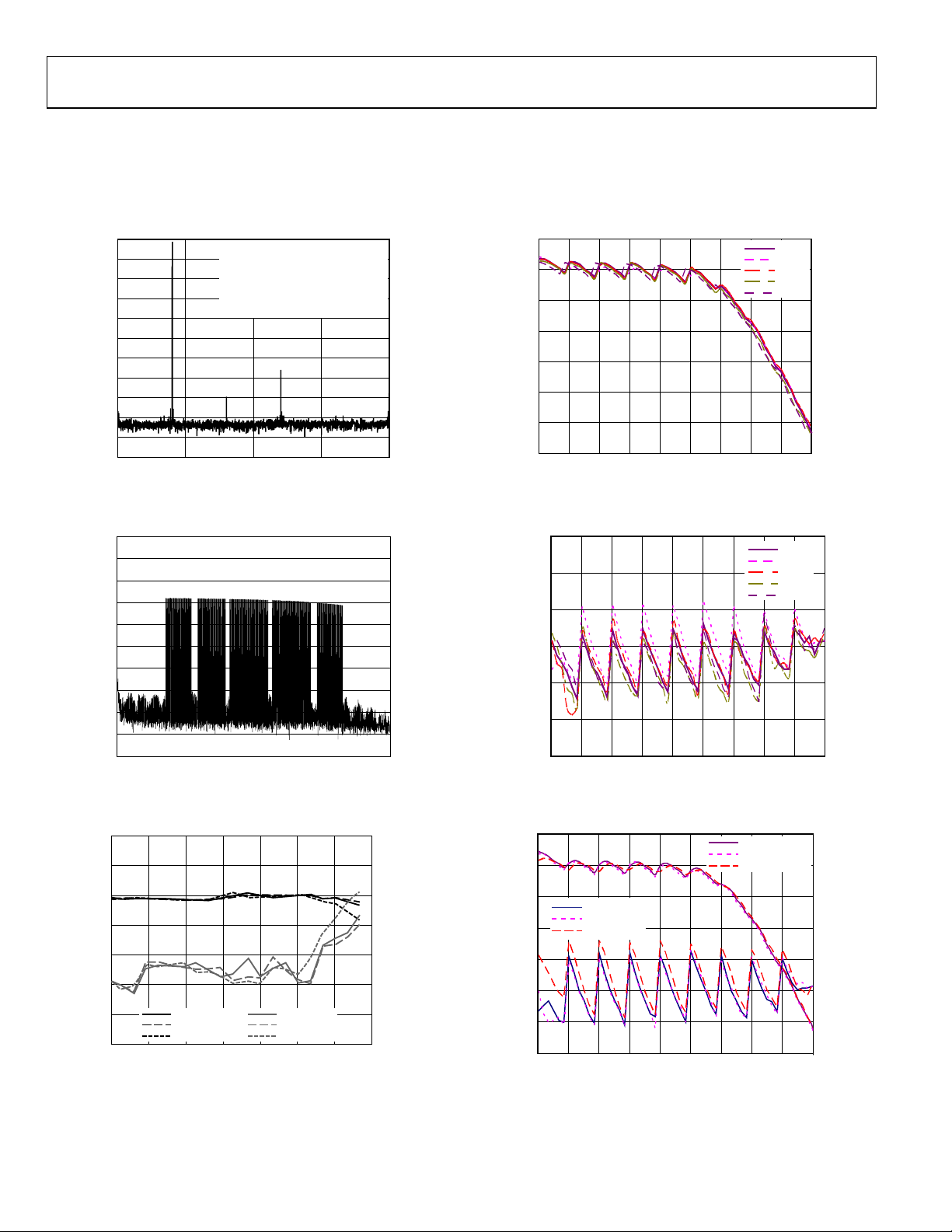

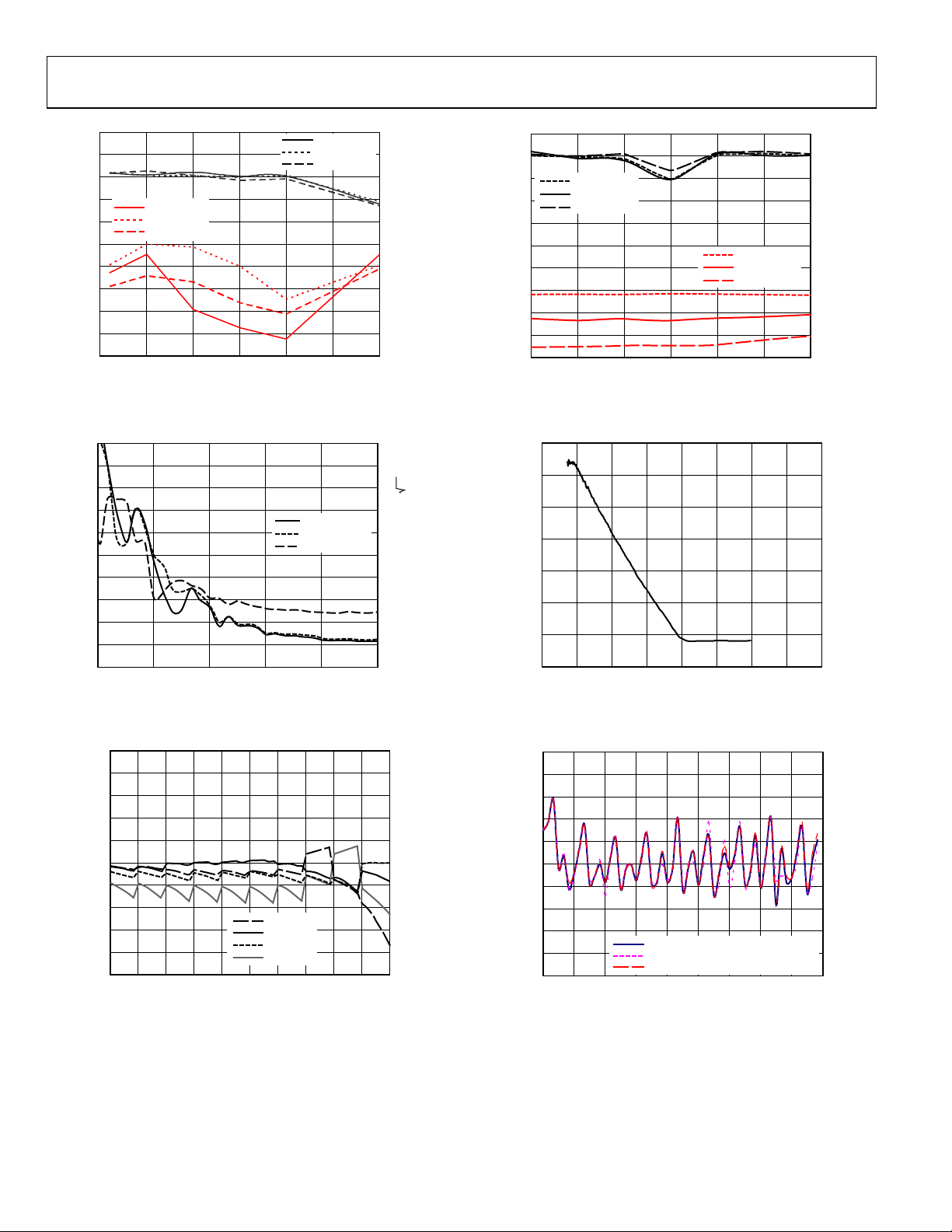

TYPICAL PERFORMANCE CHARACTERISTICS

Rx PATH TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f

RIN = 50 Ω, half- or full-duplex interface, default power bias settings.

10

0

–10

–20

–30

–40

–50

–60

–70

–80

INPUT REFERRED SPECTRUM (dBm)

–90

–100

0 6.25 12.50 18.75 25.00

Figure 3. Spectral Plot with 4 k FFT of Input Sinusoid with

RxPGA = 0 dB and P

–30

–40

–50

–60

–70

–80

–90

–100

–110

INPUT REFERRED SPECTRUM (dBm)

–120

–130

0 5 10 15 20 25

Figure 4. Spectral Plot with 4 k FFT of 84-Carrier DMT Signal

with PAR = 10.2 dB, P

66

63

FUND = –1dBFS

SINAD = 59.1dBFS

ENOB = 9.53 BITS

SNR = 60.2dBFS

THD = –65.2dBFS

SFDR = –64.9dBc (THIRD HARMONIC)

RBW = 12.21kHz

FREQUENCY (MHz)

= 9 dBm

IN

RBW = 12.2kHz

FREQUENCY (MHz)

= −33.7 dBm, and RxPGA = 36 dB

IN

OSCIN

= f

= 50 MSPS, low-pass filter’s f

ADC

04493-0-040

04493-0-041

–50

–56

= 22 MHz, AIN = −1 dBFS,

−3 dB

62

59

56

53

50

SINAD (dBFS)

47

44

41

–6 0 6 12 18 24 30 36 42 48

RxPGA GAIN (dB)

Figure 6. SINAD/ENOB vs. RxPGA Gain and Frequency

–55

–60

–65

–70

THD (dBFC)

–75

–80

–85

–6 0 6 12 18 24 30 36 42 48

RxPGA GAIN (dB)

Figure 7. THD vs. RxPGA Gain and Frequency

62

59

SINAD @ +25°C

SINAD @ +85°C

SINAD @ –40°C

1MHz

5MHz

10MHz

15MHz

20MHz

1MHz

5MHz

10MHz

15MHz

20MHz

10.0

9.5

9.0

8.5

8.0

7.5

7.0

6.5

–45

–50

ENOB (Bits)

04493-0-043

04493-0-044

60

57

54

SINAD (dBFS)

51

48

45

–21 –18 –15 –12 –9 –6 –3 0

SINAD @ 3.14V

SINAD @ 3.3V

SINAD @ 3.46V

INPUT AMPLITUDE (dBFS)

0dBFS = 2V p-p

THD @ 3.14V

THD @ 3.3V

THD @ 3.46V

Figure 5. SINAD and THD vs. Input Amplitude and Supply

= 8 MHz, LPF f

(f

IN

= 26 MHz; Rx PGA = 0 dB)

−3 dB

–62

–68

–74

THD (dBFS)

–80

–86

04493-0-042

–92

Rev. A | Page 12 of 48

56

53

50

SINAD (dBFS)

47

44

41

–6 0 6 12 18 24 30 36 42 48

THD @ +25°C

THD @ +85°C

THD @ –40°C

RxPGA GAIN (dB)

Figure 8. SINAD/THD Performance vs. RxPGA Gain

and Temperature ( f

= 5 MHz)

IN

–55

–60

–65

–70

–75

–80

THD (dBc)

04493-0-045

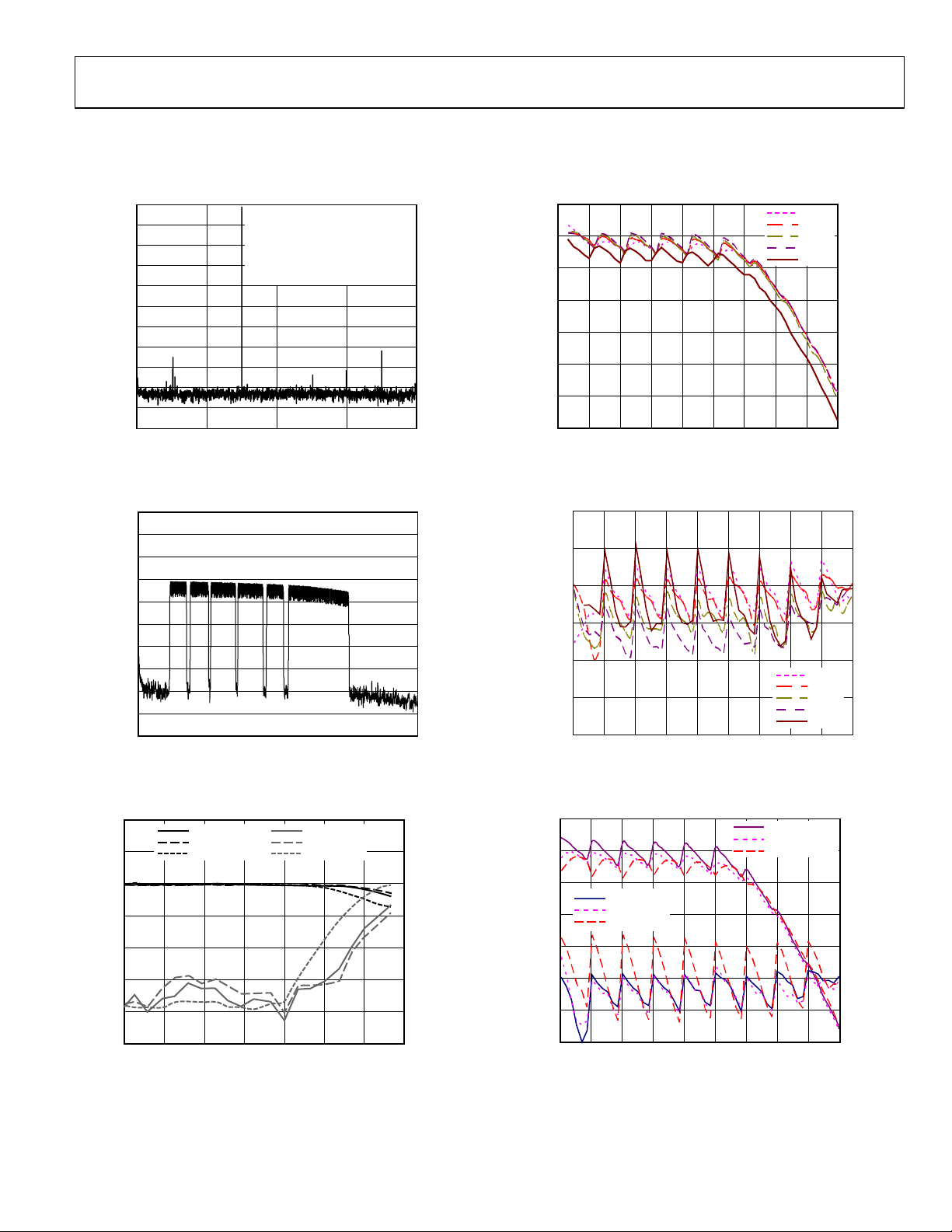

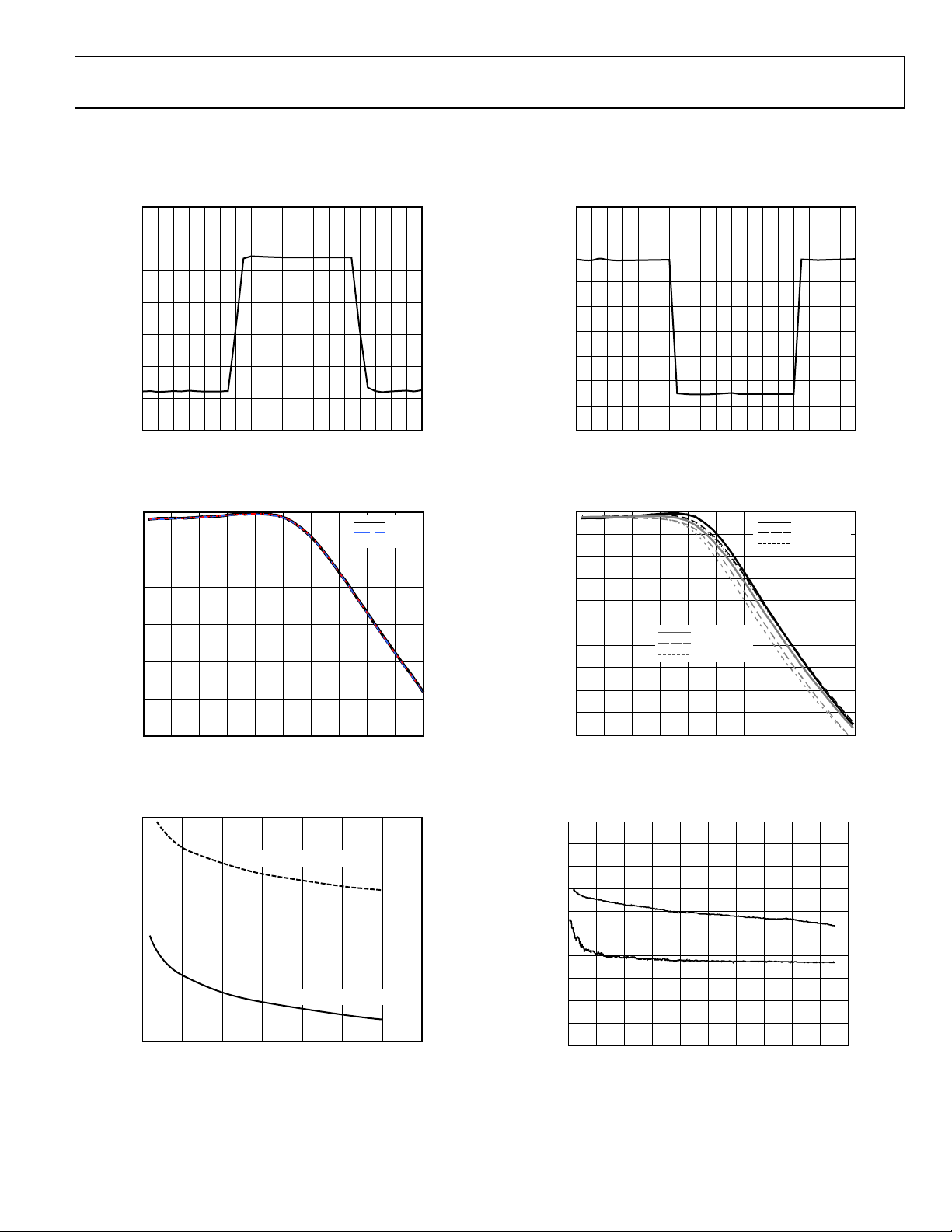

AD9865

–

–

Rx PATH TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f

RIN = 50 Ω, half- or full-duplex interface, default power bias settings.

10

0

–10

–20

–30

–40

–50

–60

–70

–80

INPUT REFERRED SPECTRUM (dBm)

–90

–100

0 1020304

Figure 9. Spectral Plot with 4k FFT of Input Sinusoid

with RxPGA = 0 dB and P

–30

–40

–50

–60

–70

–80

–90

–100

–110

INPUT REFERRED SPECTRUM (dBm)

–120

–130

0 1020304

Figure 10. Spectral Plot with 4k FFT of 111-Carrier DMT Signal with

PAR = 11 dB, P

66

63

= −33.7 dBm, LPF f

IN

SINAD @ 3.14V

SINAD @ 3.3V

SINAD @ 3.46V

FUND = –1dBFS

SINAD = 59.3dBFS

ENOB = 9.56 BITS

SNR = 59.8dBFS

THD = –69.1dBFS

SFDR = –70.3dBc (THIRD HARMONIC)

RBW = 19.53kHz

FREQUENCY (MHz)

= 9 dBm

IN

RBW = 19.53kHz

FREQUENCY (MHz)

= 32 MHz, and RxPGA = 36 dB

−3 dB

THD @ 3.14V

THD @ 3.3V

THD @ 3.46V

OSCIN

= f

= 80 MSPS, low-pass filter’s f

ADC

04493-0-046

0

04493-0-047

0

–50

–56

= 30 MHz, AIN = −1 dBFS,

−3 dB

62

59

56

53

50

SINAD (dBFS)

47

44

41

–6 0 6 12 18 24 30 36 42 48

RxPGA GAIN (dB)

Figure 12. SINAD/ENOB vs. RxPGA Gain and Frequency

55

–60

–65

–70

THD (dBc)

–75

–80

–85

–6 0 6 12 18 24 30 36 42 48

RxPGA GAIN (dB)

Figure 13. THD vs. RxPGA Gain and Frequency

62

59

SINAD @ +25°C

SINAD @ +85°C

SINAD @ –40°C

5MHz

10MHz

15MHz

20MHz

30MHz

5MHz

10MHz

15MHz

20MHz

30MHz

10.0

9.5

9.0

8.5

8.0

7.5

7.0

6.5

–45

ENOB (Bits)

04493-0-049

04493-0-050

40

60

57

54

SINAD (dBFS)

51

48

45

–21 –18 –15 –12 –9 –6 –3 0

INPUT AMPLITUDE (dBFS)

0dBFS = 2V p-p

Figure 11. SINAD and THD vs. Input Amplitude and Supply

= 8 MHz, LPF f

(f

IN

= 26 MHz; RxPGA = 0 dB)

−3 dB

–62

–68

–74

–80

–86

–92

THD (dBFS)

04493-0-048

56

53

50

SINAD (dBFS)

47

44

41

–6 0 6 12 18 24 30 36 42 48

THD @ +25°C

THD @ +85°C

THD @ –40°C

RxPGA GAIN (dB)

Figure 14. SINAD/THD Performance vs. RxPGA Gain and Temperature

= 10 MHz)

( f

IN

–50

–55

–60

–65

–70

–75

THD (dBc)

04493-0-051

Rev. A | Page 13 of 48

AD9865

–

61.0

60.5

60.0

59.5

59.0

58.5

58.0

SNR (dBFS)

57.5

57.0

56.5

56.0

–6 0 6 12 18 24 30 36 42 48

THD @ 3.13V

THD @ 3.3V

THD @ 3.47V

INPUT FREQUENCY (MHz)

SNR @ 3.13V

SNR @ 3.3V

SNR @ 3.47V

Figure 15. SNR and THD vs. Input Frequency and Supply

= 26 MHz; RxPGA = 0 dB)

( LPF f

−3 dB

109.4

98.5

87.5

76.6

65.6

54.7

43.8

32.8

INTEGRATED NOISE (µV rms)

21.9

10.9

0

–6 0 6 12 18 24 30 36 42 48

RxPGA GAIN (dB)

AD9865: +25°C

AD9865: +85°C

AD9865: –40°C

Figure 16. Input Referred Integrated Noise and Noise Spectral Density vs.

RxPGA Gain (LPF f

5

4

3

2

1

0

–1

–2

DC OFFSET (% of full-scale)

–3

–4

–5

–6 0 6 12 18 24 30 36 42 48

−3 dB

GAIN (dB)

= 26 MHz)

DEVICE 1

DEVICE 2

DEVICE 3

DEVICE 4

Figure 17. Rx DC Offset vs. RxPGA Gain

52

–54

–56

–58

–60

–62

–64

–66

–68

–70

–72

20

18

16

14

12

10

8

6

4

2

0

THD (dBc)

04493-0-052

NOISE SPECTRAL DENSITY (nV/ Hz)

04493-0-053

04493-0-054

60.0

59.5

59.0

58.5

58.0

57.5

57.0

SNR (dBFS)

56.5

56.0

55.5

55.0

20 30 40 50 60 70 80

SNR @ 3.13V

SNR @ 3.3V

SNR @ 3.46V

THD @ 3.13V

THD @ 3.3V

THD @ 3.46V

INPUT FREQUENCY (MHz)

Figure 18. SNR and THD vs. Sample Rate and Supply

(LPF Disabled; RxPGA = 0 dB; f

45

44

43

42

41

SNR (dBc)

40

39

38

0 1020304050607080

CUTOFF FREQUENCY (MHz)

= 8 MHz)

IN

Figure 19. SNR vs. Filter Cutoff Frequency

(50 MSPS; f

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

GAIN STEP ERROR (dB)

–0.3

–0.4

–0.5

–6 0 6 12 18 24 30 36 42 48

Figure 20. RxPGA Gain Step Error vs. Gain (f

= 5 MHz; AIN = −1 dB; RxPGA = 48 dB)

IN

AD9865: GAIN STEP ERROR @ +25°C

AD9865: GAIN STEP ERROR @ +85°C

AD9865: GAIN STEP ERROR @ –40°C

RxPGA GAIN (dB)

= 10 MHz)

IN

–20

–30

–40

–50

–60

–70

THD (dBc)

04493-0-055

04493-0-056

04493-0-057

Rev. A | Page 14 of 48

AD9865

Rx PATH TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f

RIN = 50 Ω, half- or full-duplex interface, default power bias settings.

512

448

384

320

CODE

256

192

128

64

0 80 160 240 320 400 480 560 640 720

Figure 21. RxPGA Settling Time −12 dB to +48 dB Transition for DC Input

(f

ADC

0

–3

–6

–9

–12

AMPLITUDE RESPONSE (dB)

–15

–18

0 5 10 15 20 25 30 35 40 45 50

Figure 22. Rx Low-Pass Filter Amplitude Response vs. Supply

(f

= 50 MSPS, f

ADC

140

130

120

(dB)

110

100

@RxPGA = 0dB

90

ATTEN

80

70

60

0 5 10 15 20 25 30 35

Figure 23. Rx to Tx Full-Duplex Isolation @ 0 RxPGA Setting

(Note: ATTEN

@ RxPGA = x dB

TIME (ns)

= 50 MSPS, LPF Disabled)

INPUT FREQUENCY (MHz)

= 33 MHz, RxPGA = 0 dB)

−3 dB

TxDAC ISOLATION @ 0dB

IAMP ISOLATION @ 0dB

FREQUENCY (MHz)

= ATTEN

@ RxPGA = 0 dB

− RxPGA Gain)

OSCIN

3.3V

3.0V

3.6V

= f

= 50 MSPS, low-pass filter disabled, RxPGA = 0 dB, AIN = −1 dBFS,

ADC

352

320

288

256

224

CODE

192

160

128

96

04493-0-058

64

0 80 160 240 320 400 480 560 640 720

TIME (ns)

Figure 24. RxPGA Settling Time for 0 dB to +5 dB Transition for DC Input

= 50 MSPS, LPF Disabled)

(f

ADC

0

–2

–4

–6

–8

04493-0-059

–10

–12

FUNDAMENTAL (dB)

–14

–16

–18

–20

0 5 10 15 20 25 30 35 40 5045

+18dB GAIN

+30dB GAIN

+42dB GAIN

INPUT FREQUENCY (MHz)

Figure 25. Rx Low-Pass Filter Amplitude Response vs. RxPGA Gain

= 33 MHz)

3 dB

−

R

IN

C

IN

FREQUENCY (MHz)

04493-0-060

(LPF's f

420

410

400

390

)

Ω

380

370

360

RESISTANCE (

350

340

330

320

5 105958575655545352515

Figure 26. Rx Input Impedance vs. Frequency

–6dB GAIN

0dB GAIN

+6dB GAIN

10

9

8

7

6

5

4

3

2

1

0

04493-0-061

04493-0-062

CAPACITANCE (pF)

04493-0-090

Rev. A | Page 15 of 48

Loading...

Loading...