REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AD9856

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

CMOS 200 MHz

Quadrature Digital Upconverter

FUNCTIONAL BLOCK DIAGRAM

DDS AND CONTROL FUNCTIONS

12-BIT

DAC

12

1212

COSINESINE

COMPLEX

DATA IN

REFERENCE

CLOCK IN

TxENABLE

(I/Q SYNC)

PROFILE

SELECT

1–2

PROFILE

SELECT

3–4

MASTER

RESET

SPI INTERFACE

TO AD8320/AD8321

PROGRAMMABLE

CABLE DRIVER

AMPLIFIER

DAC

R

SET

DC-80 MHz

OUTPUT

BIDIRECTIONAL SPI CONTROL INTERFACE:

32-BIT FREQUENCY TUNING WORD

FREQUENCY UPDATE

INTERPOLATION FILTER RATE

REFERENCE CLOCK MULTIPLIER RATE

SPECTRAL PHASE INVERSION ENABLE

CABLE DRIVER AMPLIFIER CONTROL

12

1212

12

12

12

DEMULTIPLEXER AND

SERIAL-TO-PARALLEL

CONVERTER

12

12

INV

SINC

12

AD9856

43–83

SELECTABLE

INTERPOLATING

HALFBANDS

43–83

SELECTABLE

INTERPOLATING

HALFBANDS

43–203PROG.

CLOCK

MULTIPLIER

23 TO 633

SELECTABLE

INTERPOLATOR

23 TO 633

SELECTABLE

INTERPOLATOR

FEATURES

Universal Low Cost Modulator Solution for

Communications Applications

DC to 80 MHz Output Bandwidth

Integrated 12-Bit D/A Converter

Programmable Sample Rate Interpolation Filter

Programmable Reference Clock Multiplier

Internal SIN(x)/x Compensation Filter

>52 dB SFDR @ 40 MHz A

OUT

>48 dB SFDR @ 70 MHz A

OUT

>80 dB Narrowband SFDR @ 70 MHz A

OUT

+3 V Single Supply Operation

Space-Saving Surface-Mount Packaging

Bidirectional Control Bus Interface

Supports Burst and Continuous Tx Modes

Single Tone Mode for Frequency Synthesis Applications

Four Programmable, Pin-Selectable Modulator Profiles

Direct Interface to AD8320/AD8321 PGA Cable Driver

GENERAL DESCRIPTION

The AD9856 integrates a high speed direct-digital synthesizer

(DDS), a high performance, high speed 12-bit digital-to-analog

converter (DAC), clock multiplier circuitry, digital filters and

other DSP functions onto a single chip, to form a complete

quadrature digital upconverter device. The AD9856 is intended

to function as a universal I/Q modulator and agile upconverter

for communications applications, where cost, size, power dissipation and dynamic performance are critical attributes.

The AD9856 is available in a space-saving surface mount package and specified to operate over the extended industrial tem-

perature range of –40°C to +85°C.

APPLICATIONS

HFC Data, Telephony and Video Modems

Wireless and Satellite Communications

Cellular Basestations

–2– REV. B

AD9856–SPECIFICATIONS

(VS = +3 V ⴞ 5%, R

SET

= 3.9 k⍀, External reference clock frequency = 10 MHz

with REFCLK Multiplier enabled at 20ⴛ).

Test AD9856

Parameter Temp Level Min Typ Max Units

REF CLOCK INPUT CHARACTERISTICS

Frequency Range

REFCLK Multiplier Disabled Full VI 5 200

1

MHz

REFCLK Multiplier Enabled at 4× Full VI 5 50 MHz

REFCLK Multiplier Enabled at 20× Full VI 5 10 MHz

Duty Cycle +25°CV 50 %

Input Capacitance +25°CV 3 pF

Input Impedance +25°C V 100 MΩ

DAC OUTPUT CHARACTERISTICS

Resolution 12 Bits

Full-Scale Output Current 5 10 20 mA

Gain Error +25°C I –10 +10 %FS

Output Offset +25°CI 10µA

Differential Nonlinearity +25°C V 0.5 LSB

Integral Nonlinearity +25°C V 1 LSB

Output Capacitance +25°CV 5 pF

Phase Noise @ 1 kHz Offset, 40 MHz A

OUT

REFCLK Multiplier Enabled at 20× +25°C V –85 dBc/Hz

REFCLK Multiplier at 4× +25°C V –100 dBc/Hz

REFCLK Multiplier Disabled +25°C V –110 dBc/Hz

Voltage Compliance Range +25°C I –0.5 1.5 V

Wideband SFDR:

1 MHz Analog Out +25°C IV 70 dBc

20 MHz Analog Out +25°C IV 65 dBc

42 MHz Analog Out +25°C IV 60 dBc

65 MHz Analog Out +25°C IV 55 dBc

80 MHz Analog Out +25°C IV 50 dBc

Narrowband SFDR: (±100 kHz Window)

70 MHz Analog Out +25°C IV 80 dBc

MODULATOR CHARACTERISTICS

Adjacent Channel Power (CH Power = –6.98 dBm) +25°C IV 50 dBm

Error Vector Magnitude +25°CIV 12%

I/Q Offset +25°CIV5055 dB

Inband Spurious Emissions +25°C IV 45 50 dBc

Pass Band Amplitude Ripple (DC to 80 MHz) +25°CV ±0.3 dB

TIMING CHARACTERISTICS

Serial Control Bus

Maximum Frequency Full IV 10 MHz

Minimum Clock Pulsewidth High (t

PWH

) Full IV 30 ns

Minimum Clock Pulsewidth Low (t

PWL

) Full IV 30 ns

Maximum Clock Rise/Fall Time Full IV 1 ms

Minimum Data Setup Time (t

DS

) Full IV 25 ns

Minimum Data Hold Time (t

DH

) Full IV 0 ns

Maximum Data Valid Time (t

DV

) Full IV 30 ns

Wake-Up Time

2

Full IV 1 ms

Minimum RESET Pulsewidth High (t

RH

) Full IV 5 REFCLK

Cycles

CMOS LOGIC INPUTS

Logic “1” Voltage +25°C I +2.6 V

Logic “0” Voltage +25°C I +0.4 V

Logic “1” Current +25°CI 12µA

Logic “0” Current +25°CI 12µA

Input Capacitance +25°CV 3 pF

–3–REV. B

AD9856

Test AD9856

Parameter Temp Level Min Typ Max Units

CMOS LOGIC OUTPUTS (1 mA LOAD)

Logic “1” Voltage +25°C I 2.7 mA

Logic “0” Voltage +25°C I 0.4 mA

POWER SUPPLY

+V

S

Current

Full Operating Conditions

2

+25°C I 530 mA

Burst Operation (25%) +25°C I 450 mA

Single Tone Mode +25°C I 495 mA

160 MHz Clock +25°C I 445 mA

120 MHz Clock +25°C I 345 mA

Power-Down Mode +25°CI 2mA

NOTES

1

For 200 MHz operation in Modulation Mode at +85°C operating temperature, V

S

must be +3 V min.

2

Assuming 1.3 kΩ and 0.01 µF loop filter components.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS*

Maximum Junction Temperature . . . . . . . . . . . . . . . .+165°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

V

S

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +4 V

Operating Temperature . . . . . . . . . . . . . . . . . –40°C to +85°C

Digital Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . –0.7 V to +V

S

Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . .+300°C

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 5 mA

θ

JA

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . . 38°C/W

*Absolute maximum ratings are limiting values, to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability under any of these conditions is not necessarily implied. Exposure of

absolute maximum rating conditions for extended periods of time may affect

device reliability.

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD9856AST –40°C to +85°C Thin Quad Flatpack ST-48

AD9856/PCB +25°C Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9856 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

EXPLANATION OF TEST LEVELS

Test Level

I – 100% Production Tested.

III – Sample Tested Only.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – Devices are 100% production tested at +25°C and

guaranteed by design and characterization testing for

industrial operating temperature range.

AD9856

–4– REV. B

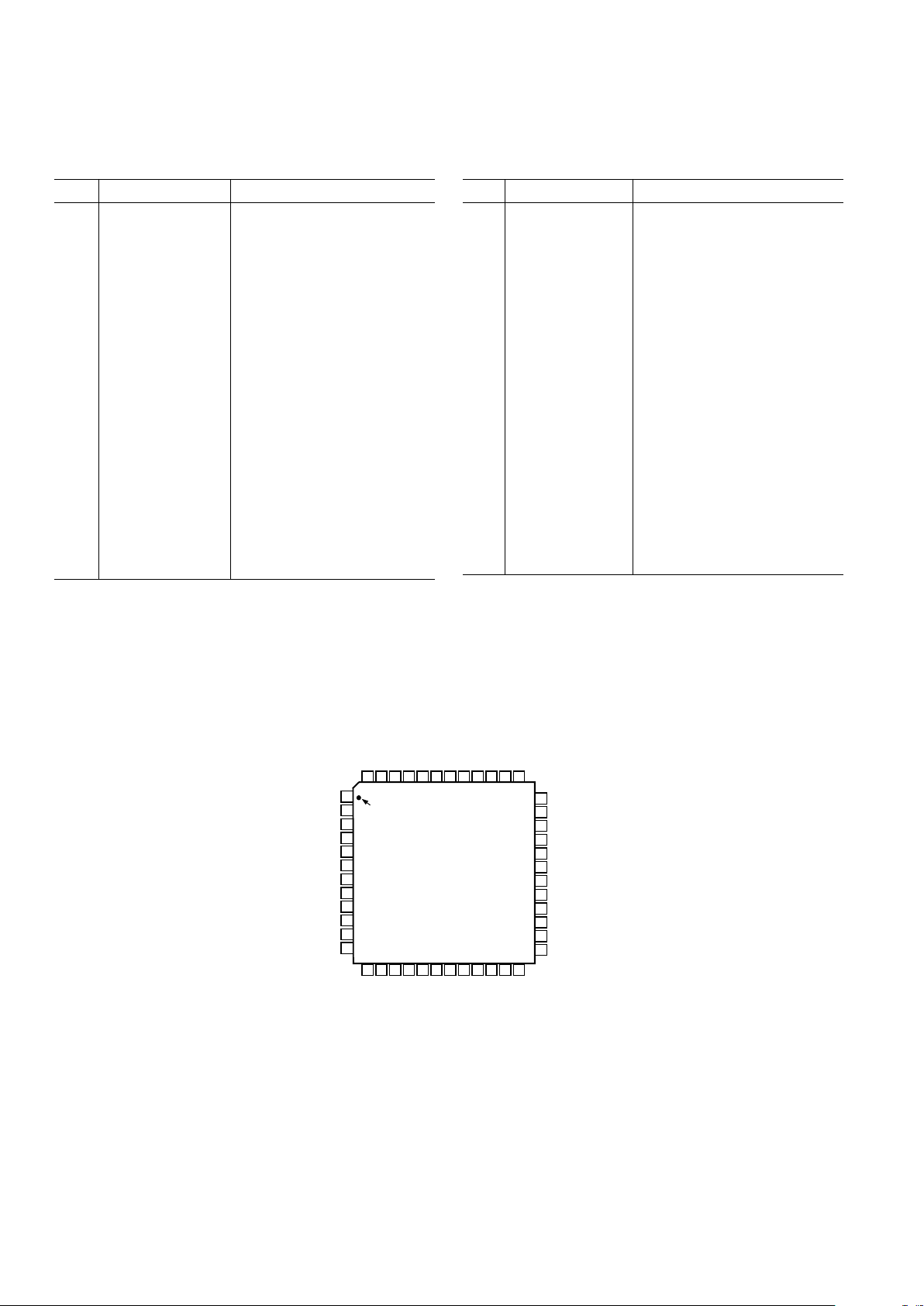

Pin # Pin Name Pin Function

1 TxENABLE Input Pulse that Synchronizes

the Data Stream

2 D11 Input Data (Most Significant Bit)

3 D10 Input Data

4, 10,

21, 44 DVDD Digital Supply Voltage

5, 11,

20, 43 DGND Digital Ground

6–9 D9–D6 Input Data

12–16 D5–D1 Input Data

17 D0 Input Data (Least Significant

Bit)

18, 19,

22 NC No Internal Connection

23, 28,

31 AGND Analog Ground

24 BG REF BYPASS No External Connection*

25 DAC R

SET

R

SET

Resistor Connection

26 DAC REF BYPASS No External Connection*

27 AVDD Analog Supply Voltage

Pin # Pin Name Pin Function

29 I

OUTB

Complementary Analog

Current Output of the DAC

30 I

OUT

True Analog Current Output

of DAC

32 PLL GND PLL Ground

33 PLL FILTER PLL Loop Filter Connection

34 PLL SUPPLY PLL Voltage Supply

35 CA ENABLE Cable Driver Amp Enable

36 CA DATA Cable Driver Amp Data

37 CA CLK Cable Driver Amp Clock

38 CS Chip Select

39 SDO Serial Data Output

40 SDIO Serial Port I/O

41 SCLK Serial Port Clock

42 SYNC I/O Performs I/O Synchronization

45 PS0 Profile Select 0

46 PS1 Profile Select 1

47 REFCLK Reference Clock Input

48 RESET Master Reset

PIN FUNCTION DESCRIPTIONS

PIN CONFIGURATION

36

35

34

33

32

31

30

29

28

27

26

25

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

48 47 46 45 44 39 3843 42 41 40 37

PIN 1

IDENTIFIER

TOP VIEW

(Not to Scale)

AD9856

CA DATA

CA ENABLE

PLL SUPPLY

PLL FILTER

PLL GND

AGND

I

OUT

TxENABLE

D11

D10

DVDD

DGND

D9

D8

NC = NO CONNECT

D7

D6

DVDD

DGND

I

OUTB

AGND

AVDD

DAC REF BYPASS

BG REF

BYPASS

D5

DAC R

SET

NC

DVDD

DGND

NC

D0

D1

D2

D3

D4

NC

AGND

SYNC I/O

CS

REFCLK

SCLK

RESET

PS0

DVDD

DGND

CA CLK

PS1

SDO

SDIO

*In most cases optimal performance is achieved with no external connection. For extremely noisy environments BG REF BYPASS can be bypassed with up to a

0.1 µF capacitor to AGND (Pin 23). DAC REF BYPASS can be bypassed with up to a 0.1 µF capacitor to AVDD (Pin 27).

AD9856

–5–REV. B

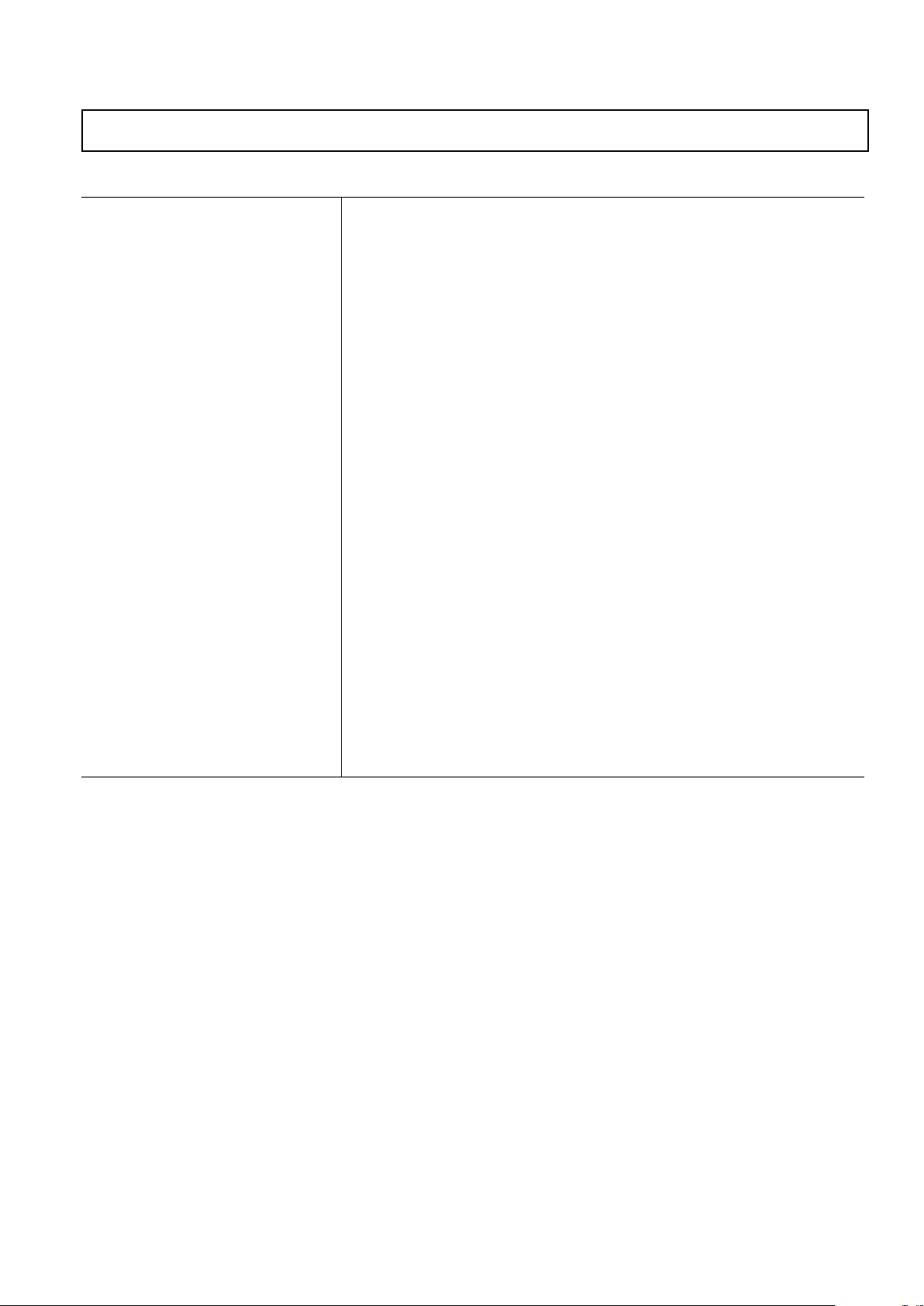

FUNCTIONAL BLOCK AND MODE DESCRIPTION

Operating Modes 1. Complex quadrature modulator mode.

2. Single tone output mode.

Input Data Format Programmable: 12-bit, 6-bit, or 3-bit input formats. Data input to the AD9856 is

12-bit, twos complement. Complex I/Q symbol component data is required to be at

least 2× oversampled, depending upon configuration.

Input Sample Rate Up to 50 Msamples/s @ 200 MHz SYSCLK rate.

Input Reference Clock Frequency For DC-80 MHz A

OUT

operation (200 MHz SYSCLK rate):

w/REFCLK Multiplier enabled: 10 MHz–50 MHz, programmable via control bus

w/REFCLK Multiplier disabled: 200 MHz.

Note: For optimum data synchronization, the AD9856 Reference Clock, and the

input data clock, should be derived from the same clock source.

Internal Reference Clock Multiplier Programmable in integer steps over the range of 4×–20×. Can be disabled (effective

REFCLK Multiplier = 1) via control bus. Output of REFCLK Multiplier = SYSCLK

rate, which is the internal clock rate applied to the DDS and DAC function.

Profile Select Four pin-selectable, preprogrammed formats. Available for modulation and single

tone operating modes.

Interpolating Range Fixed 4×, selectable 2× and selectable 2×–63× range.

Half-Band Filters Interpolating filters that provide upsampling and reduce the effects of the CIC

passband roll-off characteristics.

TxENABLE Function–Burst Mode When Burst Mode is enabled via the control bus, the rising edge of the applied

TxENABLE pulse should be coincident with, and frame, the input data packet. This

establishes data sampling synchronization.

TxENABLE Function–Continuous Mode When continuous mode is enabled via the control bus, the TxENABLE pin becomes

an I/Q control line. A Logic “1” on TxENABLE indicates I data is being presented

to the AD9856. A Logic “0” on TxENABLE indicates Q data is being presented to the

AD9856. Each rising edge of TxENABLE resynchronizes the AD9856 input sampling capability.

Inverse SINC Filter Precompensates for SIN(x)/x roll-off of DAC; user bypassable.

I/Q Channel Invert [I × Cos(ωt) + Q × Sin(ωt)] or [I × Cos(ωt) – Q × Sin(ωt)] (default), configurable via

control bus, per profile.

Full Sleep Mode Power dissipation reduced to less than 6 mW when Full Sleep Mode active, program-

mable via control bus.

AD9856

–6– REV. B

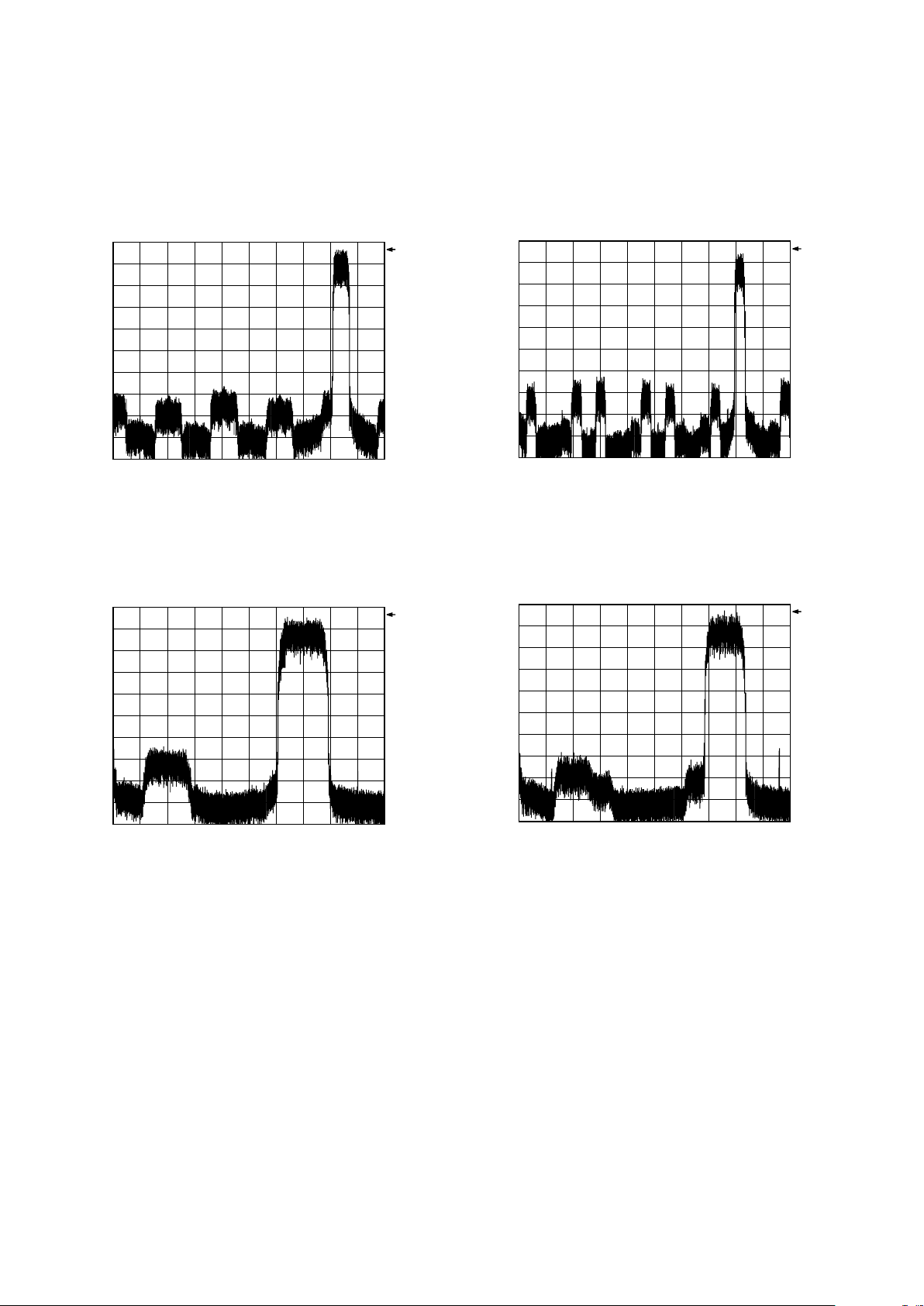

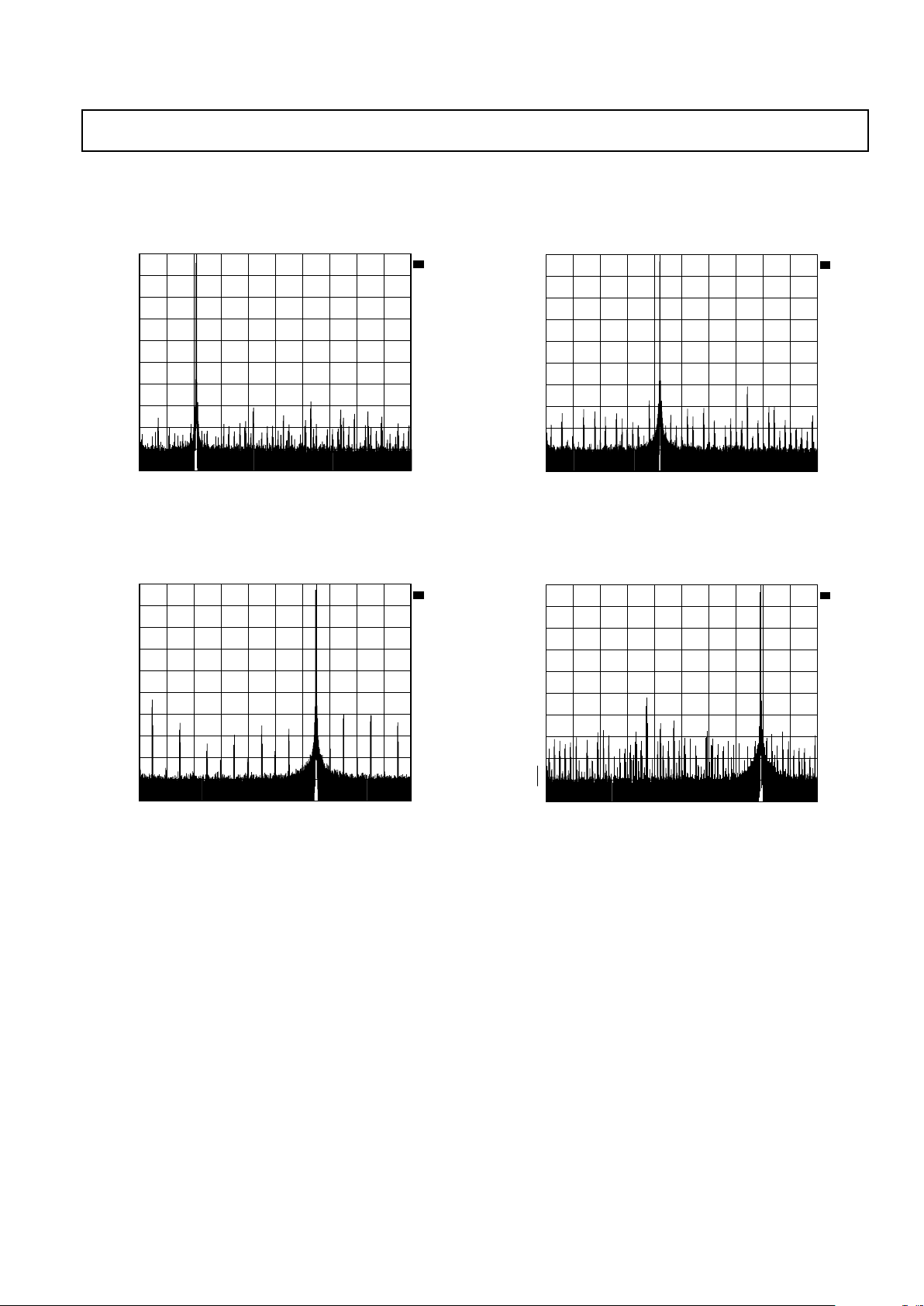

Typical Modulated Output Spectral Plots

START 0Hz 5MHz/ STOP 50MHz

0

–8

REF LVL

–25dBm

dBm

1AP

–16

–24

–32

–40

–48

–56

–64

–72

–80

RBW 10kHz RF ATT 10dB

VBW 1kHz

SWT 12.5s Unit dBm

Figure 1. QPSK at 42 MHz and 2.56 MS/s; 10.24 MHz

External Clock with REFCLK Multiplier = 12, CIC = 3,

HB3 On, 2

×

Data

START 0Hz 4MHz/ STOP 40MHz

0

–8

REF LVL

–30dBm

dBm

1AP

–16

–24

–32

–40

–48

–56

–64

–72

–80

RBW 10kHz RF ATT 10dB

VBW 1kHz

SWT 10s UNIT dBm

Figure 2. 64-QAM at 28 MHz and 6 MS/s; 36 MHz External

Clock with REFCLK Multiplier = 4, CIC = 2, HB3 Off, 3

×

Data

START 0Hz 8MHz/ STOP 80MHz

0

–8

REF LVL

–25dBm

dBm

1AP

–16

–24

–32

–40

–48

–56

–64

–72

–80

RBW 10kHz RF ATT 10dB

VBW 1kHz

SWT 20s Unit dBm

Figure 3. 16-QAM at 65 MHz and 2.56 MS/s; 10.24 MHz

External Clock with REFCLK Multiplier = 18, CIC = 9,

HB3 Off, 2

×

Data

START 0Hz 5MHz/ STOP 50MHz

0

–8

REF LVL

–30dBm

dBm

1AP

–16

–24

–32

–40

–48

–56

–64

–72

–80

RBW 10kHz RF ATT 10dB

VBW 1kHz

SWT 12.5s UNIT dBm

Figure 4. 256-QAM at 38 MHz and 6 MS/s; 48 MHz External

Clock with REFCLK Multiplier = 4, CIC = 2, HB3 Off, 4

×

Data

AD9856

–7–REV. B

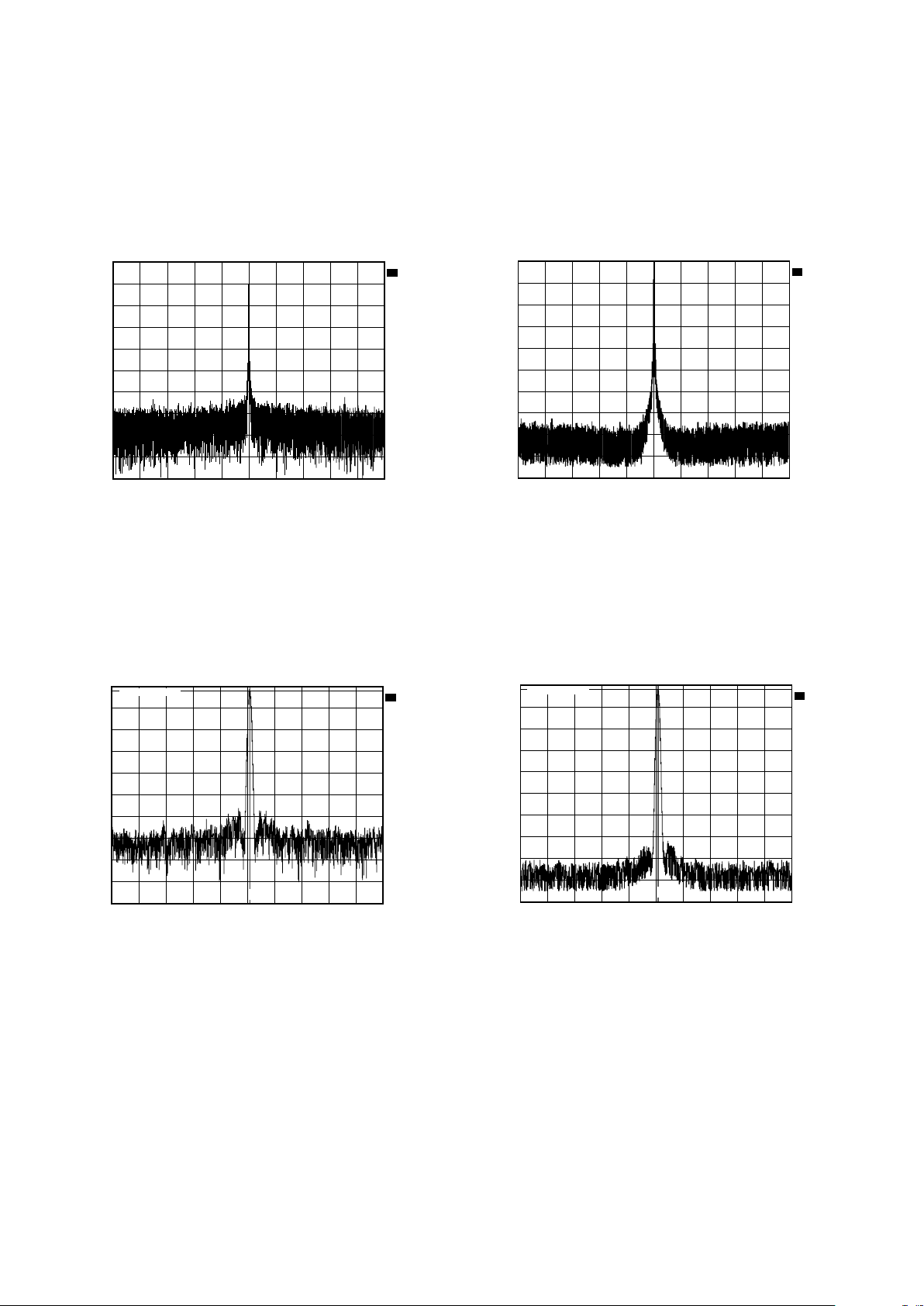

Typical Single Tone Output Spectral Plots

START 0Hz 10MHz/ STOP 100MHz

0

–10

REF LVL

–5dBm

dBm

1AP

–20

–30

–40

–50

–60

–70

–80

–90

–100

RBW 3kHz RF ATT 20dB

VBW 3kHz

SWT 28s UNIT dB

A

Figure 5. 21 MHz CW Output

START 0Hz 10MHz/ STOP 100MHz

0

–10

REF LVL

–5dBm

dBm

1AP

–20

–30

–40

–50

–60

–70

–80

–90

–100

RBW 3kHz RF ATT 20dB

VBW 3kHz

SWT 28s UNIT dB

A

Figure 6. 65 MHz CW Output

START 0Hz 10MHz/ STOP 100MHz

0

–10

REF LVL

–5dBm

dBm

1AP

–20

–30

–40

–50

–60

–70

–80

–90

–100

RBW 3kHz RF ATT 20dB

VBW 3kHz

SWT 28s UNIT dB

A

Figure 7. 42 MHz CW Output

START 0Hz 10MHz/ STOP 100MHz

0

–10

REF LVL

–5dBm

dBm

1AP

–20

–30

–40

–50

–60

–70

–80

–90

–100

RBW 3kHz RF ALT 20dB

VBW 3kHz

SWT 28s UNIT dB

A

Figure 8. 79 MHz CW Output

AD9856

–8– REV. B

Typical Narrowband SFDR Spectral Plots

Typical Phase Noise Spectral Plots

CENTER 70.1MHz 10kHz/ SPAN 100kHz

0

–10

REF LVL

–5dBm

dBm

1AP

–20

–30

–40

–50

–60

–70

–80

–90

–100

RBW 100Hz RF ATT 20dB

VBW 100Hz

SWT 50s UNIT dB

A

Figure 9. 70.1 MHz Narrowband SFDR, 10 MHz External

Clock with REFCLK Multiplier = 20

×

CENTER 70.1MHz 10kHz/ SPAN 100kHz

0

–12

REF LVL

–5dBm

dBm

1AP

–24

–36

–48

–60

–72

–84

–96

–100

–120

RBW 100Hz RF ATT 20dB

VBW 100Hz

SWT 50s UNIT dB

A

Figure 11. 70.1 MHz Narrowband SFDR, 200 MHz External

Clock with REFCLK Multiplier Disabled

CENTER 40.1MHz 500Hz/ SPAN 5kHz

0

–12

REF LVL

0dBm

dBm

1AP

–24

–36

–48

–60

–72

–84

–96

–108

–120

RBW 30Hz RF ATT 30dB

VBW 30Hz

SWT 28s UNIT dB

A

FXD

FXD –2.248dBm

Figure 10. 40.1 MHz Output, 10 MHz External Clock with

REFCLK Multiplier = 20

×

CENTER 40.1MHz 500Hz/ SPAN 5kHz

0

–12

REF LVL

0dBm

dBm

1AP

–24

–36

–48

–60

–72

–84

–96

–100

–120

RBW 30Hz RF ATT 30dB

VBW 30Hz

SWT 28s UNIT dB

A

FXD

FXD –2.248dBm

Figure 12. 40.1 MHz Output, 200 MHz External Clock with

REFCLK Multiplier Disabled

AD9856

–9–REV. B

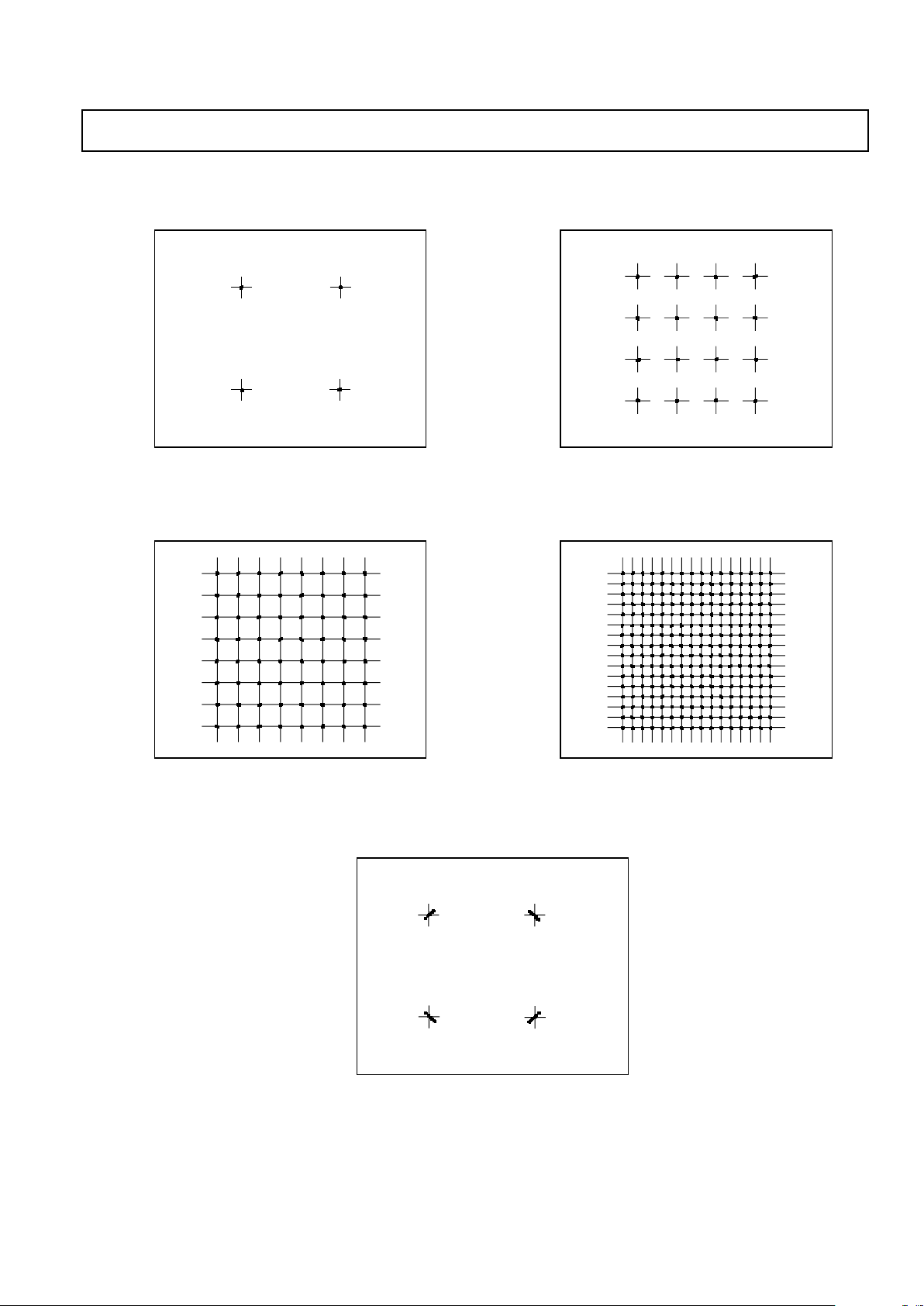

Typical Plots of Output Constellations

–1.9607843757 1.96078437567

1.5

TRACE A: CH 1 QPSK MEAS TIME

CONST

300

M

/DIV

–1.5

Figure 13. QPSK, 65 MHz, 2.56 MS/s

–1.3071895838 1.30718958378

1

TRACE A: CH 1 64QAM MEAS TIME

CONST

200

M

/DIV

–1

Figure 14. 64-QAM, 42 MHz, 6 MS/s

–1.6339869797 1.63398697972

1.25

TRACE A: CH 1 16QAM MEAS TIME

CONST

250

M

/DIV

–1.25

Figure 15. 16-QAM, 65 MHz, 2.56 MS/s

–1.3071895838 1.30718958378

1

TRACE A: CH 1 256QAM MEAS TIME

CONST

200

M

/DIV

–1

Figure 16. 256-QAM, 42 MHz, 6 MS/s

–1.9607843757 1.96078437567

1.5

TRACE A: CH 1 MSK1 MEAS TIME

CONST

300

M

/DIV

–1.5

Figure 17. GMSK Modulation, 13 MS/s

AD9856

–10– REV. B

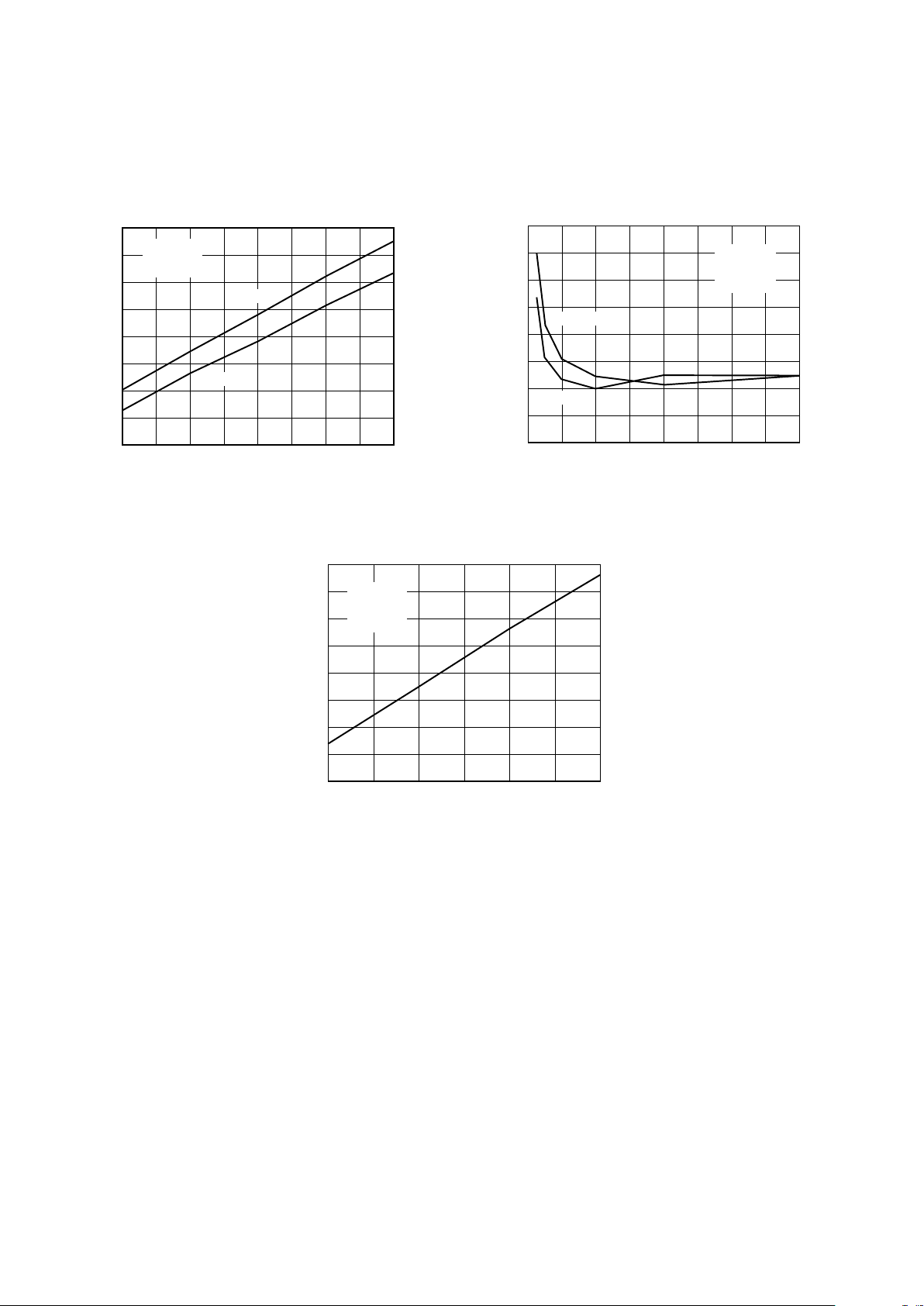

Power Consumption

CLOCK SPEED – MHz

1600

120

POWER CONSUMPTION – mW

1400

1200

1000

800

140 160 200180

HB3 = OFF

HB3 = ON

+VS = +3V

CIC = 2

+258C

Figure 18. Power Consumption vs. Clock Speed; +VS =

+3 V, CIC = 2, +25

°

C

CIC RATE

1600

0

POWER CONSUMPTION – mW

1500

1400

1300

1200

16 32 6448

HB3 = OFF

HB3 = ON

+VS = +3V

CIC = 2

200MHz

+25

8C

Figure 19. Power Consumption vs. CIC Rate; +VS =

+3 V, 200 MHz, +25

°

C

Tx ENABLE DUTY CYCLE

1450

25

POWER CONSUMPTION – mW

1350

1250

1150

1050

50 75 100

+VS = +3V

CIC = 2

200MHz

+25

8

C

Figure 20. Power Consumption vs. Burst Duty Cycle;

+V

S

= +3 V, CIC = 2, 200 MHz, +25°C

Loading...

Loading...