Information furnished by Analog Devices is be lieved to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

that may result from its use. No license is granted by implication or oth-

erwise under any patent or patent rights of Analog Devices. Trademarks

and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© 2004 Analog Devices, Inc. All rights reserved.

AD9851

FEATURES

Reference Clock

Multiplier

On-Chip High Performance 10-Bit DAC and High Speed

Comparator with Hysteresis

SFDR >43 dB @ 70 MHz A

OUT

32-Bit Frequency Tuning Word

Simpli ed Control Interface: Parallel or Serial

Asynchronous Loading Format

5-Bit Phase Modulation and Offset Capability

Comparator Jitter <80 ps p-p @ 20 MHz

2.7 V to 5.25 V Single-Supply Operation

Low Power: 555 mW @ 180 MHz

Power-Down Function, 4 mW @ 2.7 V

Ultrasmall 28-Lead SSOP Packaging

APPLICATIONS

Frequency/Phase-Agile Sine Wave Synthesis

Clock Recovery and Locking Circuitry for Digital

Communications

Digitally Controlled ADC Encode Generator

Agile Local Oscillator Applications in Communications

Quadrature Oscillator

CW, AM, FM, FSK, MSK Mode Transmitter

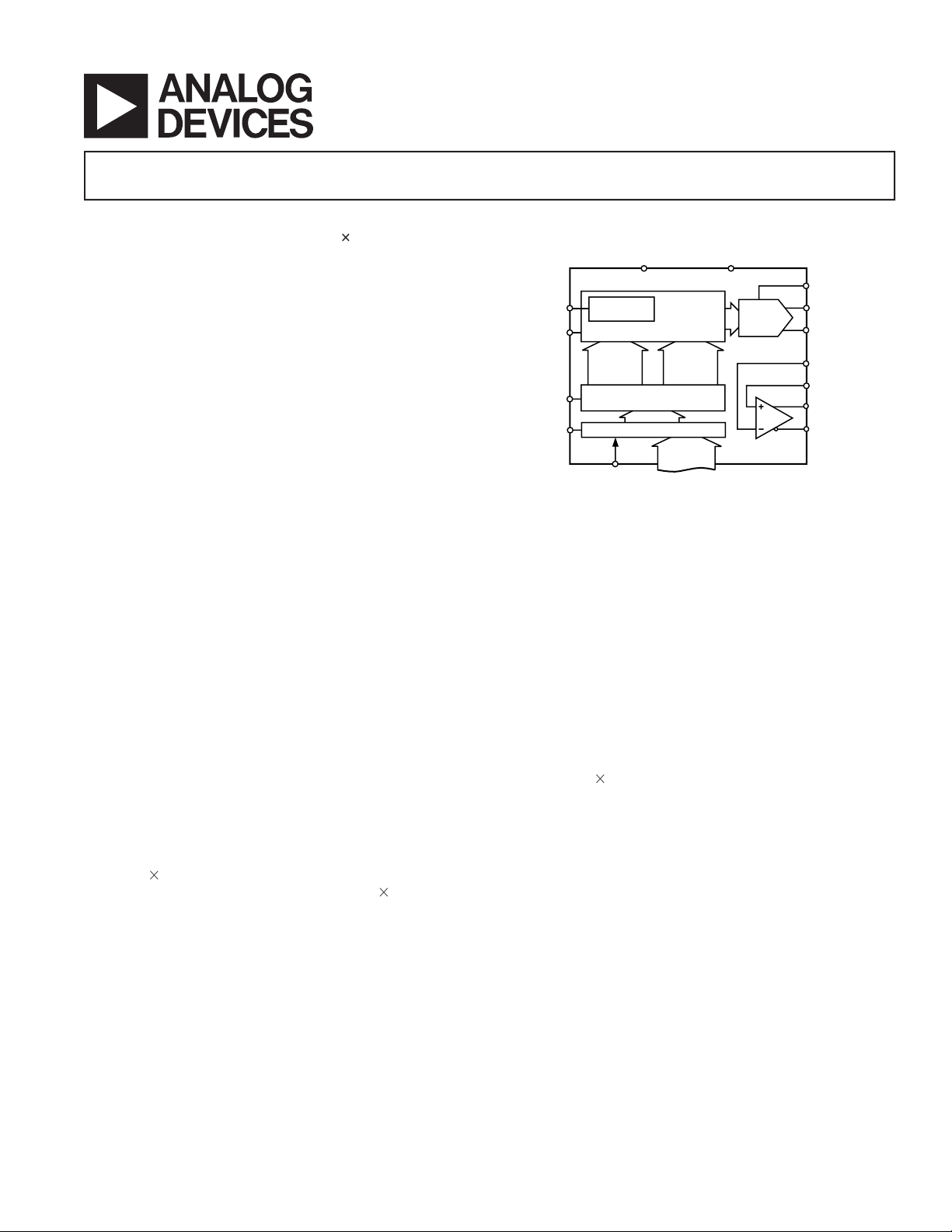

FUNCTIONAL BLOCK DIAGRAM

32-BIT

TUNING

WORD

PHASE

AND

CONTROL

WORDS

FREQUENCY/PHASE

DATA REGISTER

DATA INPUT REGISTER

10-BIT

DAC

DAC R

SET

ANALOG

OUT

ANALOG

IN

CLOCK OUT

CLOCK OUT

HIGH SPEED

DDS

FREQUENCY

UPDATE/DATA

REGISTER

RESET

WORD LOAD

CLOCK

MASTER

RESET

REF

CLOCK IN

6 REFCLK

MULTIPLIER

COMPARATOR

SERIAL

LOAD

1 BIT

40 LOADS

PARALLEL

LOAD

8 BITS

5 LOADS

FREQUENCY, PHASE

AND CONTROL DATA INPUT

AD9851

+V

S

GND

GENERAL DESCRIPTION

The AD9851 is a highly integrated device that uses advanced

DDS technology, coupled with an internal high speed, high

performance D/A converter, and comparator, to form a dig i tal ly

programmable frequency synthesizer and clock generator func-

tion. When referenced to an accurate clock source, the AD9851

generates a stable frequency and phase-programmable digitized

analog output sine wave. This sine wave can be used directly as

a frequency source, or internally converted to a square wave for

agile-clock generator applications. The AD9851’s innovative

high speed DDS core accepts a 32-bit frequency tuning word,

which results in an output tuning res o lu tion of approximately

0.04 Hz with a 180 MHz system clock. The AD9851 con tains

a unique 6

REFCLK Multiplier circuit that eliminates the

need for a high speed reference oscillator. The 6

REFCLK

Multiplier has min i mal impact on SFDR and phase noise char-

ac ter is tics. The AD9851 provides ve bits of programmable

phase mod u la tion resolution to enable phase shifting of its

output in in cre ments of 11.25°.

The AD9851 contains an internal high speed comparator that

can be con gured to accept the (externally) ltered output of the

DAC to generate a low jitter output pulse.

The frequency tuning, control, and phase modulation words are

asynchronously loaded into the AD9851 via a parallel or serial

loading format. The parallel load format consists of ve it er a tive

loads of an 8-bit control word (byte). The rst 8-bit byte controls

output phase, 6

REFCLK Multiplier, power-down enable and

loading for mat; the remaining bytes comprise the 32-bit frequency

tuning word. Serial loading is accomplished via a 40-bit serial data

stream entering through one of the parallel input bus lines. The

AD9851 uses advanced CMOS technology to provide this break-

through level of functionality on just 555 mW of power dissipation

The AD9851 is available in a space-saving 28-lead SSOP,

surface-mount package that is pin-for-pin compatible with the

popular AD9850 125 MHz DDS. It is speci ed to operate over

the extended industrial temperature range of –40°C to +85°C

at >3.0 V supply voltage. Below 3.0 V, the speci cations apply

over the commercial temperature range of 0°C to 85°C.

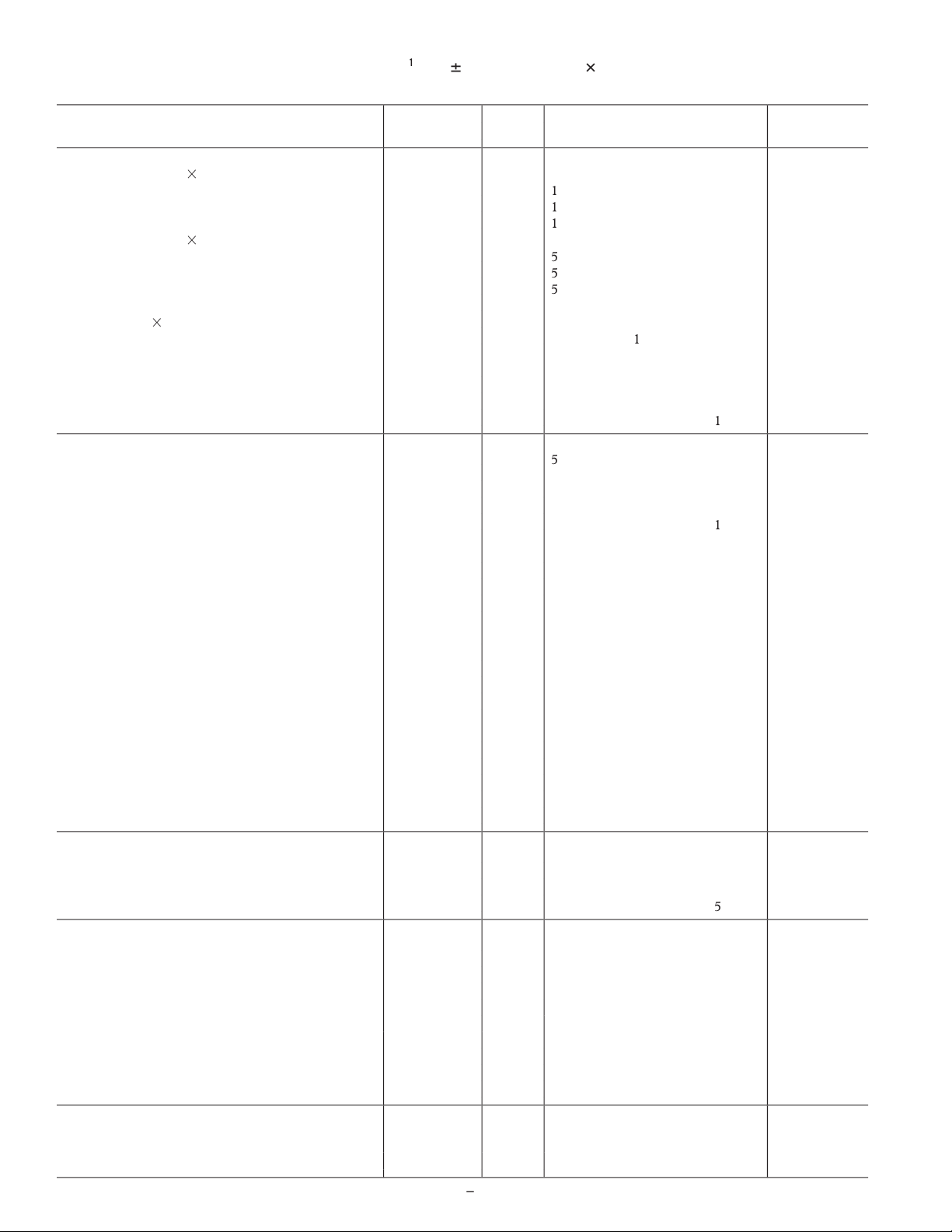

AD9851–SPECIFICATIONS

(V

S

1

= 5 V

5%, R

SET

= 3.9 k

, 6

REFCLK Multiplier Disabled, External Ref er ence

Clock = 180 MHz, except as noted.)

Test

AD9851BRS

arameter

Temp

Level

Typ

Max

Unit

CLOCK INPUT CHARACTERISTICS

Frequency Range (6

REFCLK Multiplier Disabled)

5.0 V Supply

Full

IV

3.3 V Supply

Full

IV

2.7 V Supply

0°C to 85°C

IV

MHz

Frequency Range (6

REFCLK Multiplier Enabled)

5.0 V Supply

Full

IV

5

30MHz

3.3 V Supply

Full

IV520.83

2.7 V Supply

0°C to 85°C

IV

5

MHz

Duty Cycle

Full

IV

45

60

%

Duty Cycle (6

REFCLK Multiplier Enabled)

Full

IV

35

65

%

Input Resistance

25°C

V

Minimum Switching Thresholds

Logic 1, 5.0 V Supply

25°C

IV

3.5

V

Logic 1, 3.3 V Supply

25°C

IV

2.3

V

Logic 0, 5.0 V Supply

25°C

IV

V

Logic 0, 3.3 V Supply

25°C

IV

V

DAC OUTPUT CHARACTERISTICS

Full-Scale Output Current

25°C

IV

5

20mA

Gain Error

25°C

–10

+10

% FS

Output Offset

25°C

I

µA

Differential Nonlinearity

25°C

I

0.75

LSB

Integral Nonlinearity

25°C

LSB

Residual Phase Noise, 5.2 MHz, 1 kHz Offset

PLL On

25°C

V

–125

dBc/Hz

PLL Off

25°C

V

–132

dBc/Hz

Output Impedance

25°C

V

k

Voltage Com pli ance Range

25°C

I

–0.5

+1.5

V

Wideband Spu ri ous-Free Dynamic Range

25°C

IV

60

64

dBc

20.1 MHz An a log Out (DC to 72 MHz)

25°C

IV

51

53

dBc

40.1 MHz Analog Out (DC to 72 MHz)

25°C

IV5155

dBc

50.1 MHz An a log Out (DC to 72 MHz)

25°C

IV

46

53

dBc

70.1 MHz Analog Out (DC to 72 MHz)

25°C

IV

42

43

dBc

Narrowband Spurious-Free Dynamic Range

25°C

V

85

dBc

25°C

V

80

dBc

40.1 MHz (±50 kHz)

25°C

V

85

dBc

40.1 MHz (±200 kHz)

25°C

V

80

dBc

70.1 MHz (±50 kHz)

25°C

V

85

dBc

70.1 MHz (±200 kHz)

25°C

V

73

dBc

COMPARATOR INPUT CHARACTERISTICS

Input Capacitance

25°C

V

3

pF

Input Re sis tance

25°C

IV

500

k

Input Bias Current

25°C

µA

Input Voltage Range

25°C

IV05

V

COMPARATOR OUTPUT CHARACTERISTICS

Logic 1 Voltage 5 V Supply

25°C

VI

4.8

V

Logic 1 Voltage 3.3 V Supply

25°C

VI

3.1

V

Logic 1 Voltage 2.7 V Supply

25°C

VI

2.3

V

Logic 0 Voltage

25°C

VI

+0.4

V

Continuous Output Current

25°C

IV

20

Hysteresis

25°C

IV

mV

Propagation Delay

25°C

IV

7

ns

Toggle Frequency (1 V p-p Input Sine Wave)

25°C

IV

200

Rise/Fall Time, 15 pF Output Load

25°C

IV

ns

Output Jitter (p-p)

3

25°C

IV

80

ps (p-p)

CLOCK OUTPUT CHAR AC TER IS TICS

Output Jitter (Clock Generator Con guration,

40 MHz 1 V p-p Input Sine Wave)

25°C

V

250

ps (p-p)

Clock Output Duty Cycle

Full

IV

50 ± 10

%

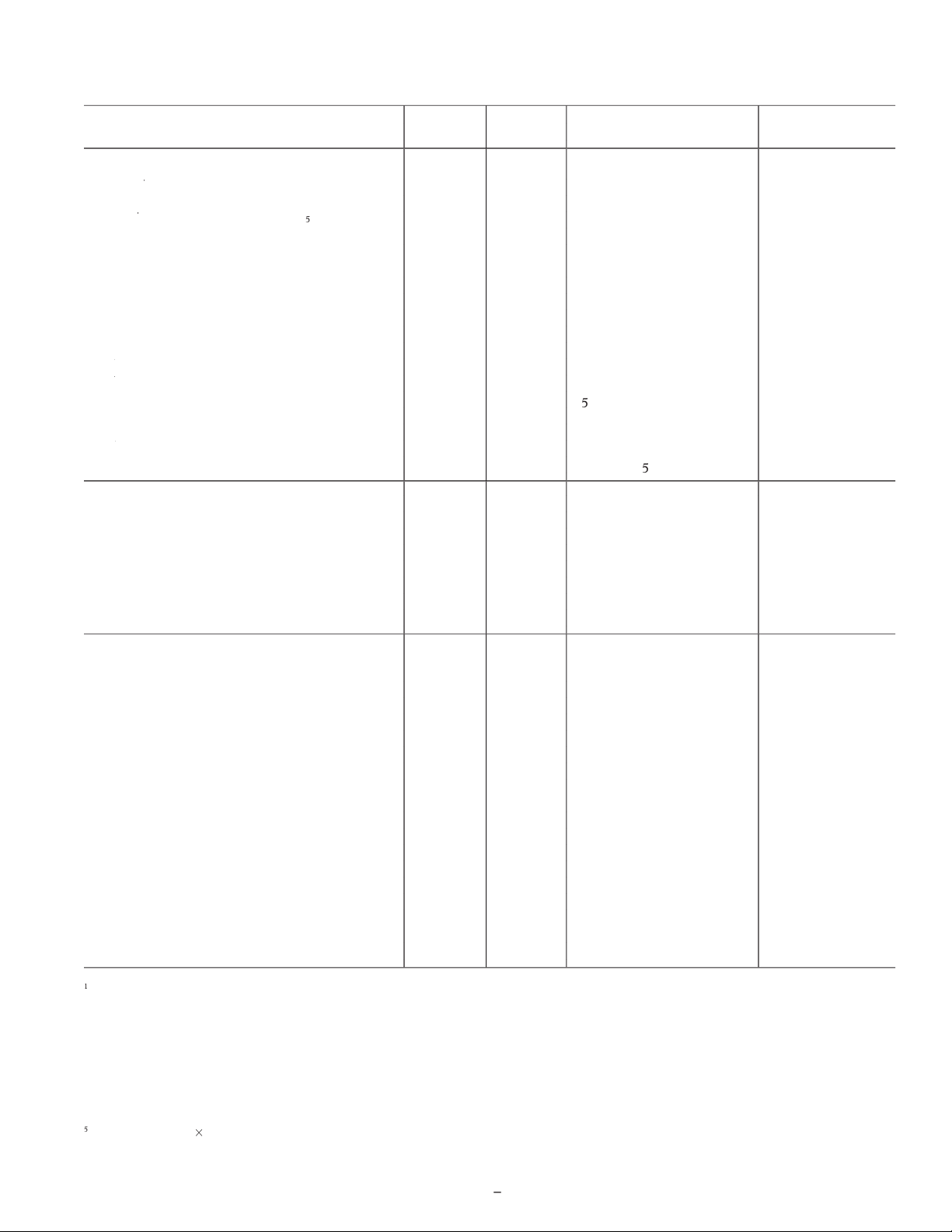

AD9851

–3

Test

AD9851BRS

Parameter

Temp

Level

Min

Typ

Max

Unit

TIMING CHARACTERISTICS

4

t

WH

, t

WL

(W_CLK Min Pulse Width High/Low)

(W_CLK Min Pulse Width High/Low)

Full

IV

3.5

ns

t

DS

, t

(Data to W_CLK Setup and Hold Times)

Full

IV

3.5

ns

t

FH

, t

FL

(FQ_UD Min Pulse Width High/Low)

(FQ_UD Min Pulse Width High/Low)

Full

IV

7

ns

t

CD

(REFCLK Delay After FQ_UD)

5

Full

IV

3.5

ns

t

(FQ_UD Min Delay After W_CLK)

FullIVns

t

CF

(Out put Latency from FQ_UD)

Frequency Change

Full

IV

SYSCLK

Cycles

Phase Change

Full

IV

SYSCLK

Cycles

t

(CLKIN Delay After RESET Rising Edge)

Full

IV

3.5

ns

t

RL

(RESET Falling Edge After CLKIN)

(RESET Falling Edge After CLKIN)

Full

IV

3.5

ns

t

RR

(Recovery from RESET)

(Recovery from RESET)

Full

IV

2

SYSCLK

Cycles

t

RS

(Min i mum RE SET Width)

Full

IV

5

SYSCLK

Cycles

t

OL

(RESET Output Latency)

(RESET Output Latency)

Full

IV

SYSCLK

Cycles

Wake-Up Time from Power-Down Mode

6

25°C

V

5

µs

CMOS LOGIC INPUTS

Logic 1 Voltage, 5 V Supply

25°C

3.5

V

Logic 1 Voltage, 3.3 V Supply

25°C

IV

2.4

V

Logic 1 Voltage, 2.7 V Supply

25°C

IV

2.0

V

Logic 0 Voltage

25°C

IV

0.8

V

Logic 1 Current

25°C

µA

Logic 0 Current

25°C

I

µA

Rise/Fall Time

25°C

IV

ns

Input Capacitance

25°C

V

3

pF

POWER SUPPLY

V

S

6

Current @:

62.5 MHz Clock, 2.7 V Supply

25°C

VI

30

35

mA

25°C

VI4050

62.5 MHz Clock, 3.3 V Supply

25°C

VI

35

45

mA

25°C

VI

55

70

mA

62.5 MHz Clock, 5 V Supply

25°C

VI5065

25°C

VI

70

90

mA

25°C

VI

mA

Power Dissipation @ :

62.5 MHz Clock, 5 V Supply

25°C

VI

250

325

mW

62.5 MHz Clock, 3.3 V Supply

25°C

VI

mW

62.5 MHz Clock, 2.7 V Supply

25°C

VI8595

mW

25°C

VI

mW

25°C

VI

365

450

mW

25°C

VI

230

mW

25°C

VI

555

650

mW

P

DISS

Power-Down Mode @:

5 V Supply

25°C

VI55mW

2.7 V Supply

25°C

VI20mW

NOTES

1

+V

S

collectively refers to the positive voltages applied to DVDD, PVCC, and AVDD. Voltages applied to these pins should be of the same po ten tial.

2

Indicates the minimum signal levels required to reliably clock the device at the indicated supply voltages. This speci es the p-p signal level and dc offset needed when the

clocking signal is not of CMOS/TTL origin, i.e., a sine wave with 0 V dc offset.

3

The comparator’s jitter contribution to any input signal. This is the minimum jitter on the outputs that can be expected from an ideal input. Considerably more output

jitter is seen when nonideal input signals are presented to the comparator inputs. Nonideal characteristics include the presence of extraneous, nonharmonic signals (spur’s,

noise), slower slew rate, and low comparator overdrive.

4

Timing of input signals FQ_UD, WCLK, RESET are asynchronous to the reference clock; however, the presence of a reference clock is required to implement those

functions. In the absence of a reference clock, the AD9851 automatically enters power-down mode rendering the IC, including the comparator, inoperable until a refer-

ence clock is restored. Very high speed updates of frequency/phase word will require FQ_UD and WCLK to be externally synchronized with the ex ter nal reference clock to

ensure proper timing.

5

Not applicable when 6

REFCLK Multiplier is engaged.

6

Assumes no capacitive load on DACBP (Pin 17).

Speci cations subject to change without notice.

AD9851

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily ac cu mu late on

the human body and test equipment and can discharge without detection. Although the AD9851 features

proprietary ESD pro tec tion circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD pre cau tions are rec om mend ed to avoid per for mance

deg ra da tion or loss of functionality.

Application Note:

Users are cautioned not to apply digital input signals prior to power-up of this device.

Doing so may result in a latch-up condition.

ABSOLUTE MAXIMUM RATINGS

Maximum Junction Temperature

. . . . . . . . . . . . . . . . . . .

Storage Tem per a ture

. . . . . . . . . . . . . . . . . . .

–65°C to +150°C

V

S

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

6 V

Operating Temperature

. . . . . . . . . . . . . . . . . . .

–40°C to +85°C

Digital Inputs

. . . . . . . . . . . . . . . . . . . . . .

–0.7 V to +V

S

+ 0.7 V

Lead Temperature (10 sec) Soldering

. . . . . . . . . . . . . . . .

300°C

Digital Output Current

. . . . . . . . . . . . . . . . . . . . . . . . . .

30 mA

SSOP

JA

Thermal Impedance

. . . . . . . . . . . . . . . . . . .

82°C/W

DAC Output Current

. . . . . . . . . . . . . . . . . . . . . . . . . . .

30 mA

Absolute maximum ratings are limiting values, to be applied individually, and beyond

which the serviceability of the circuit may be impaired. Functional operability under

any of these conditions is not necessarily implied. Exposure of absolute maximum

rating conditions for extended periods of time may affect device reliability.

EXPLANATION OF TEST LEVELS

Test Level

I

III

Sample Tested Only.

IV

Pa ram e ter is guaranteed by design and char ac ter iza tion

testing.

V

Parameter is a typical value only.

VI

Devices are 100% pro duc tion tested at 25°C and guar an -

teed by design and characterization testing for in dus tri al

operating temperature range.

ORDERING GUIDE

Model

Temperature Range

Package Description

Package Option

AD9851BRS

–40°C to +85°C

Shrink Small Outline (SSOP)

RS-28

AD9851BRSRL

–40°C to +85°C

Shrink Small Outline (SSOP)

RS-28

AD9851/CGPCB

Evaluation Board Clock Generator

AD9851/FSPCB

Evaluation Board Frequency Synthesizer

AD9851

–5

IN FUNCTION DESCRIPTIONS

Pin

No.

Mnemonic

Function

4–1,

D0–D7

8-Bit Data Input. The data port for loading the 32-bit frequency and 8-bit phase/control words. D7 = MSB;

28–25

D0 = LSB. D7, Pin 25, also serves as the input pin for 40-bit serial data word.

5

PGND

6

REFCLK Multiplier Ground Connection.

6

PVCC

6

REFCLK Multiplier Positive Supply Voltage Pin.

7

W_CLK

Word Load Clock. Rising edge loads the parallel or serial frequency/phase/control words asynchronously

into the 40-bit input register.

8

FQ_UD

Frequency Update. A rising edge asynchronously transfers the contents of the 40-bit input register to be

acted upon by the DDS core. FQ_UD should be issued when the contents of the input register are known

to contain only valid, allowable data.

9

REFCLOCK

Reference Clock Input. CMOS/TTL-level pulse train, direct or via the 6

REFCLK Multiplier. In direct

mode, this is also the SYSTEM CLOCK. If the 6

REFCLK Multiplier is engaged, then the out put of the

multiplier is the SYS TEM CLOCK. The rising edge of the SYSTEM CLOCK initiates op er a tions.

AGND

Analog Ground. The ground return for the analog circuitry (DAC and Comparator).

AVDD

Positive supply voltage for analog circuitry (DAC and Comparator, Pin 18) and bandgap volt age ref er ence,

Pin 11.

SET

The DAC’s external R

SET

connection—nominally a 3.92 k

resistor to ground for 10 mA out. This sets

the DAC full-scale output current available from IOUT and IOUTB. R

SET

= 39.93/IOUT.

VOUTN

Voltage Output Negative. The comparator’s complementary CMOS logic level output.

VOUTP

Voltage Output Positive. The comparator’s true CMOS logic level output.

VINN

Voltage Input Negative. The comparator’s inverting input.

VINP

Voltage Input Positive. The comparator’s noninverting input.

DACBP

DAC Bypass Connection. This is the DAC voltage reference bypass connection normally NC (NO

CONNECT) for optimum SFDR performance.

20

IOUTB

The complementary DAC output with same characteristics as IOUT except that

IOUTB = (full-scale

output–IOUT)

IOUT

The true output of the balanced DAC. Current is sourcing and requires current-to-voltage

conversion, usually a resistor or transformer referenced to GND.

IOUT = (full-scale output–IOUTB).

22

RESET

Master Reset pin; active high; clears DDS accumulator and phase offset register to achieve 0 Hz and 0°

output phase. Sets programming to parallel mode and disengages the 6

REFCLK Multiplier. Reset does

not clear the 40-bit input reg is ter. On pow er-up, as sert ing RE SET should be the rst pri or i ty before pro-

gramming com menc es.

23

DVDD

Positive supply voltage pin for digital circuitry.

24

DGND

Dig i tal Ground. The ground return pin for the digital circuitry.

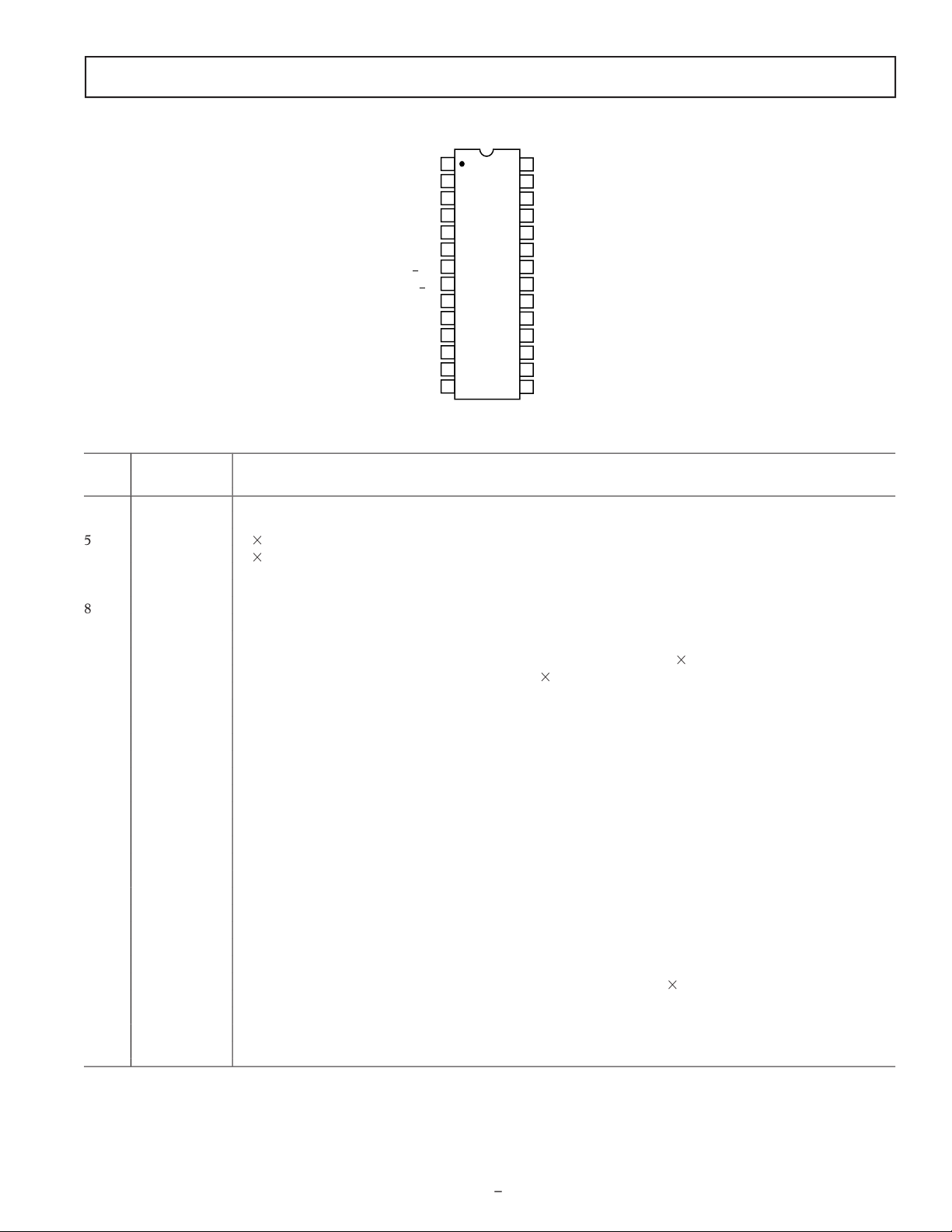

PIN CONFIGURATION

TOP VIEW

(Not to Scale)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AD9851

VOUTP

VOUTN

R

SET

AVDD

AGND

REFCLOCK

FQ UD

D3

D2

D1

LSB D0

PVCC

PGND

VINN

VINP

DACBP

AVDD

AGND

IOUTB

IOUT

D4

D5

D6

D7 MSB/SERIAL LOAD

RESET

DVDD

DGND

W CLK

–6

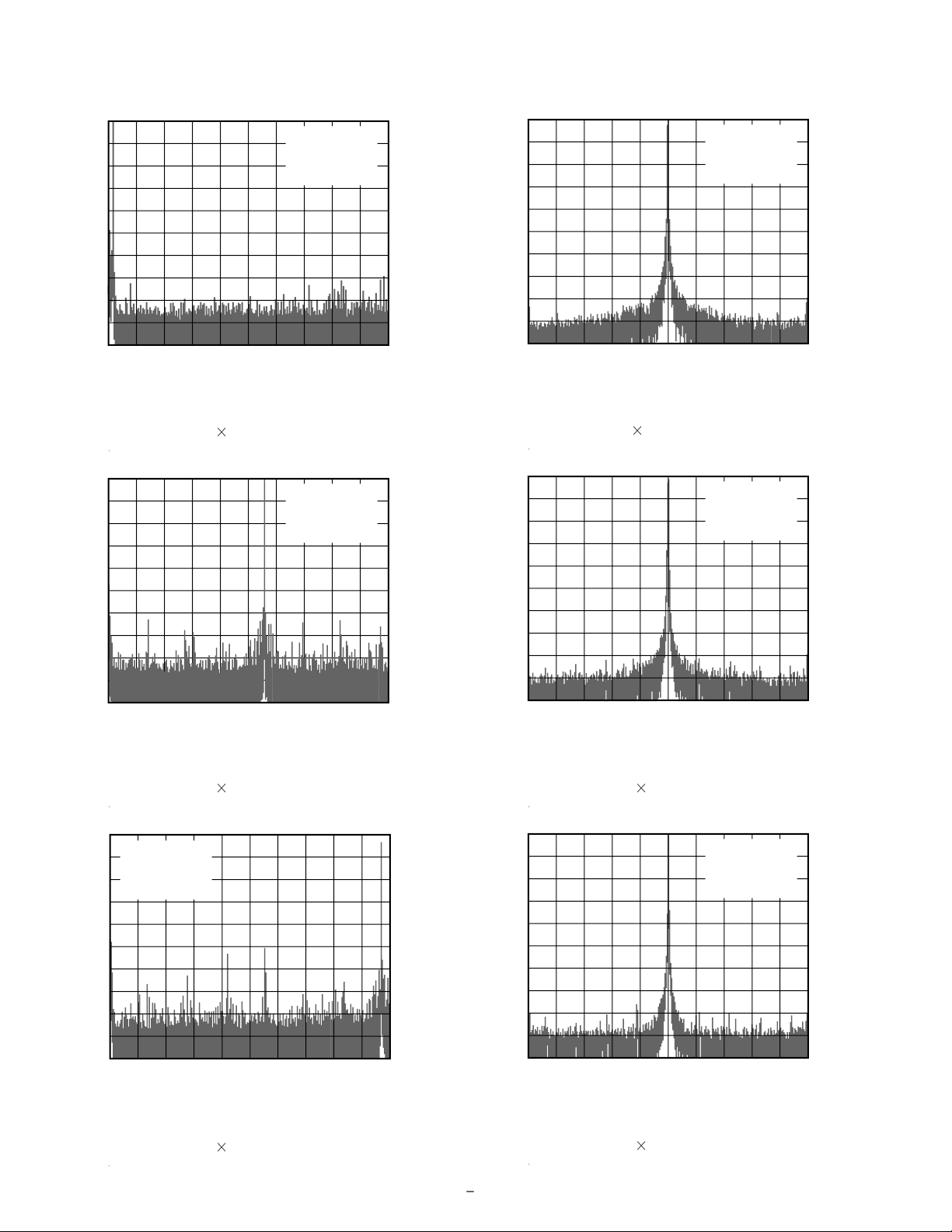

AD9851–Typical Performance Characteristics

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

0Hz

START

72MHz

STOP

7.2MHz/

RBW = 5kHz

VBW = 5kHz

SWT = 7.2s

RF ATT = 20dB

REF LVL = –7dBm

2AP

REFCLK multiplier engaged),

= 5 V.

= 5 V.

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

2AP

0Hz

START

72MHz

STOP

7.2MHz/

RBW = 5kHz

VBW = 5kHz

SWT = 7.2s

RF ATT = 20dB

REF LVL = –7dBm

REFCLK multiplier engaged),

= 5 V.

= 5 V.

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

2AP

0Hz

START

72MHz

STOP

7.2MHz/

RBW = 5kHz

VBW = 5kHz

SWT = 7.2s

RF ATT = 20dB

REF LVL = –7dBm

REFCLK multiplier engaged),

= 5 V.

= 5 V.

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

2AP

1.1MHz

CENTER

200kHz

SPAN

20kHz/

RBW = 300Hz

VBW = 300Hz

SWT = 11.5s

RF ATT = 20dB

REF LVL = –7dBm

REFCLK multiplier engaged),

= 5 V.

= 5 V.

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

2AP

40.1MHz

CENTER

200kHz

SPAN

20kHz/

RBW = 300Hz

VBW = 300Hz

SWT = 11.5s

RF ATT = 20dB

REF LVL = –7dBm

REFCLK multiplier engaged),

= 5 V.

= 5 V.

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

2AP

70.1MHz

CENTER

200kHz

SPAN

20kHz/

RBW = 300Hz

VBW = 300Hz

SWT = 11.5s

RF ATT = 20dB

REF LVL = –7dBm

REFCLK multiplier engaged),

= 5 V.

= 5 V.

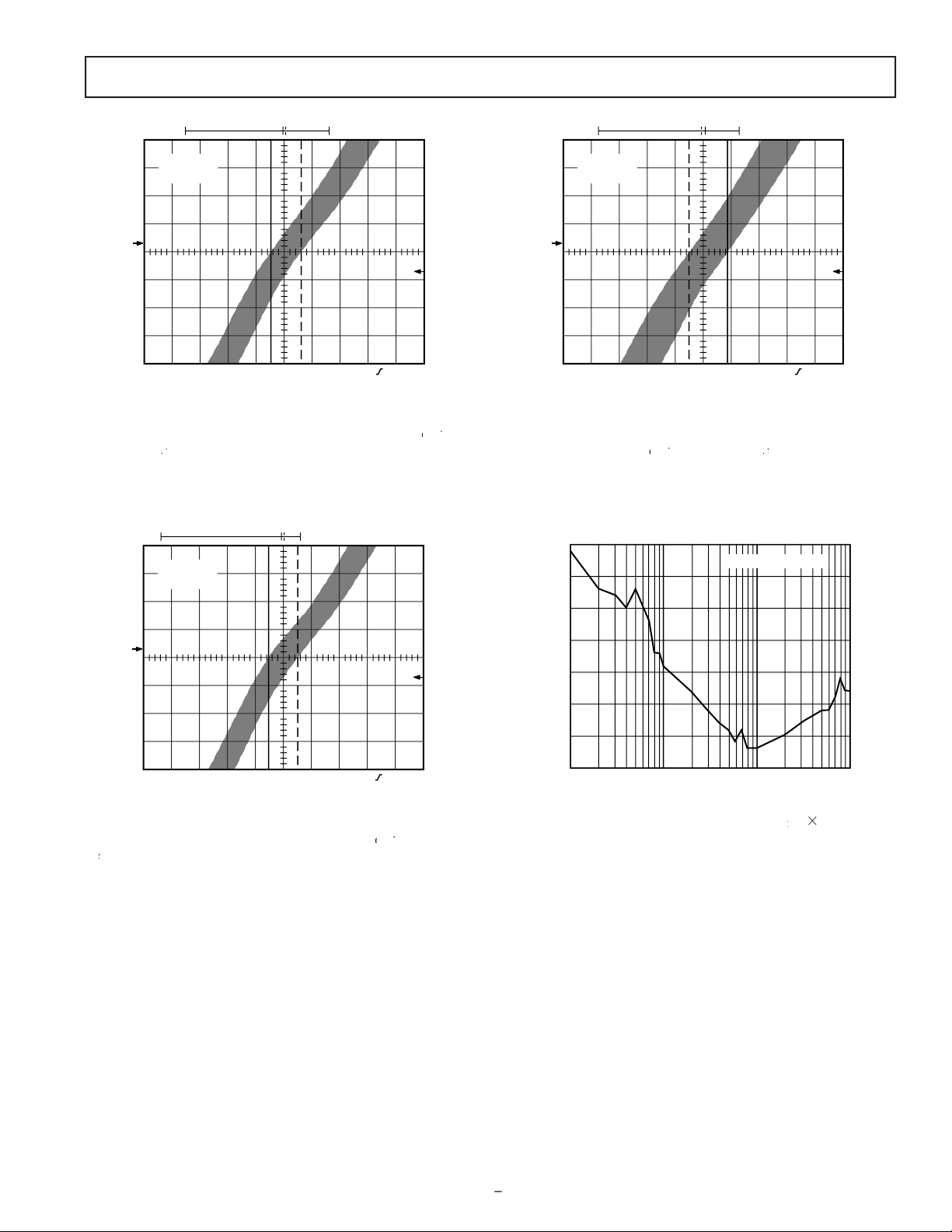

1

Ch1 200mV

T

[ ]

Tek Run 4.00GS/s Sample

M 12.5ns Ch 1 –200mV

D 200ps Runs After

: 208ps

@ : 1.940ns

= 5 V, system clock = 180 MHz, 70 MHz LPF.

= 5 V, system clock = 180 MHz, 70 MHz LPF.

1

Ch1 200mV

T

[ ]

Tek Run 4.00GS/s Sample

M 12.5ns Ch 1 –200mV

D 200ps Runs After

: 204ps

@ : 3.672ns

= 40.1 MHz,

= 40.1 MHz,

= 5 V, system clock = 180 MHz, 70 MHz LPF. Graph details

= 5 V, system clock = 180 MHz, 70 MHz LPF. Graph details

1

Ch1 200mV

T

[ ]

Tek Run 4.00GS/s Sample

: 280ps

@ : 2.668ns

M 12.5ns Ch 1 –200mV

D 200ps Runs After

jitter with the AD9851 con gured as a clock

= 70.1 MHz, V

= 70.1 MHz, V

= 5 V, system

= 5 V, system

FREQUENCY OFFSET – Hz

–145

100

MAGNITUDE – –dBc/Hz

1k 10k 100k

–135

–130

–125

–120

–115

–100

AD9851 PHASE NOISE

–140

REFCLK

–8

FREQUENCY OFFSET – Hz

–155

100

MAGNITUDE – –dBc/Hz

1k 10k 100k

–145

–140

–135

–130

–125

–120

AD9851 RESIDUAL PHASE NOISE

–150

SYSTEM CLOCK FREQUENCY – MHz

45

10

SFDR – –dBc

20 40 60 80 100 120 140 160 180

50

55

60

65

70

75

VS = +3.3V

VS = +5V

FUNDAMENTAL OUTPUT =

SYSTEM CLOCK/3

1

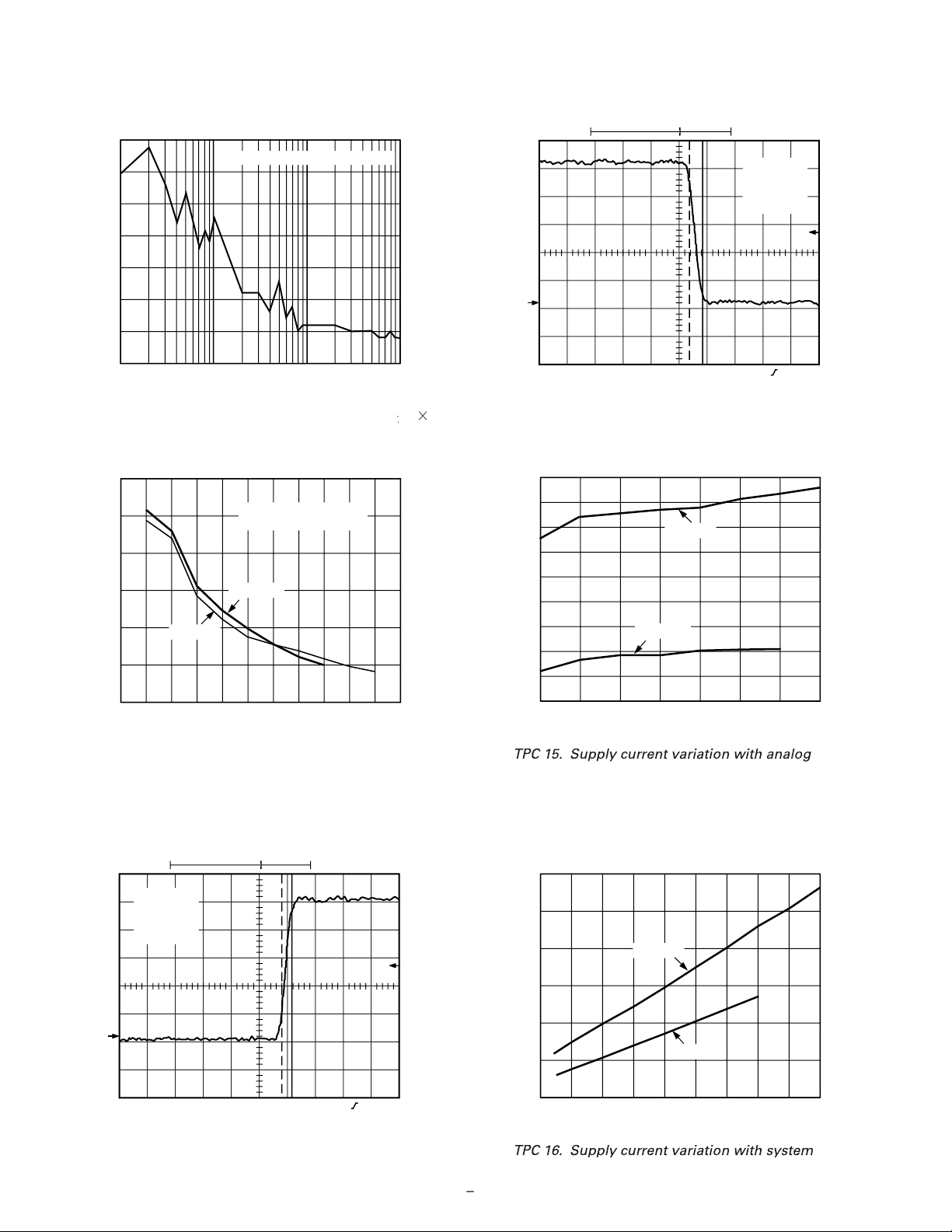

Ch1 100mV

T

[ ]

Tek Stop 2.50GS/s 22 Acgs

: 2.0ns

@ : 105.2ns

C1 Rise

2.03ns

M 20.0ns Ch 1 252mV

D 5.00ns Runs After

1

Ch1 100mV

T

[ ]

Tek Stop 2.50GS/s 2227 Acgs

: 2.3ns

@ : 103.6ns

C1 Fall

2.33ns

M 20.0ns Ch 1 252mV

D 5.00ns Runs After

ANALOG OUTPUT FREQUENCY – MHz

30

10

SUPPLY CURRENT – mA

20 30 40 50 600 70

50

70

80

90

110

120

VS = +3.3V

VS = +5V

100

60

40

SYSTEM CLOCK – MHz

0

140

SUPPLY CURRENT – mA

20 40 60 10080 1200

20

40

60

80

100

120

VS = +3.3V

VS = +5V

160 180

Loading...

Loading...