CCD Signal Processors with

a

FEATURES

AD9848: 10-Bit, 20 MHz Version

AD9849: 12-Bit, 30 MHz Version

Correlated Double Sampler (CDS)

–2 dB to +10 dB Pixel Gain Amplifier (

2 dB to 36 dB 10-Bit Variable Gain Amplifier (VGA)

10-Bit 20 MHz A/D Converter (AD9848)

12-Bit 30 MHz A/D Converter (AD9849)

Black Level Clamp with Variable Level Control

Complete On-Chip Timing Driver

Precision Timing

™

Core with 1 ns Resolution @ 20 MSPS

On-Chip 3 V Horizontal and RG Drivers (AD9848)

On-Chip 5 V Horizontal and RG Drivers (AD9849)

48-Lead LQFP Package

APPLICATIONS

Digital Still Cameras

®

PxGA

)

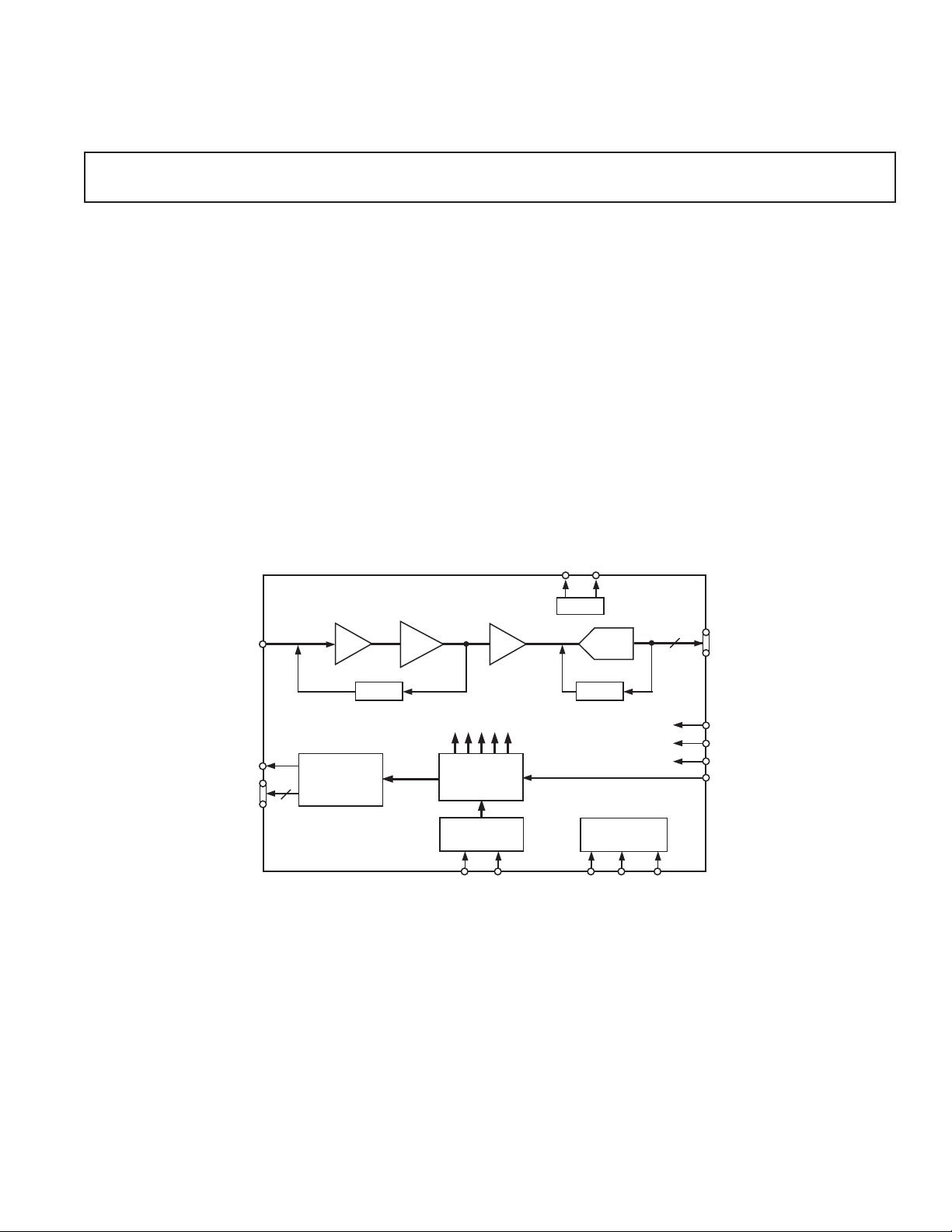

FUNCTIONAL BLOCK DIAGRAM

Integrated Timing Driver

AD9848/AD9849

PRODUCT DESCRIPTION

The AD9848 and AD9849 are highly integrated CCD signal

cessors for digital still camera applications. Both include a complete

analog front end with A/D conversion, combined with a programmable timing driver. The Precision Timing core allows adjustment

of high speed clocks with approximately 1 ns resolution.

The AD9848 is specified at pixel rates of 20 MHz, and the

AD9849 is specified at 30 MHz. The analog front end includes

black level clamping, CDS, PxGA, VGA, and a 10-bit or 12-bit A/D

converter. The timing driver provides the high speed CCD clock

drivers for RG and H1–H4. Operation is programmed using a

3-wire serial interface.

Packaged in a space saving 48-lead LQFP, the AD9848 and

AD9849 are specified over an operating temperature range of

–20°C to +85°C.

VRB

VRT

pro-

CCDIN

RG

H1–H4

CDS

HORIZONTAL

DRIVERS

4

AD9848/AD9849

CLAMP

4ⴞ6dB

PxGA

2dB TO 36dB

VGA

INTERNAL

CLOCKS

PRECISION

TIMING

CORE

SYNC

GENERATOR

HD VD

VREF

ADC

CLAMP

INTERNAL

REGISTERS

SL

10 OR 12

DOUT

CLPOB

CLPDM

PBLK

CLI

SDATASCK

PxGA is a registered trademark and Precision Timing is a trademark of Analog Devices, Inc.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc.

AD9848/AD9849

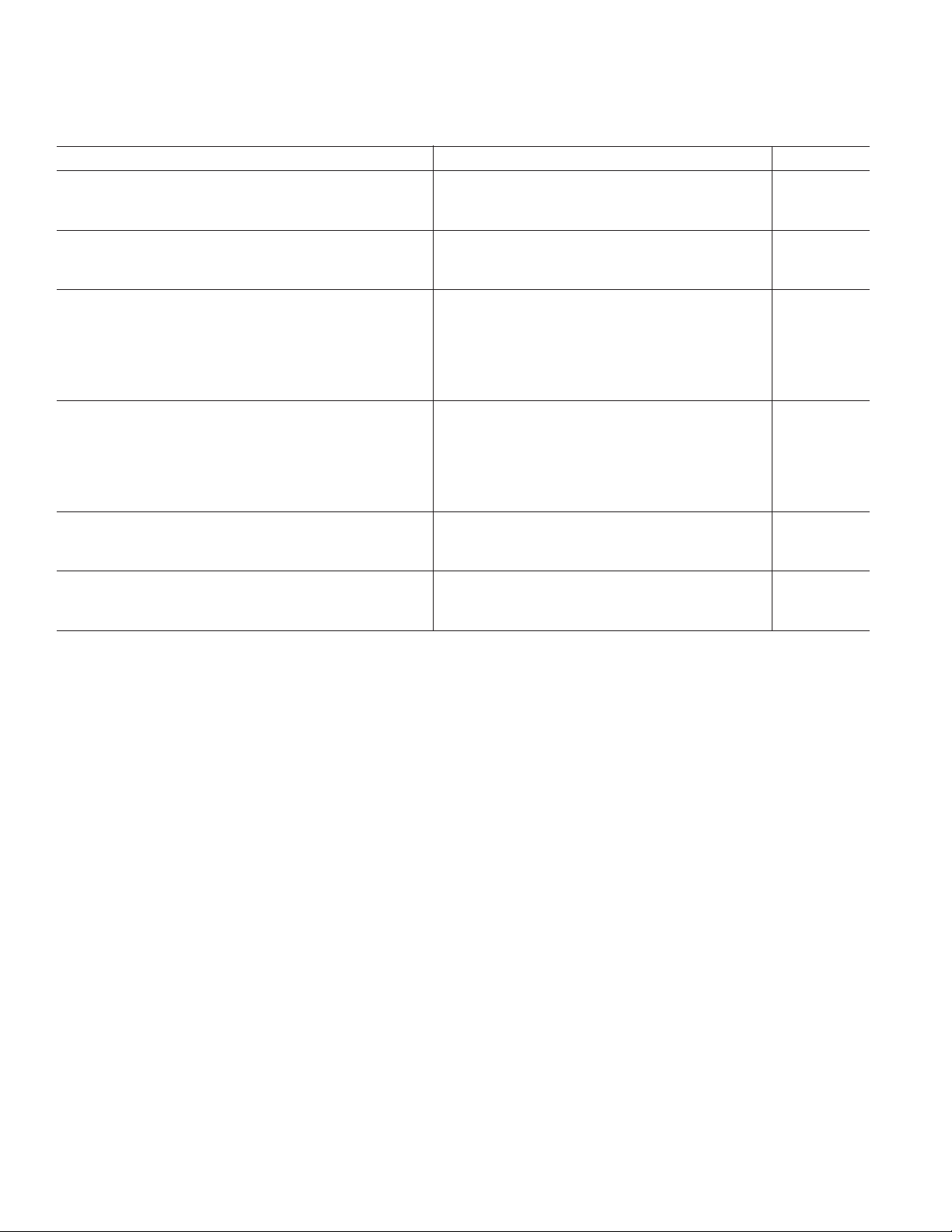

–SPECIFICATIONS

GENERAL SPECIFICATIONS

Parameter Min Typ Max Unit

TEMPERATURE RANGE

Operating –20 +85 °C

Storage –65 +150 °C

MAXIMUM CLOCK RATE

AD9848 20 MHz

AD9849 30 MHz

POWER SUPPLY VOLTAGE, AD9848

Analog (AVDD1, 2, 3) 2.7 3.6 V

Digital1 (DVDD1) H1–H4 2.7 3.6 V

Digital2 (DVDD2) RG 2.7 3.6 V

Digital3 (DVDD3) D0–D11 3.0 V

Digital4 (DVDD4) All Other Digital 3.0 V

POWER SUPPLY VOLTAGE, AD9849

Analog (AVDD1, 2, 3) 2.7 3.6 V

Digital1 (DVDD1) H1–H4 3.0 5.5 V

Digital2 (DVDD2) RG 3.0 5.5 V

Digital3 (DVDD3) D0–D11 3.0 V

Digital4 (DVDD4) All Other Digital 3.0 V

POWER DISSIPATION, AD9848

20 MHz, DVDD1, 2 = 3 V, 100 pF H Loading 220 mW

Total Shutdown Mode 1 mW

POWER DISSIPATION, AD9849

30 MHz, DVDD1, 2 = 5 V, 100 pF H Loading 450 mW

Total Shutdown Mode 1 mW

Specifications subject to change without notice.

–2–

REV. A

AD9848/AD9849

(T

to T

MIN

DIGITAL SPECIFICATIONS

DVDD2 = 5.25 V (AD9849), CL = 20 pF, unless otherwise noted.)

Parameter Symbol Min Typ Max Unit

LOGIC INPUTS

High Level Input Voltage V

Low Level Input Voltage V

High Level Input Current I

Low Level Input Current I

Input Capacitance C

LOGIC OUTPUTS

High Level Output Voltage, I

= 2 mA V

OH

Low Level Output Voltage, IOL = 2 mA V

CLI INPUT

High Level Input Voltage

(AVDD1, 2 + 0.5 V) V

Low Level Input Voltage V

RG AND H-DRIVER OUTPUTS, AD9848

High Level Output Voltage

(DVDD1, 2 – 0.5 V) V

Low Level Output Voltage V

Maximum Output Current (Programmable) 24 mA

Maximum Load Capacitance 100 pF

RG AND H-DRIVER OUTPUTS, AD9849

High Level Output Voltage

(DVDD1, 2 – 0.5 V) V

Low Level Output Voltage V

Maximum Output Current (Programmable) 24 mA

Maximum Load Capacitance 100 pF

Specifications subject to change without notice.

, AVDD1 = DVDD3, DVDD4 = 2.7 V, DVDD1, DVDD2 = 2.7 V (AD9848), DVDD1,

MAX

IH

IL

IH

IL

IN

OH

OL

IH–CLI

IL–CLI

OH

OL

OH

OL

2.1 V

0.6 V

10 µA

10 µA

10 pF

2.2 V

0.5 V

1.85 V

0.85 V

2.2 V

0.5 V

4.75 V

0.5 V

REV. A

–3–

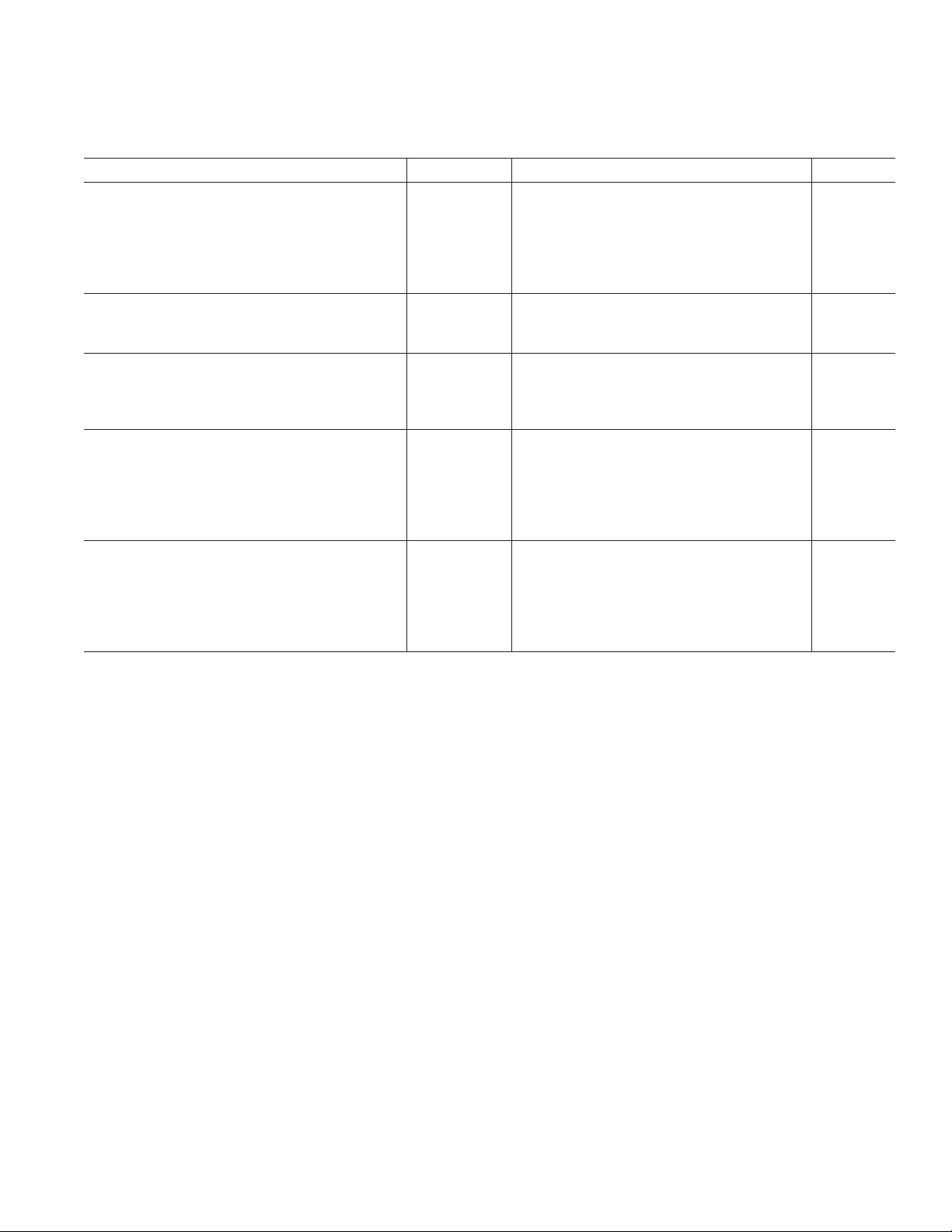

AD9848/AD9849

AD9848–ANALOG SPECIFICATIONS

(T

to T

MIN

, AVDD = DVDD = 3.0 V, f

MAX

= 20 MHz, unless otherwise noted.)

CLI

Parameter Min Typ Max Unit Notes

CDS

Gain 0 dB

Allowable CCD Reset Transient* 500 mV See Input Waveform in Note

Max Input Range Before Saturation* 1.0 V p-p

Max CCD Black Pixel Amplitude* 150 mV

PIXEL GAIN AMPLIFIER (PxGA)

Max Input Range 1.0 V p-p

Max Output Range 1.6 V p-p

Gain Control Resolution 64 Steps

Gain Monotonicity Guaranteed

Gain Range

Min Gain (32) –2 dB

Med Gain (0) 4 dB Medium Gain (4 dB) Is Default Setting

Max Gain (31) 10 dB

VARIABLE GAIN AMPLIFIER (VGA)

Max Input Range 1.6 V p-p

Max Output Range 2.0 V p-p

Gain Control Resolution 1024 Steps

Gain Monotonicity Guaranteed

Gain Range

Low Gain (91) 2 dB

Max Gain (1023) 36 dB

BLACK LEVEL CLAMP

Clamp Level Resolution 256 Steps

Clamp Level Measured at ADC Output

Min Clamp Level (0) 0 LSB

Max Clamp Level (255) 63.75 LSB

A/D CONVERTER

Resolution 10 Bits

Differential Nonlinearity (DNL) ± 0.4 ±1.0 LSB

No Missing Codes Guaranteed

Full-Scale Input Voltage 2.0 V

VOLTAGE REFERENCE

Reference Top Voltage (VRT) 2.0 V

Reference Bottom Voltage (VRB) 1.0 V

SYSTEM PERFORMANCE

VGA Gain Accuracy Specifications Include Entire Signal Chain

Gain Includes 4 dB Default PxGA Gain

Low Gain (91) 5 6 7 dB

Max Gain (1023) 38 39.5 41 dB

Peak Nonlinearity, 500 mV Input Signal 0.2 % 12 dB Gain Applied

Total Output Noise 0.2 LSB rms AC Grounded Input, 6 dB Gain Applied

Power Supply Rejection (PSR) 40 dB Measured with Step Change on Supply

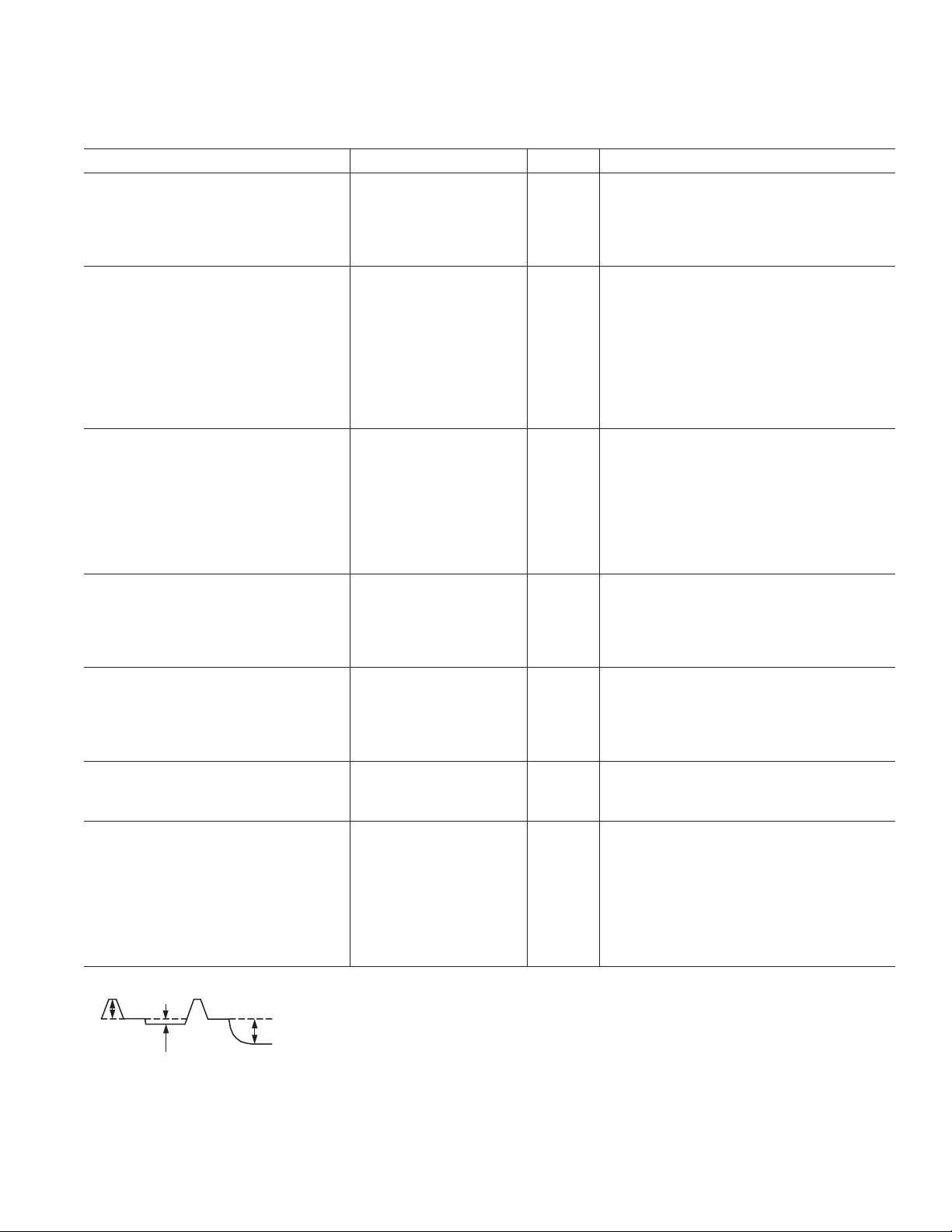

*Input signal characteristics defined as follows:

500mV TYP

RESET

TRANSIENT

Specifications subject to change without notice.

150mV MAX

OPTICAL

BLACK PIXEL

1V MAX

INPUT

SIGNAL RANGE

–4–

REV. A

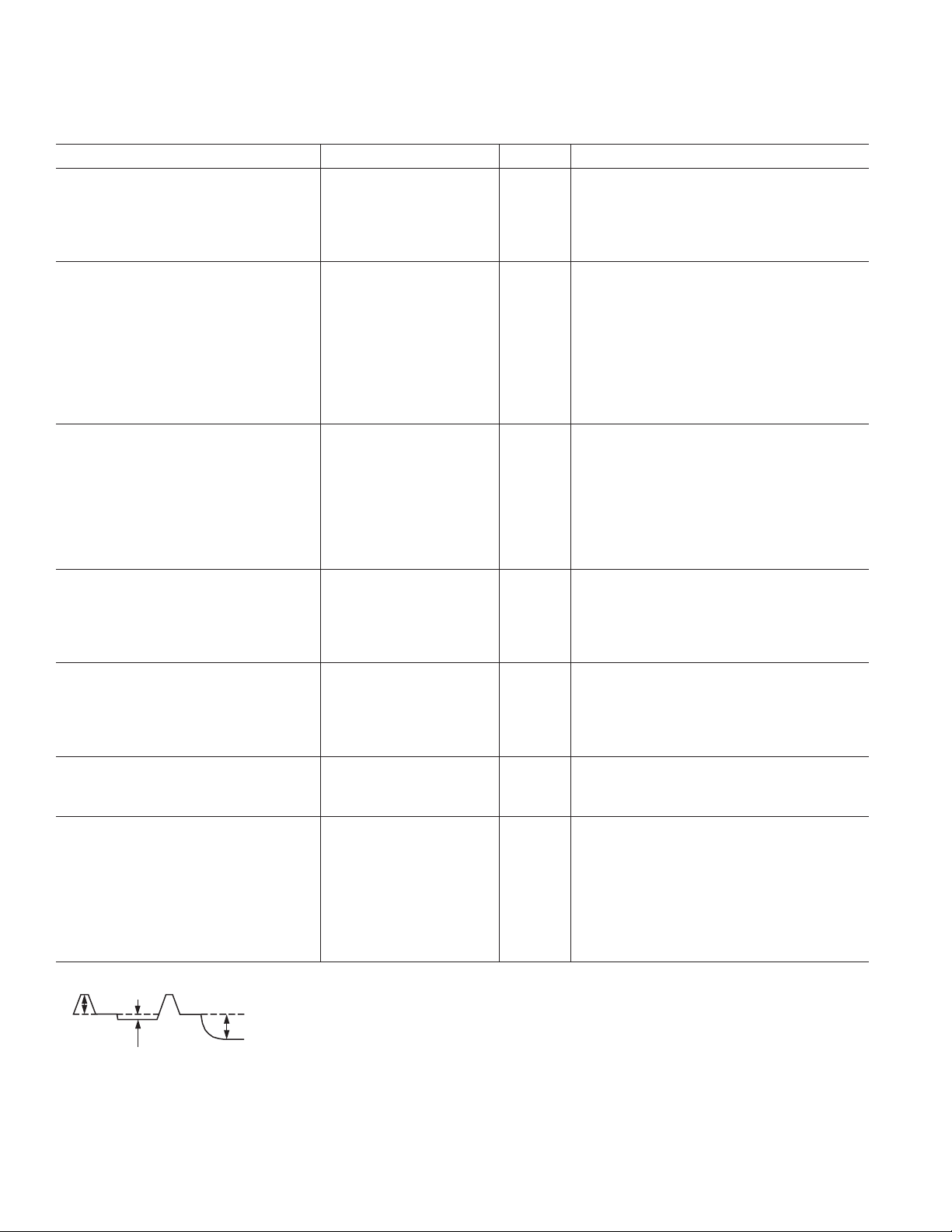

AD9848/AD9849

AD9849–ANALOG SPECIFICATIONS

(T

to T

MIN

, AVDD = DVDD = 3.0 V, f

MAX

= 30 MHz, unless otherwise noted.)

CLI

Parameter Min Typ Max Unit Notes

CDS

Gain 0 dB

Allowable CCD Reset Transient* 500 mV See Input Waveform in Note

Max Input Range Before Saturation* 1.0 V p-p

Max CCD Black Pixel Amplitude* 150 mV

PIXEL GAIN AMPLIFIER (PxGA)

Max Input Range 1.0 V p-p

Max Output Range 1.6 V p-p

Gain Control Resolution 64 Steps

Gain Monotonicity Guaranteed

Gain Range

Min Gain (32) –2 dB

Med Gain (0) 4 dB Medium Gain (4 dB) Is Default Setting

Max Gain (31) 10 dB

VARIABLE GAIN AMPLIFIER (VGA)

Max Input Range 1.6 V p-p

Max Output Range 2.0 V p-p

Gain Control Resolution 1024 Steps

Gain Monotonicity Guaranteed

Gain Range

Low Gain (91) 2 dB

Max Gain (1023) 36 dB

BLACK LEVEL CLAMP

Clamp Level Resolution 256 Steps

Clamp Level Measured at ADC Output

Min Clamp Level (0) 0 LSB

Max Clamp Level (255) 255 LSB

A/D CONVERTER

Resolution 12 Bits

Differential Nonlinearity (DNL) ± 0.5 ±1.0 LSB

No Missing Codes Guaranteed

Full-Scale Input Voltage 2.0 V

VOLTAGE REFERENCE

Reference Top Voltage (VRT) 2.0 V

Reference Bottom Voltage (VRB) 1.0 V

SYSTEM PERFORMANCE

Gain Accuracy Specifications Include Entire Signal Chain

Gain Includes 4 dB Default PxGA Gain

Low Gain (91) 5 6 7 dB

Max Gain (1023) 38 39.5 41 dB

Peak Nonlinearity, 500 mV Input Signal 0.2 % 12 dB Gain Applied

Total Output Noise 0.6 LSB rms AC Grounded Input, 6 dB Gain Applied

Power Supply Rejection (PSR) 40 dB Measured with Step Change on Supply

*Input signal characteristics defined as follows:

500mV TYP

RESET

TRANSIENT

Specifications subject to change without notice.

150mV MAX

OPTICAL

BLACK PIXEL

1V MAX

INPUT

SIGNAL RANGE

REV. A

–5–

AD9848/AD9849

TIMING SPECIFICATIONS

(CL = 20 pF, f

unless otherwise noted.)

= 20 MHz (AD9848) or 30 MHz (AD9849), Serial Timing in Figures 3a and 3b,

CLI

Parameter Symbol Min Typ Max Unit

MASTER CLOCK (CLI), AD9848

CLI Clock Period t

CLI High/Low Pulsewidth t

Delay From CLI to Internal Pixel Period Position t

CLI

ADC

CLIDLY

50 ns

25 ns

6ns

MASTER CLOCK (CLI), AD9849

CLI Clock Period t

CLI High/Low Pulsewidth t

CONV

ADC

33.33 ns

16.67 ns

EXTERNAL MODE CLAMPING

CLPDM Pulsewidth t

CLPOB Pulsewidth* t

CDM

COB

410 Pixels

220 Pixels

SAMPLE CLOCKS

SHP Rising Edge to SHD Rising Edge (AD9848) t

SHP Rising Edge to SHD Rising Edge (AD9849) t

S1

S1

20 ns

13 ns

DATA OUTPUTS

Output Delay from Programmed Edge t

OD

6ns

Pipeline Delay 9 Cycles

SERIAL INTERFACE

Maximum SCK Frequency f

SL to SCK Setup Time t

SCK to SL Hold Time t

SDATA Valid to SCK Rising Edge Setup t

SCK Falling Edge to SDATA Valid Hold t

SCK Falling Edge to SDATA Valid Read t

*Maximum CLPOB pulsewidth is for functional operation only. Wider typical pulses are recommended to achieve low noise clamp reference.

Specifications subject to change without notice.

SCLK

LS

LH

DS

DH

DV

10 MHz

10 ns

10 ns

10 ns

10 ns

10 ns

–6–

REV. A

AD9848/AD9849

ABSOLUTE MAXIMUM RATINGS

With

Parameter Respect To Min Max Unit

AVDD1, 2, 3 AVSS –0.3 +3.9 V

DVDD1, DVDD2 (AD9848) DVSS –0.3 +3.9 V

DVDD1, DVDD2 (AD9849) DVSS –0.3 +5.5 V

DVDD3, 4 DVSS –0.3 +3.9 V

Digital Outputs DVSS3 –0.3 DVDD3 + 0.3 V

CLPOB, CLPDM, BLK DVSS4 –0.3 DVDD4 + 0.3 V

CLI AVSS –0.3 AVDD + 0.3 V

SCK, SL, SDATA DVSS4 –0.3 DVDD4 + 0.3 V

VRT, VRB AVSS –0.3 AVDD + 0.3 V

BYP1–3, CCDIN AVSS –0.3 AVDD + 0.3 V

Junction Temperature 150 °C

Lead Temperature (10 sec) 300 °C

THERMAL CHARACTERISTICS

Thermal Resistance

48-Lead LQFP Package

= 92°C

JA

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD9848/AD9849 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

Model Range Description Option

AD9848AKST –20°C to +85°CThin Plastic Quad ST-48

AD9849AKST –20°C to +85°CThin Plastic Quad ST-48

Temperature Package Package

ORDERING GUIDE

Flatpack (LQFP)

Flatpack (LQFP)

WARNING!

ESD SENSITIVE DEVICE

REV. A

–7–

AD9848/AD9849

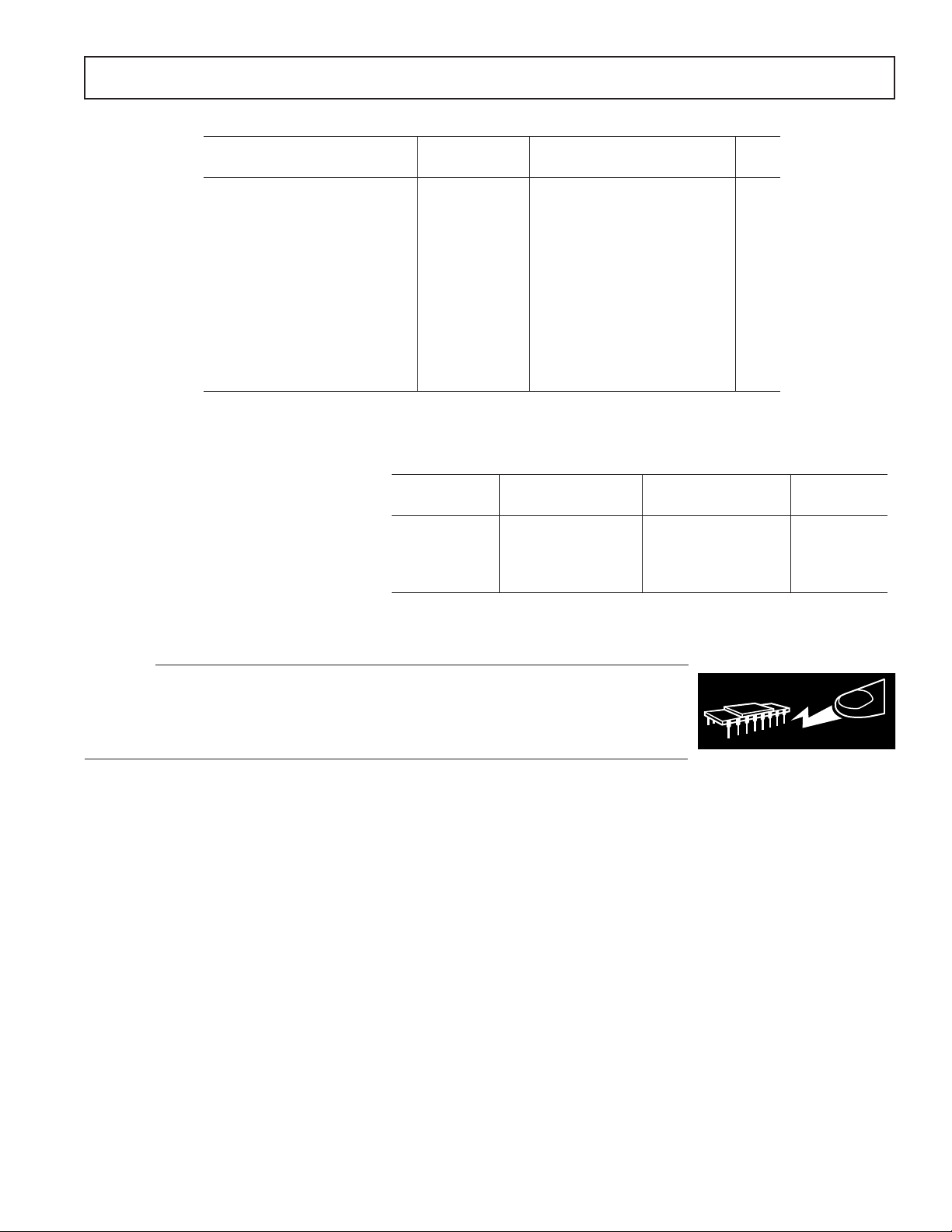

PIN CONFIGURATION

D1

D0 (LSB)

DVDD4

DVSS4HDVD

PBLK

HBLK

CLPDM

CLPOB

SCK

AVSS1

DVDD2

CLI

SDI

36

35

34

33

32

31

30

29

28

27

26

25

AVDD1

SL

REFT

REFB

CMLEVEL

AVSS3

AVDD3

BYP3

CCDIN

BYP2

BYP1

AVDD2

AVSS2

NCNCDVDD4

DVSS4HDVD

PBLK

HBLK

CLPDM

CLPOB

SCK

(LSB) D0

D1

D2

D3

D4

DVSS3

DVDD3

D5

D6

D7

D8

(MSB) D9

NC = NO CONNECT

48 47 46 4 5 44 39 38 3743 4 2 41 40

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

H1

H2

DVSS1

AD9848

TOP VIEW

(Not to Scale)

H3

H4

DVSS2

DVDD1

RG

AVSS1

DVDD2

CLI

SDI

36

35

34

33

32

31

30

29

28

27

26

25

AVDD1

SL

REFT

REFB

CMLEVEL

AVSS3

AVDD3

BYP3

CCDIN

BYP2

BYP1

AVDD2

AVSS2

DVSS3

DVDD3

(MSB) D11

48 47 46 4 5 44 39 38 3743 4 2 41 40

1

D2

PIN 1

2

D3

IDENTIFIER

3

D4

4

D5

D6

5

6

7

D7

8

9

D8

10

D9

11

D10

12

13 14 15 16 17 18 19 20 21 22 23 24

H1

H2

DVSS1

AD9849

TOP VIEW

(Not to Scale)

DVDD1

H3

H4

RG

DVSS2

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Type* Description

1–5 D0–D4 DO Data Outputs AD9848 Only

1–5 D2–D6 DO Data Outputs AD9849 Only

6 DVSS3 P Digital Ground 3 – Data Outputs

7 DVDD3 P Digital Supply 3 – Data Outputs

8–12 D5–D9 DO Data Outputs (D9 is MSB) AD9848 Only

8–12 D7–D11 DO Data Outputs (D9 is MSB) AD9849 Only

13, 14 H1, H2 DO Horizontal Clocks (to CCD)

15 DVSS1 P Digital Ground 1 – H Drivers

16 DVDD1 P Digital Supply 1 – H Drivers

17, 18 H3, H4 DO Horizontal Clocks (to CCD)

19 DVSS2 P Digital Ground 1 – RG Driver

20 RG DO Reset Gate Clock (to CCD)

21 DVDD2 P Digital Supply 2 – RG Driver

22 AVSS1 P Analog Ground 1

23 CLI DI Master Clock Input

24 AVDD1 P Analog Supply 1

25 AVSS2 P Analog Ground 2

26 AVDD2 P Analog Supply 2

27 BYP1 AO Bypass Pin (0.1 µF to AVSS)

28 BYP2 AO Bypass Pin (0.1 µF to AVSS)

29 CCDIN AI Analog Input for CCD Signal

30 BYP3 AO Bypass Pin (0.1 µF to AVSS)

31 AVDD3 P Analog Supply 3

32 AVSS3 P Analog Ground 3

33 CMLEVEL AO Internal Bias Level Decoupling (0.1 µF to AVSS)

34 REFB AO Reference Bottom Decoupling (1.0 µF to AVSS)

35 REFT AO Reference Top Decoupling (1.0 µF to AVSS)

36 SL DI 3-Wire Serial Load (from µP)

37 SDI DI 3-Wire Serial Data Input (from µP)

38 SCK DI 3-Wire Serial Clock (from µP)

39 CLPOB DI Optical Black Clamp Pulse

40 CLPDM DI Dummy Black Clamp Pulse

41 HBLK DI HCLK Blanking Pulse

42 PBLK DI Preblanking Pulse

43 VD DI Vertical Sync Pulse

44 HD DI Horizontal Sync Pulse

45 DVSS4 P Digital Ground 4 – VD, HD, CLPOB, CLPDM, HBLK, PBLK, SCK, SL, SDATA

46 DVDD4 P Digital Supply 4 – VD, HD, CLPOB, CLPDM, HBLK, PBLK, CK, SL, SDATA

47, 48 NC NC Internally Not Connected AD9848 Only

47, 48 D0, D1 DO Data Output (D0 is LSB) AD9849 Only

*Type: AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, P = Power

–8–

REV. A

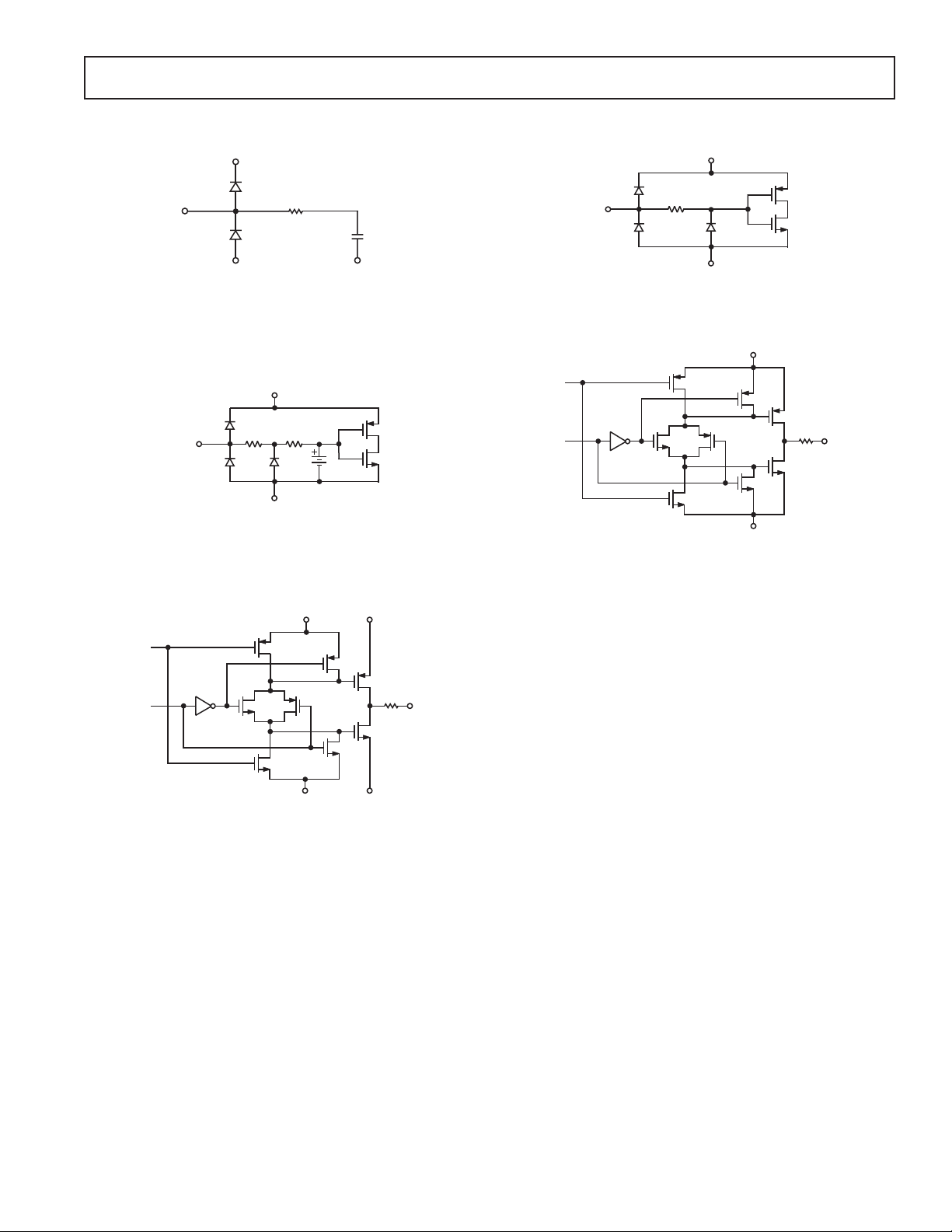

EQUIVALENT INPUT/OUTPUT CIRCUITS

DVDD4

DVSS4

330⍀

AVDD2

R

AD9848/AD9849

DATA

THREE-

STATE

AVSS2

Circuit 1. CCDIN (Pin 29)

AVDD1

330⍀

CLI

25k⍀

1.4V

AVSS1

Circuit 2. CLI (Pin 23)

DVDD4 DVDD3

AVSS2

DOUT

Circuit 4. Digital Inputs (Pins 36–44)

DVDD1

DATA

ENABLE

DVSS1

Circuit 5. H1–H4 and RG (Pins 13, 14, 17, 18, 20)

OUTPUT

DVSS4 DVSS3

Circuit 3. Data Outputs D0–D11 (Pins 1–5, 8–12, 47–48)

REV. A

–9–

AD9848/AD9849

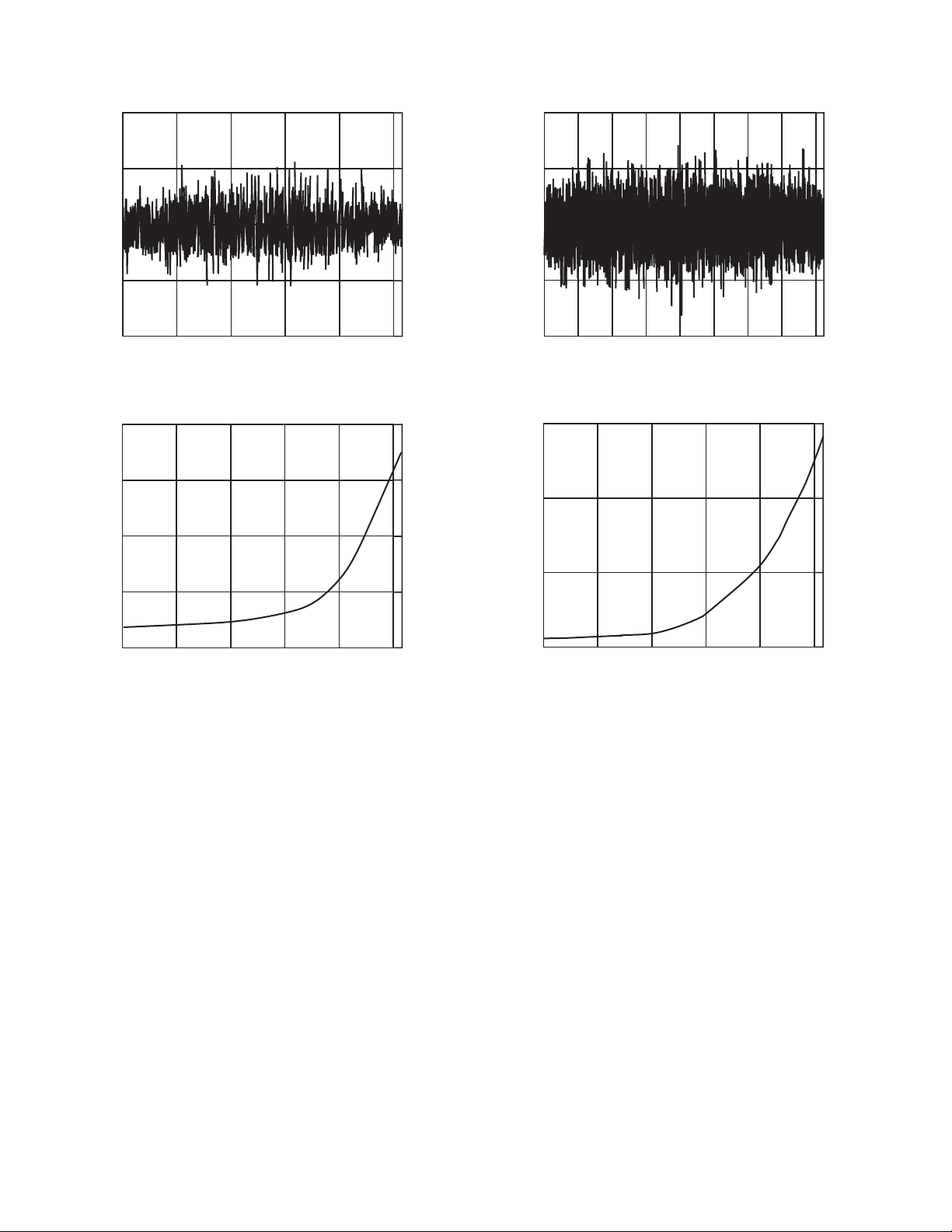

—Typical Performance Characteristics

0.50

0.25

–0.25

–0.50

0

0

200 600 800

400

TPC 1. AD9848 Typical DNL

4

3

2

1000

0.5

0.25

–0.25

–0.5

0

0

500

1500 2000 2500 3000 3500 4000

1000

TPC 3. AD9849 Typical DNL

15

10

OUTPUT NOISE – LSB

1

0

0

200

400

VGA GAIN CODE – LSB

600 800

1000

TPC 2. AD9848 Output Noise vs. VGA Gain Setting

5

OUTPUT NOISE – LSB

0

0

200

400

VGA GAIN CODE – LSB

600

800

1000

TPC 4. AD9849 Output Noise vs. VGA Gain Setting

–10–

REV. A

Loading...

Loading...