Dual 8-/10-/12-/14-/16-Bit

250 MSPS Digital-to-Analog Converters

AD9741/AD9743/AD9745/AD9746/AD9747

FEATURES

High dynamic range, dual DACs

Low noise and intermodulation distortion

Single carrier WCDMA ACLR = 80 dBc @ 61.44 MHz IF

Innovative switching output stage permits useable outputs

beyond Nyquist frequency

LVCMOS inputs with dual-port or optional interleaved

single-port operation

Differential analog current outputs are programmable from

8.6 mA to 31.7 mA full scale

Auxiliary 10-bit current DACs with source/sink capability for

external offset nulling

Internal 1.2 V precision reference voltage source

Operates from 1.8 V and 3.3 V supplies

315 mW power dissipation

Small footprint, Pb-free, 72-Lead LFCSP

APPLICATIONS

Wireless infrastructure:

WCDMA, CDMA2000, TD-SCDMA, WiMAX

Wideband communications:

LMDS/MMDS, point-to-point

Instrumentation:

RF signal generators, arbitrary waveform generators

GENERAL DESCRIPTION

The AD9741/AD9743/AD9745/AD9746/AD9747 are pincompatible, high dynamic range, dual digital-to-analog

converters (DACs) with 8-/10-/12-/ 14-/16-bit resolutions

and sample rates of up to 250 MSPS. The devices include

specific features for direct conversion transmit applications,

including gain and offset compensation, and they interface

seamlessly with analog quadrature modulators, such as the

ADL5370.

A proprietary, dynamic output architecture permits synthesis

of analog outputs even above Nyquist by shifting energy away

from the fundamental and into the image frequency.

Full programmability is provided through a serial peripheral

interface (SPI) port. In addition, some pin-programmable

features are offered for those applications without a controller.

PRODUCT HIGHLIGHTS

1. Low noise and intermodulation distortion (IMD) enables

high quality synthesis of wideband signals.

2. Proprietary switching output for enhanced dynamic

performance.

3. Programmable current outputs and dual auxiliary DACs

provide flexibility and system enhancements.

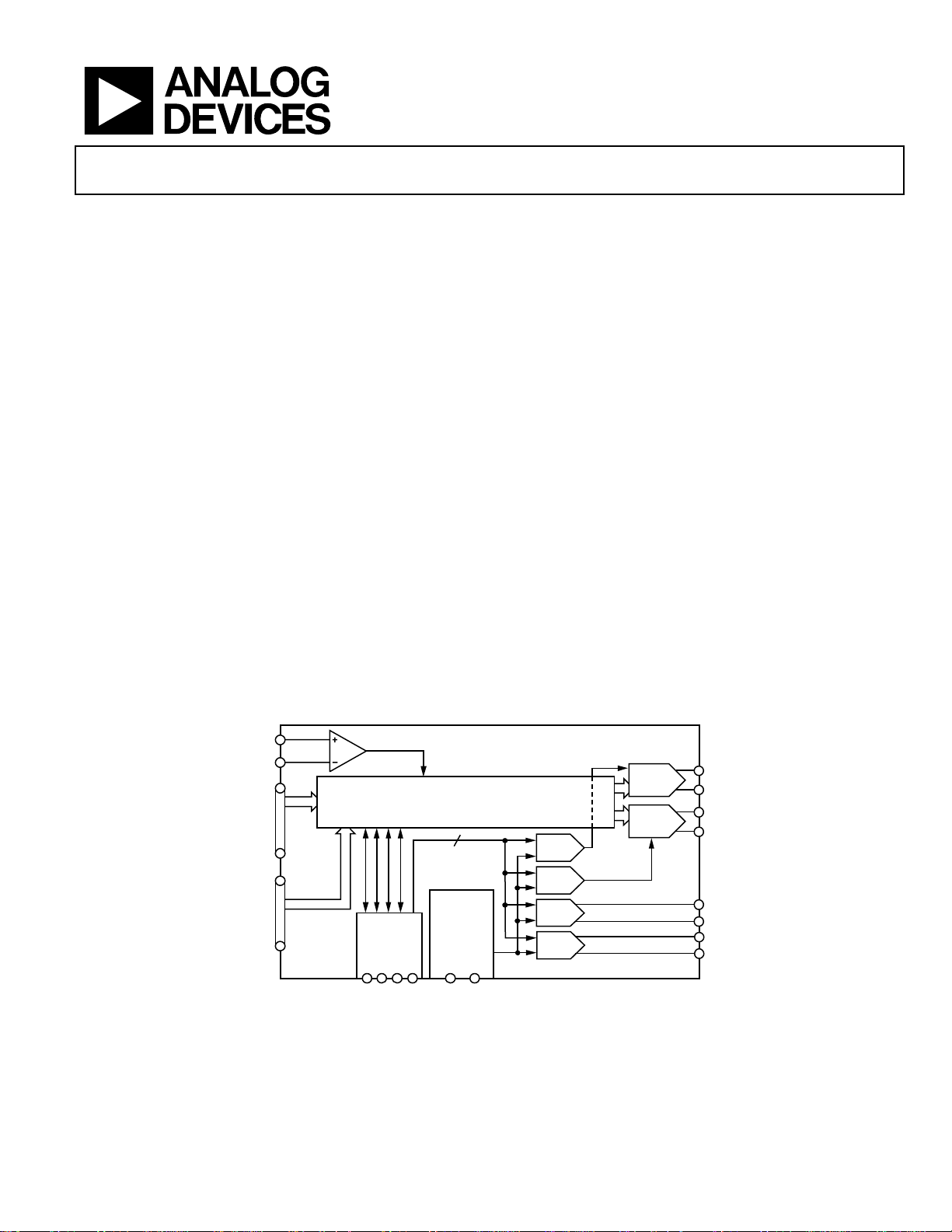

FUNCTIONAL BLOCK DIAGRAM

CLKP

CLKN

PID<15:0>

CMOS

INTERFACE

P2D<15:0>

SERIAL

PERIPHERAL

INTERFACE

SDO

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

INTERFACE L OGIC

CSB

SDIO

SCLK

INTERNAL

REFERENCE

AND

BIAS

REFIO

10

FSADJ

Figure 1.

16-BIT

DAC1

16-BIT

DAC2

GAIN

DAC

GAIN

DAC

OFFSET

DAC

OFFSET

DAC

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

IOUT1P

IOUT1N

IOUT2P

IOUT2N

AUX1P

AUX1N

AUX2P

AUX2N

06569-001

AD9741/AD9743/AD9745/AD9746/AD9747

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

DC Specifications ......................................................................... 3

AC Specifications.......................................................................... 5

Digital and Timing Specifications.............................................. 7

Absolute Maximum Ratings............................................................ 8

Thermal Resistance ...................................................................... 8

ESD Caution.................................................................................. 8

Pin Configurations and Function Descriptions ........................... 9

Typical Performance Characteristics ........................................... 14

Terminology .................................................................................... 17

Theory of Operation ...................................................................... 18

Serial Peripheral Interface......................................................... 18

General Operation of the Serial Interface............................... 18

Instruction Byte.......................................................................... 18

MSB/LSB Transfers .................................................................... 19

Serial Interface Port Pin Descriptions..................................... 19

SPI Register Map ............................................................................ 20

SPI Register Descriptions.............................................................. 21

Digital Inputs and Outputs ........................................................... 22

Input Data Timing ..................................................................... 22

Dual-Port Mode Timing ........................................................... 22

Single-Port Mode Timing ......................................................... 22

SPI Port, Reset, and Pin Mode.................................................. 22

Driving the DAC Clock Input .................................................. 23

Full-Scale Current Generation ................................................. 23

DAC Transfer Function............................................................. 24

Analog Modes of Operation ..................................................... 24

Auxiliary DACS .......................................................................... 25

Power Dissipation....................................................................... 25

Outline Dimensions....................................................................... 27

Ordering Guide .......................................................................... 27

REVISION HISTORY

5/07—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

AD9741/AD9743/AD9745/AD9746/AD9747

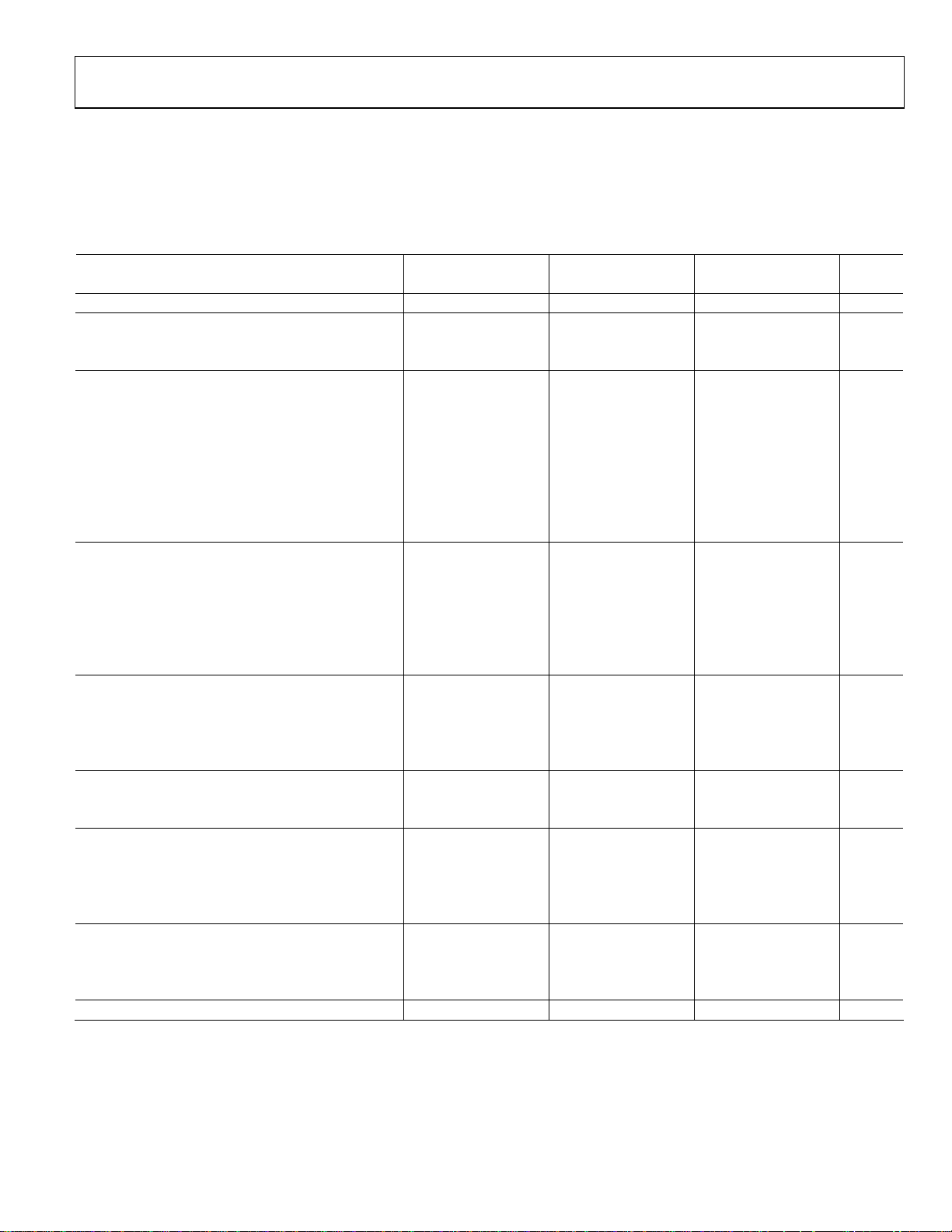

SPECIFICATIONS

DC SPECIFICATIONS

T

to T

MIN

sample rate, unless otherwise noted.

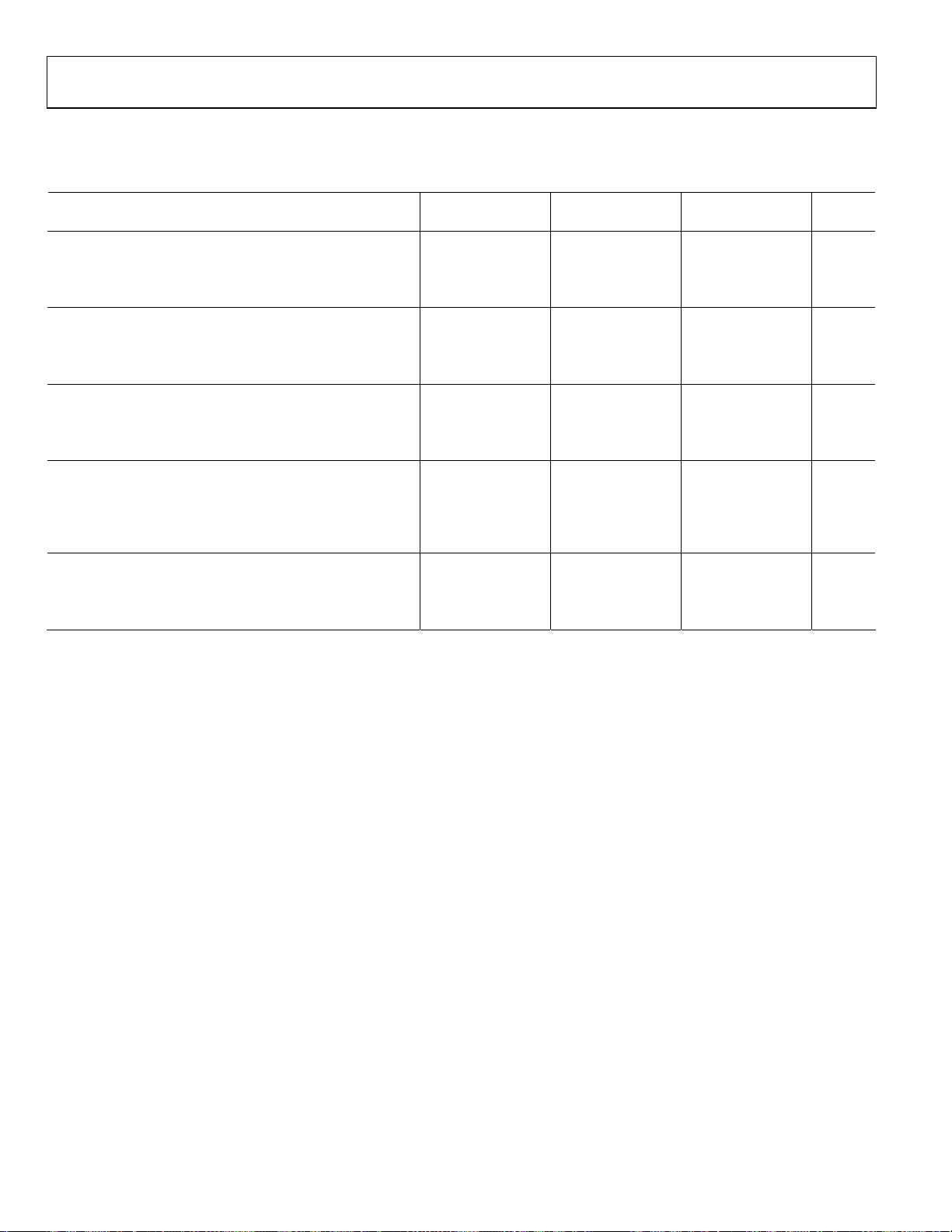

Table 1. AD9741, AD9743, and AD9745

Parameter

RESOLUTION 8 10 12 Bits

ACCURACY

Differential Nonlinearity (DNL) ±0.03 ±0.05 ±0.13 LSB

Integral Nonlinearity (INL) ±0.05 ±0.10 ±0.25 LSB

MAIN DAC OUTPUTS

Offset Error ±0.001 ±0.001 ±0.001 %FSR

Offset Error Temperature Coefficient 1.0 1.0 1.0 ppm/°C

Gain Error ±2.0 ±2.0 ±2.0 %FSR

Gain Error Temperature Coefficient 100 100 100 ppm/°C

Gain Matching (DAC1 to DAC2) ±1.0 ±1.0 ±1.0 %FSR

Full-Scale Output Current 8.6 31.7 8.6 31.7 8.6 31.7 mA

Output Compliance Voltage −1.0 +1.0 −1.0 +1.0 −1.0 +1.0 V

Output Resistance 10 10 10 MΩ

AUXILIARY DAC OUTPUTS

Resolution 10 10 10 Bits

Full-Scale Output Current −2.0 +2.0 −2.0 +2.0 −2.0 +2.0 mA

Output Compliance Voltage Range—Sink Current 0.8 1.6 0.8 1.6 0.8 1.6 V

Output Compliance Voltage Range—Source Current 0 1.6 0 1.6 0 1.6 V

Output Resistance 1 1 1 MΩ

Monotonicity 10 10 10 Bits

REFERENCE INPUT/OUTPUT

Output Voltage 1.2 1.2 1.2 V

Output Voltage Temperature Coefficient 10 10 10 ppm/°C

External Input Voltage Range 1.15 1.3 1.15 1.3 1.15 1.3 V

Input or Output Resistance 5 5 5 kΩ

POWER SUPPLY VOLTAGES

AVDD33, DVDD33 3.13 3.47 3.13 3.47 3.13 3.47 V

CVDD18, DVDD18 1.70 1.90 1.70 1.90 1.70 1.90 V

POWER SUPPLY CURRENTS

I

AVDD33

I

DVDD33

I

CVDD18

I

DVDD18

POWER DISSIPATION

f

DAC

DAC Outputs Disabled 115 115 120 mW

Full Device Power-Down 3 3 3 mW

OPERATING TEMPERATURE −40 +85 −40 +85 −40 +85 °C

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, full-scale digital input, maximum

MAX

AD9741 AD9743 AD9745

Min Typ Max Min Typ Max Min Typ Max

Unit

56 60 56 60 56 60 mA

10 14 10 14 11 15 mA

18 22 18 22 18 22 mA

28 32 29 33 30 34 mA

= 250 MSPS, f

= 20 MHz 300 345 300 345 305 350 mW

OUT

Rev. 0 | Page 3 of 28

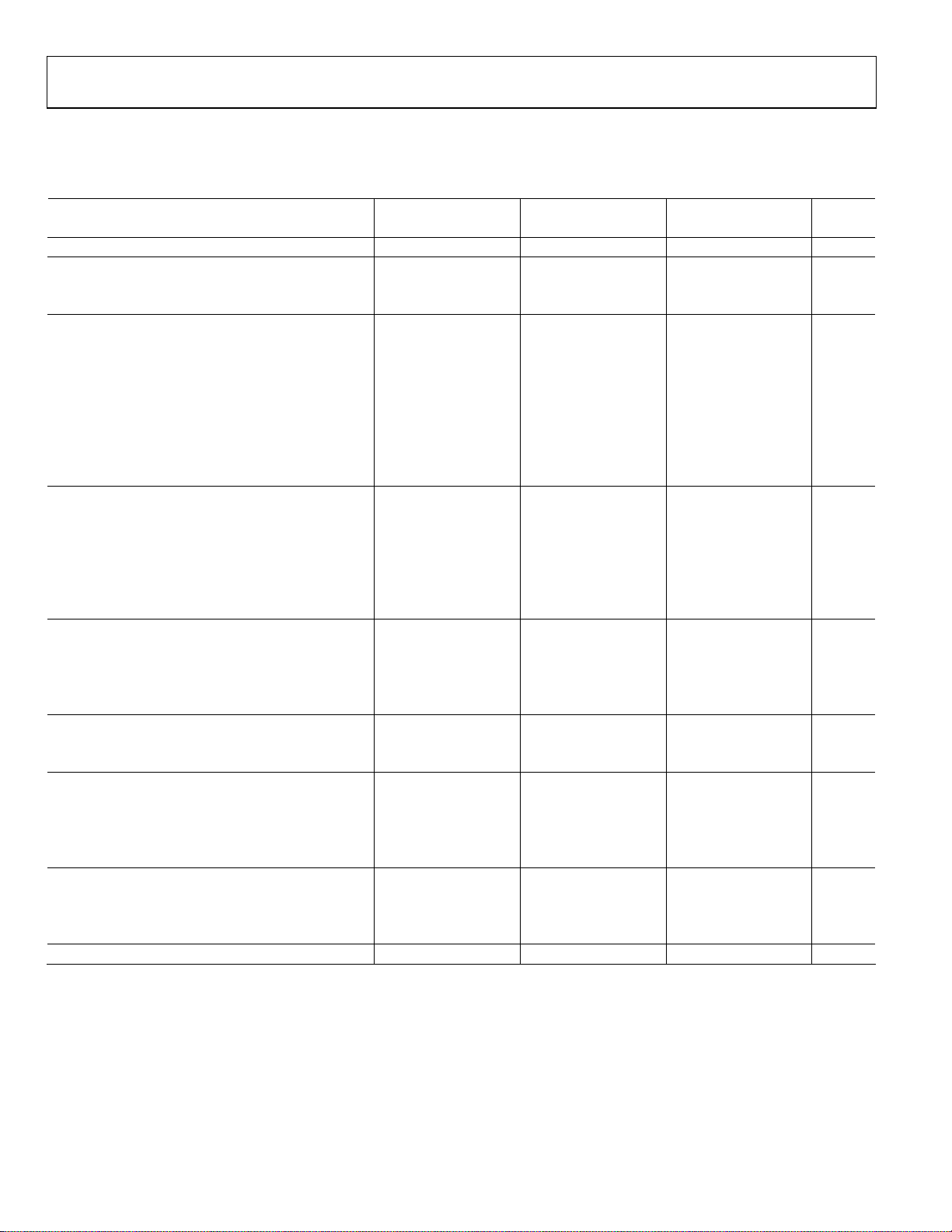

AD9741/AD9743/AD9745/AD9746/AD9747

T

to T

MIN

sample rate, unless otherwise noted. The AD9745 is repeated in

Table 2. AD9745, AD9746, and AD9747

Parameter

RESOLUTION 12 14 16 Bits

ACCURACY

Differential Nonlinearity (DNL) ±0.13 ±0.5 ±2.0 LSB

Integral Nonlinearity (INL) ±0.25 ±1.0 ±4.0 LSB

MAIN DAC OUTPUTS

Offset Error ±0.001 ±0.001 ±0.001 %FSR

Offset Error Temperature Coefficient 0.1 0.1 0.1 ppm/°C

Gain Error ±2.0 ±2.0 ±2.0 %FSR

Gain Error Temperature Coefficient 100 100 100 ppm/°C

Gain Matching (DAC1 to DAC2) ±1.0 ±1.0 ±1.0 %FSR

Full-Scale Output Current 8.6 31.7 8.6 31.7 8.6 31.7 mA

Output Compliance Voltage −1.0 +1.0 −1.0 +1.0 −1.0 +1.0 V

Output Resistance 10 10 10 MΩ

AUXILIARY DAC OUTPUTS

Resolution 10 10 10 Bits

Full-Scale Output Current −2.0 +2.0 −2.0 +2.0 −2.0 +2.0 mA

Output Compliance Voltage Range—Sink Current 0.8 1.6 0.8 1.6 0.8 1.6 V

Output Compliance Voltage Range—Source Current 0 1.6 0 1.6 0 1.6 V

Output Resistance 1 1 1 MΩ

Monotonicity 10 10 10 Bits

REFERENCE INPUT/OUTPUT

Output Voltage 1.2 1.2 1.2 V

Output Voltage Temperature Coefficient 10 10 10 ppm/°C

External Input Voltage Range 1.15 1.3 1.15 1.3 1.15 1.3 V

Input or Output Resistance 5 5 5 kΩ

POWER SUPPLY VOLTAGES

AVDD33, DVDD33 3.13 3.47 3.13 3.47 3.13 3.47 V

CVDD18, DVDD18 1.70 1.90 1.70 1.90 1.70 1.90 V

POWER SUPPLY CURRENTS

I

AVDD33

I

DVDD33

I

CVDD18

I

DVDD18

POWER DISSIPATION

f

DAC

DAC Outputs Disabled 120 125 125 mW

Full Device Power-Down 3 3 3 mW

OPERATING TEMPERATURE −40 +85 −40 +85 −40 +85 °C

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, full-scale digital input, maximum

MAX

Tabl e 2 so the user can compare it with all other parts.

AD9745 AD9746 AD9747

Min Typ Max Min Typ Max Min Typ Max

Unit

56 60 56 60 56 60 mA

11 15 12 16 12 16 mA

18 22 18 22 18 22 mA

30 34 31 35 32 36 mA

= 250 MSPS, f

= 20 MHz 305 350 310 355 310 355 mW

OUT

Rev. 0 | Page 4 of 28

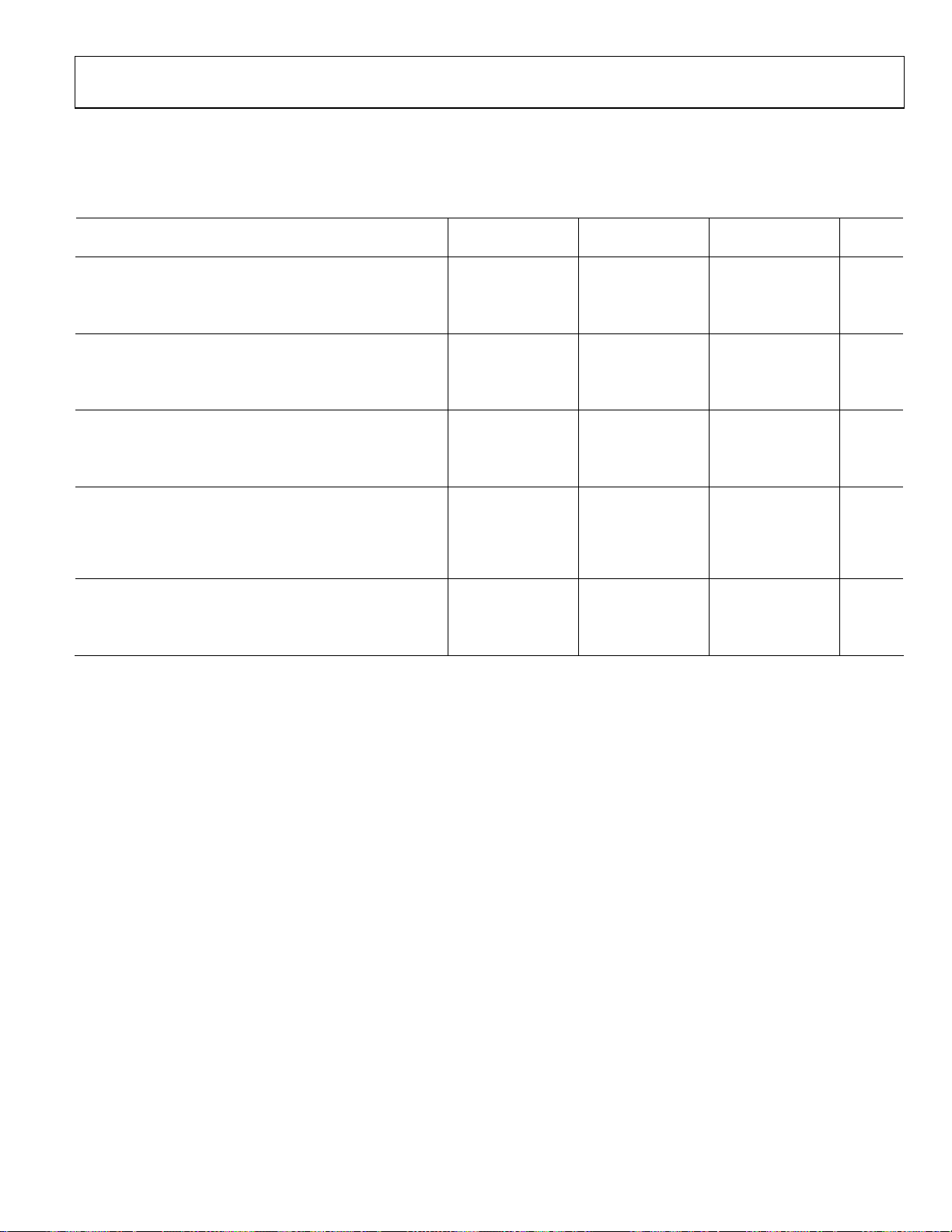

AD9741/AD9743/AD9745/AD9746/AD9747

AC SPECIFICATIONS

T

to T

MIN

sample rate, unless otherwise noted.

Table 3. AD9741, AD9743, and AD9745

Parameter

SPURIOUS FREE DYNAMIC RANGE (SFDR)

f

DAC

f

DAC

f

DAC

INTERMODULATION DISTORTION (IMD)

f

DAC

f

DAC

f

DAC

CROSSTALK

f

DAC

f

DAC

f

DAC

ADJACENT CHANNEL LEAKAGE RATIO (ACLR) SINGLE

CARRIER WCDMA

f

DAC

f

DAC

f

DAC

NOISE SPECTRAL DENSITY (NSD)

f

DAC

f

DAC

f

DAC

1

Mix Mode.

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, full-scale digital input, maximum

MAX

AD9741 AD9743 AD9745

Min Typ Max Min Typ Max Min Typ Max

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 20 MHz 70 80 82 dBc

OUT

= 70 MHz 70 70 70 dBc

OUT

= 180 MHz

OUT

= 20 MHz 80 80 86 dBc

OUT

= 70 MHz 80 80 80 dBc

OUT

= 180 MHz

OUT

= 20 MHz 80 80 80 dBc

OUT

= 70 MHz 80 80 80 dBc

OUT

= 180 MHz

OUT

1

1

1

64 64 66 dBc

72 72 74 dBc

80 80 80 dBc

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 15.36 MHz 54 66 76 dBc

OUT

= 61.44 MHz 54 66 76 dBc

OUT

= 184.32 MHz

OUT

= 15.36 MHz −132 −144 −155 dBm/Hz

OUT

= 61.44 MHz −132 −144 −155 dBm/Hz

OUT

= 184.32 MHz

OUT

1

1

54 64 72 dBc

−135 −147 −155 dBm/Hz

Unit

Rev. 0 | Page 5 of 28

AD9741/AD9743/AD9745/AD9746/AD9747

T

to T

MIN

sample rate, unless otherwise noted. The AD9745 is repeated in Table 4 so the user can compare it with all other parts.

Table 4. AD9745, AD9746, and AD9747

Parameter

SPURIOUS FREE DYNAMIC RANGE (SFDR)

f

DAC

f

DAC

f

DAC

INTERMODULATION DISTORTION (IMD)

f

DAC

f

DAC

f

DAC

CROSSTALK

f

DAC

f

DAC

f

DAC

ADJACENT CHANNEL LEAKAGE RATIO (ACLR) SINGLE

CARRIER WCDMA

f

DAC

f

DAC

f

DAC

NOISE SPECTRAL DENSITY (NSD)

f

DAC

f

DAC

f

DAC

1

Mix Mode.

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, full-scale digital input, maximum

MAX

AD9745 AD9746 AD9747

Min Typ Max Min Typ Max Min Typ Max

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 250 MSPS, f

= 20 MHz 82 82 82 dBc

OUT

= 70 MHz 70 70 70 dBc

OUT

= 180 MHz1 66 66 66 dBc

OUT

= 20 MHz 86 86 86 dBc

OUT

= 70 MHz 80 80 80 dBc

OUT

= 180 MHz1 74 74 74 dBc

OUT

= 20 MHz 80 80 80 dBc

OUT

= 70 MHz 80 80 80 dBc

OUT

= 180 MHz1 80 80 80 dBc

OUT

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 245.76 MSPS, f

= 15.36 MHz 76 78 82 dBc

OUT

= 61.44 MHz 76 78 80 dBc

OUT

= 184.32 MHz1 72 74 74 dBc

OUT

= 15.36 MHz −155 −163 −165 dBm/Hz

OUT

= 61.44 MHz −155 −160 −162 dBm/Hz

OUT

= 184.32 MHz1 −155 −158 −160 dBm/Hz

OUT

Unit

Rev. 0 | Page 6 of 28

AD9741/AD9743/AD9745/AD9746/AD9747

DIGITAL AND TIMING SPECIFICATIONS

T

to T

MIN

sample rate, unless otherwise noted.

Table 5. AD9741/AD9743/AD9745/AD9746/AD9747

Parameter Min Typ Max Unit

DAC CLOCK INPUTS (CLKP, CLKN)

Differential Peak-to-Peak Voltage 400 800 1600 mV

Single-Ended Peak-to-Peak Voltage 800 mV

Common-Mode Voltage 300 400 500 mV

Input Current 1 μA

Input Frequency 250 MHz

DATA CLOCK OUTPUT (DCO)

Output Voltage High 2.4 V

Output Voltage Low 0.4 V

Output Current 10 mA

DAC Clock to Data Clock Output Delay (t

DATA PORT INPUTS

Input Voltage High 2.0 V

Input Voltage Low 0.8 V

Input Current 1 μA

Data to DAC Clock Setup Time (t

Data to DAC Clock Hold Time (t

DAC Clock to Analog Output Data Latency (Dual-Port Mode) 7 Cycles

Data or IQSEL Input to DAC Clock Setup Time (t

Data or IQSEL Input to DAC Clock Hold Time (t

DAC Clock to Analog Output Data Latency (Single-Port Mode) 8 Cycles

SERIAL PERIPHERAL INTERFACE

SCLK Frequency (f

SCLK Pulse Width High (t

SCLK Pulse Width Low (t

CSB to SCLK Setup Time (tS) 1 ns

CSB to SCLK Hold Time (tH) 0 ns

SDIO to SCLK Setup Time (tDS) 1 ns

SDIO to SCLK Hold Time (tDH) 0 ns

SCLK to SDIO/SDO Data Valid Time (tDV) 1 ns

RESET Pulse Width High 10 ns

WAKE-UP TIME AND OUTPUT LATENCY

From DAC Outputs Disabled 200 μs

From Full Device Power-Down 1200 μs

DAC Clock to Analog Output Latency (Dual-Port Mode) 7 Cycles

DAC Clock to Analog Output Latency (Single-Port Mode) 8 Cycles

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, full-scale digital input, maximum

MAX

) 2.0 2.2 2.8 ns

DCO

Dual-Port Mode) 400 ps

DBS

Dual-Port Mode) 1200 ps

DBH

Single-Port Mode) 400 ps

DBS

Single-Port Mode) 1200 ps

DBH

) 40 MHz

SCLK

) 10 ns

PWH

) 10 ns

PWL

Rev. 0 | Page 7 of 28

AD9741/AD9743/AD9745/AD9746/AD9747

ABSOLUTE MAXIMUM RATINGS

Table 6.

With

Parameter

AVDD33, DVDD33 AVSS DVSS

DVDD18, CVDD18 AVSS DVSS

AVSS DVSS CVSS −0.3 V to +0.3 V

DVSS AVSS CVSS −0.3 V to +0.3 V

CVSS AVSS DVSS −0.3 V to +0.3 V

REFIO AVSS −0.3 V to AVDD33 + 0.3 V

IOUT1P, IOUT1N, IOUT2P,

IOUT2P, AUX1P, AUX1N,

AUX2P, AUX2N

P1D15 to P1D0,

P2D15 to P2D0

CLKP, CLKN CVSS −0.3 V to CVDD18 + 0.3 V

RESET, CSB, SCLK, SDIO, SDO DVSS –0.3 V to DVDD33 + 0.3 V

Junction Temperature 125°C

Storage Temperature −65°C to +150°C

Respect to

CVSS

CVSS

AVSS −1.0 V to AVDD33 + 0.3 V

DVSS −0.3 V to DVDD33 + 0.3 V

Rating

−0.3 V to +3.6 V

−0.3 V to +1.98 V

THERMAL RESISTANCE

Thermal resistance tested using JEDEC standard 4-layer

thermal test board with no airflow.

Table 7.

Package Type θJA Unit

CP-72-1 (Exposed Pad Soldered to PCB) 25 °C/W

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 8 of 28

AD9741/AD9743/AD9745/AD9746/AD9747

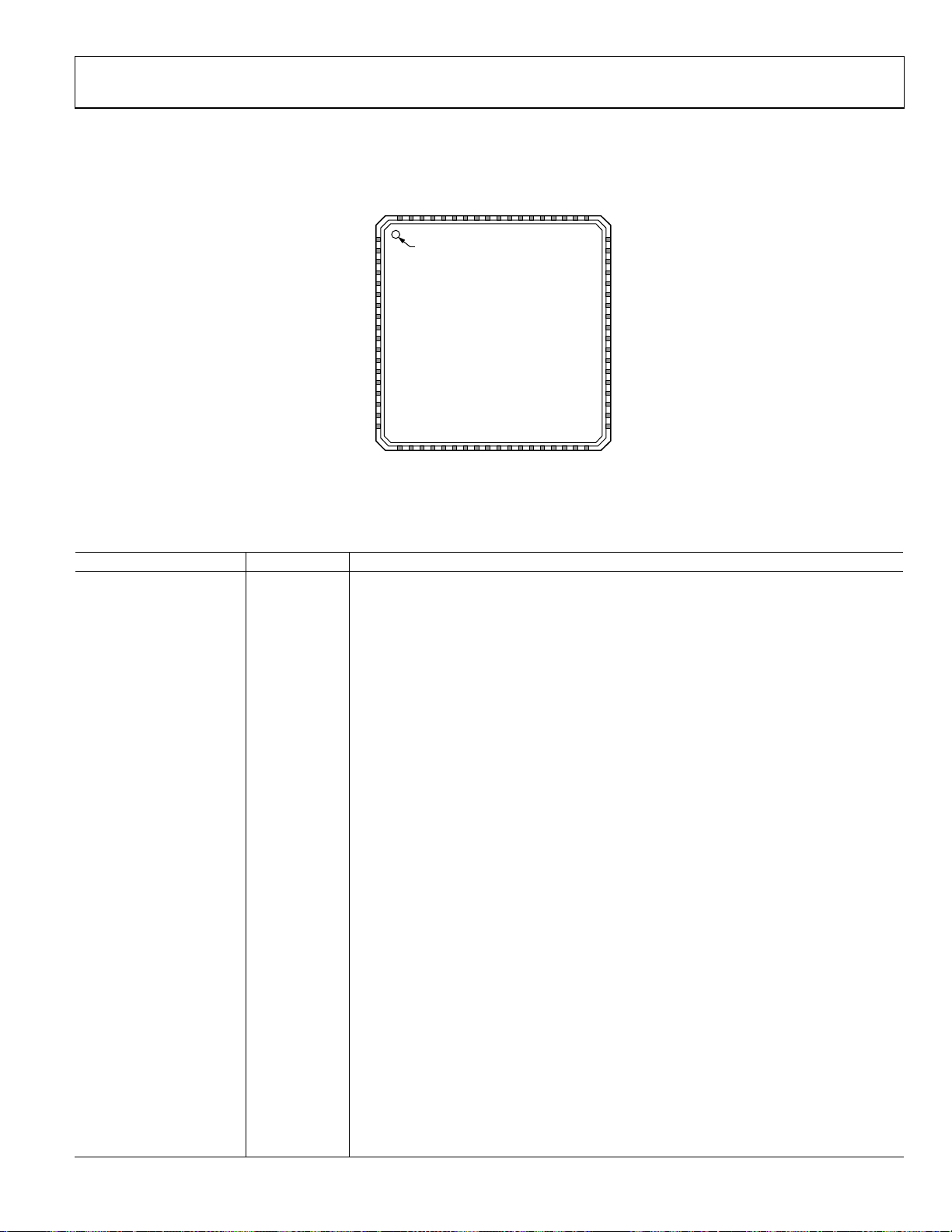

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

AVDD33

AVDD33

AVSS

IOUT1P

IOUT1N

AVSS

AUX1P

AUX1N

AVSS

AUX2N

AUX2P

AVSS

IOUT2N

IOUT2P

AVSS

AVDD33

AVDD33

REFIO

7271706968676665646362616059585756

55

CVDD18

CVDD18

DVDD18

NC = NO CONNECT

CVSS

CLKP

CLKN

CVSS

DVSS

P1D7

P1D6

P1D5

P1D4

P1D3

P1D2

P1D1

P1D0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17NC

18NC

PIN 1

INDICATOR

(TOP VIEW)

192021222324252627282930313233

NCNCNCNCNC

NC

DCO

AD9741

NC

DVSS

DVDD33

FSADJ

54

RESET

53

CSB

52

SCLK

51

SDIO

50

SDO

49

DVSS

48

DVDD18

47

NC

46

NC

45

NC

44

NC

43

NC

42

NC

41

NC

40

NC

39

P2D0

38

P2D1

37

34

35P2D3

36P2D2

NC

P2D7

P2D6

P2D5

IQSEL

P2D4

06569-006

Figure 2. AD9741 Pin Configuration

Table 8. AD 9741 Pin Function Descriptions

Pin No. Mnemonic Description

1, 6 CVDD18 Clock Supply Voltage (1.8 V).

2, 5 CVSS Clock Supply Common (0 V).

3 CLKP Differential DAC Clock Input.

4 CLKN Complementary Differential DAC Clock Input.

7, 28, 48 DVSS Digital Supply Common (0 V).

8, 47 DVDD18 Digital Core Supply Voltage (1.8 V).

9 to 16 P1D<7:0> Port 1 Data Bit Inputs.

17 to 24, 26, 30, 39 to 46 NC No Connect.

25 DCO Data Clock Output. Use to clock data source.

27 DVDD33 Digital I/O Supply Voltage (3.3 V).

29 IQSEL I/Q Framing Signal for Single-Port Mode Operation.

31 to 38 P2D<7:0> Port 2 Data Bit Inputs.

49 SDO Serial Peripheral Interface Data Output.

50 SDIO Serial Peripheral Interface Data Input and Optional Data Output.

51 SCLK Serial Peripheral Interface Clock Input.

52 CSB Serial Peripheral Interface Chip Select Input. Active low.

53 RESET Hardware Reset. Active high.

54 FSADJ Full-Scale Current Output Adjust. Connect a 10 kΩ resistor to AVSS.

55 REFIO Reference Input/Output. Connect a 0.1 μF capacitor to AVSS.

56, 57, 71, 72 AVDD33 Analog Supply Voltage (3.3 V).

58, 61, 64, 67, 70 AVSS Analog Supply Common (0 V).

59 IOUT2P DAC2 Current Output True. Sources full-scale current when input data bits are all 1.

60 IOUT2N DAC2 Current Output Complement. Sources full-scale current when data bits are all 0.

62 AUX2P Auxiliary DAC2 Default Current Output Pin.

63 AUX2N Auxiliary DAC2 Optional Output Pin. Enable through SPI.

65 AUX1N Auxiliary DAC1 Optional Output Pin. Enable through SPI.

66 AUX1P Auxiliary DAC1 Default Current Output Pin.

68 IOUT1N Complementary DAC1 Current Output. Sources full-scale current when data bits are all 0.

69 IOUT1P DAC1 Current Output. Sources full-scale current when data bits are all 1.

EPAD AVSS

Exposed Thermal Pad. Must be soldered to copper pour on top surface of PCB for mechanical

stability and must be electrically tied to low impedance GND plane for low noise performance.

Rev. 0 | Page 9 of 28

Loading...

Loading...