12路LVPECL/24路CMOS输出时钟

特性

低相位噪声锁相环(PLL)

片内VCO调谐范围:2.53 GHz至2.95 GHz

支持最高2.4 GHz的外部3.3 V/5 V VCO/VCXO

1路差分或2路单端参考输入

支持最高250 MHz的CMOS、LVDS或LVPECL参考

参考输入接受16.67 MHz至33.3 MHz晶振

可选参考时钟倍频器

参考监控功能

自动和手动参考切换/保持模式,支持可选的恢复式/非恢

复式切换

参考间无毛刺切换

从保持模式自动恢复

可选数字或模拟锁定检测

可选零延迟工作

12路1.6 GHz LVPECL输出分为4组

每组3路输出,具有一个带相位延迟的1至32分频器

加性输出抖动低至225 fs rms

分组输出的通道间偏斜:<16 ps

可以将每路LVPECL输出配置为2路CMOS输出(fOUT ≤ 250

MHz)

上电时所有输出自动同步

可以根据需要手动同步多路输出

SPI和I²C兼容型串行控制端口

64引脚LFCSP封装

非易失性EEPROM存储配置设置

应用

低抖动、低相位噪声时钟分配

SONET、10Ge、10G FC和其它10 Gbps协议的时钟产生和转换

前向纠错(G.710)

为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

高性能无线收发器

自动测试设备(ATE)和高性能仪器仪表

宽带基础设施

概述

AD9520-01提供多路输出时钟分配功能,具有亚皮秒级抖动

性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。

片内VCO的调谐频率范围为2.53 GHz至2.95 GHz。也可以使

用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

发生器,集成2.8 GHz VCO

AD9520-0

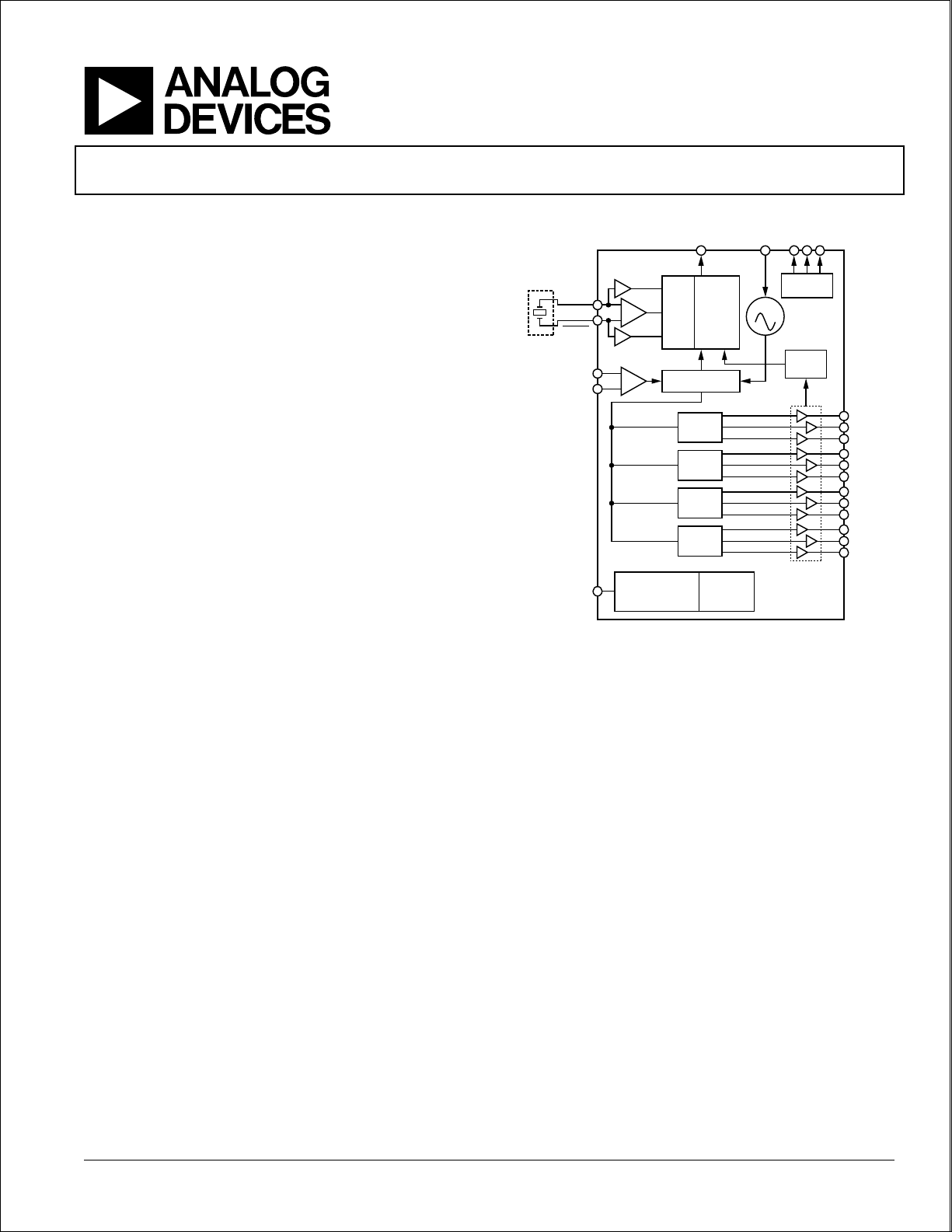

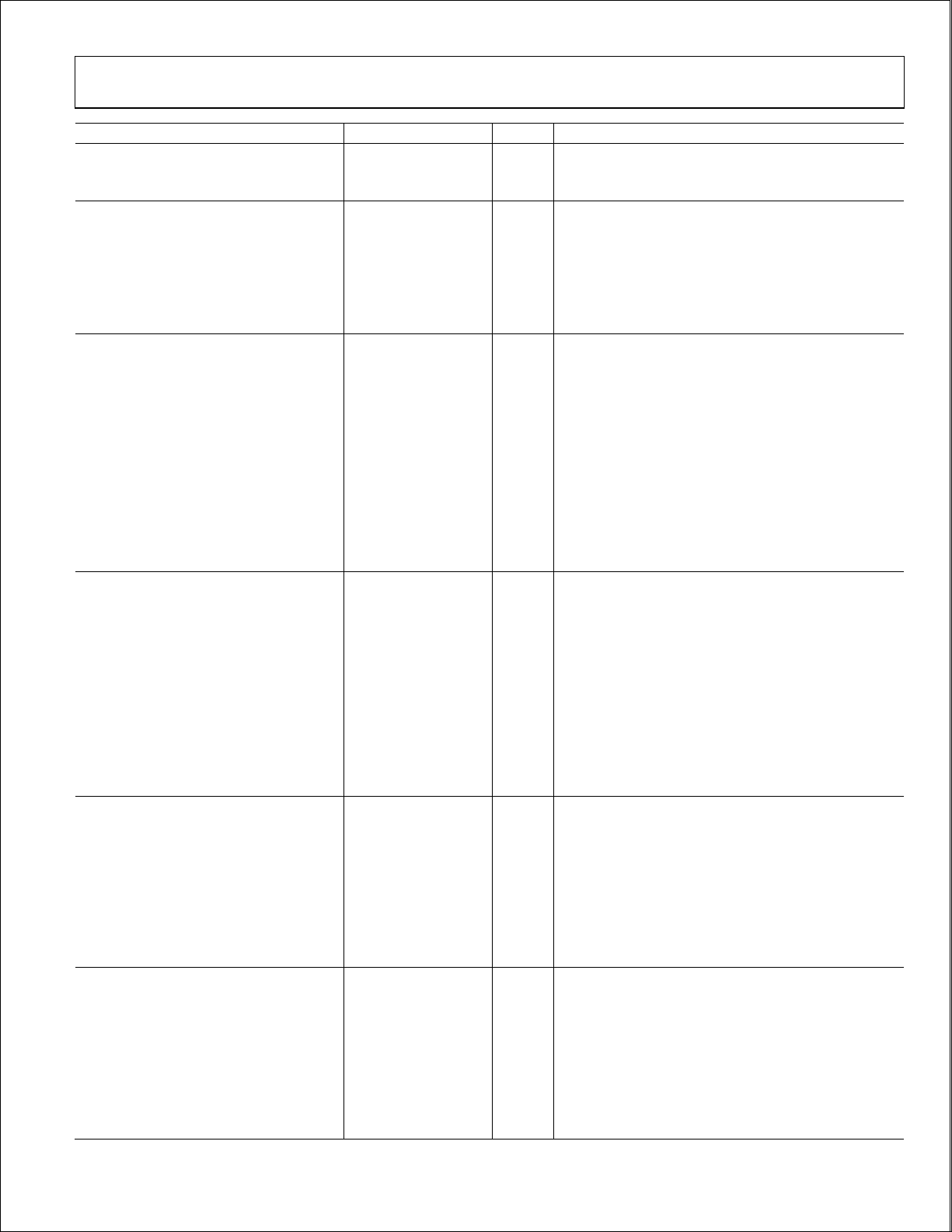

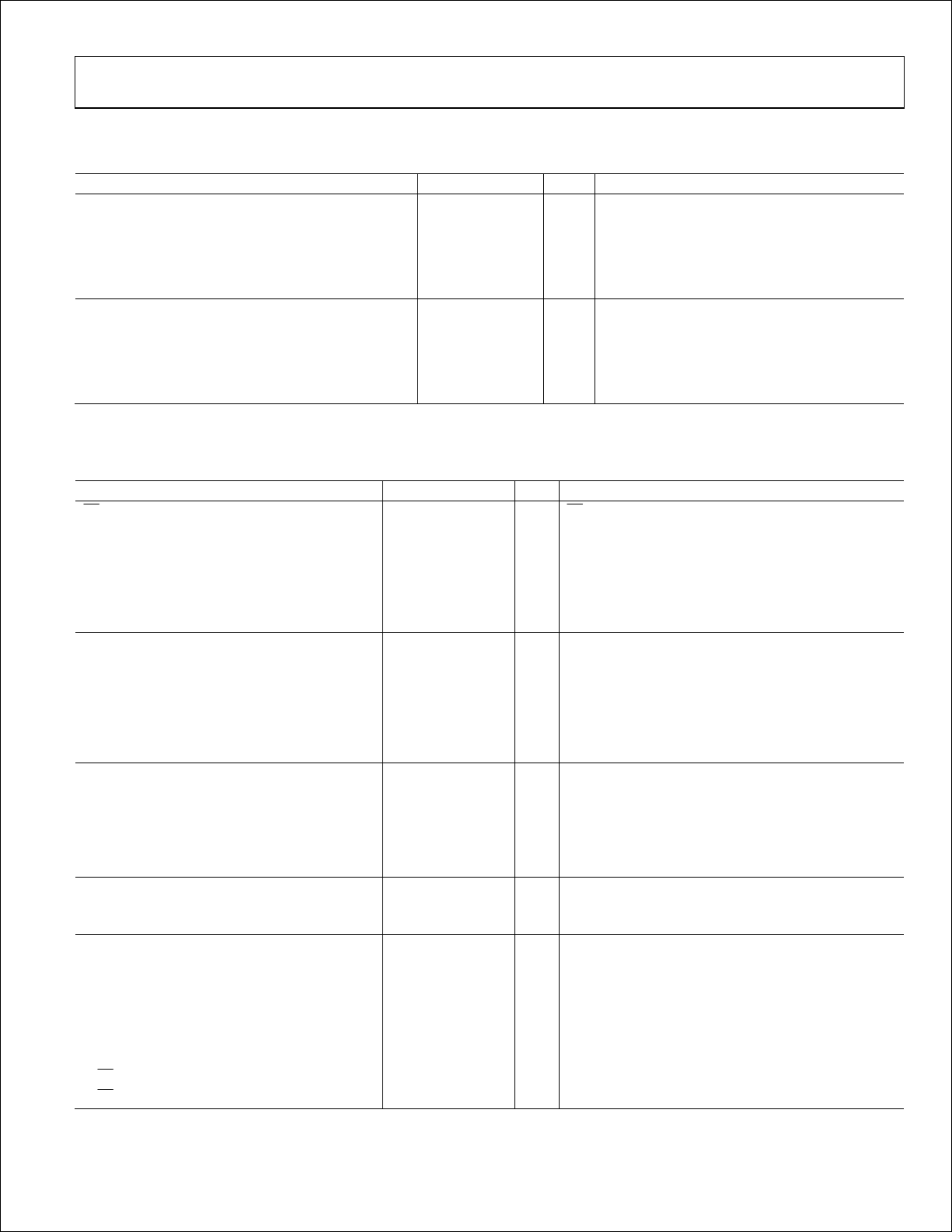

功能框图

CP

OPTIONAL

REFIN

REFIN

CLK

REF1

REF2

SWITCHOVER

DIVIDER

AND MUXES

SPI/I2C CONTROL

PORT AND

DIGITAL LOGIC

AND MONITOR

DIV/

DIV/

DIV/

DIV/

Φ

Φ

Φ

Φ

EEPROM

图1

AD9520串行接口支持SPI和I2C®端口。封装内EEPROM可

以通过串行接口进行编程,存储用于上电和芯片复位的用

户定义寄存器设置。

AD9520具有12路LVPECL输出,分为四组。任何一路1.6

GHz LVPECL输出都可以重新配置为两路250 MHz CMOS输

出。

每组输出具有一个分频器,其分频比(从1至32)和相位(粗

调延迟)均可以设置。

AD9520提供64引脚LFCSP封装,可以采用3.3 V单电源供电。

外部VCO的工作电压最高可达5.5 V。独立的输出驱动器电

源可以为2.375 V至3.465 V。

AD9520的额定工作温度范围为−40°C至+85°C标准工业温

度范围。

LF

STATUS

MONITOR

VCO

PLL

ZERO

DELAY

LVPECL/

CMOS

AD9520

OUT0

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

OUT8

OUT9

OUT10

OUT11

07213-001

1

AD9520在本数据手册中泛指AD9520系列的所有器件。但是,使用AD9520-0时,它仅指AD9520系列的该特定器件。

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademark

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供

的最新英文版数据手册。

s are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

AD9520-0

目录

特性....................................................................................................1

应用....................................................................................................1

概述....................................................................................................1

功能框图...........................................................................................1

修订历史...........................................................................................3

技术规格...........................................................................................4

电源要求......................................................................................4

PLL特性 .......................................................................................4

时钟输入......................................................................................7

时钟输出......................................................................................7

时序特性......................................................................................8

时序图.....................................................................................9

时钟输出加性相位噪声(仅分配;

未使用VCO分频器) ...............................................................10

时钟输出绝对相位噪声(使用内部VCO)........................... 11

时钟输出绝对时间抖动(使用内部VCO

的时钟产生).............................................................................11

时钟输出绝对时间抖动(使用内部

VCO的时钟净化).................................................................... 11

时钟输出绝对时间抖动(使用外部

VCXO的时钟产生)................................................................. 12

时钟输出加性时间抖动(未使用

VCO分频器) ............................................................................12

时钟输出加性时间抖动(使用VCO分频器) ......................13

串行控制端口—SPI模式 ....................................................... 13

2

串行控制端口—I

PD, SYNC和RESET引脚........................................................ 15

串行端口设置引脚:SP1、SP0 ........................................... 15

LD、STATUS和REFMON引脚 ...........................................15

功耗 ........................................................................................... 16

绝对最大额定值........................................................................... 17

热阻 ........................................................................................... 17

ESD警告.................................................................................... 17

引脚配置和功能描述 .................................................................. 18

典型工作特性 ...............................................................................21

术语................................................................................................. 26

详细框图........................................................................................ 27

工作原理........................................................................................ 28

C模式 ....................................................... 14

工作配置.........................................................................................28

模式0:内部VCO和时钟分配..............................................28

模式1:时钟分配或外部VCO <1600 MHz ........................30

模式2:高频时钟分配—CLK或外部

VCO > 1600 MHz .....................................................................32

锁相环(PLL) .............................................................................34

PLL配置 .....................................................................................34

鉴频鉴相器(PFD) ...................................................................34

电荷泵(CP) ...............................................................................35

片内VCO ...................................................................................35

PLL外部环路滤波器 ...............................................................35

PLL参考输入.............................................................................35

参考切换....................................................................................36

参考分频器R.............................................................................36

VCO/VCXO反馈分频器N:P、A、B、R.........................36

数字锁定检测(DLD) ..............................................................38

模拟锁定检测(ALD) ..............................................................38

电流源数字锁定检测(CSDLD) ............................................38

外部VCXO/VCO时钟输入(CLK/CLK) ..............................39

保持 ............................................................................................39

外部/手动保持模式.................................................................39

自动/内部保持模式.................................................................39

频率状态监控器.......................................................................41

VCO校准 ...................................................................................42

零延迟操作.....................................................................................43

内部零延迟模式.......................................................................43

外部零延迟模式.......................................................................43

时钟分配.........................................................................................44

工作模式....................................................................................44

CLK或VCO直接至LVPECL输出..........................................44

时钟分频....................................................................................45

VCO分频器...............................................................................45

通道分频器 ...............................................................................45

同步输出—SYNC功能............................................................47

LVPECL输出驱动器................................................................49

CMOS输出驱动器 ...................................................................49

Rev 0 | Page 2 of 84

AD9520-0

复位模式....................................................................................... 49

上电复位.................................................................................. 49

通过RESET引脚进行硬件复位........................................... 49

通过串行端口进行软复位................................................... 50

通过串行端口软复位到EEPROM中

的设置(EEPROM引脚= 0时)............................................... 50

关断模式....................................................................................... 50

通过PD关断芯片 ...................................................................50

PLL关断 ................................................................................... 50

分配关断.................................................................................. 50

各时钟输出独立关断............................................................ 50

各时钟通道独立关断............................................................ 50

串行控制端口 ..............................................................................51

2

C端口选择 .......................................................................51

SPI/I

2

C串行端口操作...................................................................... 51

I

2

C总线特性 ............................................................................ 51

I

数据传输过程......................................................................... 52

数据传输格式......................................................................... 53

2

C串行端口时序 ................................................................... 53

I

SPI串行端口操作...................................................................... 54

引脚描述.................................................................................. 54

SPI工作模式............................................................................ 54

通信周期—指令加数据........................................................ 54

写操作 ...................................................................................... 54

读操作 ...................................................................................... 54

修订历史

2008年9月—修订版0:初始版

SPI指令字(16位) .................................................................. 55

SPI MSB/LSB优先传输........................................................ 55

EEPROM操作 ............................................................................ 58

写入EEPROM ....................................................................... 58

读取EEPROM ....................................................................... 58

EEPROM缓冲段编程.......................................................... 59

寄存器段定义组................................................................... 59

IO_UPDATE(操作代码0x80) ............................................ 59

End-of-Data(操作代码0xFF).............................................. 59

Pseudo-End-of-Data(操作代码0xFE) ............................... 59

热性能 ......................................................................................... 61

寄存器映射................................................................................. 62

寄存器映射描述........................................................................ 67

应用信息..................................................................................... 82

使用AD9520进行频率规划 ............................................... 82

在ADC时钟应用中使用AD9520输出.............................. 82

LVPECL时钟分配 ................................................................ 82

CMOS时钟分配.................................................................... 83

外形尺寸..................................................................................... 84

订购指南................................................................................ 84

Rev. 0 | Page 3 of 84

AD9520-0

技术规格

除非另有说明,典型值的测量条件为:VS = VS_DRV = 3.3 V ± 5%;VS ≤ VCP ≤ 5.25 V;TA = 25°C;RSET = 4.12 kΩ;

CPRSET = 5.1 kΩ。最小值和最大值的测量条件为整个VS和TA(−40°C至+85°C)范围内。

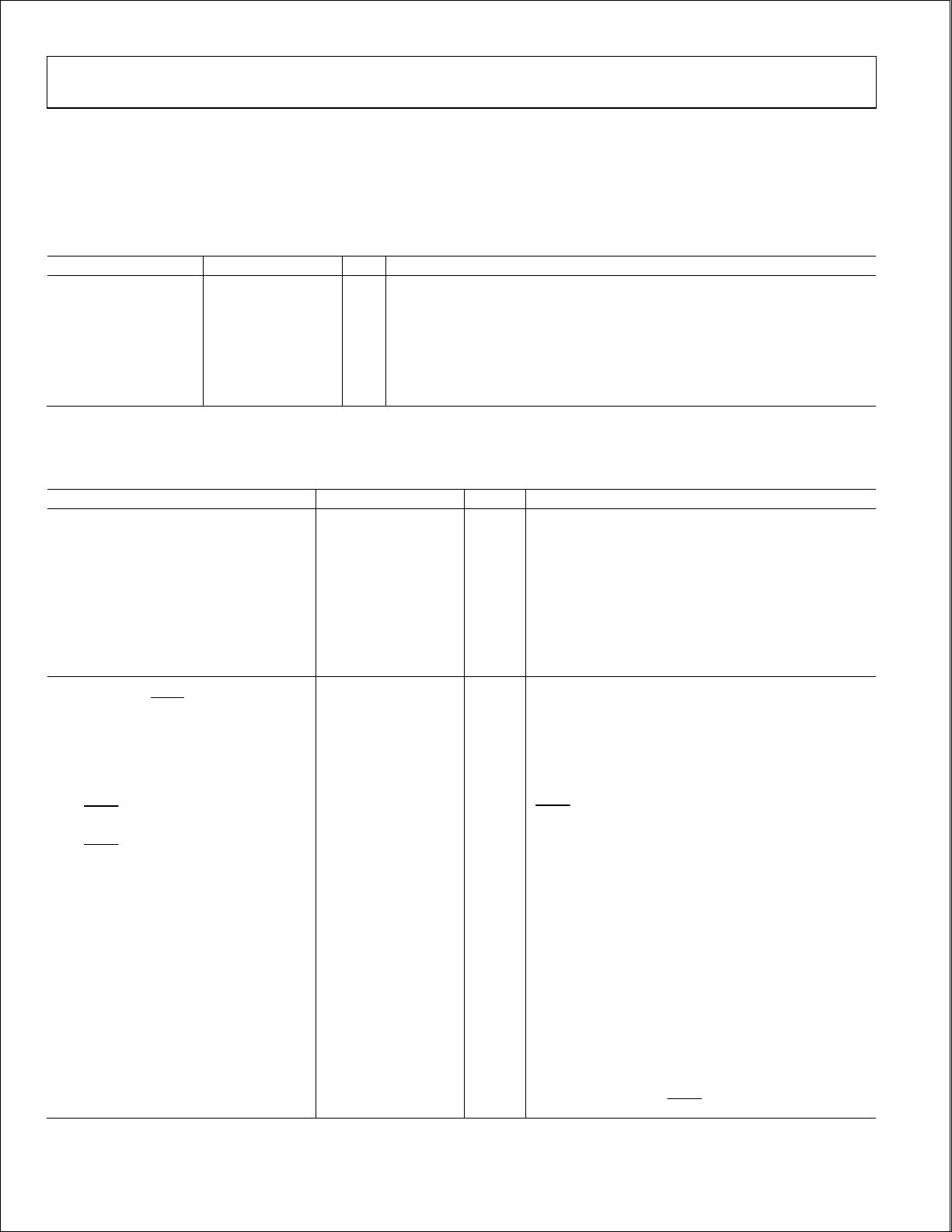

电源要求

表1

最小值 典型值 最大值 单位单位测试条件/注释

VS 3.135 3.3 3.465 V 3.3 V ± 5%

VS_DRV 2.375 VS V 标称值为2.5 V至3.3 V ± 5%

VCP VS 5.25 V 标称值为3.3 V至5.0 V ± 5%

RSET引脚电阻 4.12 kΩ 设置内部偏置电流;接地

CPRSET引脚电阻 5.1 kΩ

BYPASS引脚电容 220 nF 内部LDO调节器的旁路电容;LDO稳定工作所必需的;接地

PLL特性

表2

最小值 典型值 最大值参数

VCO(片内)

频率范围

VCO增益(K

调谐电压(V

VCO

)

)

T

推频(开环)

1 kHz偏移时的相位噪声

100 kHz偏移时的相位噪声

1 MHz偏移时的相位噪声

参考输入

差模(REFIN、REFIN)

输入频率 0 250 MHz

输入灵敏度 280 mV p-p

REFIN自偏置电压 1.34 1.60 1.75 V REFIN的自偏置电压

REFIN自偏置电压

REFIN输入电阻 4.0 4.8 5.9 kΩ 自偏置

REFIN输入电阻

双路单端模式(REF1、REF2) 两路单端CMOS兼容型输入

输入频率(交流耦合,直流偏移关闭)

2530 2950 MHz 见图13

52 MHz/V 见图8

1 MHz/V

−51 dBc/Hz f = 2550 MHz

−108 dBc/Hz f = 2550 MHz

−127 dBc/Hz f = 2550 MHz

1.30 1.50 1.60 V

10 250 MHz 压摆率必须大于50 V/μs

设置内部电荷泵电流范围,标称值4.8 mA (CP_lsb = 600 μA);实际

电流计算如下:CP_lsb = 3.06/CPRSET;接地

测试条件/注释

VCP −

V 使用内部VCO时,VCP ≤ VS

0.5

差分模式(让未驱动的输入交流接地,可以

支持单端输入)

低于约1 MHz的频率应直流耦合;注意匹配

V

(自偏置电压)

CM

1

1

REFIN的自偏置电压

1

1

4.4 5.3 6.4 kΩ 自偏置

输入频率(交流耦合,直流偏移开启)

250 MHz

压摆率必须大于50 V/μs,并且必须满足输

入幅度灵敏度要求;见输入灵敏度

输入频率(直流耦合) 0 250 MHz 压摆率大于50 V/μs;CMOS电平

输入灵敏度(交流耦合,直流偏移关闭)

输入灵敏度(交流耦合,直流偏移开启)

0.55 3.28 V p-p V

1.5 2.78 V p-p V

不应超过V

IH

不应超过V

IH

S

S

输入逻辑高电平,直流偏移关闭 2.0 V

输入逻辑低电平,直流偏移关闭 0.8 V

输入电流 −100 +100 µA

输入电容 2 pF

Rev. 0 | Page 4 of 84

各引脚,REFIN (REF1)/REFIN (REF2)

AD9520-0

参数

晶体振荡器

晶振频率范围 16.67 33.33 MHz

最大晶体动态电阻 30 Ω

鉴频鉴相器(PFD)

PFD输入频率 100 MHz 防反冲脉冲宽度 = 1.3 ns、2.9 ns

45 MHz 防反冲脉冲宽度 = 6.0 ns

参考输入时钟倍频器频率 0.004 50 MHz 防反冲脉冲宽度 = 1.3 ns、2.9 ns

防反冲脉冲宽度 1.3 ns 0x017[1:0] = 01b

2.9 ns 0x017[1:0] = 00b; 0x017[1:0] = 11b

6.0 ns 0x017[1:0] = 10b

电荷泵(CP)

ICP吸/源电流 可编程

高值 4.8 mA

最小值 典型值 最大值 单位 测试条件/注释

CPRSET = 5.1 kΩ时;更改CPRSET可以获得更高的I

CP

低值 0.60 mA

CPRSET = 5.1 kΩ时;更改CPRSET可以获得更低的I

绝对精度 2.5 % 电荷泵电压设置为VCP/2

CPRSET范围 2.7 10 kΩ

ICP高阻抗模式漏电流 1 nA

吸电流与源电流匹配 1 %

0.5 V < VCP< VCP − 0.5 V;VCP为CP(电荷泵)引脚

上的电压;VCP为VCP电源引脚上的电压

I

CP与VCP

ICP与温度 2 %

1.5 %

0.5 V < V

V

= VCP/2 V

CP

< VCP − 0.5 V

CP

预分频器(N分频器的一部分)

预分频器输入频率

P = 1 FD 300 MHz

P = 2 FD 600 MHz

P = 3 FD 900 MHz

P = 2 DM (2/3) 600 MHz

P = 4 DM (4/5) 1000 MHz

P = 8 DM (8/9) 2400 MHz

P = 16 DM (16/17) 3000 MHz

P = 32 DM (32/33) 3000 MHz

预分频器输出频率 300 MHz

PLL N分频器延迟

A、B计数器输入频率(预分频器输入频率除以P)

寄存器0x019[2:0];见表53

000 O

001 410 ps

010 530 ps

011 650 ps

100 770 ps

101 890 ps

110 1010 ps

111 1130 ps

PLL R分频器延迟

寄存器0x019[5:3];见表53

000 O

001 370 ps

010 490 ps

011 610 ps

100 730 ps

101 850 ps

110 970 ps

111 1090 ps

CP

Rev. 0 | Page 5 of 84

AD9520-0

参数

零延迟模式下的相位偏移

内部零延迟模式下的相位偏移

(REF至LVPECL时钟输出引脚)

内部零延迟模式下的相位偏移

(REF至LVPECL时钟输出引脚)

外部零延迟模式下的相位偏移

(REF至CLK输入引脚)

外部零延迟模式下的相位偏移

(REF至CLK输入引脚)

噪声特性

电荷泵/鉴频鉴相器的带内相位噪声

(带内指在PLL的LBW内)

@ 500 kHz PFD频率 −165 dBc/Hz

@ 1 MHz PFD频率 −162 dBc/Hz

@ 10 MHz PFD频率 −152 dBc/Hz

@ 50 MHz PFD频率 −144 dBc/Hz

PLL品质因数(FOM) −222 dBc/Hz

PLL数字锁定检测窗口

2

锁定阈值(边沿重合)

低范围(ABP 1.3 ns、2.9 ns) 3.5 ns 0x017[1:0] = 00b, 01b,11b; 0x018[4] = 1b

高范围(ABP 1.3 ns、2.9 ns) 7.5 ns 0x017[1:0] = 00b, 01b, 11b; 0x018[4] = 0b

高范围(ABP 6.0 ns) 3.5 ns 0x017[1:0] = 10b; 0x018[4] = 0b

解锁阈值(迟滞)

2

低范围(ABP 1.3 ns、2.9 ns) 7 ns 0x017[1:0] = 00b, 01b, 11b; 0x018[4] = 1b

高范围(ABP 1.3 ns、2.9 ns) 15 ns 0x017[1:0] = 00b, 01b, 11b; 0x018[4] = 0b

高范围(ABP 6.0 ns) 11 ns 0x017[1:0] = 10b; 0x018[4] = 0b

1

REFIN和REFIN自偏置点略微偏移,以免在开路输入条件下发生震颤。

2

为使数字锁定检测可靠地工作,PFD频率的周期必须大于锁定后解锁的时间。

最小值 典型值 最大值 单位 测试条件/注释

REF指REFIN (REF1)/REFIN (REF2)

560 1060 1310 ps 旁路N延迟和R延迟时

−320 +50 +240 ps N延迟设置为110且旁路R延迟时

140 630 870 ps 旁路N延迟和R延迟时

−460 −20 +200 ps N延迟设置为011且旁路R延迟时

PLL带内相位噪底的估算方法如下:

测量VCO输出端的带内相位噪声,

然后减去20 log(N)(其中N为N分频器的值)

参考压摆率大于0.5 V/ns;FOM + 10 log(fPFD)为PLL

环路带宽内PFD/CP带内相位噪声(平坦区域中)的

近似值;闭环工作时,VCO输出端测得的相位噪声

提高20 log(N);PLL品质因数随着压摆率降低而降低;

见图12

通过适当的寄存器设置选择时,信号可在LD、STATUS

和REFMON引脚上提供;锁定检测窗口设置可通过更

改CPRSET电阻而改变

由0x017[1:0]和0x018[4]选择

(这是从解锁到锁定的阈值)

由0x017[1:0]和0x018[4]选择

(这是从锁定到解锁的阈值)

Rev. 0 | Page 6 of 84

时钟输入

表3

参数

时钟输入(CLK、CLK)

输入频率 0

0

最小值 典型值 最大值

测试条件/注释

差分输入

1

2.4 GHz 高频分配(VCO分频器)

1

1.6 GHz

仅分配(旁路VCO分频器);这是通道分频器支持的频率范围

AD9520-0

差分输入灵敏度 150 mV p-p

差分输入电平 2 V p-p

输入共模电压V

输入共模范围V

CM

CMR

1.3 1.57 1.8 V 自偏置;支持交流耦合

1.3 1.8 V

单端输入灵敏度 150 mV p-p

在2.4 GHz下测得;压摆率大于1 V/ns时可改善抖动性能

较大的电压摆幅可启动保护二极管,降低抖动性能

施加200 mV p-p信号;直流耦合

CLK交流耦合;CLK交流旁路至RF地

输入电阻 3.9 4.7 5.7 kΩ 自偏置

输入电容 2 pF

1

低于约1 MHz时,输入应直流耦合。应注意匹配VCM。

时钟输出

表4

参数

最小值 典型值 最大值单位单位

LVPECL时钟输出 终端 = 50 Ω接VS_DRV − 2 V

OUT0, OUT1, OUT2, OUT3, OUT4,

OUT5, OUT6, OUT7, OUT8,

OUT9, OUT10, OUT11

最大输出频率 2400 MHz

测试条件/注释

差分(OUT、OUT)

使用直接至输出;见图21(可以提供更高

的频率,但幅度无法满足V

输出频率受限于VCO最大频率或CLK输入

频率,取决于AD9520的配置

要求);最大

OD

输出高电压V

输出低电压V

OH

OL

输出差分电压V

VS_DRV −

1.07

VS_DRV −

1.95

OD

660 820 950 mV

VS_DRV −

0.96

VS_DRV −

1.79

VS_DRV −

0.84

VS_DRV −

1.64

V

V

CMOS时钟输出

OUT0A, OUT0B, OUT1A, OUT1B,

单端;终端 = 10 pF

OUT2A, OUT2B, OUT3A, OUT3B,

OUT4A, OUT4B, OUT5A, OUT5B,

OUT6A, OUT6B, OUT7A, OUT7B,

OUT8A, OUT8B, OUT9A, OUT9B,

OUT10A, OUT10B, OUT11A,

OUT11B

输出频率 250 MHz 见图22

输出高电压V

输出低电压V

输出高电压V

输出低电压V

输出高电压V

输出低电压V

OH

OL

OH

OL

OH

OL

VS − 0.1 V @ 1 mA load, VS_DRV = 3.3 V/2.5 V

0.1 V @ 1 mA load, VS_DRV = 3.3 V/2.5 V

2.7 V @ 10 mA load, VS_DRV = 3.3 V

0.5 V @ 10 mA load, VS_DRV = 3.3 V

1.8 V @ 10 mA load, VS_DRV = 2.5 V

0.6 V @ 10 mA load, VS_DRV = 2.5 V

Rev. 0 | Page 7 of 84

AD9520-0

时序特性

表5

参数 最小值 典型值 最大值 单位 测试条件/注释

LVPECL输出上升/下降时间 终端 = 50 Ω接VS_DRV − 2 V

输出上升时间tRP 130 170 ps

20%至80%,差分测量(上升/下降时间独立于

VS,在VS_DRV = 3.3 V和2.5 V下有效)

输出下降时间tFP 130 170 ps

80%至20%,差分测量(上升/下降时间独立于

VS,在VS_DRV = 3.3 V和2.5 V下有效)

传播延迟t

针对所有分频值

,CLK至LVPECL输出

PECL

850 1050 1280 ps 高频时钟分配配置

800 970 1180 ps 时钟分配配置

随温度的变化

输出偏斜,LVPECL输出

1

1.0 ps/°C

终端 = 50 Ω接VS_DRV − 2 V

共享同一分频器的LVPECL输出 5 16 ps VS_DRV = 3.3 V

5 20 ps VS_DRV = 2.5 V

不同分频器上的LVPECL输出 5 45 ps VS_DRV = 3.3 V

5 60 ps VS_DRV = 2.5 V

跨多个器件的所有LVPECL输出 190 ps VS_DRV = 3.3 V和2.5 V

CMOS输出上升/下降时间 终端 = 开路

输出上升时间t

输出下降时间t

输出上升时间t

输出下降时间t

传播延迟t

CMOS

针对所有分频值

RC

FC

RC

FC

,CLK至CMOS输出

750 960 ps 20% 至 80%; C

715 890 ps 80% 至 20%; C

965 1280 ps 20% 至 80%; C

890 1100 ps 80% 至 20%; C

时钟分配配置

2.1 2.75 3.55 ns VS_DRV = 3.3 V

= 10 pF; VS_DRV = 3.3 V

LOAD

= 10 pF; VS_DRV = 3.3 V

LOAD

= 10 pF; VS_DRV = 2.5 V

LOAD

= 10 pF; VS_DRV = 2.5 V

LOAD

3.35 ns VS_DRV = 2.5 V

随温度的变化

输出偏斜,CMOS输出

1

共享同一分频器的CMOS输出

2 ps/°C VS_DRV = 3.3 V和2.5 V

7 85 ps VS_DRV = 3.3 V

10 105 ps VS_DRV = 2.5 V

不同分频器上的所有CMOS输出 10 240 ps VS_DRV = 3.3 V

10 285 ps VS_DRV = 2.5 V

跨多个器件的所有CMOS输出 600 ps VS_DRV = 3.3 V

620 ps VS_DRV = 2.5 V

输出偏斜,LVPECL至CMOS输出

1

所有设置相同;逻辑类型不同

共享同一分频器的输出 1.18 1.76 2.48 ns 同一器件上的LVPECL至CMOS

不同分频器上的输出 1.20 1.78 2.50 ns 同一器件上的LVPECL至CMOS

1

输出偏斜是指在相同的电压、温度条件下,任何两条相似的延迟路径之间的差异。

Rev. 0 | Page 8 of 84

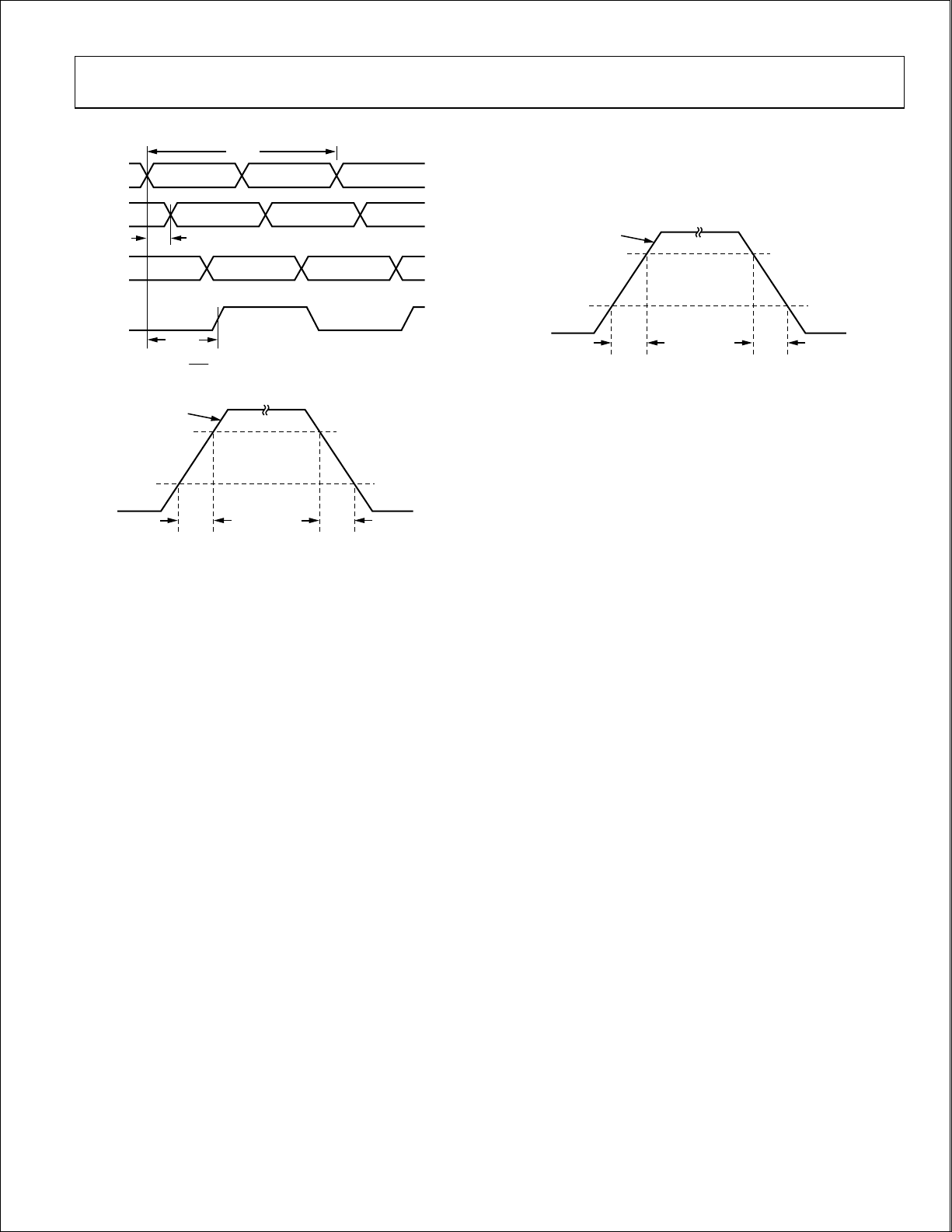

时序图

CLK

AD9520-0

t

CLK

SINGLE-ENDED

80%

20%

t

CMOS

10pF LOAD

RC

t

FC

07213-063

t

CMOS

t

PECL

07213-060

图2. CLK/CLK至时钟输出时序,分频比 = 1

图4. CMOS时序,单端,10 pF负载

DIFFERENTIAL

80%

20%

LVPECL

t

RP

t

FP

07213-061

图3. LVPECL时序,差分

Rev. 0 | Page 9 of 84

AD9520-0

时钟输出加性相位噪声(仅分配;未使用VCO分频器)

表6 .

参数

CLK至LVPECL加性相位噪声

CLK = 1 GHz,输出 = 1 GHz

分频比 = 1

@ 10 Hz偏移

@ 100 Hz偏移

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

@ 10 MHz偏移

@ 100 MHz偏移

CLK = 1 GHz,输出 = 200 MHz

分频比 = 5

@ 10 Hz偏移

@ 100 Hz偏移

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

>10 MHz偏移

CLK至CMOS加性相位噪声

CLK = 1 GHz,输出 = 250 MHz

分频比 = 4

@ 10 Hz偏移

@ 100 Hz偏移

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

>10 MHz偏移

CLK = 1 GHz,输出 = 50 MHz

分频比 = 20

@ 10 Hz偏移

@ 100 Hz偏移

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

>10 MHz偏移

最小值 典型值

−107 dBc/Hz

−117 dBc/Hz

−127 dBc/Hz

−135 dBc/Hz

−142 dBc/Hz

−145 dBc/Hz

−147 dBc/Hz

−150 dBc/Hz

−122 dBc/Hz

−132 dBc/Hz

−143 dBc/Hz

−150 dBc/Hz

−156 dBc/Hz

−157 dBc/Hz

−157 dBc/Hz

−107 dBc/Hz

−119 dBc/Hz

−125 dBc/Hz

−134 dBc/Hz

−144 dBc/Hz

−148 dBc/Hz

−154 dBc/Hz

−126 dBc/Hz

−133 dBc/Hz

−140 dBc/Hz

−148 dBc/Hz

−157 dBc/Hz

−160 dBc/Hz

−163 dBc/Hz

最大值 单位 测试条件/注释

仅分配部分;不包括PLL和VCO

输入压摆率 > 1 V/ns

输入压摆率 > 1 V/ns

仅分配部分;不包括PLL和VCO

输入压摆率 > 1 V/ns

输入压摆率 > 1 V/ns

Rev. 0 | Page 10 of 84

时钟输出绝对相位噪声(使用内部VCO)

表7

参数 最小值 典型值 最大值 单位 测试条件/注释

LVPECL绝对相位噪声

VCO = 2.95 GHz;输出 = 2.95 GHz

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

@ 10 MHz偏移

@ 40 MHz偏移

VCO = 2.75 GHz;输出 = 2.75 GHz

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

@ 10 MHz偏移

@ 40 MHz偏移

VCO = 2.55 GHz;输出 = 2.55 GHz

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

@ 1 MHz偏移

@ 10 MHz偏移

@ 40 MHz偏移

−46 dBc/Hz

−78 dBc/Hz

−104 dBc/Hz

−123 dBc/Hz

−139 dBc/Hz

−145 dBc/Hz

−49 dBc/Hz

−80 dBc/Hz

−106 dBc/Hz

−125 dBc/Hz

−140 dBc/Hz

−146 dBc/Hz

−51 dBc/Hz

−82 dBc/Hz

−108 dBc/Hz

−127 dBc/Hz

−140 dBc/Hz

−146 dBc/Hz

内部VCO;直接至LVPECL输出,

环路带宽小于1 kHz

AD9520-0

时钟输出绝对时间抖动(使用内部VCO的时钟产生)

表8

参数

LVPECL输出绝对时间抖动

VCO = 2.949 GHz; LVPECL = 245.76 MHz; PLL LBW = 63 kHz 176 fs rms

351 fs rms

VCO = 2.703 GHz; LVPECL = 122.88 MHz; PLL LBW = 63 kHz 158 fs rms

324 fs rms

VCO = 2.703 GHz; LVPECL = 61.44 MHz; PLL LBW = 63 kHz 177 fs rms

330 fs rms

最小值 典型值 最大值

时钟输出绝对时间抖动(使用内部VCO的时钟净化)

表9

参数

LVPECL输出绝对时间抖动

VCO = 2.799 GHz; LVPECL = 155.52 MHz; PLL LBW = 1.8 kHz 652 fs rms

VCO = 2.703 GHz; LVPECL = 122.88 MHz; PLL LBW = 2.1 kHz 607 fs rms

最小值 典型值 最大值

单位 测试条件/注释

应用示例基于典型设置,参考源干净,

因此使用较宽的PLL环路带宽;

参考 = 15.36 MHz;R DIV = 1

积分带宽 = 200 kHz至10 MHz

积分带宽 = 12 kHz至20 MHz

积分带宽 = 200 kHz至10 MHz

积分带宽 = 12 kHz至20 MHz

积分带宽 = 200 kHz至10 MHz

积分带宽 = 12 kHz至20 MHz

单位 测试条件/注释

应用示例基于典型设置,参考源抖动,

因此使用较窄的PLL环路带宽;

参考 = 19.44 MHz;R DIV = 162

积分带宽 = 12 kHz至20 MHz

积分带宽 = 12 kHz至20 MHz

Rev. 0 | Page 11 of 84

AD9520-0

时钟输出绝对时间抖动(使用外部VCXO的时钟产生)

表 10.

参数

LVPECL输出绝对时间抖动

LVPECL = 245.76 MHz; PLL LBW = 125 Hz 54 fs rms

77 fs rms

109 fs rms

LVPECL = 122.88 MHz; PLL LBW = 125 Hz 79 fs rms

114 fs rms

163 fs rms

LVPECL = 61.44 MHz; PLL LBW = 125 Hz 124 fs rms

176 fs rms

259 fs rms

时钟输出加性时间抖动(未使用VCO分频器)

表11 .

参数 最小值 典型值 最大值 单位 测试条件/注释

LVPECL输出加性时间抖动

CLK = 622.08 MHz

任意LVPECL输出 = 622.08 MHz

分频比 = 1

CLK = 622.08 MHz

任意LVPECL输出 = 155.52 MHz

分频比 = 4

CLK = 1000 MHz

任意LVPECL输出 = 100 MHz

分频比 = 10

CLK = 500 MHz

任意LVPECL输出 = 100 MHz

分频比 = 5

CMOS输出加性时间抖动

CLK = 200 MHz

任意CMOS输出对 = 100 MHz

分频比 = 2

最小值 典型值 最大值

46 fs rms

64 fs rms

223 fs rms

209 fs rms

325 fs rms

单位 测试条件/注释

应用示例基于使用外部245.76 MHz VCXO

(Toyocom TCO-2112)的典型设置;

参考 = 15.36 MHz;R DIV = 1

积分带宽 = 200 kHz至5 MHz

积分带宽 = 200 kHz至10 MHz

积分带宽 = 12 kHz至20 MHz

积分带宽 = 200 kHz至5 MHz

积分带宽 = 200 kHz至10 MHz

积分带宽 = 12 kHz至20 MHz

积分带宽 = 200 kHz至5 MHz

积分带宽 = 200 kHz至10 MHz

积分带宽 = 12 kHz至20 MHz

仅分配部分;不包括PLL和VCO;

在时钟信号的上升沿测量

积分带宽 = 12 kHz至20 MHz

积分带宽 = 12 kHz至20 MHz

根据ADC的信噪比方法计算

宽带抖动

根据ADC的信噪比方法计算

宽带抖动

仅分配部分;不包括PLL和VCO

根据ADC的信噪比方法计算

宽带抖动

Rev. 0 | Page 12 of 84

时钟输出加性时间抖动(使用VCO分频器)

表12

参数

最小值 典型值 最大值

LVPECL输出加性时间抖动

CLK = 1.0 GHz;VCO DIV = 5;LVPECL = 100 MHz;

230 fs rms

通道分频比 = 2;占空比校正 = 关

CLK = 500 MHz;VCO DIV = 5;LVPECL = 100 MHz;

215 fs rms

旁路通道分频器;占空比校正 = 开

CMOS输出加性时间抖动

CLK = 200 MHz;VCO DIV = 2;CMOS = 100 MHz;

326 fs rms

旁路通道分频器;占空比校正 = 关

CLK = 1600 MHz;VCO DIV = 2;CMOS = 100 MHz;

362 fs rms

通道分频比 = 8;占空比校正 = 关

串行控制端口—SPI模式

表13

参数

CS (输入)

最小值 典型值 最大值

输入逻辑1电压 2.0 V

输入逻辑0电压 0.8 V

输入逻辑1电流 3 µA

输入逻辑0电流 −110 µA

单位 测试条件/注释

AD9520-0

单位 测试条件/注释

仅分配部分;不包括PLL和VCO;

使用时钟信号的上升沿

根据ADC的信噪比方法计算(宽带抖动)

根据ADC的信噪比方法计算(宽带抖动)

仅分配部分;不包括PLL和VCO;

使用时钟信号的上升沿

根据ADC的信噪比方法计算(宽带抖动)

根据ADC的信噪比方法计算(宽带抖动)

CS 内置一个30 kΩ上拉电阻

负值表示内部上拉电阻导致电流流出AD9520

输入电容 2 pF

SCLK(输入),SPI模式

输入逻辑1电压 2.0 V

输入逻辑0电压 0.8 V

输入逻辑1电流 110 µA

输入逻辑0电流 1 µA

输入电容 2 pF

SDIO(输入处于双向模式)

输入逻辑1电压 2.0 V

输入逻辑0电压 0.8 V

输入逻辑1电流 1 µA

输入逻辑0电流 1 µA

输入电容 2 pF

SDIO、SDO(输出)

输出逻辑1电压 2.7 V

输出逻辑0电压 0.4 V

时序

时钟速率(SCLK, 1/t

高电平脉冲宽度,t

低电平脉冲宽度,t

SCLK

)

HIGH

LOW

25 MHz

16 ns

16 ns

SDIO至SCLK建立时间,tDS 4 ns

SCLK至SDIO保持时间,t

DH

0 ns

SCLK至有效SDIO和SDO时间,tDV 11 ns

CS 至SCLK建立和保持时间,tS、t

CS 最短脉冲宽度(高电平),t

PWH

C

2 ns

3 ns

SPI模式下SCLK内置一个30 kΩ下拉电阻,

2

C模式下无内置电阻

I

Rev. 0 | Page 13 of 84

AD9520-0

串行控制端口—I2C模式

表14

参数 最小值 典型值 最大值 单位 测试条件/注释

SDA、SCL(输入数据时)

输入逻辑1电压 0.7 × VS V

输入逻辑0电压 0.3 × VS V

输入电流(输入电压介于0.1 × VS和0.9 × VS之间)

施密特触发器输入的迟滞 0.015 × VS V

输入滤波器必须抑制的尖峰的脉冲宽度,t

SPIKE

SDA(输出数据时)

输出逻辑0电压(3 mA吸电流) 0.4 V

从VIH

MIN

到VIL

的输出下降时间

MAX

(总线电容从10 pF到400 pF)

时序

时钟速率(SCL,f

停止条件与起始条件之间的总线空闲时间,t

重复起始条件的建立时间,t

)

I2C

IDLE

SET;STR

(重复)起始条件保持时间(此周期

结束后产生第一个时钟脉冲),t

停止条件建立时间,t

SET;STP

SCL时钟的低电平周期,t

SCL时钟的高电平周期,t

SCL、SDA上升时间,t

SCL、SDA下降时间,t

数据建立时间,t

数据保持时间,t

RISE

FALL

SET;DAT

HLD;DAT

HLD;STR

1.3 µs

LOW

0.6 µs

HIGH

−10 +10 µA

50 ns

20 + 0.1 C

250 ns Cb = 一条总线的电容(单位pF)

b

400 kHz

1.3 µs

0.6 µs

0.6 µs

0.6 µs

20 + 0.1 Cb 300 ns

20 + 0.1 Cb 300 ns

120 ns

140 880 ns

注意所有I2C时序值均参考

VIH

(0.3 × VS)和VIL

MIN

电平(0.7 × VS)

这与100 ns最小值的原始I²C

规范略有不同

这与0 ns最小值的原始I²C规范略有不同

MAX

1

各条总线的容性负载,C

1

根据原始I2C规范,I2C主机还必须提供最短300 ns的保持时间,以便SDA信号桥接SCL下降沿的未定义区域。

b

400 pF

Rev. 0 | Page 14 of 84

AD9520-0

PD, SYNC和RESET引脚

表15

参数 最小值 典型值 最大值 单位 测试条件/注释

输入特性 这些引脚各有一个30 kΩ内部上拉电阻

逻辑1电压 2.0 V

逻辑0电压 0.8 V

逻辑1电流 1 µA

逻辑0电流 −110 µA

电容 2 pF

复位时序

低电平脉冲宽度 50 ns

RESET 无活动到启动寄存器编程

SYNC 时序

低电平脉冲宽度 1.3 ns 高速时钟为CLK输入信号

串行端口设置引脚:SP1、SP0

100 ns

表16

参数 最小值 典型值 最大值 单位 测试条件/注释

SP1, SP0 这些引脚无内部上拉/下拉电阻

逻辑电平0 0.25 × VS V VS为VS引脚上的电压

逻辑电平½ 0.4 × VS 0.65 × VS V

逻辑电平1 0.8 × VS V

用户可以使这些引脚悬空以获得逻辑电平½;如果此引脚悬空,用

户应将一个电容接地

负值表示内部上拉电阻导致电流流出AD9520

LD、STATUS和REFMON引脚

表17

参数 最小值典型值 最大值 单位 测试条件/注释

输出特性

输出高电压V

输出低电压V

最大反转率 100 MHz

模拟锁定检测

电容 3 pF

REF1、REF2和VCO频率状态监控器

正常范围 1.02 MHz

扩展范围 8 kHz

LD引脚比较器

跳变点 1.6 V

迟滞 260 mV

OH

OL

2.7 V

0.4 V

用作数字输出(CMOS)时;在其它一些模式下,这些

引脚不是CMOS数字输出;见表53 0x017、0x01A和0x01B

适用于多路复用器设置为任意分频器或计数器输出,

或者设置为PFD升/降脉冲时;也适用于模拟锁定检测

模式;通常仅在调试模式下使用;注意:当任一引脚反

转时,杂散可能耦合到输出

片内电容;用于计算模拟锁定检测回读的RC时间常数;

使用一个上拉电阻

高于此频率时,监控器指示参考存在

高于此频率时,监控器指示参考存在

Rev. 0 | Page 15 of 84

AD9520-0

功耗

表18

参数 最小值 典型值 最大值 单位 测试条件/注释

芯片功耗

不包括外部电阻的功耗;所有LVPECL输出端接50 Ω至V

所有CMOS输出具有10 pF容性负载;VS_DRV = 3.3 V

上电默认 1.32 1.5 W 无时钟;无编程;默认寄存器值

PLL锁定;一路LVPECL输出使能 0.55 0.64 W

PLL锁定;一路CMOS输出使能 0.52 W

仅分配模式;VCO分频器开启;

0.39 W

一路LVPECL输出使能

仅分配模式;VCO分频器关闭;

0.36 W

一路LVPECL输出使能

全面运作时的最大功耗 1.5 1.7 W

= 25 MHz;f

f

REF

一路LVPECL输出和输出分频器使能;零延迟关闭;I

= 25 MHz;f

f

REF

一路CMOS输出和输出分频器使能;零延迟关闭;I

f

= 2.4 GHz;f

CLK

和输出分频器使能;零延迟关闭

= 2.4 GHz;f

f

CLK

和输出分频器使能;零延迟关闭

= 250 MHz;VCO = 2.75 GHz;VCO分频比 = 2;

OUT

= 62.5 MHz;VCO = 2.75 GHz;VCO分频比 = 2;

OUT

= 200 MHz;VCO分频比 = 2;一路LVPECL输出

OUT

= 200 MHz;旁路VCO分频器;一路LVPECL输出

OUT

PLL开启;内部VCO = 2750 MHz;VCO分频比 = 2;所有通道分频

器开启;12路LVPECL输出(125 MHz);零延迟开启

PD

关断

PD

关断,最大休眠功耗

60 80 mW

24 33 mW

PD

引脚拉低;不包括终端电阻的功耗

PD

引脚拉低;PLL关断,0x010[1:0] = 01b;关断SYNC;

0x230[2] = 1b;关断分配参考,0x230[1] = 1b

VCP电源 4 4.8 mW PLL工作;典型闭环配置

各功能引起的功耗变化 使能/禁用某个功能时的功耗变化

VCO分频器开/关 32 40 mW 不使用VCO分频器

REFIN(差分)关闭 25 30 mW

REF1、REF2(单端)开/关 15 20 mW

参考输入关闭与差分参考输入模式之间的变化

参考输入关闭与一路单端参考使能之间的变化;如果REF1和

REF2均上电,此数值应加倍

VCO开/关 67 104 mW 内部VCO禁用;选择CLK输入

PLL分频器和鉴相器开/关 51 63 mW PLL关闭至PLL开启,正常工作;无参考使能

LVPECL通道 121 144 mW

无LVPECL输出开启至一路LVPECL输出开启;通道分频比设为1

LVPECL驱动器 51 73 mW 同一通道的第二路LVPECL输出开启

CMOS通道 145 180 mW

无CMOS输出开启至一路CMOS输出开启;通道分频比设为1;

f

= 62.5 MHz、10 pF容性负载

OUT

CMOS驱动器开/关 11 24 mW 同一通道内的其它CMOS输出开启

通道分频器使能 40 57 mW

分频器旁路(1分频)与2分频至32分频之间的变化

零延迟模块开/关 30 34 mW

CP

− 2 V;

CC

= 4.8 mA

CP

= 4.8 mA

Rev. 0 | Page 16 of 84

绝对最大额定值

表19

参数或引脚 相对于 额定值

VS GND −0.3 V至+3.6 V

VCP, CP GND −0.3 V至+5.8 V

VS_DRV GND −0.3 V至+3.6 V

REFIN, REFIN

GND

RSET, LF, BYPASS GND −0.3 V至VS + 0.3 V

CPRSET GND −0.3 V至VS + 0.3 V

CLK, CLK

CLK

SCLK/SCL, SDIO/SDA, SDO, CS

OUT0, OUT0, OUT1, OUT1,

OUT2, OUT2

OUT4, OUT4

OUT6, OUT6

OUT8, OUT8

OUT10, OUT10

SYNC

, OUT3, OUT3,

, OUT5, OUT5,

, OUT7, OUT7,

, OUT9, OUT9,

RESET, PD

,

, OUT11, OUT11

GND

CLK

GND

GND

GND −0.3 V至VS + 0.3 V

REFMON, STATUS, LD GND −0.3 V至VS + 0.3 V

SP0, SP1, EEPROM GND −0.3 V至VS + 0.3 V

1

结温

存储温度范围

引脚温度(10秒)

1

θJA见表20。

150°C

−65°C至+150°C

300°C

−0.3 V至VS + 0.3 V

−0.3 V至VS + 0.3 V

−1.2 V至+1.2 V

−0.3 V至VS + 0.3 V

−0.3 V至VS + 0.3 V

AD9520-0

注意,超出上述绝对最大额定值可能会导致器件永久性

损坏。这只是额定最值,不表示在这些条件下或者在任

何其它超出本技术规范操作章节中所示规格的条件下,

器件能够正常工作。长期在绝对最大额定值条件下工作

会影响器件的可靠性。

热阻

热阻采用JEDEC 51-5 2S2P测试板在静止空气条件下根据

JEDEC JESD51-2进行测量。详情见“热性能”部分。

表20

封装类型 θJA 单位

64引脚LFCSP (CP-64-4) 22 °C/W

ESD警告

ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。

尽管本产品具有专利或专有保护电路,但在遇到高

能量ESD时,器件可能会损坏。因此,应当采取适当

的ESD防范措施,以避免器件性能下降或功能丧失。

Rev. 0 | Page 17 of 84

AD9520-0

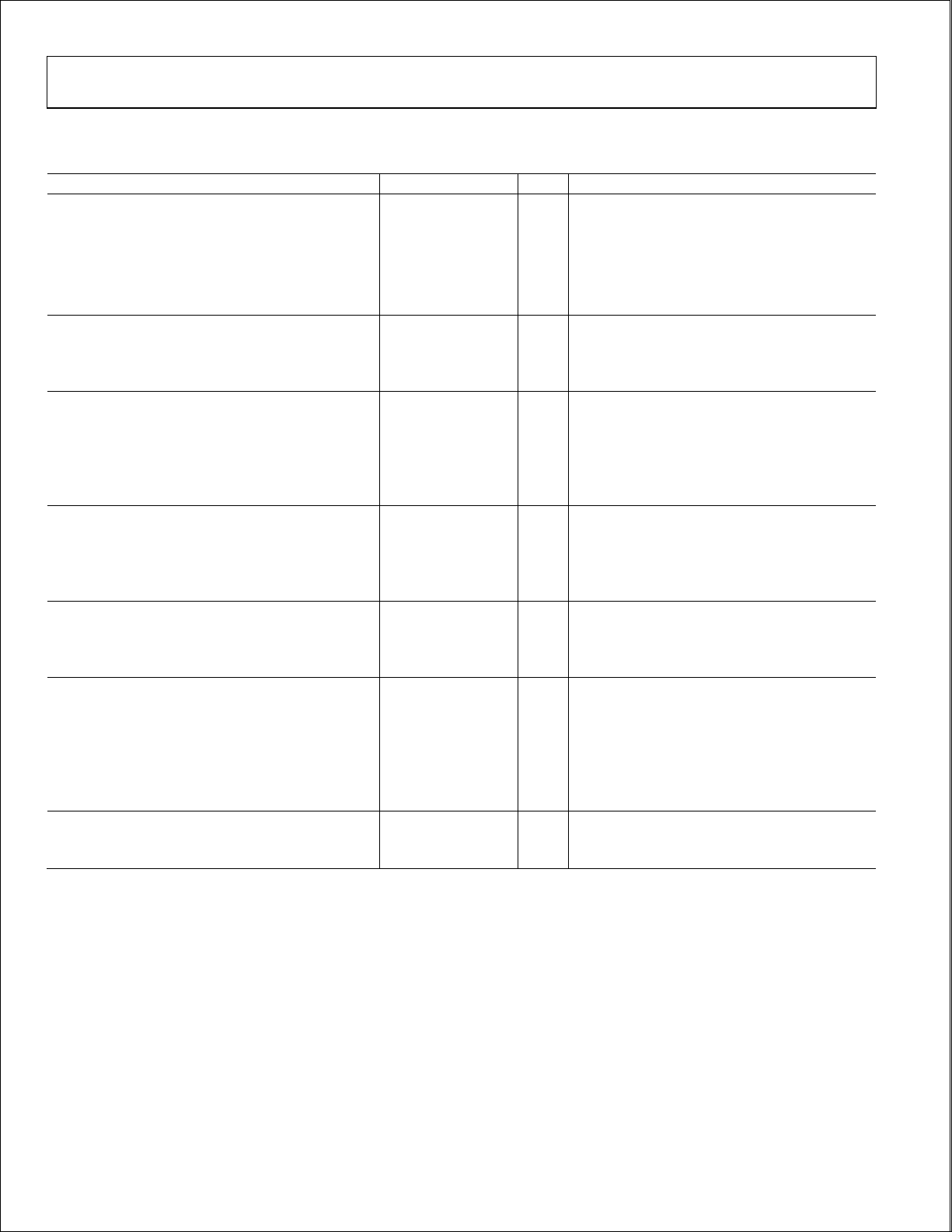

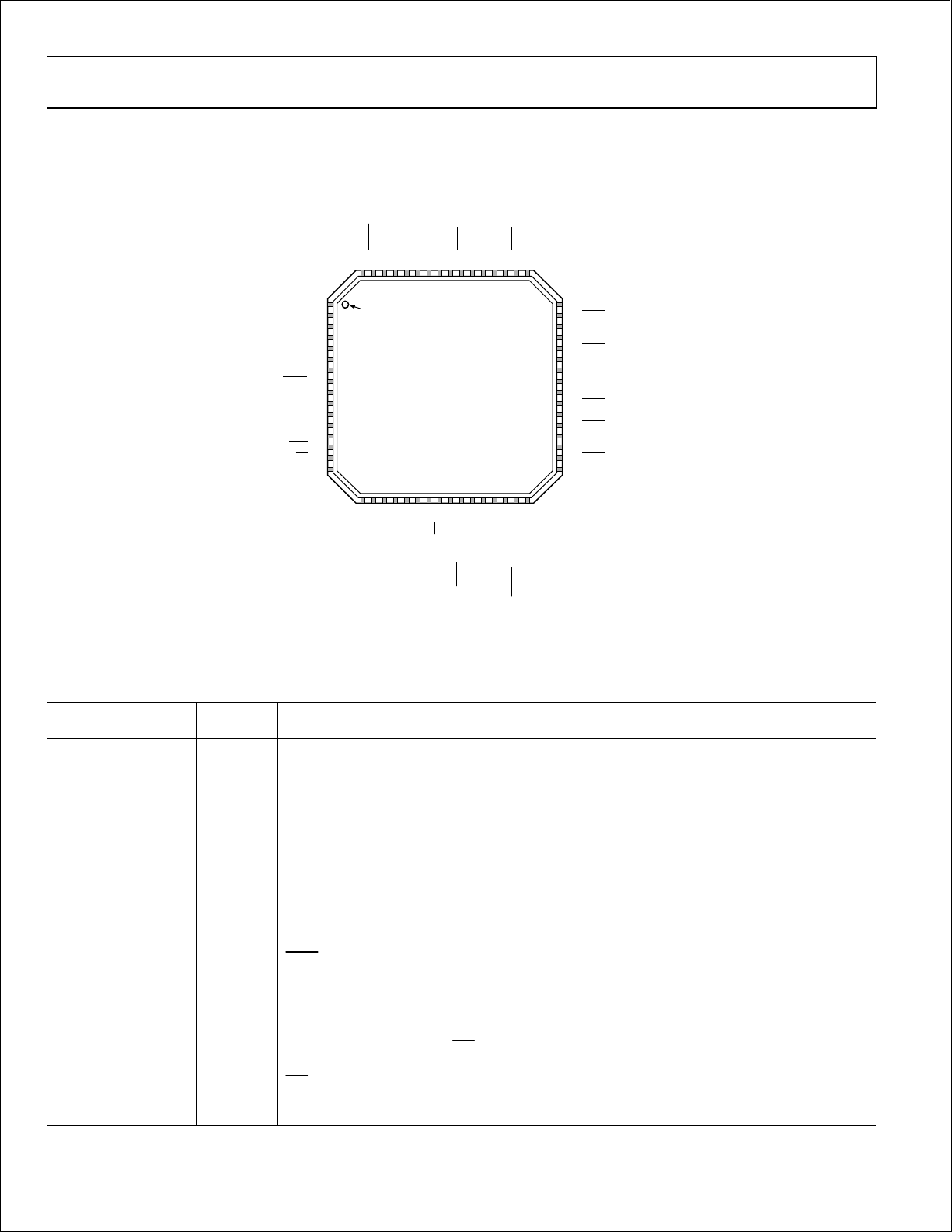

引脚配置和功能描述

REFIN (REF1)

REFIN (REF2)

CPRSETVSVS

GND

RSETVSOUT0 (OUT0A)

OUT0 (OUT0B)

VS_DRV

OUT1 (OUT1A)

OUT1 (OUT1B)

646362616059585756555453525150

OUT2 (OUT2A)

OUT2 (OUT2B)

VS

49

VS

1

PIN 1

REFMON

LD

VCP

CP

STATUS

REF_SEL

SYNC

LF

BYPASS

10

VS

11

VS

12

CLK

13

CLK

14

CS

15

SCLK/SCL

NOTES

1. EXPOSED DIE PAD MUST BE CONNECTED TO GND.

16

INDICATOR

2

3

4

5

6

7

8

9

171819202122232425262728293031

SDIO/SDA

SDO

GND

AD9520

TOP VIEW

(Not to Scale)

SP1

SP0

EEPROM

PD

RESET

VS_DRV

OUT10A)

T9 (OUT9A)

T9 (OUT9B)

OU

OU

OUT10 (

OUT10B)

OUT11A)

OUT11B)

OUT10 (

OUT11 (

OUT11 (

48

OUT3 (OUT3A)

47

OUT3 (OUT3B)

46

VS_DRV

45

O

UT4 (OUT4A)

44

OUT4 (OUT4B)

43

OUT5 (OUT5A)

42

OUT5 (OUT5B)

41

VS

40

VS

39

OUT8 (OUT8B)

38

OUT8 (OUT8A)

37

OUT7 (OUT7B)

36

OUT7 (OUT7A)

35

VS_DRV

34

OUT6 (OUT6B)

33

OUT6 (OUT6A)

32

VS

07213-003

图5. 引脚配置

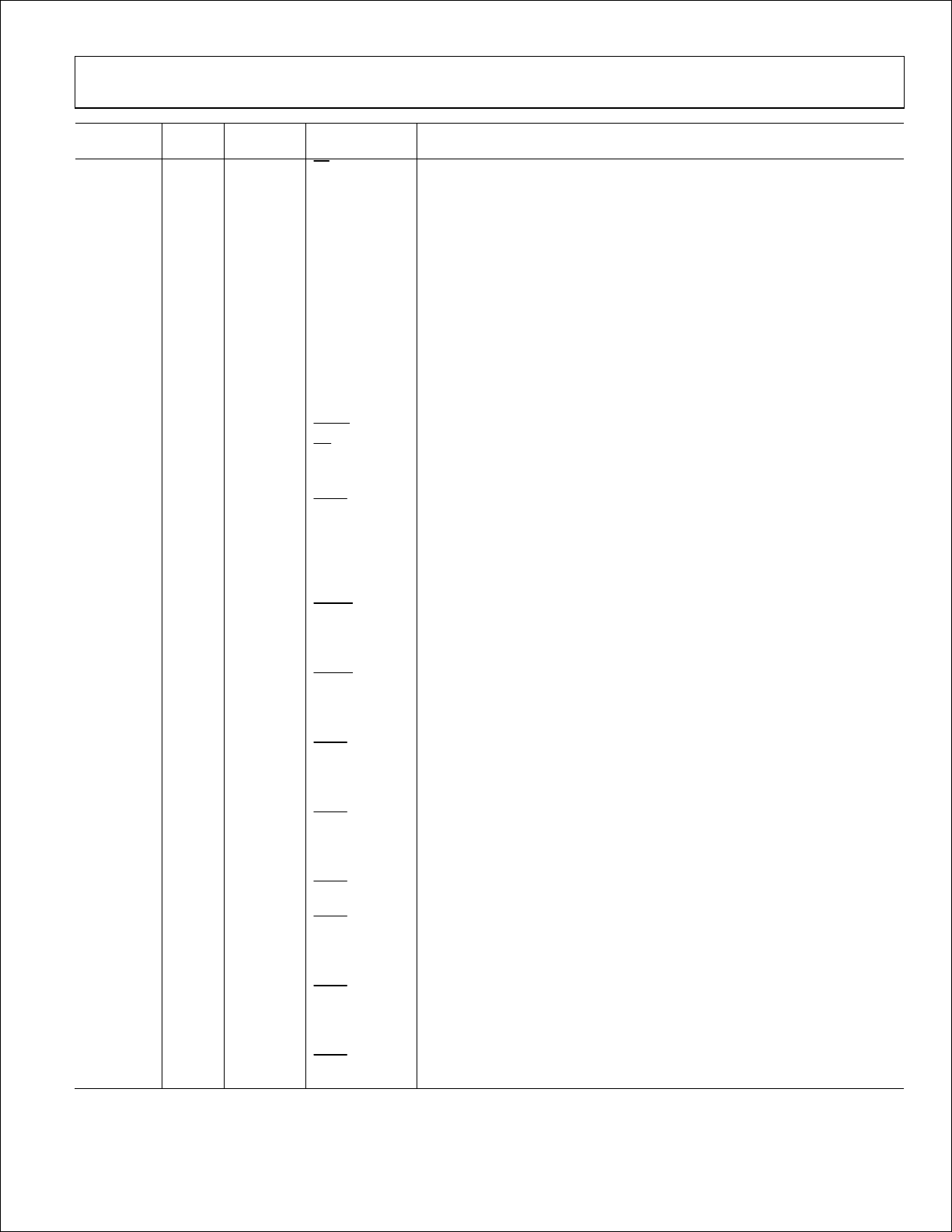

表21. 引脚功能描述

输入/

引脚编号

1, 11, 12,32,

输出

I 电源 VS 3.3 V电源引脚。

引脚类型 引脚名称 描述

40, 41,49,

57, 60, 61

2 O 3.3 V CMOS REFMON 参考监控器(输出)。此引脚具有多个可选输出。

3 O 3.3 V CMOS LD

4 I 电源 VCP

锁定检测(输出)。此引脚具有多个可选输出。

电荷泵(CP)的电源;VS < VCP < 5.0 V。

如果不使用PLL,VCP仍须连接到3.3 V。

5 O CP

环路滤波器

电荷泵(输出)。此引脚连接到外部环路滤波器。

如果不使用PLL,此引脚可以不连接。

6 O 3.3 V CMOS STATUS

7 I 3.3 V CMOS REF_SEL

可编程状态输出。

参考选择。选择REF1(低电平)或REF2(高电平)。

此引脚内置一个30 kΩ下拉电阻。

8 I 3.3 V CMOS

SYNC

手动同步和手动保持。此引脚启动手动同步,并用于手动保持。

低电平有效。此引脚内置一个30 kΩ上拉电阻。

9 I

10 O BYPASS

13 I

环路滤波器

环路滤波器

差分时钟

LF

CLK

输入

14 I

差分时钟

此引脚与CLK一起构成时钟分配部分的差分输入。

CLK

输入

环路滤波器(输入)。内部连接到VCO控制电压节点。

此引脚用于通过一个220 nF电容将LDO旁路至地。

此引脚与CLK一起构成时钟分配部分的差分输入。

如果将单端输入连接到CLK引脚,应在该引脚与地之间连接一个0.1 μF旁路电容。

Rev. 0 | Page 18 of 84

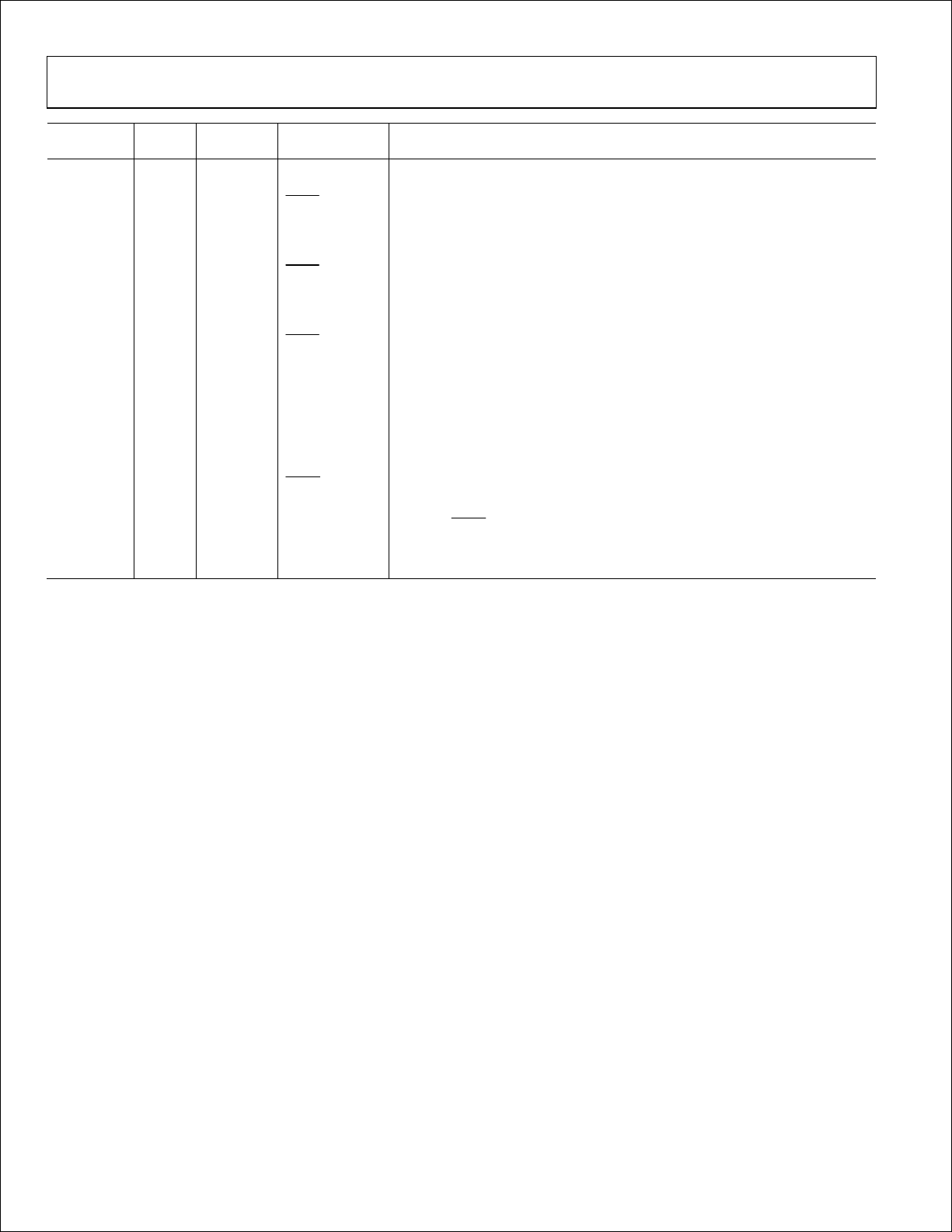

输入/

引脚编号

输出

引脚类型 引脚名称 描述

15 I 3.3 V CMOS

AD9520-0

串行控制端口片选;低电平有效。此引脚内置一个30 kΩ上拉电阻。

CS

16 I 3.3 V CMOS SCLK/SCL

串行控制端口时钟信号。SPI模式下此引脚内置一个30 kΩ下拉电阻,

2

C模式下为高阻抗。

I

17 I/O 3.3 V CMOS SDIO/SDA 串行控制端口双向串行数据输入/输出。

18 O 3.3 V CMOS SDO 串行控制端口单向串行数据输出。

19, 59 I GND GND 接地引脚。

20 I

三电平逻辑

SP1

选择SPI或I

2

C作为串行接口端口,在I2C模式下选择I2C从机地址。三

电平逻辑。该引脚内部偏置到开路逻辑电平。

21 I

三电平逻辑

22 I 3.3 V CMOS EEPROM

SP0

选择SPI或I

电平逻辑。该引脚内部偏置到开路逻辑电平。

C作为串行接口端口,在I2C模式下选择I2C从机地址。三

2

设置此引脚为高电平,可选择在复位和/或上电时载入内部EEPROM

中存储的寄存器值。设置此引脚为低电平,则使AD9520在上电/复

位时载入硬编码的默认寄存器值。此引脚内置一个30 kΩ下拉电阻。

23 I 3.3 V CMOS

24 I 3.3 V CMOS

25 O

LVPECL 或

CMOS

26 O

LVPECL 或

CMOS

27, 35,

I 电源 VS_DRV

46, 54

28 O

LVPECL 或

CMOS

29 O

LVPECL 或

CMOS

30 O

LVPECL 或

CMOS

31 O

LVPECL 或

CMOS

33 O

LVPECL 或

CMOS

34 O

LVPECL 或

CMOS

36 O

LVPECL 或

CMOS

37 O

LVPECL 或

CMOS

38 O

LVPECL 或

CMOS

39 O

LVPECL 或

CMOS

42 O

LVPECL 或

CMOS

43 O

LVPECL 或

CMOS

44 O

LVPECL 或

CMOS

45 O

LVPECL 或

CMOS

47 O

LVPECL 或

CMOS

RESET

PD

OUT9 (OUT9A)

(OUT9B)

OUT9

OUT10

(OUT10A)

(OUT10B)

OUT10

OUT11

(OUT11A)

(OUT11B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT11

OUT6 (OUT6A)

(OUT6B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT6

OUT7 (OUT7A)

(OUT7B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT7

OUT8 (OUT8A)

(OUT8B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT8

(OUT5B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT5

OUT5 (OUT5A)

(OUT4B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT4

OUT4 (OUT4A)

(OUT3B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

OUT3

芯片复位,低电平有效。此引脚内置一个30 kΩ上拉电阻。

芯片关断引脚,低电平有效。此引脚内置一个30 kΩ上拉电阻。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,或

者配置为单端CMOS输出。

输出驱动器电源引脚。作为一组,这些引脚可以设置为2.5 V或3.3 V。

所有4个引脚必须设为相同的电压。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

或者配置为单端CMOS输出。

Rev. 0 | Page 19 of 84

AD9520-0

输入/

引脚编号

48 O

50 O

51 O

52 O

53 O

55 O

56 O

58 O RSET

62 O

63 I

64 I

EPAD

输出

引脚类型 引脚名称 描述

LVPECL 或

CMOS

LVPECL 或

CMOS

LVPECL 或

CMOS

LVPECL 或

CMOS

LVPECL 或

CMOS

LVPECL 或

CMOS

LVPECL 或

CMOS

电流设置

电阻

电流设置

电阻

参考输入 REFIN

参考输入

GND GND

OUT3 (OUT3A)

OUT2

OUT2 (OUT2A)

OUT1

OUT1 (OUT1A)

OUT0

OUT0 (OUT0A)

CPRSET

REFIN (REF1)

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

(OUT2B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

(OUT1B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

(OUT0B) 时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟输出。此引脚可以配置为差分LVPECL输出的一端,

或者配置为单端CMOS输出。

时钟分配电流设置电阻。

应将一个4.12 kΩ电阻连接在此引脚与GND之间。

电荷泵电流设置电阻。应将一个5.1 kΩ电阻连接在此引脚与GND之间。

如果不使用PLL,则无需连接该电阻。

(REF2)

此引脚与REFIN一起构成PLL参考的差分输入。

此引脚还可以是REF1的单端输入。

此引脚与REFIN一起构成PLL参考的差分输入。

此引脚还可以是REF1的单端输入。

裸露焊盘必须连接到GND。

Rev. 0 | Page 20 of 84

–

典型工作特性

350

3 CHANNELS—6 LVPECL

AD9520-0

5

300

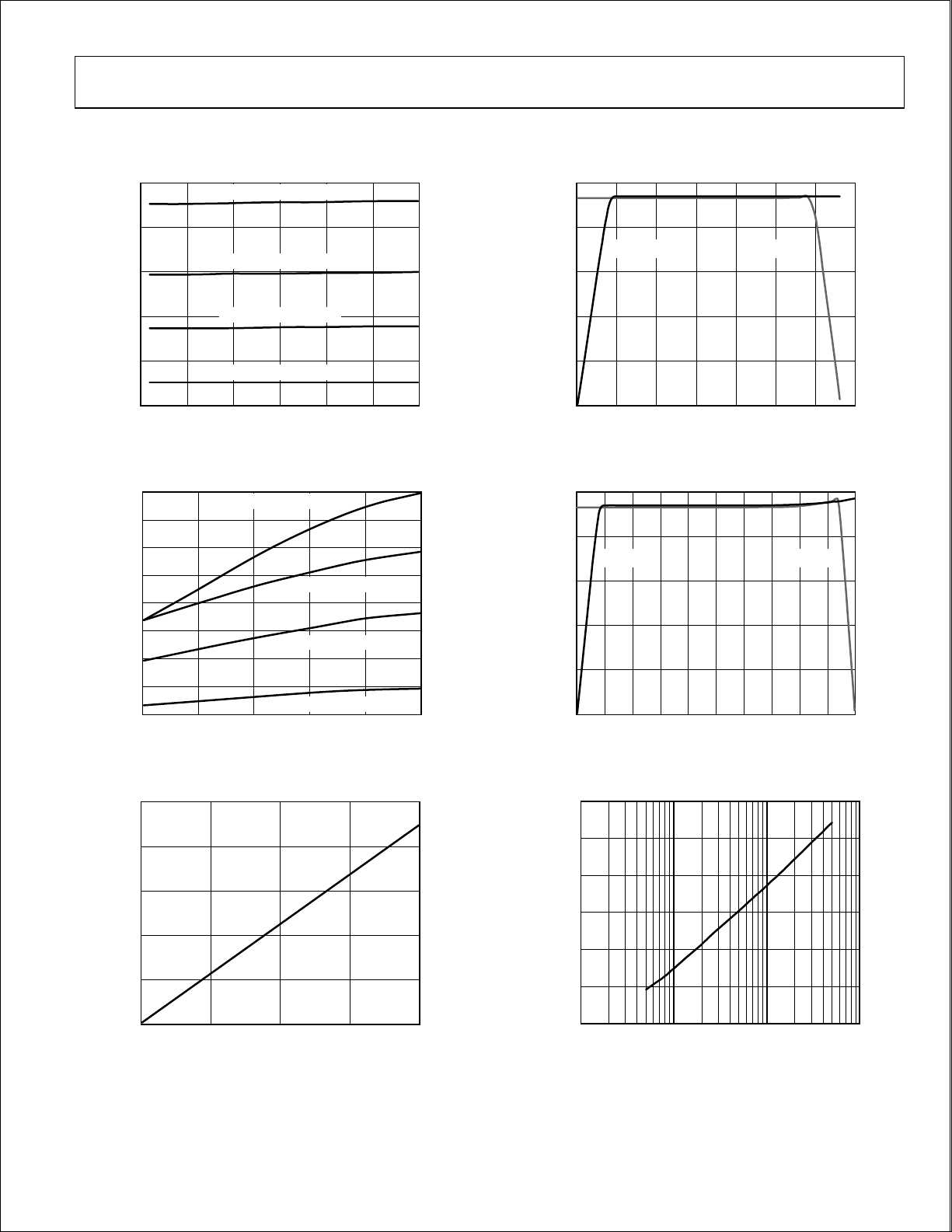

250

200

CURRENT (mA)

150

100

0 500 1000 1500 2000 2500 3000

3 CHANNELS—3 LVPECL

2 CHANNELS—2 LVPECL

1 CHANNEL—1 LVPECL

FREQUENCY (MHz)

图6. 总电流与频率的关系,CLK至输出(PLL关闭),

LVPECL输出端接50 Ω至VS_DRV − 2 V

240

220

200

180

160

140

CURRENT (mA)

120

100

80

0 50 100 150 200 250

3 CHANNELS—6 CMOS

3 CHANNELS—3 CMOS

2 CHANNELS—2 CMOS

1 CHANNEL—1 CMOS

FREQUENCY (MHz)

图7. 总电流与频率的关系,CLK至输出

(PLL关闭),CMOS输出,10 pF负载

65

4

PUMP UPPUMP DOWN

3

2

CURRENT FROM CP PIN (mA)

1

0

07213-108

VOLTAGE ON CP PIN (V)

30 3.02.52.01.51.00.5

.5

07213-111

图9. 电荷泵特性(VCP = 3.3 V)

5

4

PUMP DOWN PUMP UP

3

2

CURRENT FROM CP PIN (mA)

1

0

07213-109

VOLTAGE ON CP PIN (V)

50 4.03.0 4.53.55.0 0.1 5.1 0.2 5.2

.0

07213-112

图10. 电荷泵特性(VCP = 5.0 V)

140

60

55

(MHz/V)

VCO

50

K

45

40

2.55 2.952.852.752.65

VCO FREQUENCY (GHz)

图8. K

与VCO频率的关系 图11. 折合到PFD输入端的PFD相位噪声与PFD频率的关系

VCO

07213-010

–145

–150

–155

(dBc/Hz)

–160

–165

PFD PHASE NOISE REFERRED TO PFD INPUT

–170

0.1 1 10010

PFD FREQUENCY (MHz)

07213-013

Rev. 0 | Page 21 of 84

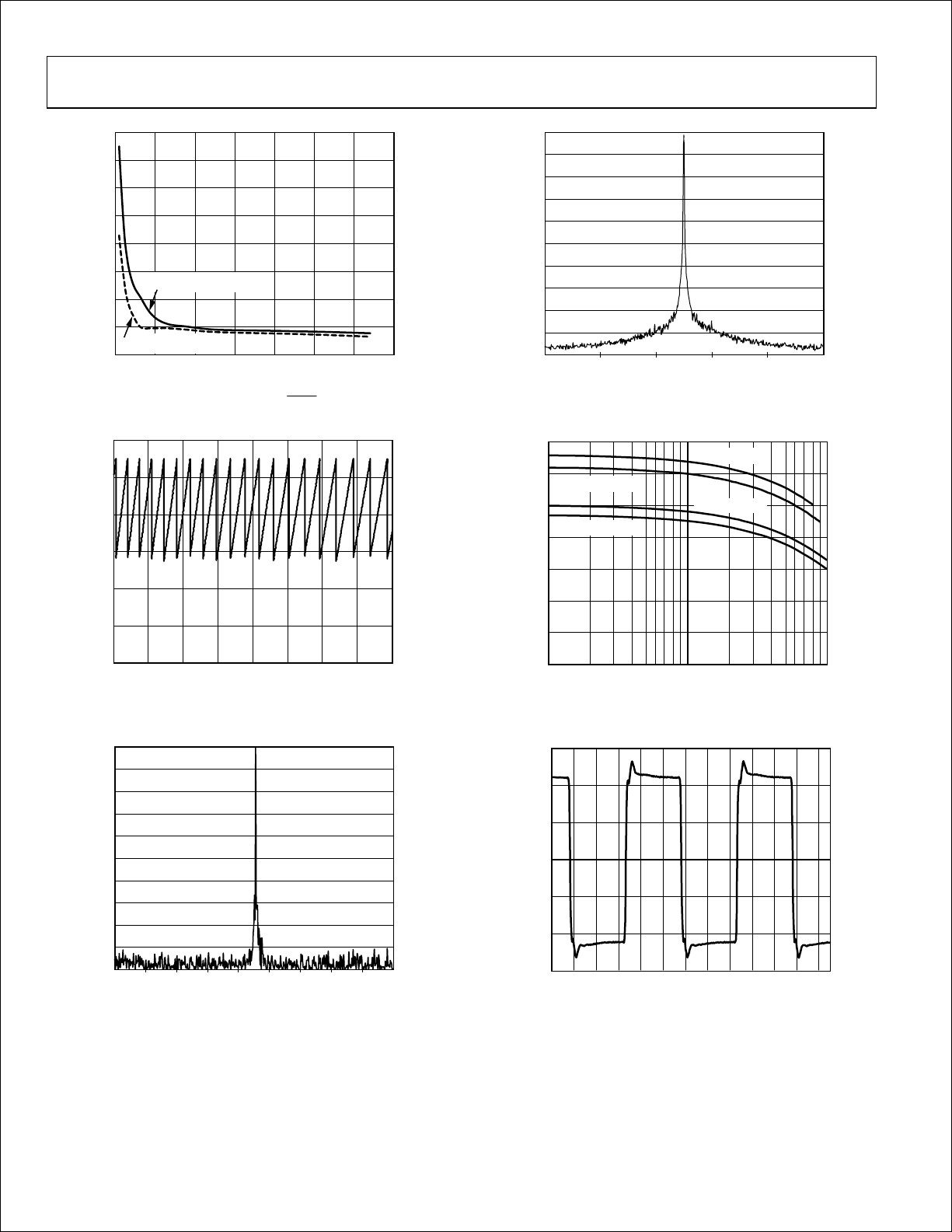

AD9520-0

–208

–210

–212

–214

–216

–218

–220

PLL FIGURE OF MERIT (dBc/Hz)

–222

–224

DIFFERENTIAL INPUT

SINGLE-ENDED INPUT

0 0.4 0.8 1.20.2 0.6 1.0 1.4

INPUT SLEW RATE (V/ns)

07213-114

图12. PLL品质因数(FOM)与REFIN/REFIN压摆率的关系 图15. LVPECL输出频谱;122.88 MHz;PFD = 15.36 MHz;

2.1

1.9

1.7

1.5

1.3

VCO TUNING VOLTAGE (V)

1.1

0

–10

–20

–30

–40

–50

–60

POWER (dBm)

–70

–80

–90

–100

122.38 122.58 122.78 122.98 123.18 123.38

LBW = 127 kHz;I

3.5

3.0

VS_DRV = 3.135V

2.5

VS_DRV = 2.35V

2.0

(V)

OH

V

1.5

1.0

0.5

FREQUENCY (MHz)

= 3.0 mA;f

CP

VS_DRV = 3.3V

VS_DRV = 2.5V

= 2703.4 MHz

VCO

07213-117

0.9

2.55 2.952.902.852.802.752.702.652.60

FREQUENCY (GHz)

图13. VCO调谐电压与频率的关系 图16. CMOS输出V

0

–10

–20

–30

–40

–50

–60

POWER (dBm)

–70

–80

–90

–100

100 511 021 521 031 531 041 541110105

FREQUENCY (MHz)

图14. PFD/CP杂散;122.88 MHz;PFD = 15.36 MHz;

LBW = 127 kHz;I

= 3.0 mA;f

CP

= 2703.4 MHz

VCO

0

10k 1k 100

07213-115

1.2

0.8

0.4

0

–0.4

DIFFERENTIAL OUTPUT (V)

–0.8

–1.2

07213-116

RESISTIVE LOAD (Ω)

(静态)与R

OH

TIME (ns)

LOAD

(接地)的关系

07213-118

20 81 02 2241 6101 218642

4

07213-014

图17. LVPECL输出(差分,100 MHz)

Rev. 0 | Page 22 of 84

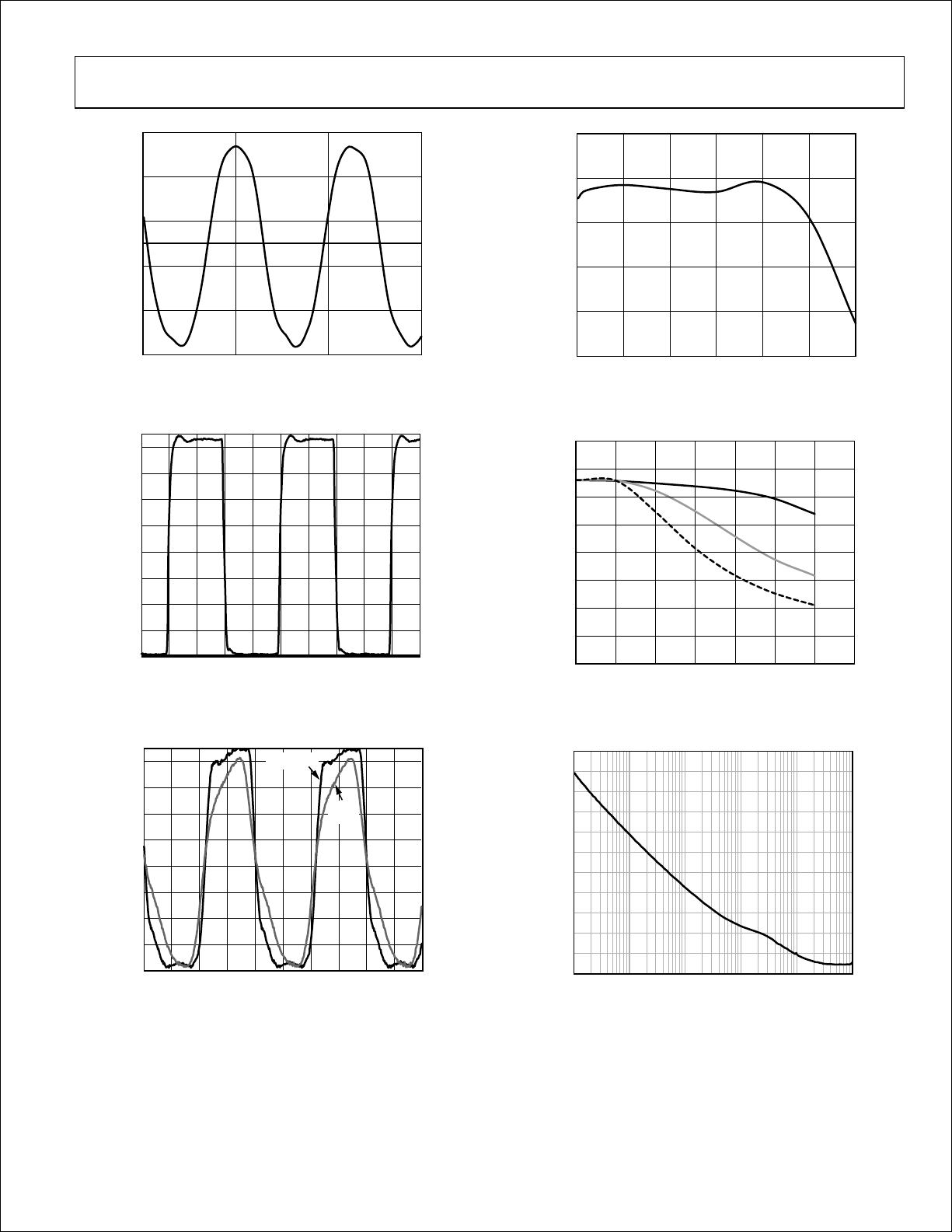

AD9520-0

1.0

2.0

0.6

0.2

–0.2

DIFFERENTIAL SWING (V p-p)

–0.6

–1.0

TIME (ns)

10 0.5 1.0

.5

07213-015

图18. LVPECL差分电压摆幅(1600 MHz)

3.2

2.8

2.4

2.0

1.6

AMPLITUDE (V)

1.2

0.8

0.4

0

TIME (ns)

80 60 1004020 7050 903010

0

07213-018

图19. CMOS输出(10 pF负载,25 MHz)

3.2

2.8

2.4

2.0

1.6

AMPLITUDE (V)

1.2

0.8

0.4

0

2pF LOAD

TIME (ns)

10pF

LOAD

987 6 5 4 3 2 1

10 0

07213-019

1.8

1.6

1.4

DIFFERENTIAL SWING (V p-p)

1.2

1.0

4.0

3.5

3.0

2.5

2.0

1.5

AMPLITUDE (V)

1.0

0.5

0

–40

–50

–60

–70

–80

–90

–100

–110

PHASE NOISE (dBc/Hz)

–120

–130

–140

–150

FREQUENCY (GHz)

图21. LVPECL差分电压摆幅与频率的关系

图22. CMOS输出摆幅与频率和容性负载的关系

1k 100M1M 10M100k10k

FREQUENCY (MHz)

FREQUENCY (Hz)

图20. CMOS输出(2 pF和10 pF负载,250 MHz) 图23. 内部VCO相位噪声(绝对),直接至LVPECL (2550 MHz)

30 1.5 2.0 2.51.00.5

.0

07213-123

2pF

10pF

20pF

70

600500400300200100

00

07213-124

07213-023

Rev. 0 | Page 23 of 84

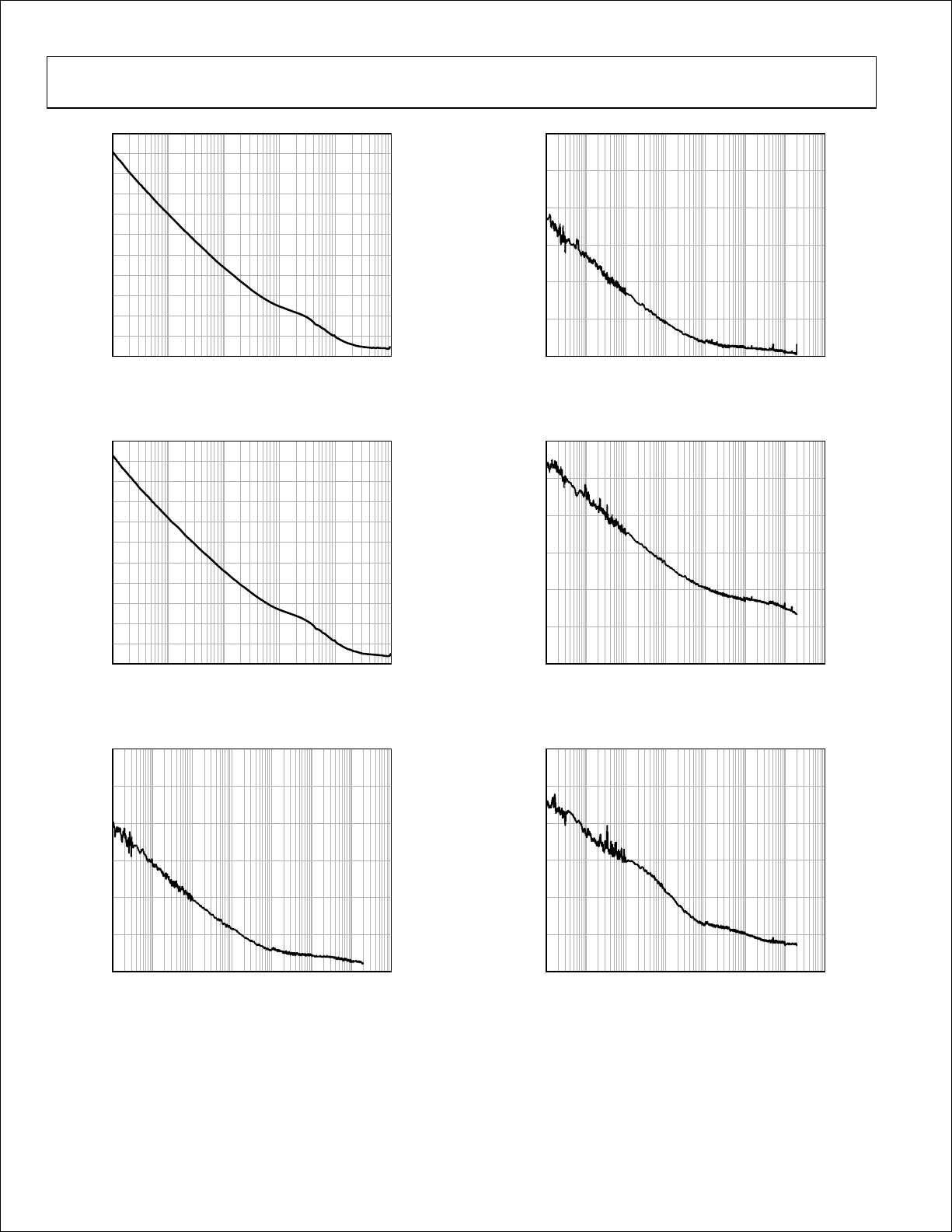

AD9520-0

–40

–50

–60

–70

–80

–90

–100

–110

PHASE NOISE (dBc/Hz)

–120

–130

–140

–150

1k 100M1M 10M100k10k

图24. 内部VCO相位噪声(绝对),直接至LVPECL (2750 MHz) 图27. 加性(残余)相位噪声,CLK至LVPECL (200 MHz),5分频

–40

–50

–60

–70

–80

–90

–100

–110

PHASE NOISE (dBc/Hz)

–120

–130

–140

–150

1k 100M1M 10M100k10k

图25. 内部VCO相位噪声(绝对),直接至LVPECL (2950 MHz) 图28. 加性(残余)相位噪声,CLK至LVPECL (1600 MHz),1分频

–100

FREQUENCY (Hz)

FREQUENCY (Hz)

07213-024

07213-025

–100

–110

–120

–130

–140

PHASE NOISE (dBc/Hz)

–150

–160

10 1k100 100M1M 10M100k10k

–100

–110

–120

–130

–140

PHASE NOISE (dBc/Hz)

–150

–160

10 1k100 100M1M 10M100k10k

–110

FREQUENCY (Hz)

FREQUENCY (Hz)

07213-129

07213-130

–110

–120

–130

–140

PHASE NOISE (dBc/Hz)

–150

–160

10 1k100 100M1M 10M100k10k

FREQUENCY (Hz)

07213-128

–120

–130

–140

–150

PHASE NOISE (dBc/Hz)

–160

–170

10 1k100 100M1M 10M100k10k

FREQUENCY (Hz)

图26. 加性(残余)相位噪声,CLK至LVPECL (245.76 MHz),1分频 图29. 加性(残余)相位噪声,CLK至CMOS (50 MHz),20分频

Rev. 0 | Page 24 of 84

07213-131

AD9520-0

–100

–110

–120

–120

–130

–130

–140

PHASE NOISE (dBc/Hz)

–150

–160

10 1k100 100M1M 10M100k10k

FREQUENCY (Hz)

07213-132

–140

PHASE NOISE (dBc/Hz)

–150

–160

1k 100M1M 10M100k10k

FREQUENCY (Hz)

图30. 加性(残余)相位噪声,CLK至CMOS (250 MHz),4分频 图33. 相位噪声(绝对),外部VCXO(Toyocom TCO-2112,245.76 MHz);

PFD = 15.36 MHz;LBW = 250 Hz;LVPECL输出 = 245.76 MHz

–100

–110

–120

–130

–140

PHASE NOISE (dBc/Hz)

–150

–160

1k 100M1M 10M100k10k

FREQUENCY (Hz)

图31. 相位噪声(绝对)时钟产生;内部VCO (2.703 GHz);

PFD = 15.36 MHz;LBW = 63 kHz;LVPECL输出 = 122.88 MHz

–80

–90

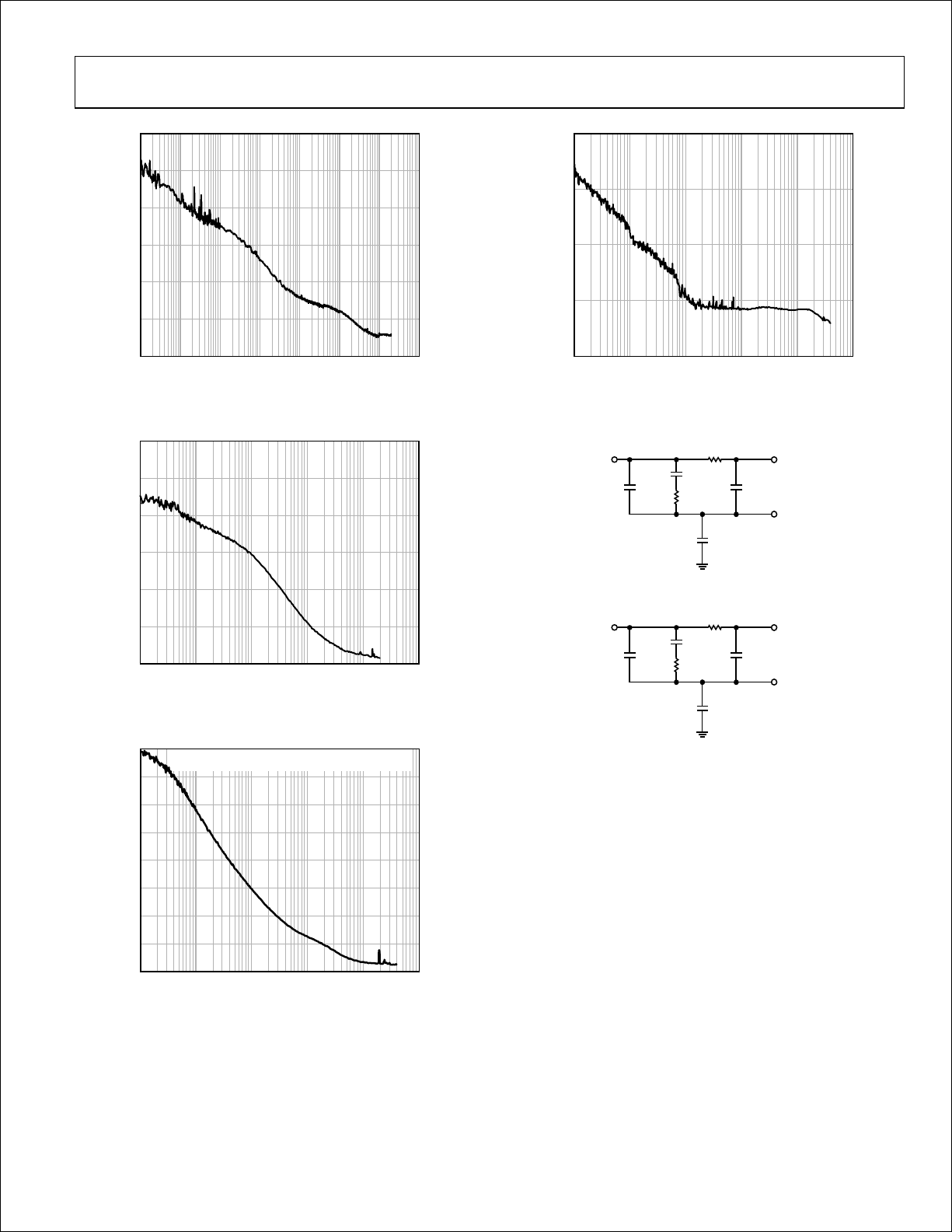

INTEGRATED RMS JITTER (12kHz TO 20MHz): 652fs

C2

62pF

BYPASS

CAPACITOR

FOR LDO

图34. 用于时钟产生的PLL环路滤波器图(见图31)

C2

1.5nF

07213-033

BYPASS

CAPACITOR

FOR LDO

图35. 用于时钟净化的PLL环路滤波器图(见图32)

C1

240nF

R1

820Ω

C1

4.7µF

R1

2.1kΩ

R2

390Ω

C12

220nF

R2

3kΩ

C12

220nF

C3

33pF

C3

2.2nF

LFCP

BYPASS

07213-234

LFCP

BYPASS

07213-235

07213-135

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

1k 100M1M 10M100k10k

FREQUENCY (Hz)

图32. 相位噪声(绝对)时钟净化;内部VCO (2.799 GHz);

PFD = 120 kHz;LBW = 2.1 kHz;LVPECL输出 = 155.52 MHz

07213-034

Rev. 0 | Page 25 of 84

AD9520-0

术语

相位抖动和相位噪声

理想情况下,在正弦波的每个周期,相位都会随着时间从0°

连续均匀地变化到360°。不过,实际信号的相位随时间的

变化与理想情况会有一定的偏差,这种现象称为相位抖

动。导致相位抖动的原因有许多,其中一个主要原因是随

机噪声,其统计特征为高斯(正则)分布。

这种相位抖动导致正弦波能量在频域中扩散,产生连续的

功率频谱。通常将该功率频谱报告为相对于正弦波(载波)的

给定频率偏移下的一系列值,其单位为dBc/Hz。该值是1 Hz

带宽内包含的功率与载波频率时的功率之比(用dB表示)。对

于每次测量,还会给出相对于载波频率的偏移。

对一定偏移频率区间(例如10 kHz到10 MHz)内所含的总功

率进行积分很有意义。这称为该频率偏移区间内的积分相

位噪声,它与该偏移频率区间内的相位噪声所引起的时间

抖动直接相关。

相位噪声对ADC、DAC和RF混频器的性能有不利影响。虽

然影响方式不同,但它会降低转换器和混频器可实现的动

态范围。

时间抖动

相位噪声是一种频域现象。在时域内,该效应表现为时间

抖动。观察正弦波时,连续过零的时间并不固定。方波

中,时间抖动表现为边沿偏离其理想(规则)的出现时间。

这两种情况下,实际时序与理想时序的偏差即为时间抖

动。这些偏差是随机的,因此用均方根(rms)秒或高斯分布

的1 Σ来规定时间抖动。

出现在DAC或ADC采样时钟上的时间抖动会降低转换器的

信噪比(SNR)和动态范围。抖动最低的采样时钟可使给定

转换器发挥最高性能。

加性相位噪声

加性相位噪声指可归因于受测设备或子系统的相位噪声

量。所有外部振荡器或时钟源的相位噪声都会被扣除。这

样,当器件结合不同的振荡器和时钟源使用时,就可以预

测器件对系统总相位噪声的影响程度。各元件都会贡献一

定的相位噪声,但在许多情况下,某个元件的相位噪声占

居系统总相位噪声的主要部分。当有多个相位噪声源时,

总相位噪声等于各噪声源的平方和的平方根。

加性时间抖动

加性时间抖动指可归因于受测设备或子系统的时间抖动

量。所有外部振荡器或时钟源的时间抖动都会被扣除。这

样,当器件结合不同的振荡器和时钟源使用时,就可以预

测器件对系统总时间抖动的影响程度。各元件都会贡献一

定的时间抖动,但在许多情况下,外部振荡器和时钟源的

时间抖动占居系统时间抖动的主要部分。

Rev. 0 | Page 26 of 84

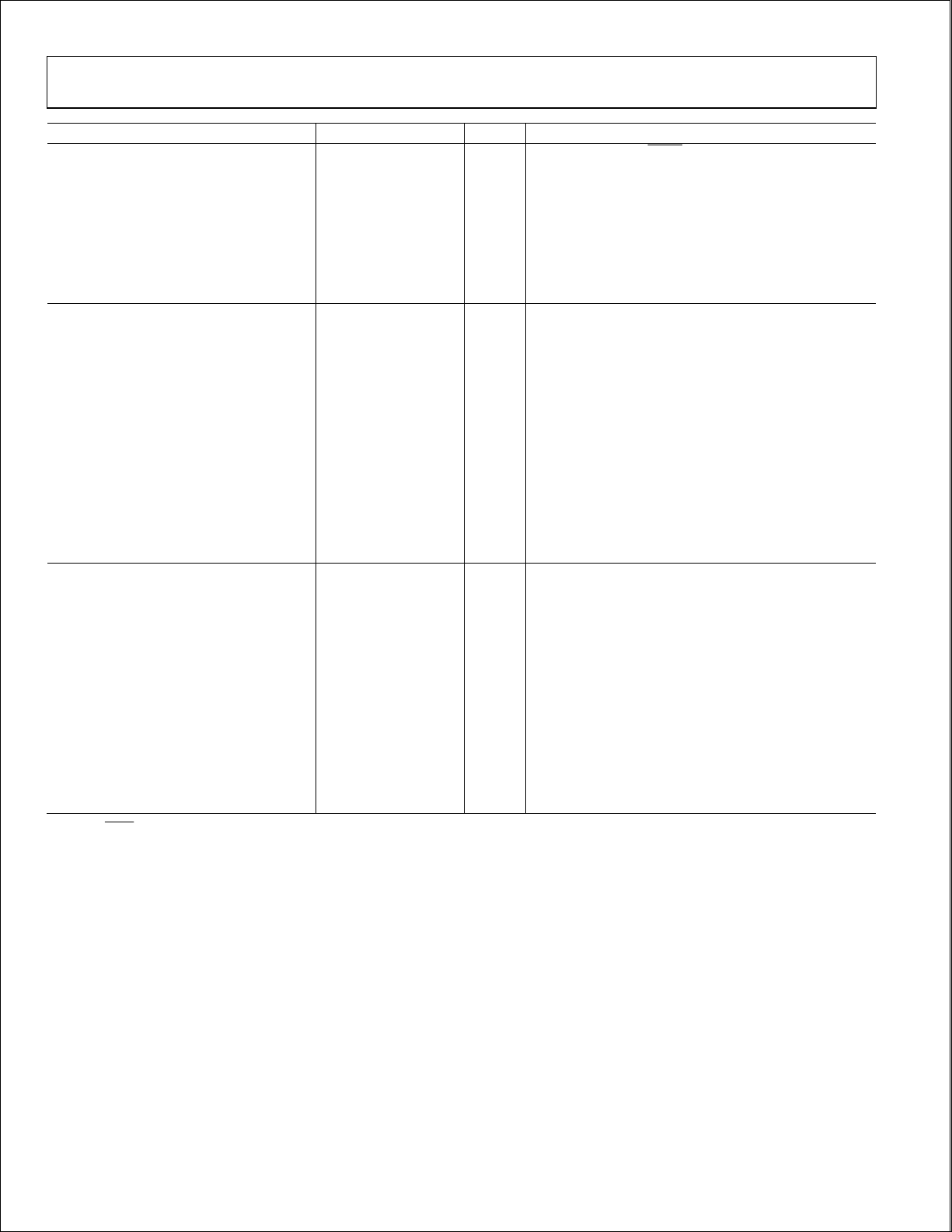

详细框图

OPTIONAL

REFIN

REFIN

BYPASS

LF

REF_SEL CPRSET VCPVS GND RSET

REFERENCE

REF1

REF2

SWITCHOVER

STATUS

BUF

AMP

LOW DROPOUT

REGULATOR (LDO)

STATUS

CLOCK

STATUS

P, P + 1

PRESCALER

N DIVIDER

ZERO DELAY BLOCK

DISTRIBUTION

REFERENCE

DOUBLER

A/B

COUNTERS

REFMON

R

DIVIDER

PROGRAMMABLE

PROGRAMMABLE

N DELAY

AD9520-0

LOCK

DETECT

R DELAY

PHASE

FREQUENCY

DETECTOR

PLL

REFERENCE

CHARGE

HOLD

PUMP

LD

CP

STATUS

CLK

CLK

PD

SYNC

RESET

EEPROM

SP1

SP0

SCLK/SCL

SDIO/SDA

SDO

CS

DIGITAL

LOGIC

SERIAL

PORT

DECODE

INTERFACE

SPI

EEPROM

INTERFACE

I2C

DIVIDE BY 1,

2, 3, 4, 5, OR 6

0 1

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

VS_DRV

OUT0

OUT0

OUT1

OUT1

OUT2

OUT2

OUT3

OUT3

OUT4

OUT4

OUT5

OUT5

OUT6

OUT6

LVPECL/CMOS OUTPUT

OUT7

OUT7

OUT8

OUT8

AD9520

DIVIDE BY

1 TO 32

图36

Rev. 0 | Page 27 of 84

OUT9

OUT9

OUT10

OUT10

OUT11

OUT11

07213-028

AD9520-0

工作原理

工作配置

AD9520有多种配置方式,必须通过加载控制寄存器进行配

置(见表49至表60)。各部分或功能必须通过设置相应的一

个或多个控制寄存器中的适当位进行独立编程。设置好所

需的配置后,用户可以将这些值存储到片内EEPROM中,

器件上电时便可以采用所需的配置,而无需用户干预。

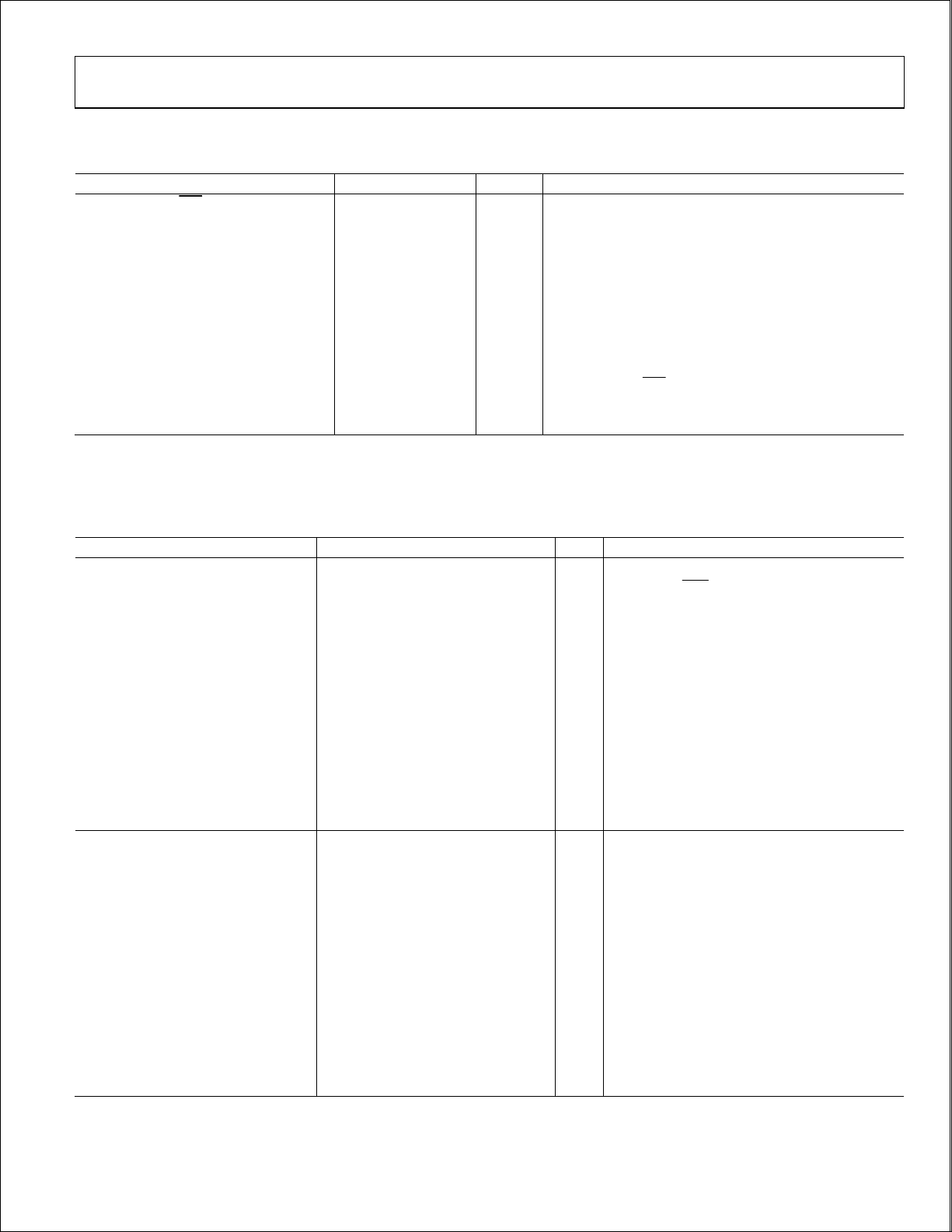

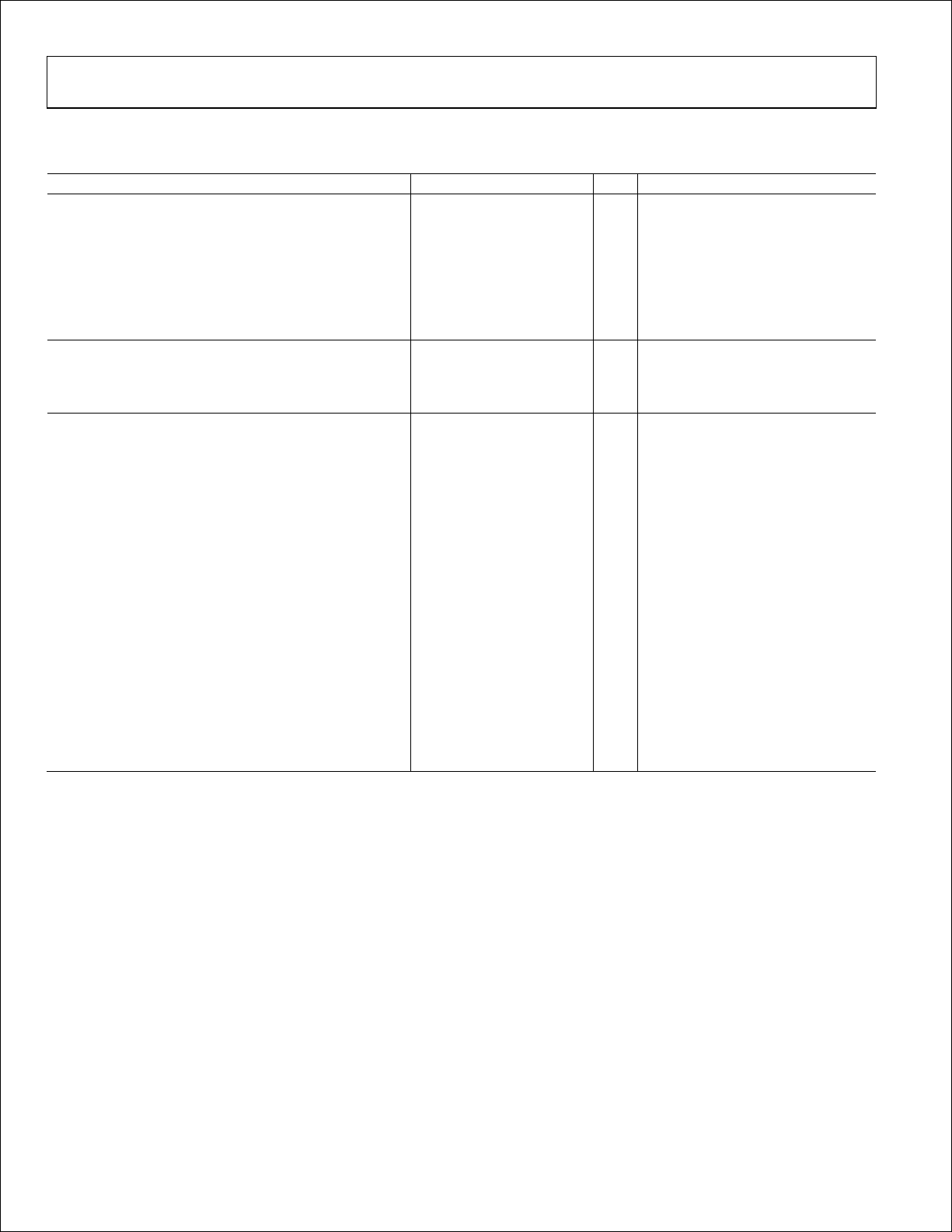

模式0:内部VCO和时钟分配

使用内部VCO和PLL时,必须采用VCO分频器,确保提供

给通道分频器的频率不超过其额定最大频率(见表3)。内部

PLL利用外部环路滤波器设置环路带宽。该外部环路滤波

器对于环路稳定性也很重要。

使用内部VCO时,必须校准VCO (0x018[0]),确保性能最

佳。

对于内部VCO和时钟分配应用,应使用表22所示的寄存器

设置。

表22. 使用内部VCO时的设置

寄存器 描述

0x010[1:0] = 00b PLL正常工作(PLL开启)

0x010 to 0x01E

0x1E1[1] = 1b 选择VCO作为时钟源

0x01C[2:0] 使能参考输入

0x1E0[2:0] 设置VCO分频器

0x1E1[0] = 0b

0x018[0] = 0b

0x232[0] = 1b

0x018[0] = 1b

0x232[0] = 1b

PLL设置;选择并使能一路参考输入;

根据目标环路配置设置R、N(P、A、B)、

PFD极性和ICP

使用VCO分频器作为分配部分的时钟源

复位VCO校准并发出IO_UPDATE(上电后首

次工作时不需要,但随后需要)

启动VCO校准,发出IO_UPDATE

Rev. 0 | Page 28 of 84

AD9520-0

O

PTIONAL

REFIN

REFIN

BYPASS

CLK

CLK

PD

SYNC

RESET

EEPROM

REF1

REF2

REGULATOR (LDO)

LF

REF_SEL CPRSET VCPVS GND RSET

REFERENCE

SWITCHOVER

STATUS

STATUS

BUF

AMP

LOW DROPOUT

P, P + 1

PRESCALER

ZERO DELAY BLOCK

DIVIDE BY 1,

2, 3, 4, 5, OR 6

DIGITAL

LOGIC

EEPROM

STATUS

N DIVIDER

0 1

DISTRIBUTION

REFERENCE

CLOCK

DOUBLER

A/B

COUNTERS

REFMON

R

DIVIDER

PROGRAMMABLE

N DELAY

DIVIDE BY

1 TO 32

LOCK

DETECT

R DELAY

PROGRAMMABLE

PHASE

FREQUENCY

DETECTOR

PLL

REFERENCE

CHARGE

HOLD

PUMP

LD

CP

STATUS

VS_DRV

OUT0

OUT0

OUT1

OUT1

OUT2

OUT2

SP1

SP0

SCLK/SCL

SDIO/SDA

SDO

CS

SERIAL

PORT

DECODE

INTERFACE

SPI

INTERFACE

AD9520

I2C

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

图37. 内部VCO和时钟分配(模式0)

OUT3

OUT3

OUT4

OUT4

OUT5

OUT5

OUT6

OUT6

OUT7

OUT7

OUT8

OUT8

OUT9

OUT9

OUT10

OUT10

OUT11

OUT11

LVPECL/CMOS OUTPUT

07213-030

Rev. 0 | Page 29 of 84

AD9520-0

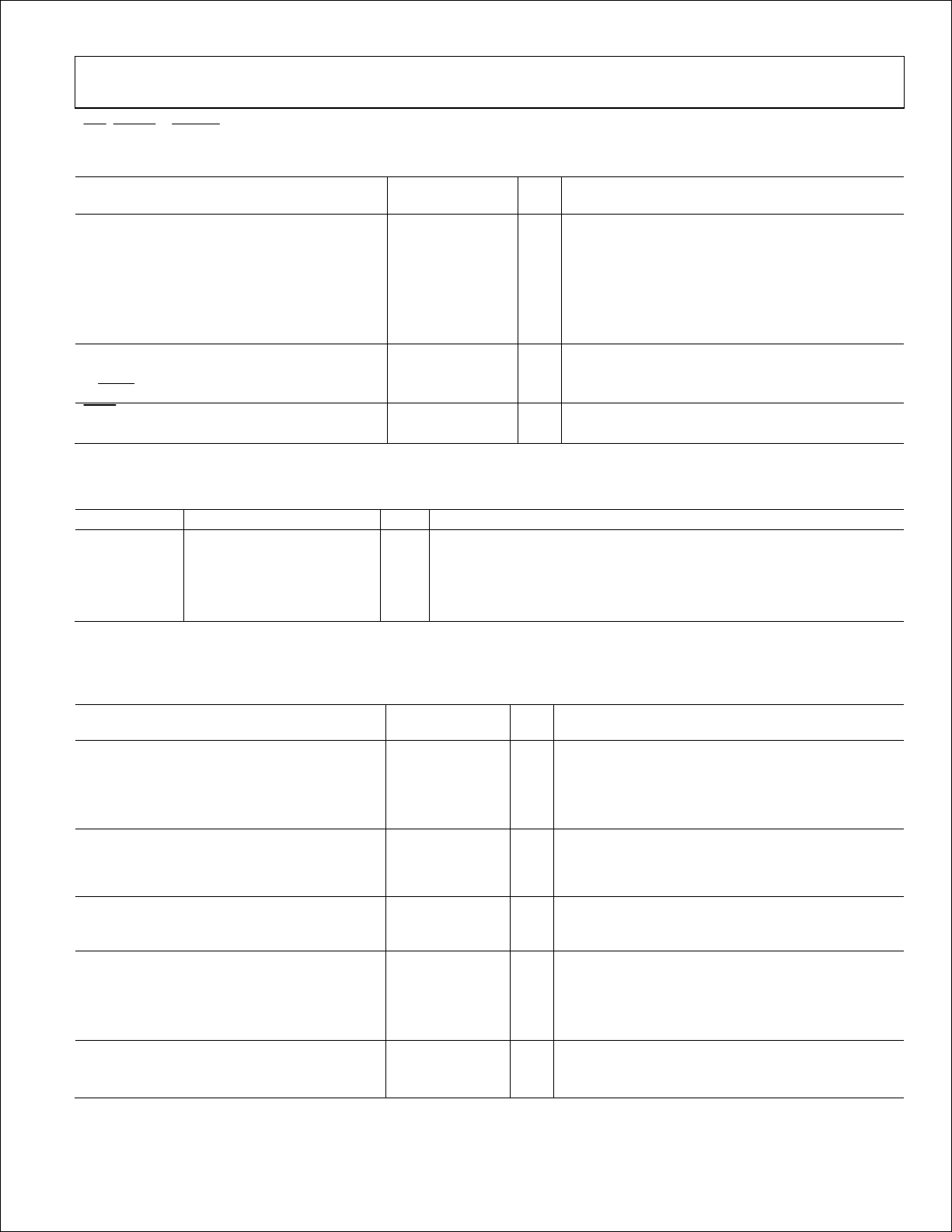

模式1:时钟分配或外部VCO <1600 MHz

当要分配的外部时钟源或外部VCO/VCXO小于1600 MHz

时,可以使用旁路VCO分频器的配置,这是模式2的唯一

不同之处。旁路VCO分频器时,时钟源的频率限制在1600

MHz以下(受限于通道分频器支持的最大输入频率)。

配置和寄存器设置

对于外部时钟小于1600 MHz的时钟分配应用,应使用表23

所示的寄存器设置。

表23. 时钟分配小于1600 MHz的设置

寄存器 描述

0x010[1:0] = 01b PLL异步关断(PLL关)

0x1E1[0] = 1b

0x1E1[1] = 0b 选择CLK作为时钟源

在外部VCO小于1600 MHz的情况下使用内部PLL时,必须

开启PLL。

旁路作为分配部分时钟源的VCO分频器

表24. 在外部VCO小于1600 MHz时使用内部PLL的设置

寄存器 描述

0x1E1[0] = 1b

0x010[1:0] = 00b

外部VCO/VCXO需要外部环路滤波器,必须将该环路滤波

旁路作为分配部分时钟源的VCO分频器

PLL正常工作(PLL开启),

以及0x010至0x01E中的其它适当PLL设置

器连接在CP与VCO/VCXO的调谐引脚之间。该环路滤波

器决定环路带宽和PLL的稳定性。针对所用的

VCO/VCXO,务必选择正确的PFD极性。

表25. 设置PFD极性

寄存器 描述

0x010[7] = 0b

0x010[7] = 1b

PFD正极性(较高的控制电压产生较高的频率)

PFD负极性(较高的控制电压产生较低的频率)

Rev. 0 | Page 30 of 84

AD9520-0

OPTIONAL

REFIN

REFIN

BYPASS

CLK

CLK

PD

SYNC

RESET

EEPROM

REF1

REF2

REGULATOR (LDO)

LF

REF_SEL CPRSET VCPVS GND RSET

REFERENCE

SWITCHOVER

STATUS

STATUS

BUF

AMP

LOW DROPOUT

P, P + 1

PRESCALER

ZERO DELAY BLOCK

DIVIDE BY 1,

2, 3, 4, 5, OR 6

DIGITAL

LOGIC

EEPROM

STATUS

N DIVIDER

0 1

DISTRIBUTION

REFERENCE

CLOCK

DOUBLER

A/B

COUNTERS

REFMON

R

DIVIDER

PROGRAMMABLE

N DELAY

DIVIDE BY

1 TO 32

LOCK

DETECT

R DELAY

PROGRAMMABLE

PHASE

FREQUENCY

DETECTOR

PLL

REFERENCE

CHARGE

HOLD

PUMP

LD

CP

STATUS

VS_DRV

OUT0

OUT0

OUT1

OUT1

OUT2

OUT2

SP1

SP0

SCLK/SCL

SDIO/SDA

SDO

CS

SERIAL

PORT

DECODE

INTERFACE

SPI

INTERFACE

AD9520

I2C

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

图38. 时钟分配或外部VCO <1600 MHz(模式1)

OUT3

OUT3

OUT4

OUT4

OUT5

OUT5

OUT6

OUT6

OUT7

OUT7

OUT8

OUT8

OUT9

OUT9

OUT10

OUT10

OUT11

OUT11

LVPECL/CMOS OUTPUT

07213-031

Rev. 0 | Page 31 of 84

AD9520-0

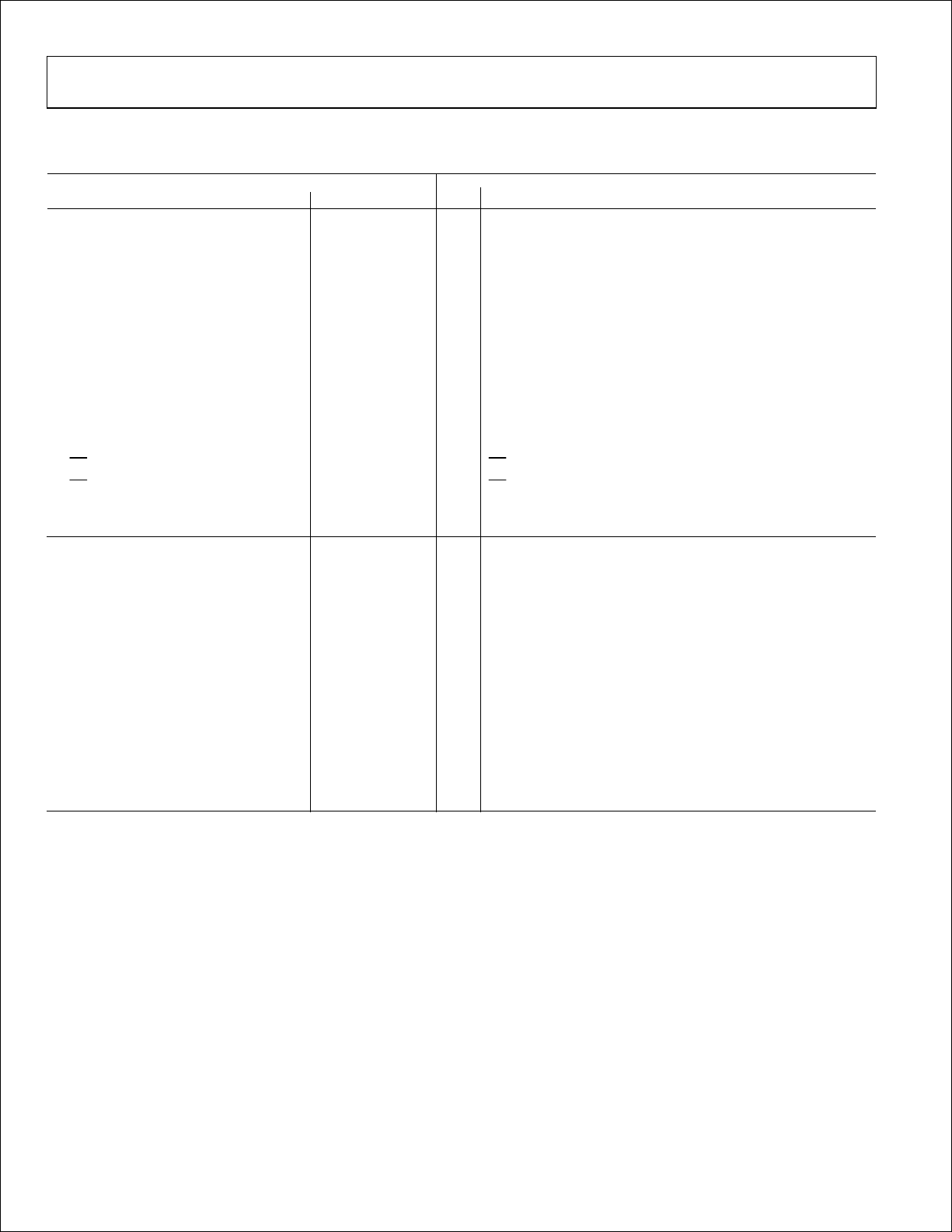

模式2:高频时钟分配—CLK或外部VCO > 1600 MHz

在AD9520的上电默认配置中,PLL关断,CLK/CLK输入通

过VCO分频器(1分频/2分频/3分频/4分频/5分频/6分频)连接

到分配部分。这是一种仅分配模式,支持最高达2400 MHz

的外部输入(见表3)。能够施加于通道分频器的最大频率为

1600 MHz,因此,更高的输入频率必须降频后才能到达通

道分频器。

当PLL使能时,这种连接也支持PLL与频率小于2400 MHz的

外部VCO或VCXO一起使用。该配置不使用内部VCO,因

而将其关断。外部VCO/VCXO直接馈入预分频器。

表26所示的寄存器设置是复位操作后这些寄存器在上电时

的默认值。

表26. 时钟分配模式的默认寄存器设置

寄存器

0x010[1:0] = 01b PLL异步关断(PLL关)

0x1E0[2:0] = 000b 设置VCO分频比 = 2

0x1E1[0] = 0b 设置VCO分频比 = 2

0x1E1[1] = 0b 选择CLK作为时钟源

内部PLL与外部VCO一起使用时,必须开启PLL。

描述

表27. 使用外部VCO时的设置

寄存器

0x010[1:0] = 00b PLL正常工作(PLL开启)

0x010 to 0x01E

描述

PLL设置;选择并使能一路参考输入;

根据目标环路配置设置R、N(P、A、B

PFD极性和ICP

)、

0x1E1[1] = 0b 选择CLK作为时钟源

外部VCO需要外部环路滤波器,必须将该环路滤波器连接

在CP与VCO的调谐引脚之间。该环路滤波器决定环路带宽

和PLL的稳定性。针对所用的VCO,务必选择正确的PFD极

性。

表28. 设置PFD极性

寄存器

0x010[7] = 0b

0x010[7] = 1b

描述

PFD正极性(较高的控制电压产生较高

的频率

)

PFD负极性(较高的控制电压产生较低

的频率)

Rev. 0 | Page 32 of 84

O

AD9520-0

PTIONAL

REFIN

REFIN

BYPASS

CLK

CLK

PD

SYNC

RESET

EEPROM

REF1

REF2

REGULATOR (LDO)

LF

REF_SEL CPRSET VCPVS GND RSET

REFERENCE

SWITCHOVER

STATUS

STATUS

BUF

AMP

LOW DROPOUT

P, P + 1

PRESCALER

ZERO DELAY BLOCK

DIVIDE BY 1,

2, 3, 4, 5, OR 6

DIGITAL

LOGIC

EEPROM

STATUS

N DIVIDER

0 1

DISTRIBUTION

REFERENCE

CLOCK

DOUBLER

A/B

COUNTERS

REFMON

R

DIVIDER

PROGRAMMABLE

N DELAY

DIVIDE BY

1 TO 32

LOCK

DETECT

R DELAY

PROGRAMMABLE

PHASE

FREQUENCY

DETECTOR

PLL

REFERENCE

CHARGE

HOLD

PUMP

LD

CP

STATUS

VS_DRV

OUT0

OUT0

OUT1

OUT1

OUT2

OUT2

SP1

SP0

SCLK/SCL

SDIO/SDA

SDO

CS

SERIAL

PORT

DECODE

INTERFACE

SPI

INTERFACE

AD9520

I2C

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

DIVIDE BY

1 TO 32

图39. 高频时钟分配或外部VCO >1600 MHz(模式2)

OUT3

OUT3

OUT4

OUT4

OUT5

OUT5

OUT6

OUT6

OUT7

OUT7

OUT8

OUT8

OUT9

OUT9

OUT10

OUT10

OUT11

OUT11

LVPECL/CMOS OUTPUT

7213-029

Rev. 0 | Page 33 of 84

AD9520-0

锁相环(PLL)

OPTIONAL

BYPASS

REFIN

REFIN

CLK

CLK

REF1

REF2

REGULATOR (LDO)

LF

REF_SEL CPRSET VCPVS GND RSET

REFERENCE

SWITCHOVER

STATUS

STATUS

BUF

LOW DROPOUT

P, P + 1

PRESCALER

ZERO DELAY BLOCK

DIVIDE BY 1,

2, 3, 4, 5, OR 6

STATUS

N DIVIDER

0 1

DISTRIBUTION

REFERENCE

CLOCK

DOUBLER

A/B

COUNTERS

图40. PLL功能模块

REFMON

R

DIVIDER

PROGRAMMABLE

N DELAY

FROM CHANNEL

DIVIDER 0

LOCK

DETECT

R DELAY

PROGRAMMABLE

PHASE

FREQUENCY

DETECTOR

PLL

REFERENCE

CHARGE

PUMP

HOLD

LD

CP

STATUS

VS_DRV

7213-064

AD9520片内集成PLL和VCO。PLL模块可以结合片内VCO

使用,构成一个完整的锁相环,或者结合外部VCO或

VCXO使用。PLL需要一个外部环路滤波器,它通常由少量

电容和电阻组成。环路滤波器的配置和元件有助于建立工

作PLL的带宽并确保其稳定性。

AD9520 PLL可用于从提供的参考频率产生时钟频率,包括

将参考频率转换为高得多的频率,以便随后进行分频和分

配。此外,PLL可以用来清除高噪声参考的抖动和相位噪

声。PLL参数和环路动态特性的确切选择取决于具体应

用。AD9520 PLL十分灵活且具深度,因而可以定制该器件

以用于许多不同的应用和信号环境。

PLL配置

AD9520 PLL的配置十分灵活,支持各种参考频率、PFD比

较频率、VCO频率、内部或外部VCO/VCXO以及环路动态

特性。上述支持是通过R分频器、N分频器、PFD极性(仅适

用于外部VCO/VCXO)、防反冲脉冲宽度、电荷泵电流、内

部VCO或外部VCO/VCXO的选择以及环路带宽的各种设置

实现的,这些设置通过可编程寄存器设置(见表49和表53)

以及外部环路滤波器的设置进行管理。

成功的PLL运作和满意的PLL环路性能高度依赖于PLL设置

的正确配置,而外部环路滤波器的设计对于PLL的正常工

作至关重要。

TM

ADIsimCLK

是一款免费程序,可帮助设计和探索AD9520

的能力和特性,包括PLL环路滤波器的设计。ADIsimCLK

1.2版中的AD9516模型也可以用于AD9520环路滤波器的建

模,请访问:www.analog.com/clocks。

鉴频鉴相器(PFD)

PFD接受R分频器和N分频器的输入,产生与二者的相位和

频率差成比例的输出。PFD内置一个可编程延迟元件,用

来控制防反冲脉冲的宽度。此脉冲可确保PFD传递函数中

无死区,并使相位噪声和参考杂散最小。防反冲脉冲宽度

由0x017[1:0]设置。

必须注意一项重要的限制条件,即PFD支持的最大频率。

PFD的最大输入频率是防反冲脉冲设置的函数,参见表2中

鉴频鉴相器(PFD)参数的规定。

Rev. 0 | Page 34 of 84

电荷泵(CP)

电荷泵由PFD控制。PFD监控其两路输入之间的相位和频

率关系,并告知电荷泵补充或移除电荷,从而给积分节点

(环路滤波器的一部分)充电或放电。经过积分和滤波的电

荷泵电流转化为电压,通过LF引脚驱动内部VCO的调谐节

点(或外部VCO的调谐引脚),以便提高或降低VCO频率。

电荷泵可以设置(0x010[3:2])为高阻抗模式(支持保持工

作)、正常工作模式(尝试锁定PLL环路)、充电或放电模式

(测试模式)。电荷泵电流可以在标称值600 μA至4.8 mA范围

内分8步设置。电荷泵电流LSB的确切值由标称值为5.1 kΩ

的CPRSET电阻设置。

片内VCO

AD9520片内集成VCO,其涵盖的频率范围如表2所示。实

现了低相位噪声是VCO设计的一个优先目标。

为了在该VCO涵盖的宽频率范围内进行调谐,需使用不同

的范围。这在很大程度上对用户是透明的,但正因如此,

所以在初次设置PLL环路时,必须校准VCO。针对所需的

VCO频率,校准程序确保VCO在正确的频段范围内工作。

更多信息参见“VCO校准”部分。

片内VCO由片内低压差(LDO)线性电压调节器供电。LDO

为VCO提供一定的隔离,使之不受电源电压变化的影响。

BYPASS引脚应通过一个220 nF电容连接到地,确保稳定

®

性。此LDO采用与ADI公司anyCAP

术,对所用电容的类型不敏感。不支持从BYPASS引脚驱动

外部负载。

PLL外部环路滤波器

使用内部VCO时,外部环路滤波器应参考BYPASS引脚,以

实现最佳的噪声和杂散性能。图41显示了一个用于PLL的

外部环路滤波器示例。环路滤波器必须针对所需的每种

PLL配置进行计算。元件值取决于VCO频率、K

率、CP电流、所需的环路带宽以及所需的裕量。环路滤波

器影响相位噪声、环路建立时间和环路稳定性。要了解环

路滤波器设计,关于PLL理论的知识是必不可少的。

ADIsimCLK等工具可以帮助用户根据应用要求计算环路滤

波器。

系列调节器相同的技

、PFD频

VCO

AD9520-0

AD9520

LF

VCO

CHARGE

PUMP

图41. PLL外部环路滤波器示例

CP

BYPASS

C

= 220nF

BP

PLL参考输入

AD9520具有一个灵活的PLL参考输入电路,通过片内保持

放大器支持一路全差分输入、两路独立的单端输入或16.67

MHz/33.33 MHz晶体振荡器。可选的参考时钟倍频器可用

来使PLL参考频率加倍。参考输入的输入频率范围见表2的

规定。差分输入和单端输入均为自偏置,输入信号可以轻

松进行交流耦合。

差分或单端参考必须明确使能。PLL的所有参考输入在默

认情况下均关闭。

差分输入和单端输入共用两个引脚:REFIN(REF1)/REFIN

(REF2)。所需的参考输入类型通过0x01C选择和控制(见表

49和表53)。

选择差分参考输入时,两端的自偏置电平略微偏移,以防

输入缓冲器在参考较慢或丢失时发生震颤。关于该电平的

规定见表2。输入迟滞提高驱动器需要提供的电压摆幅,以

消除偏移的影响。

单端输入可以通过直流耦合CMOS电平信号或交流耦合正

弦波或方波驱动。当单端交流耦合输入信号停止切换时,

为了防止输入缓冲器震颤,用户可以将0x018[7]设置为1b,

这会使直流偏移偏置点降低140 mV。为了提高隔离效果并

降低功耗,各单端输入可以独立关断。

当未选择差分参考输入或者PLL关断时,差分参考输入接

收器关断。当PLL关断或相应的关断寄存器置1时,单端缓

冲器关断。选择差分模式时,单端输入关断。

R2

R1

C1 C2 C3

7213-065

Rev. 0 | Page 35 of 84

AD9520-0

在差分模式下,参考输入引脚内部自偏置,因而能够通过

电容交流耦合。也可以直流耦合到这些。如果以单端信号

驱动差分REFIN,则未使用端(REFIN)应通过适当的电容去

耦到无噪声地。图42给出了REFIN的等效电路。

VS

参考切换有多种可配置的模式。切换可以手动或自动进

行。手动切换通过寄存器0x01C或使用REF_SEL引脚进行。

自动切换发生于REF1消失时。还有一个切换去抖特性,用

于确保PLL不会接收到与新选定的参考远未对齐的上升

沿。

自动参考切换有两种模式(0x01C):

85kΩ

REF1

VS

REFIN

REFIN

REF2

图42. 非XTA L 模式下的REFIN等效电路

10kΩ 12kΩ

150Ω

150Ω

10kΩ 10kΩ

VS

85kΩ

07213-066

晶振模式几乎与差分模式相同。用户通过将Enable XTAL

OSC位置1,并在REFIN/REFIN引脚上放置一个串联谐振AT

基本切割晶体,而使能保持放大器。

参考切换

AD9520不仅支持单路差分参考输入,而且支持双路单端

CMOS输入。在双路单端参考模式下,AD9520支持REF1

(引脚REFIN上)与REF2(引脚REFIN上)之间的自动和手动

PLL参考时钟切换,该特性支持需要冗余参考的网络和其

它应用。

在单端模式下,AD9520具有一个直流偏移选项。当参考输

入交流耦合并且参考时钟消失时,利用该选项可以消除参

考输入震颤的风险。使用参考切换时,单端参考输入应为

直流耦合的CMOS电平(AD9520直流偏移特性禁用)。或

者,这些输入可以交流耦合并且使能直流偏移。然而,用

户应注意,当直流偏移开启时,参考输入的最小输入幅度

更大。

• 优先使用REF1。当REF1消失时,从REF1切换到

REF2; 当REF1重新出现时,从REF2切换回REF1。

• 继续使用REF2。当REF1消失时,自动切换到REF2,

但当REF1重新出现时,不切换回REF1。在适当的时候

可以手动将参考重新设置为REF1。

在自动模式下,REF1由REF2监控。如果REF1消失(REF2上

有连续两个下降沿,而REF1上无边沿跃迁),则认为REF1

丢失。在REF2的下一个上升沿,REF2用作PLL的参考时

钟。如果0x01C[3] = 0b(默认),则当REF1重新出现时(REF1

上有四个上升沿,而在REF1的边沿之间REF2没有两个下降

沿),PLL参考切换回REF1。如果0x01C[3] = 1b,则用户可

以控制何时切换回REF1,这是通过将器件设置为手动参考

选择模式(0x01C[4] = 0b),并且确保寄存器和/或REF_SEL引

脚被设置为选择所需的参考而实现的。再次选择REF1后,

便可再次使能自动模式。

手动切换要求目标参考输入上存在一个时钟,或者去抖特

性禁用(0x01C[7])。

参考分频器R

参考输入被送至参考分频器R。通过写入0x011和0x012,可

以将R(14位计数器)设置为0到16,383的任何值(R = 0和R = 1

时,分频比均为1)。R分频器的输出进入PFD输入之一,以

便与VCO频率经N分频器分频后的结果进行比较。施加于

PFD的频率不得超过最大容许频率,最大容许频率取决于

防反冲脉冲设置(见表2)。

R分频器本身可以复位。利用R、A和B计数器共享的复位

位,可以复位R分频器。它也可以通过SYNC操作复位。

VCO/VCXO反馈分频器N:P、A、B、R

N分频器由一个预分频器(P)和两个计数器(A和 B)组合而

成。总分频器值为:

N = (P × B) + A

其中,P可以为2、4、8、16或32。

Rev. 0 | Page 36 of 84

预分频器

AD9520的预分频器支持两种工作模式:固定分频(FD)模式

(1、2或3)和双模(DM)模式。在双模模式中,预分频器除以

P和(P + 1)(2和3、4和5、8和9、16和17或32和33)。预分频器

的工作模式参见表53 0x016[2:0]。并不是所有频率下都可以

使用所有模式(见表2)。

AD9520在双模模式P/(P + 1)下工作时,输入参考频率与VCO

输出频率的关系如下:

f

= (f

VCO

/R) × (P × B + A) = f

REF

然而,当预分频器在FD模式1、FD模式2或FD模式3下工作

时,A计数器不使用(A = 0),因此上式可以简化为:

f

= (f

VCO

/R) × (P × B) = f

REF

当A = 0时,分频比为固定值:P = 2、4、8、16或32。

通过使用DM和FD模式的组合,AD9520可以实现各种N

值,最小值N = 1。表29显示了10 MHz参考输入如何锁定N

的任意整数倍。

注意,同一N值可以通过不同方式产生,如表中N = 12所

示。用户可以使用P = 2、B = 6的固定分频模式,使用A =

0、B = 6的双模模式2/3,或者使用A = 0、B = 3的双模模式

4/5。

× N/R

REF

× N/R

REF

AD9520-0

A/B计数器的最大输入频率反映在表2规定的预分频器最大

输出频率(~300 MHz)中,这是预分频器输入频率(VCO或

CLK)除以P的结果。例如,如果VCO频率大于2400 MHz,

则不支持双模P = 8/9模式,因为输入A/B计数器的频率太

高。

当AD9520 B计数器旁路(B = 1)时,A计数器应设为0,总分频

值等于预分频器设置P。这种模式下,可能的分频比为1、

2、3、4、8、16和32。这种模式仅在使用VCO/VCXO时才

有用,因为内部VCO的频率范围要求总反馈分频值大于

32。

虽然一般不需要手动复位,但A/B计数器有自己的复位

位。利用R、A和B计数器共享的复位位,也可以复位A和

计数器。注意,这些复位位不会自清0。

R、A和B计数器:SYNC 引脚复位

通过SYNC引脚,可以同时复位R、A和B计数器。此功能由

0x019[7:6]控制(见表53)。SYNC引脚复位默认禁用。

R和N分频器延迟

R和N分频器具有可编程延迟单元,可以使能这些延迟来调

整PLL参考时钟与VCO或CLK之间的相位关系。每个延迟

由三位控制,总延迟范围约为1 ns。参见表53中的0x019。

A和B计数器

B计数器必须≥3或旁路;与R计数器不同,A = 0时,A确实

为0。

表29. 10 MHz参考输入如何锁定N的任意整数倍

f

(MHz) R P A B N f

REF

10 1 1 X

10 1 2 X

10 1 1 X

10 1 1 X

10 1 1 X

10 1 2 X

1

1 1 10 FD P = 1, B = 1(旁路)

1

1 2 20 FD P = 2, B = 1(旁路)

1

3 3 30 FD P = 1, B = 3

1

4 4 40 FD P = 1, B = 4

1

5 5 50 FD P = 1, B = 5

1

3 6 60 FD P = 2, B = 3

(MHz) 模式 注释

VCO

10 1 2 0 3 6 60 DM P和P + 1 = 2和3, A = 0, B = 3

10 1 2 1 3 7 70 DM P和P + 1 = 2和3, A = 1, B = 3

10 1 2 2 3 8 80 DM P和P + 1 = 2和3, A = 2, B = 3

10 1 2 1 4 9 90 DM P和P + 1 = 2和3, A = 1, B = 4

10 1 2 X

1

5 10 100 FD P = 2, B = 5

10 1 2 0 5 10 100 DM P和P + 1 = 2和3, A = 0, B = 5

10 1 2 1 5 11 110 DM P和P + 1 = 2和3, A = 1, B = 5

10 1 2 X

1

6 12 120 FD P = 2, B = 6

10 1 2 0 6 12 120 DM P和P + 1 = 2和3, A = 0, B = 6

10 1 4 0 3 12 120 DM P和P + 1 = 4和5, A = 0, B = 3

10 1 4 1 3 13 130 DM P和P + 1 = 4和5, A = 1, B = 3

1

X = 无关位。

Rev. 0 | Page 37 of 84

AD9520-0

数字锁定检测(DLD)

通过各引脚上的多路复用器选择适当的输出,可以在LD、

STATUS和REFMON引脚上提供DLD功能。当PFD输入端的

上升沿时间差小于规定的值(锁定阈值)时,数字锁定检测

电路指示锁定。当该时间差超过规定的值(解锁阈值)时,

指示失锁。注意,解锁阈值宽于锁定阈值,因而允许相位

误差在一定程度上超过锁定窗口,但锁定指示器不会震颤。

锁定检测窗口时序取决于CPRSET电阻的值和以下三个设

置:数字锁定检测窗口位(0x018[4])、防反冲脉冲宽度位

(0x017[1:0],见表2)和锁定检测计数器(0x018[6:5])。表2中

的锁定和解锁检测值适用于标称值CPRSET = 5.11 kΩ。如果

CPRSET值增加一倍达到10 kΩ,则表2中的值也会加倍。

只有在可编程数量的连续PFD周期内,时间差一直小于锁

定检测阈值,才会指示锁定。此后锁定检测电路将继续指

示锁定,直到后续一个周期内的时间差大于解锁阈值。为

使锁定检测正常工作,PFD频率的周期必须大于解锁阈

值。锁定要求的连续PFD周期数是可编程的(0x018[6:5])。

注意,在某些低环路带宽(<500 Hz)、高相位裕量的情况下,

DLD可能会在获取期间震颤,导致AD9520自动进入和退出

保持模式。为避免发生该问题,建议用户在LD引脚上连接

一个接地电容,以便能够使用电流源数字锁定检测

(CSDLD)模式。

模拟锁定检测(ALD)

AD9520提供模拟锁定检测(ALD)功能,LD引脚可以选择使

用该功能。ALD有两种工作模式:

• N沟道开漏锁定检测。该信号需要通过一个上拉电阻拉

至正电源VS。在较短的趋低脉冲下,输出一般为高电

平。锁定由趋低脉冲的最小占空比指示。

• P沟道开漏锁定检测。该信号需要通过一个下拉电阻拉

至GND。在较短的趋高脉冲下,输出一般为低电平。锁

定由趋高脉冲的最小占空比指示。

模拟锁定检测功能需要一个RC滤波器来提供逻辑电平以指

示锁定/解锁。用户可以利用ADIsimCLK工具来帮助选择用

于ALD的合适无源元件值,以确保该功能正常工作。

VS = 3.3V

AD9520

LD

ALD

图43. 模拟锁定检测滤波器示例,使用N沟

道开漏驱动器

R2

V

R1

OUT

C

07213-067

电流源数字锁定检测(CSDLD)

在PLL锁定序列中,DLD信号一般要切换多次后才会保持

稳定,此时PLL完全锁定并处于稳定状态。某些应用中,

可能希望DLD在PLL完全锁定后才置位。通过使用电流源

锁定检测功能,这是可以实现的。启用该功能的方法如

下:在LD引脚上连接一个接地电容,并选择DLD作为LD引

脚的输出(0x01A[5:0] = 0x00)。

使能LD引脚比较器(0x01D[3] = 1)时,用户可以:

• 将CSDLD与自动切换和保持一起使用。

• 在STATUS和REFMON引脚上查看CSDLD状态。

当DLD为真时,电流源锁定检测提供110 μA的电流;当DLD

为假时,电流源锁定检测短接至地。如果将一个电容连接

到LD引脚,则在DLD为真期间,电容会以电流源所决定的

速率充电;但当DLD为假时,电容几乎立即放电。通过监

控LD引脚的电压(电容顶部),LD只有在DLD为真并保持足

够长的时间后才会变为高电平。任何短暂的DLD假状况都

会使电荷归零。通过选择适当大小的电容,可以将锁定检

测指示延迟到PLL稳定锁定并且锁定检测不震颤时。

电容上的电压可以通过连接到LD引脚的外部比较器检测。

然而,LD引脚内置一个比较器,可以通过REFMON引脚控

制(0x01B[4:0])或STATUS引脚控制(0x017[7:2])作为高电平有

效信号读取。它也可以作为低电平有效信号提供(REFMON

0x01B[4:0]和STATUS, 0x017[7:2])。LD引脚内部比较器的跳

变点和迟滞参见表17。

使用CSDLD时,用户还可以在CSDLD为高电平时异步使能

各时钟输出。要使能该特性,应将CSDLD寄存器(0x0FC和

0x0FD)中的适当使能输出位置1。

Rev. 0 | Page 38 of 84

AD9520

110µA

DLD

LD PIN

COMPARATOR

图44. 电流源数字锁定检测

LD

REFMON

OR

STATUS

V

OUT

C

07213-068

C

C

外部VCXO/VCO时钟输入(CLK/C LK)

该差分输入用于驱动AD9520时钟分配部分,支持最高2.4 GHz

的频率。引脚内部自偏置,输入信号应通过电容交流耦

合。

CLOCK INPUT

VS

LK

LK

2.5kΩ 2.5kΩ

5kΩ

5kΩ

图45. CLK等效输入电路

CLK/CLK输入既可以只用作分配输入(PLL关闭),也可以用

作外部VCO/VCXO的反馈输入(使用内部PLL,不使用内部

VCO)。这些输入也用作外部零延迟模式的反馈路径。

保持

AD9520 PLL具有保持功能。保持是通过将电荷泵置于高阻

态而实现的。当PLL参考时钟丢失时,此功能很有用。在

保持模式下,即使没有参考时钟,VCO也能维持一个相对

恒定的频率。如果没有此功能,电荷泵将被置于持续增强

或减弱状态,导致VCO频率大幅偏移。由于电荷泵被置于

高阻态,因此电荷泵输出或VCO调谐节点的任何泄漏都会

导致VCO频率偏移。这可以通过一个包含大容性元件的环

路滤波器来解决,因为此偏移受限于VCO控制电压的压摆

率(I

/C)引起的漏电流。

LEAK

该器件提供两种保持模式:使用SYNC引脚的手动保持模式

和自动保持模式。无论何种模式,首先必须使能保持功能

(0x01D[0])。

STAGE

07213-032

AD9520-0

外部/手动保持模式

在手动保持模式下,用户可以将SYNC引脚拉低,使电荷泵

进入高阻态。该操作对边沿敏感,而不是对电平敏感。电

荷泵会立即进入高阻态。要使电荷泵脱离高阻态,应将

SYNC引脚拉高。然后,电荷泵在参考时钟的下一个PFD上

升沿的同时离开高阻态。这可以防止外来电荷泵事件在

SYNC变为高电平与下一个PFD事件之间的时间内发生。同

时,这还意味着,如果没有参考时钟,电荷泵将一直处于

高阻态。

B计数器(位于N分频器中)在电荷泵因参考路径PFD事件而

离开高阻态的同时复位,这有助于对齐R和N分频器的边

沿,使PLL更快建立。由于预分频器未复位,因此当B数与

R数接近时,该功能效果最佳,此时环路要消除的相位差

较小。

使用该模式时,应设置通道分频器忽略SYNC引脚(至少在

初始SYNC事件之后)。如果未设置分频器忽略SYNC引脚,

则每次SYNC拉低都会将器件置于保持模式,分配输出关

闭。通道分频器0、1、2、3的忽略同步功能分别通过0x191

[6]、0x194[6]、0x197[6]、0x19A[6]设置。

自动/内部保持模式

如果使能此功能,则当环路失锁时,电荷泵自动进入高阻

态。这里有一个假设,即环路失锁的唯一原因是PLL丢失

参考时钟,因此,保持功能将电荷泵置于高阻态,使VCO

频率尽可能接近参考时钟消失前的原始频率。

图46给出了自动/内部保持功能操作的流程图。

Rev. 0 | Page 39 of 84

AD9520-0

PLL ENABLED

DLD == LOW

YES

WAS

LD PIN == HIGH

WHEN DLD WENT

LOW?

YES

HIGH IMPEDANCE

CHARGE PUMP

YES

REFERENCE

EDGE AT PFD?

YES

NO

NO

LOOP OUT OF LOCK. DIGITAL LOCK

DETECT SIGNAL GOES LOW WHEN THE

LOOP LEAVES LOCK AS DETERMINED

BY THE PHASE DIFFERENCE AT THE

INPUT OF THE PFD.

NO

ANALOG LOCK DETECT PIN INDICATES

LOCK WAS PREVIOUSLY ACHIEVED.

(0x01D[3] = 1; USE LD PIN VOLTAGE

WITH HOLDOVER.

0x01D[3] = 0; IGNORE LD PIN VOLTAGE,

TREAT LD PIN AS ALWAYS HIGH.)

CHARGE PUMP IS MADE

HIGH IMPEDANCE.

PLL COUNTERS CONTINUE

OPERATING NORMALLY.

CHARGE PUMP REMAINS HIGH

IMPEDANCE UNTIL THE REFERENCE

HAS RETURNED.

YES

RELEASE

CHARGE PUMP

HIGH IMPEDANCE

YES

NO

DLD == HIGH

图46. 自动/内部保持模式流程图

保持功能检测LD引脚的逻辑电平,作为进入保持模式的一

个条件。LD的信号可以来自DLD、ALD或电流源LD模式。

可以禁用LD比较器(0x01D[3]),使得保持功能始终检测到

LD为高电平。如果使用DLD,则当PLL重新获取锁定时,

DLD信号可能会震颤。保持功能可能会重新触发,防止保

持模式终止。建议使用电流源锁定检测模式来避免这种情

况(参见“电流源数字锁定检测(CSDLD)”部分)。

TAKE CHARGE PUMP OUT OF

HIGH IMPEDANCE. PLL CAN

NOW RESETTLE.

WAIT FOR DLD TO GO HIGH. THIS TAKES

5 TO 255 CYCLES (PROGRAMMING OF THE DLD

DELAY COUNTER) WITH THE REFERENCE AND

FEEDBACK CLOCKS INSIDE THE LOCK WINDOW AT

THE PFD. THIS ENSURES THAT THE HOLDOVER

FUNCTION WAITS FOR THE PLL TO SETTLE AND LOCK

BEFORE THE HOLDOVER FUNCTION CAN BE

RETRIGGERED.

在保持模式下,只要不存在参考时钟,电荷泵就一直处于

高阻态。

像在外部保持模式下一样,B计数器(位于N分频器中)在电

荷泵因参考路径PFD事件而离开高阻态的同时复位,这有

助于对齐R和N分频器的边沿,使PLL更快建立,并降低建

立期间的频率误差。由于预分频器未复位,因此当B数与R

数接近时,该功能效果最佳,此时环路要消除的相位差较

小。

7213-069

Rev. 0 | Page 40 of 84

AD9520-0

离开保持模式后,环路重新获取锁定,LD引脚必须充电(如

果0x01D[3] = 1),它才能重新进入保持模式(电荷泵高阻态)。

保持功能总是响应当前选定参考的状态(0x01C)。如果环路

在参考切换期间失锁(参见“参考切换”部分),则保持模式会

被短暂触发,直到PFD的下一个参考时钟沿。

下列寄存器会影响自动/内部保持功能:

• 0x018[6:5]—锁定检测计数器。该寄存器改变所需的边沿

在锁定检测窗口内的连续PFD周期数,只有经过该数量

的PFD周期后,DLD指示器才会指示锁定。这会影响LD

引脚开始充电的时间,以及从保持事件结束到保持功能

重新激活的延迟。

• 0x018[3]—禁用数字锁定检测。要使能DLD电路,必须

将此位设为0。如果DLD功能未使能,则内部/自动保持

模式不能正常工作。

• 0x01A[5:0]—锁定检测引脚控制。使用LD引脚比较器

时,该寄存器设为000100b可将锁定检测引脚置于电流源

锁定检测模式。LD引脚应加载一个适当大小的电容。

• 0x01D[3]—LD引脚比较器使能。1 = 使能,0 = 禁用。禁

用时,保持功能始终检测到LD引脚为高电平。

• 0x01D[1]—外部保持控制。

• 0x01D[0]—使能保持并忽略参考频率状态。如果禁用保

持,则外部和自动/内部保持均被禁用。

• 自动参考切换,优先使用REF1。

• 数字锁定检测:5个PFD周期,高范围窗口。

• 使用LD引脚比较器的自动保持。

设置下列寄存器(除一般PLL寄存器以外):

• 0x018[6:5] = 00b;锁定检测计数器 = 5个周期。

• 0x018[4] = 0b;数字锁定检测窗口 = 高范围。

• 0x018[3] = 1b;禁用DLD正常操作。

• 0x01A[5:0] = 000100b;将LD引脚控制设为电流源锁定检

测模式。

• 0x01C[4] = 1b;使能自动切换。

• 0x01C[3] = 0b;优先使用REF1。

• 0x01C[2:1] = 11b;使能REF1和REF2输入缓冲器。

• 0x01D[3] = 1b;使能LD引脚比较器。

• 0x01D[1] = 0b;禁用外部保持模式,使用自动/内部保持

模式。

• 0x01D[0] = 1b;使能保持。

频率状态监控器

AD9520包括三个频率状态监控器,用于指示PLL参考(或单

端模式下的参考)和VCO是否降到阈值频率以下。图47显示

了它们在PLL中的位置。

在下例中,自动保持模式配置如下:

REF_SEL CPRSET VCPVS GND RSET

REFERENCE

SWITCHOVER

REF1

STATUS

STATUS

BUF

OPTIONAL

BYPASS

REFIN

REFIN

CLK

CLK

REF2

REGULATOR (LDO)

LF

LOW DROPOUT

CLOCK

DOUBLER

VCO STATUS

P, P + 1

PRESCALER

N DIVIDER

ZERO DELAY BLOCK

DIVIDE BY 1,

2, 3, 4, 5, OR 6

0 1

PLL参考监控器具有两个阈值频率:正常和扩展(见表17)。

参考频率监控阈值通过0x01F选择。

REFMON

DISTRIBUTION

REFERENCE

R

DIVIDER

A/B

COUNTERS

图47. 参考和VCO状态监控器

PROGRAMMABLE

N DELAY

FROM CHANNEL

DIVIDER 0

LOCK

DETECT

R DELAY

PROGRAMMABLE

PHASE

FREQUENCY

DETECTOR

PLL

REFERENCE

CHARGE

HOLD

PUMP

LD

CP

STATUS

VS_DRV

07213-070

Rev. 0 | Page 41 of 84

AD9520-0

VCO校准

为确保AD9520能在整个工艺和温度范围内正常工作,必须

校准片内VCO。VCO校准由一个采用REFIN分频时钟工作

的校准控制器控制。校准要求正确设置PLL以便锁定PLL环

路,并且REFIN时钟存在。REFIN时钟必须来自AD9520外

部的一个稳定时钟源。

VCO校准方式有两种:上电时自动执行和手动执行。当

EEPROM被设置为自动加载EEPROM中的预编程值时,

VCO校准将自动执行。为使自动校准成功完成,上电时必

须提供一个有效参考。如果没有,用户必须手动校准

VCO。

在AD9520上电或复位后的首次初始化期间,设置0x018[0]

= 1b将启动手动VCO校准序列。这可以作为执行更新寄存

器(0x232[0] = 1b)之前的初始设置的一部分来完成。初始设

置完成后,就会启动VCO校准序列:复位0x018[0] = 0b,执

行一个更新寄存器操作,设置0x018[0] = 1b,再执行一个更

新寄存器操作。一个回读位(0x01F[6])通过返回逻辑真值

(即1b),指示VCO校准已完成。

VCO校准的操作顺序如下:

1. 将PLL寄存器编程为PLL环路所需的正确值。注意,在

VCO校准期间,VCO分频器(0x1E0[2:0])不得被设置为静

态。

2. 在上电或复位后的寄存器初始设置期间,设置0x018[0] =

1b将启动VCO校准。然后,只要需要校准,就应设置

0x018[0] = 0b,更新寄存器,然后设置0x018[0] = 1b,更新

寄存器。

3. 内部启动SYNC操作,使输出进入正常SYNC功能操作决

定的静止状态。

4. VCO校准到请求的VCO频率所需的设置。

5. 内部释放SYNC信号,使输出继续提供时钟。

6. PLL环路闭合。

7. PLL锁定。

VCO校准期间会执行SYNC,因此,AD9520的输出在校准

期间保持静态,防止产生不需要的频率。然而,在VCO校

准结束时,输出可能在PLL环路完全建立之前就恢复提供

时钟。

校准分频器将PFD频率(参考频率除以R)降频至校准时钟。

校准频率等于PFD频率除以校准分频器设置。VCO校准时

钟频率越低,则完成校准所需的时间越长。

VCO校准时钟频率的计算公式如下:

f

CAL_CLOCK

= f

REFIN

/(R × cal_div)

其中:

为REFIN信号的频率。

f

REFIN

R为R计数器的值。

cal_div为VCO校准分频器设置的分频比(0x018[2:1])。

用户应选择适当的校准分频比,使得校准频率小于6.25

MHz。表30给出了适当的校准分频值。

表30. 不同鉴相器频率下的VCO校准分频值

PFD速率(MHz) 推荐的VCO校准分频值

<12 任意