800 MHz Clock Distribution IC, PLL Core,

Preliminary Technical Data

FEATURES

Low phase noise phase-locked loop core

Reference input frequencies to 250 MHz

Programmable dual-modulus prescaler

Programmable charge pump (CP) current

Separate CP supply (VCP) extends tuning range

Two 1.5 GHz, differential clock inputs

8 programmable dividers, 1 to 32, all integers

Phase select for output-to-output coarse delay adjust

4 independent 800 MHz LVPECL outputs

Additive output jitter 225 fs rms

4 independent 800 MHz/250 MHz LVDS/CMOS clock outputs

Additive output jitter 275 fs rms

Fine delay adjust on 2 LVDS/CM OS outputs

4-wire or 3-wire serial control port

Space-saving 64-lead LFCSP

APPLICATIONS

Low jitter, low phase noise clock distribution

Clocking high speed ADCs, DACs, DDS, DDC, DUC, MxFEs

High performance wireless transceivers

High performance instrumentation

Broadband infrastructure

Dividers, Delay Adjust, Eight Outputs

AD9510

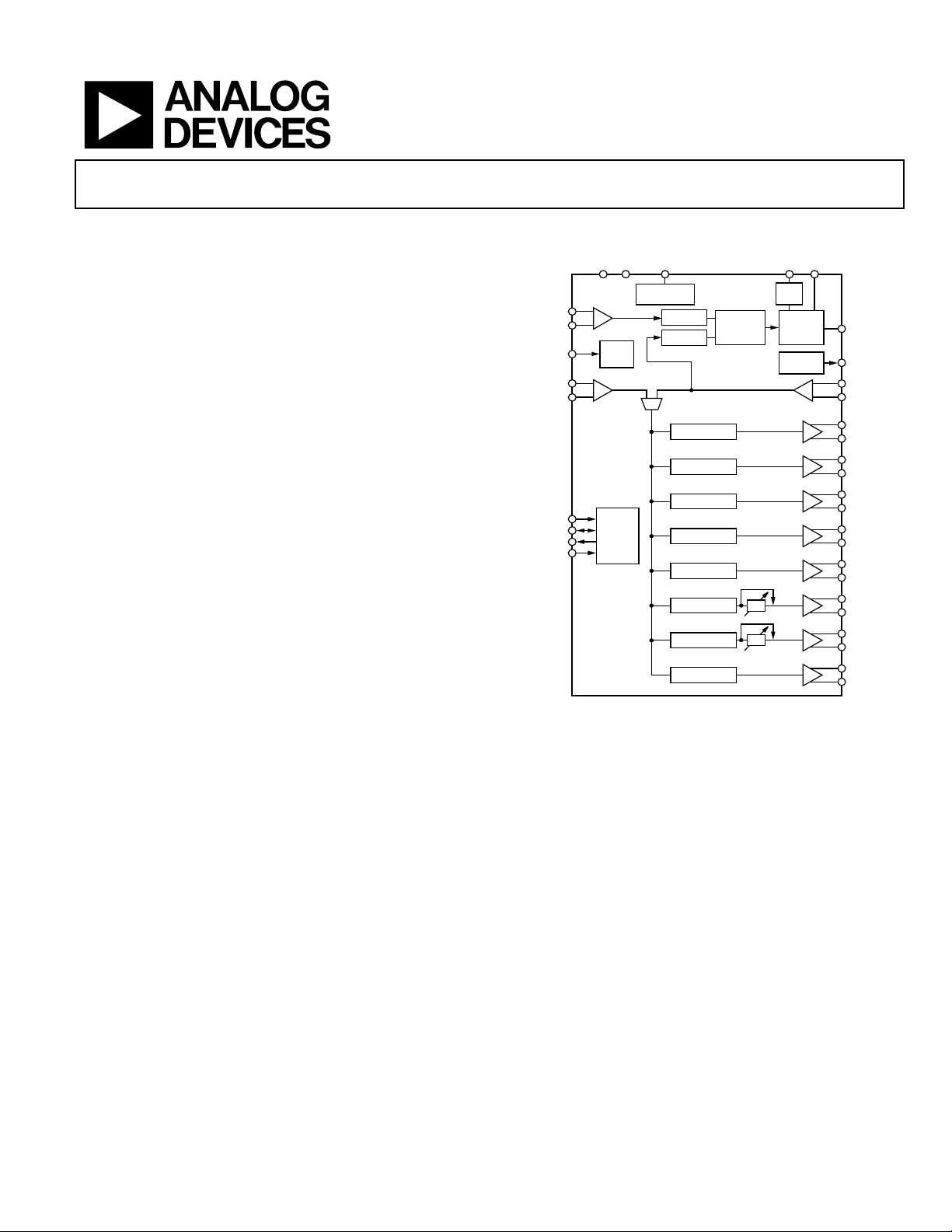

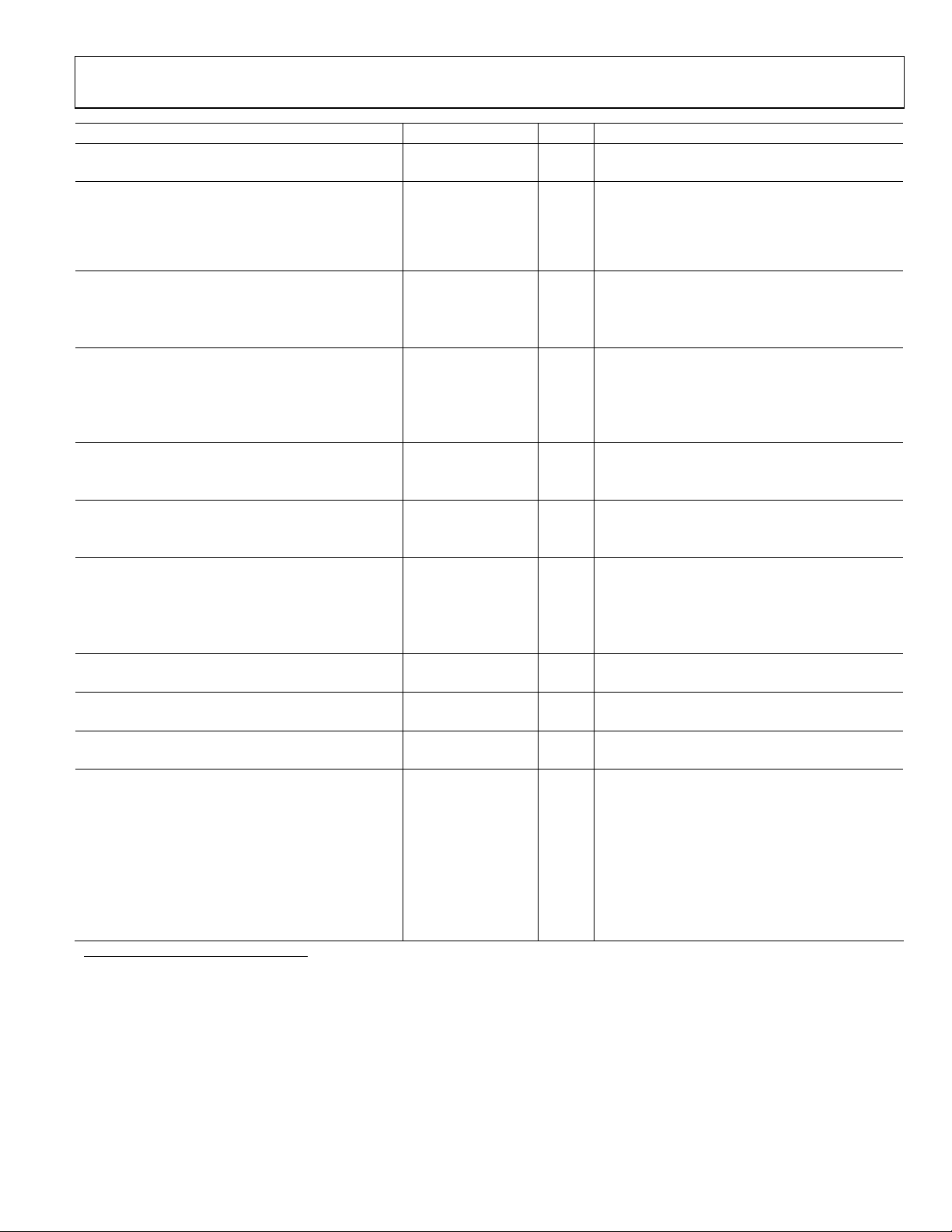

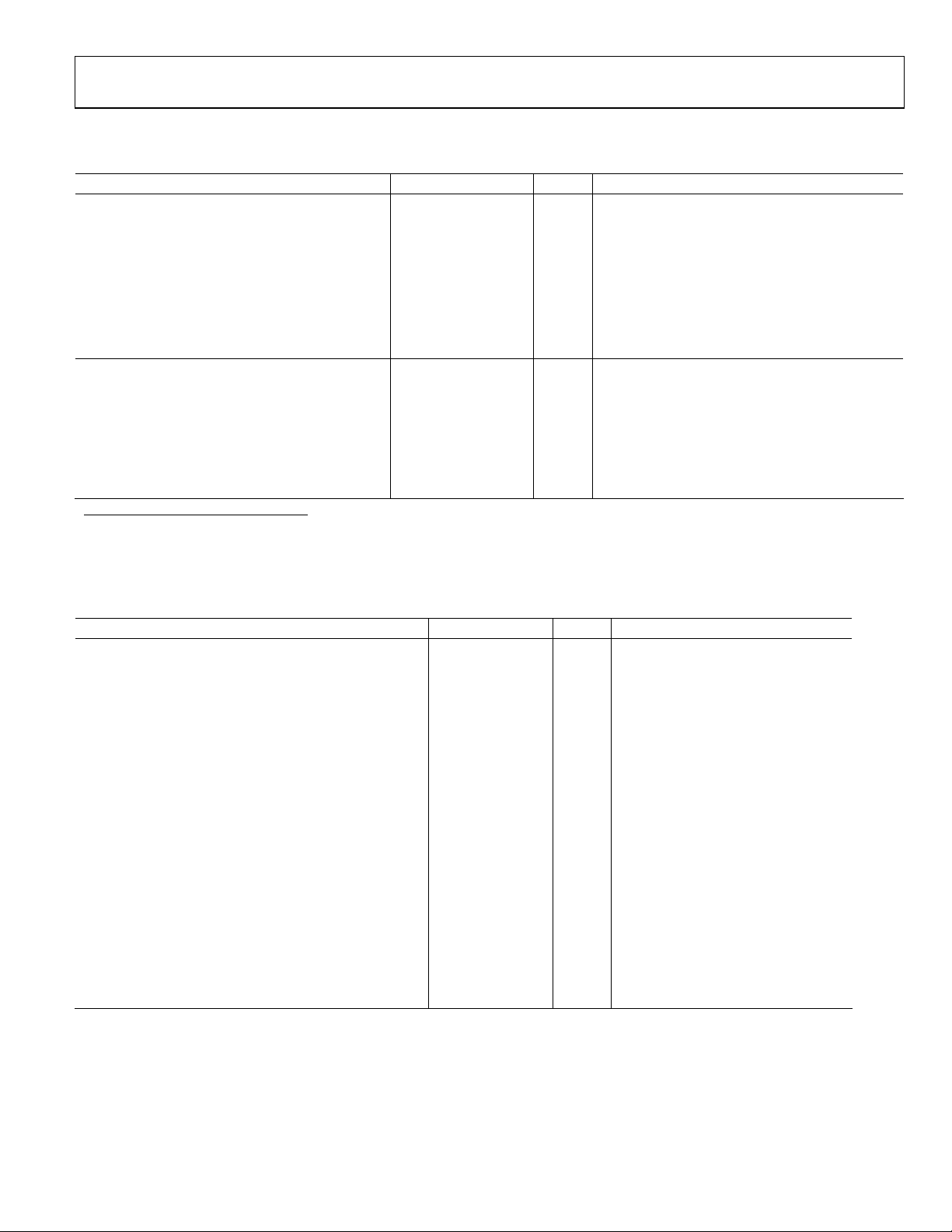

FUNCTIONAL BLOCK DIAGRAM

CPRSET

PLL

REF

CHARGE

PUMP

PLL

SETTINGS

LVPECL

LVPECL

LVPECL

LVPECL

LVDS/CMOS

LVDS/CMOS

∆

T

LVDS/CMOS

∆

T

LVDS/CMOS

CP

STATUS

CLK2

CLK2B

OUT0

OUT0B

OUT1

OUT1B

OUT2

OUT2B

OUT3

OUT3B

OUT4

OUT4B

OUT5

OUT5B

OUT6

OUT6B

OUT7

OUT7B

05046-001

REFIN

REFINB

FUNCTION

CLK1

CLK1B

SCLK

SDIO

SDO

CSB

GNDVS VCP

RSET

SYNCB,

RESETB

PDB

SERIAL

CONTROL

PORT

DISTRIBUTION

REF

R DIVIDER

N DIVIDER

PROGRAMMABLE

AD9510

FREQUENCY

DETECTOR

DIVIDERS AND

PHASE ADJUST

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

/1, /2, /3... /31, /32

PHASE

Figure 1.

GENERAL DESCRIPTION

The AD9510 provides a multi-output clock distribution

function along with an on-chip PLL core. The design

emphasizes low jitter and phase noise in order to maximize data

converter performance. Other applications with demanding

phase noise and jitter requirements also benefit from this part.

The PLL section consists of a programmable reference divider

(R); a low noise phase frequency detector (PFD); a precision

charge pump (CP); and a programmable feedback divider (N).

By connecting an external VCXO or VCO to the CLK2/CLK2B

pins, frequencies up to 1.5 GHz may be synchronized to the

input reference.

There are eight independent clock outputs. Four outputs are

LVPECL, and four are selectable as either LVDS or CMOS

levels. The LVPECL and LVDS outputs operate to 800 MHz,

and the CMOS outputs operate to 250 MHz.

Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

Each output has a programmable divider that may be bypassed

or set to divide by any integer up to 32. The phase of one clock

output relative to another clock output may be varied by means

of a divider phase select function that serves as a coarse timing

adjustment. Two of the LVDS/CMOS outputs also feature

programmable delay elements with full-scale ranges up to 10 ns

of delay. This fine tuning delay block has 5-bit resolution, giving

32 possible delays from which to choose for each full-scale

setting.

The AD9510 is ideally suited for data converter clocking

applications where maximum converter performance is

achieved by encode signals with subpicosecond jitter.

The AD9510 is available in a 64-lead LFCSP and may be

operated from a single 3.3 V supply. An external VCO that

requires an extended voltage range may be accommodated by

connecting the charge pump supply (VCP) to 5.5 V. The

temperature range is −40°C to +85°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

AD9510 Preliminary Technical Data

TABLE OF CONTENTS

Specifications..................................................................................... 4

A and B Counters....................................................................... 24

PLL Characteristics ...................................................................... 4

Clock Inputs.................................................................................. 5

Clock Outputs............................................................................... 6

Timing Characteristics ................................................................ 6

Clock Output Phase Noise .......................................................... 8

Clock Output Additive Time Jitter........................................... 11

PLL and Distribution Phase Noise and Spurious................... 11

Serial Control Port .....................................................................12

Function Pin................................................................................ 12

Status Pin..................................................................................... 13

Power............................................................................................ 13

Timing Diagrams............................................................................ 14

Absolute Maximum Ratings.......................................................... 15

Thermal Characteristics ............................................................15

ESD Caution................................................................................ 15

Determining Values for P, A, B, and R .................................... 24

Phase Frequency Detector (PFD) and Charge Pump............ 25

Antibacklash Pulse..................................................................... 25

STATUS Pin ................................................................................ 25

Loss of Reference........................................................................ 26

FUNCTION Pin......................................................................... 27

Distribution Section................................................................... 27

CLK1 Clock Input...................................................................... 27

Dividers........................................................................................ 27

Delay Block ................................................................................. 32

Outputs........................................................................................ 32

Power-Down Modes .................................................................. 33

Reset Modes ................................................................................ 33

Single-Chip Synchronization.................................................... 34

Multichip Synchronization ....................................................... 34

Pin Configuration and Function Descriptions........................... 16

Terminology ....................................................................................18

Typical Performance Characteristics ...........................................19

Typical Modes of Operation.......................................................... 20

PLL with External VCXO/VCO Followed by Clock

Distribution................................................................................. 20

Clock Distribution Only............................................................ 20

PLL with External VCO and Band-Pass Filter Followed by

Clock Distribution...................................................................... 21

Functional Description.................................................................. 23

Overall.......................................................................................... 23

PLL Section ................................................................................. 23

PLL Reference Input—REFIN.................................................. 23

VCO/VCXO Clock Input—CLK2............................................ 23

PLL Reference Divider—R........................................................ 23

VCO/VCXO Feedback Divider—N (P, A, B) ......................... 23

Serial Control Port ......................................................................... 35

Serial Control Port Pin Descriptions....................................... 35

General Operation of Serial Control Port............................... 35

The Instruction Word (16 Bits)................................................ 36

MSB/LSB First Transfers ........................................................... 36

Register Map and Description...................................................... 39

Summary Table........................................................................... 39

Register Map Description ......................................................... 41

Applications..................................................................................... 48

Using the AD9510 Outputs for ADC Clock Applications.... 48

CMOS Clock Distribution ........................................................ 48

LVPECL Clock Distribution ..................................................... 49

LVDS Clock Distribution.......................................................... 49

Power and Grounding Considerations and Power Supply

Rejection...................................................................................... 50

Outline Dimensions....................................................................... 51

Rev. PrB | Page 2 of 52

Preliminary Technical Data AD9510

Ordering Guide ...........................................................................51

REVISION HISTORY

02/05—Revision PrB: Preliminary Version

Rev. PrB | Page 3 of 52

AD9510 Preliminary Technical Data

SPECIFICATIONS

PLL CHARACTERISTICS

VS = 3.3 V ± 5%; VS ≤ VCP ≤ 5.5 V, TA = 25°C, R

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

REFERENCE INPUTS (REFIN)

Input Frequency 0 250 MHz

Input Sensitivity, Differential --- 200 mV

Input Common-Mode Voltage, VCM --- 1.6 --- V Self-bias voltage of REFINB1.

Input Single-Ended Sensitivity --- VCM ± 100 mV

Input Capacitance 2 pF

Input Resistance --- 5 --- kΩ

PHASE/FREQUENCY DETECTOR (PFD)

Phase Frequency Detector Input Frequency 80 MHz Antibacklash pulse width 0Dh<1:0>= 00b.

Phase Frequency Detector Input Frequency --- MHz Antibacklash pulse width 0Dh<1:0>= 01b.

Phase Frequency Detector Input Frequency --- MHz Antibacklash pulse width 0Dh<1:0>= 10b.

Antibacklash Pulse Width 1.3 ns 0Dh<1:0>= 00b.

Antibacklash Pulse Width 2.9 ns 0Dh<1:0>= 01b.

Antibacklash Pulse Width 6.0 ns 0Dh<1:0>= 10b.

CHARGE PUMP (CP)

ICP Sink/Source Programmable.

High Value 5 mA

Low Value 625 µA

Absolute Accuracy 2.5 % VCP = VS/2.

CPR

Range 2.7/10 kΩ

SET

ICP Three-State Leakage 1 nA

Sink-and-Source Current Matching 2 % 0.5 V < CP < VCP − 0.5 V.

ICP vs. VCP 1.5 % 0.5 V < CP < VCP − 0.5 V.

ICP vs. Temperature 2 % CP = VS/2.

RF CHARACTERISTICS

(CLK2 − PLL FEEDBACK)

Input Frequency 1.5 GHz

Input Sensitivity, Differential --- 200 mV

Input Common-Mode Voltage, VCM 1.6 V Self-biased; enables ac coupling.

Input Single-Ended Sensitivity --- VCM ± 100 mV

Input Capacitance 2 pF

Input Resistance --- 5 --- kΩ

NOISE CHARACTERISTICS

In-Band Noise of the Charge Pump/

Phase Frequency Detector (In-Band

Means Within the LBW of the PLL)

@ 50 kHz PFD Frequency −172 dBc/Hz

@ 2 MHz PFD Frequency −156 dBc/Hz

@ 10 MHz PFD Frequency −149 dBc/Hz

@ 50 MHz PFD Frequency −142 dBc/Hz

= 4.12 kΩ, CPR

SET

= 5.1 kΩ, unless otherwise noted.

SET

When dc-coupled, REFINB capacitively

bypassed to RF ground

CLK2 is electrically identical to CLK1, the

distribution only input (see Clock Inputs)

can be used as differential or single-ended

inputs.

Frequencies > 800 MHz require a minimum

divide-by-2 (see the Distribution Section)

When dc-coupled, CLK2B capacitively

bypassed to RF ground.

The synthesizer phase noise floor is

estimated by measuring the in-band

phase noise at the output of the VCO and

subtracting 20logN (where N is the

N divider value).

1

.

Rev. PrB | Page 4 of 52

Preliminary Technical Data AD9510

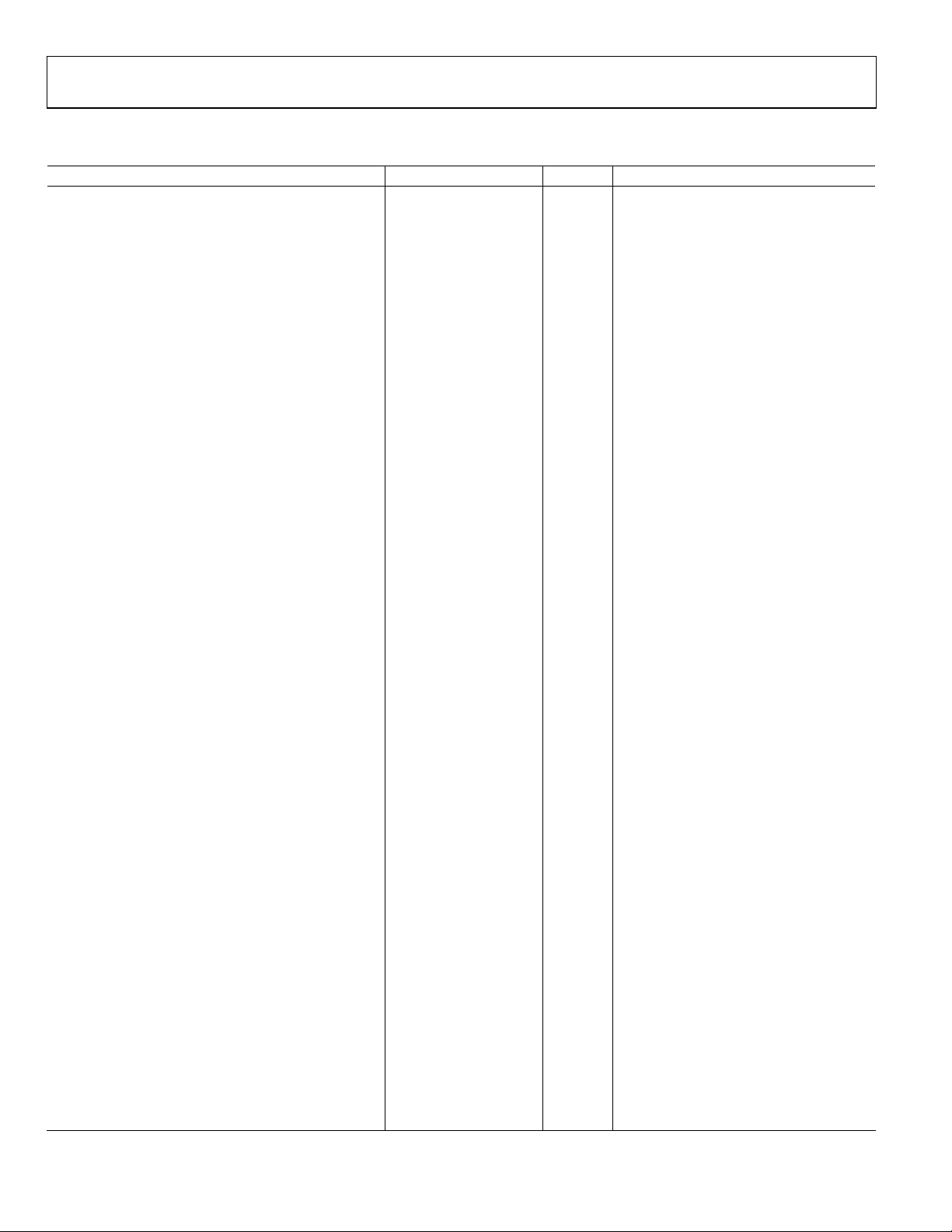

Parameter Min Typ Max Unit Test Conditions/Comments

PLL Figure of Merit

−219 +

10 × log (f

PRESCALER

Prescaler Input Frequency

P = 2 DM (2/3) 500 MHz

P = 4 DM (4/5) 750 MHz

P = 8 DM (8/9) 1500 MHz

P = 16 DM (16/17) 1500 MHz

P = 32 DM (32/33) 1500 MHz

Prescaler Output Frequency 300 MHz

PLL DIGITAL LOCK DETECT WINDOW

Required to Lock (Coincidence of Edges) Selected by Register ODh.

Low Range 3.5 ns <5> = 1.

High Range 9.5 ns <5> = 0.

To Unlock After Lock (Hysteresis) Selected by Register ODh.

Low Range 7 ns <5> = 1.

High Range 15 ns <5> = 0.

REFIN to CLK2 Delay 500 ps

1

REFIN and REFINB self-bias points are offset slightly to avoid chatter on an open input condition.

2

Example: −219 + 10 × log(f

) + 20 × log(N) should give the values for the in-band noise at the VCO output.

PFD

dBc/Hz

)

PFD

Approximation of the PFD/CP phase noise

floor (in the flat region) inside the PLL loop

bandwidth. When running closed loop this

phase noise is gained up by 20 × log(N)

2

.

Signal available at STATUS pin

when selected by 08h<5:2>.

CLOCK INPUTS

Table 2.

Parameter Min Typ Max Unit Test Conditions/Comments

CLOCK INPUTS – CLK1, CLK2

Input Frequency 1.5 GHz

Input Sensitivity, Differential --- 200 mV

Input Common-Mode Voltage , VCM --- 1.6 --- V Self-biased; enables ac coupling

Input Single-Ended Sensitivity --- VCM ± 100 mV

Input Capacitance 2 pF

Input Resistance --- 5 --- kΩ Self-biased

CLK1 and CLK2 are electrically

identical; can be used as differential

or single-ended inputs

Frequencies > 800 MHz require a

minimum divide-by-2, see the

Distribution Section

When dc-coupled, B input capacitively

bypassed to RF ground

Rev. PrB | Page 5 of 52

AD9510 Preliminary Technical Data

CLOCK OUTPUTS

Table 3.

Parameter Min Typ Max Unit Test Conditions/Comments

LVPECL CLOCK OUTPUTS Termination = 50 Ω to VS − 2 V

OUT0, OUT1, OUT2, OUT3; Differential Output level 3Ch (3Dh) (3Eh) (3Fh)<3:2>= 10b

Output Frequency 800 MHz

Output High Voltage (VOH) VS − 1.2 VS − 0.8 V @ dc

Output Low Voltage (VOL) VS − 1.8 VS − 1.6 V @ dc

Output Differential Voltage (VOD) --- 800 --- mV @ dc

Isolation LVPECL-to-LVPECL Output --- dB Typical worst case, desired out to one other out1

Isolation LVDS-to-LVPECL Output --- dB Typical worst case, desired out to one other out 1

Isolation CMOS-to-LVPECL Output --- dB Typical worst case, desired out to one other out1

LVDS CLOCK OUTPUTS Termination = 100 Ω differential; default

OUT4, OUT5, OUT6, OUT7; Differential

Output Frequency 800 MHz

Differential Output Voltage (VOD) --- 350 --- mV

Delta VOD --- 5 --- mV

Output Offset Voltage (VOS) --- 1.25 --- V

Delta VOS --- 5 --- mV

Short-Circuit Current (ISA, ISB) --- 13 --- mA Output shorted to GND

Isolation LVDS to LVDS --- dB Typical worst case, desired out to one other out1

Isolation LVPECL to LVDS --- dB Typical worst case, desired out to one other out1

Isolation CMOS to LVDS --- dB Typical worst case, desired out to one other out1

CMOS CLOCK OUTPUTS B outputs are inverted; termination = open

OUT4, OUT5, OUT6, OUT7; Single Ended

Output Frequency 250 MHz 5 pF load

Output Voltage High (VOH) --- 2.7 V

Output Voltage Low (VOL) 0.4 --- V

Isolation CMOS to CMOS --- dB Typical worst case, desired out to one other out1

Isolation LVPECL to CMOS --- dB Typical worst case, desired out to one other out1

Isolation LVDS to CMOS --- dB Typical worst case, desired out to one other out1

1

Desired output is 100 MHz and 50 MHz on one other output; isolation is level of 50 MHz signal referred to the 100 MHz signal on the desired output. Results shown are

typical worst case of isolation from a single output of indicated type.

Output Level 40h (41h) (42h) (43h)<2:1>= 01b

3.5 mA termination current

TIMING CHARACTERISTICS

Table 4.

Parameter Min Typ Max Unit Test Conditions/Comments

LVPECL

Termination = 50 Ω to V

Output level 3Ch (3Dh) (3Eh) (3Fh)<3:2> = 10b

Output Rise Time, tRP 125 --- ps 20% to 80%

Output Fall Time, tFP 125 --- ps 80% to 20%

PROPAGATION DELAY, t

, CLK1-to-LVPECL OUT

PECL

Divide = Bypass --- 480 --- ps

Divide = 2 − 32 --- 535 --- ps

PROPAGATION DELAY, t

, CLK2-to-LVPECL OUT

PECL

Divide = Bypass --- --- --- ps

Divide = 2 − 32 --- --- --- ps

OUTPUT SKEW, LVPECL OUTPUTS

OUT0 to OUT1 on Same Part, t

OUT0 to OUT1 Across Different Parts, t

--- −35 --- ps LVPECL to LVPECL on same part1

SKP

--- ps LVPECL to LVPECL on different parts2

SKP_AB

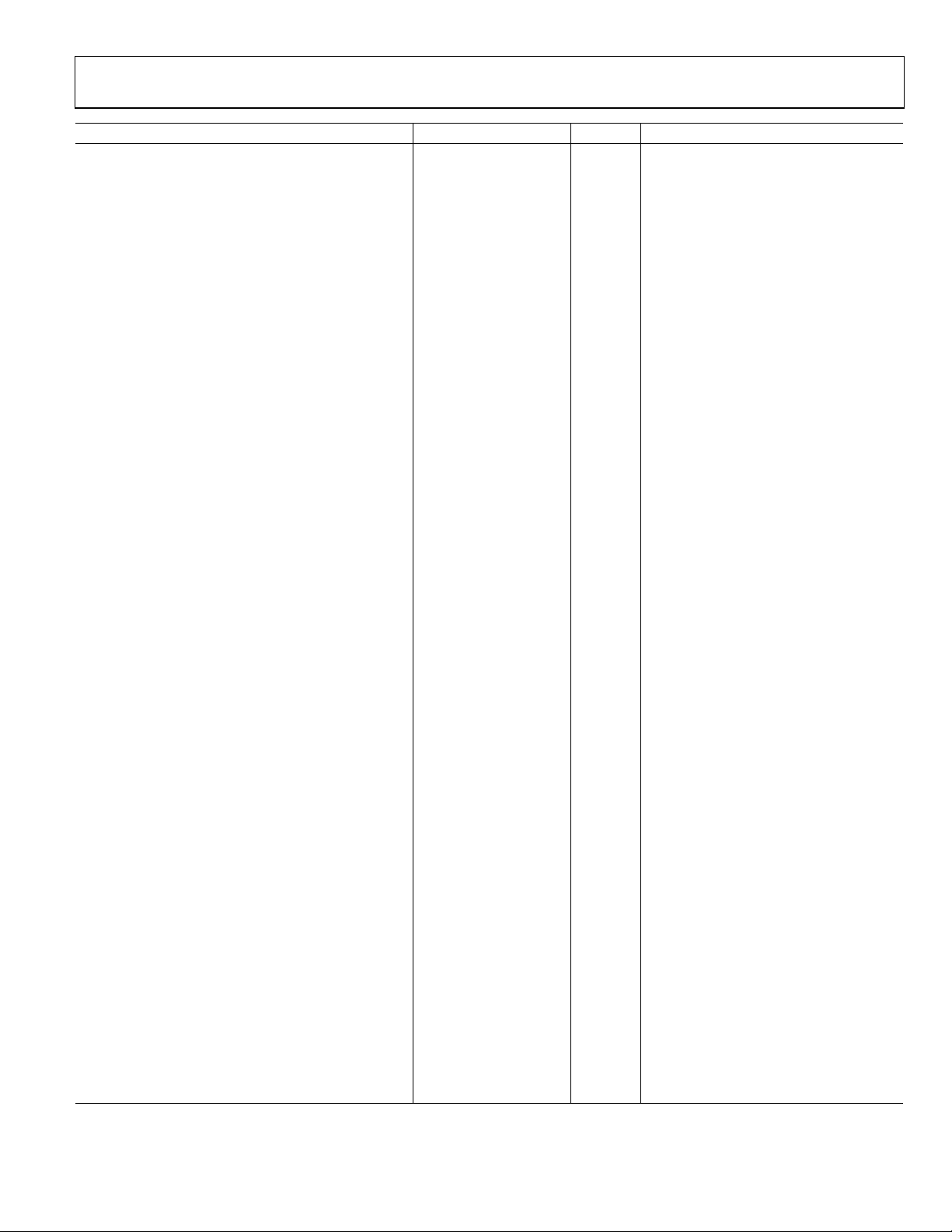

Rev. PrB | Page 6 of 52

− 2 V

S

Preliminary Technical Data AD9510

Parameter Min Typ Max Unit Test Conditions/Comments

OUT2, OUT3 on Same Part, t

OUT2, OUT3 Across Different Parts, t

LVDS

Output Rise Time, tRL 210 --- ps 20% to 80%

Output Fall Time, tFL 215 --- ps 80% to 20%

PROPAGATION DELAY, t

LVDS

OUT4, OUT5, OUT6, OUT7

Divide = Bypass --- 1.30 --- ns

Divide = 2 − 32 --- 1.35 --- ns

OUTPUT SKEW, LVDS Outputs

OUT4 to OUT7 on Same Part, t

OUT4 to OUT7 Across Different Parts, t

OUT5 to OUT6 on Same Part, t

OUT5 to OUT6 Across Different Parts, t

CMOS B outputs are inverted; termination = open

Output Rise Time, tRC 460 --- ps 20% to 80%; C

Output Fall Time, tFC 450 --- ps 80% to 20%; C

PROPAGATION DELAY, t

CMOS

Divide = Bypass --- 1.20 --- ns

Divide = 2 − 32 --- 1.41 --- ns

OUTPUT SKEW, CMOS OUTPUTS

OUT4 to OUT7 on Same Part, t

OUT4 to OUT7 Across Different Parts, t

OUT5 to OUT6 on Same Part, t

OUT5 to OUT6 Across Different Parts, t

LVPECL-TO-LVDS OUT Everything the same; different logic

Output Skew, t

--- 0.90 --- ns LVPECL to LVDS on same part

SKP_V

LVPECL-TO-CMOS OUT Everything the same; different logic

Output Skew, t

--- 0.95 --- ns LVPECL to CMOS on same part

SKP_C

LVDS-TO-CMOS OUT Everything the same; different logic

Output Skew, t

--- 100 --- ps LVDS to CMOS on same part

SKV_C

DELAY ADJUST OUT5 (OUT6); LVDS and CMOS

Shortest Delay Range3 35h (39h) <5:1> 11111b

Zero Scale --- 0.3 --- ns 36h (3Ah) <5:1> 00000b

Full Scale 1.0 ns 36h (3Ah) <5:1> 11111b

Linearity --- % LSB

Longest Delay Range3 35h (39h) <5:1> 00000b

Zero Scale --- 0.5 --- ns 36h (3Ah) <5:1> 00000b

Full Scale 10 ns 36h (3Ah) <5:1> 11111b

Linearity --- % LSB

1

Defined as the worst-case difference between any two similar delay paths within a single device operating at the same voltage and temperature.

2

Defined as the absolute worst-case difference between any two delay paths on any two devices operating at the same voltage and temperature. Part-to-part skew is

the total skew difference; pin-to-pin skew + part-to-part skew.

3

Incremental delay. Does not include propagation delay.

--- 45 --- ps LVPECL to LVPECL on same part1

SKP

--- ps LVPECL to LVPECL on different parts2

SKP_AB

Termination = 100 Ω differential

Output level 40h (41h) (42h) (43h)<2:1> = 01b

3.5 mA termination current

, CLK-TO-LVDS OUT Delay Off—OUT5, OUT6

--- 90 --- ps LVDS to LVDS on same part1

SKV

--- ps LVDS to LVDS on different parts2

SKV_AB

--- −15 --- ps LVDS to LVDS on same part1 delay off

SKVD

--- ps LVDS to LVDS on different parts2 delay off

SKVD_AB

= 3 pF

LOAD

= 3 pF

LOAD

, CLK-TO-CMOS OUT Delay off on OUT5, OUT6

--- --- --- ps CMOS to CMOS on same part1

SKC

--- ps CMOS to CMOS on different parts2

SKC_AB

--- --- --- ps CMOS to CMOS on same part1 delay off

SKCD

--- ps CMOS to CMOS on different parts2 delay off

SKCD_AB

Rev. PrB | Page 7 of 52

AD9510 Preliminary Technical Data

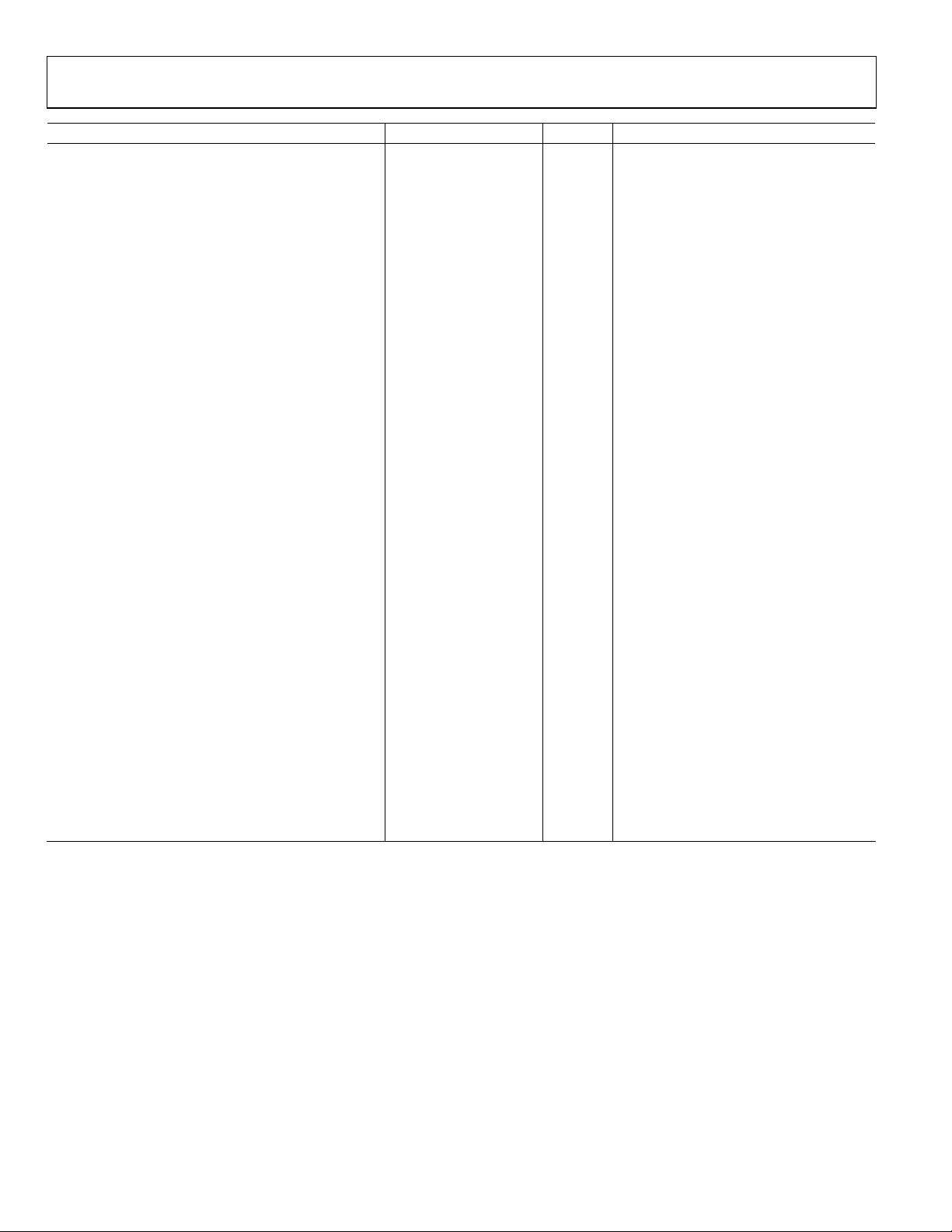

CLOCK OUTPUT PHASE NOISE

Table 5.

Parameter Min Typ Max Unit Test Conditions/Comments

CLK1-TO-LVPECL ADDITIVE PHASE NOISE

CLK1 = 622.08 MHz, OUTN = 622.08 MHz Input slew rate > 1 V/ns

Divide Ratio = 1

@ 10 Hz Offset −125 dBc/Hz

@ 100 Hz Offset −132 dBc/Hz

@ 1 kHz Offset −140 dBc/Hz

@ 10 kHz Offset −148 dBc/Hz

@ 100 kHz Offset −153 dBc/Hz

>1 MHz Offset −154 dBc/Hz

CLK1 = 622.08 MHz, OUTN = 155.52 MHz

Divide Ratio = 4

@ 10 Hz Offset −130 dBc/Hz

@ 100 Hz Offset −140 dBc/Hz

@ 1 kHz Offset −148 dBc/Hz

@ 10 kHz Offset −155 dBc/Hz

@ 100 kHz Offset −161 dBc/Hz

>1 MHz Offset −161 dBc/Hz

CLK1 = 622.08 MHz, OUTN = 38.88 MHz

Divide Ratio = 16

@ 10 Hz Offset −145 dBc/Hz

@ 100 Hz Offset −152 dBc/Hz

@ 1 kHz Offset −161 dBc/Hz

@ 10 kHz Offset −165 dBc/Hz

@ 100 kHz Offset −165 dBc/Hz

>1 MHz Offset −166 dBc/Hz

CLK1 = 491.52 MHz, OUTN = 61.44 MHz

Divide Ratio = 8

@ 10 Hz Offset −131 dBc/Hz

@ 100 Hz Offset −142 dBc/Hz

@ 1 kHz Offset −153 dBc/Hz

@ 10 kHz Offset −160 dBc/Hz

@ 100 kHz Offset −165 dBc/Hz

> 1 MHz Offset −165 dBc/Hz

CLK1 = 491.52 MHz, OUTN = 245.76 MHz

Divide Ratio = 2

@ 10 Hz Offset −127 dBc/Hz

@ 100 Hz Offset −136 dBc/Hz

@ 1 kHz Offset −144 dBc/Hz

@ 10 kHz Offset −153 dBc/Hz

@ 100 kHz Offset −157 dBc/Hz

>1 MHz Offset −158 dBc/Hz

CLK1 = 245.76 MHz, OUTN = 61.44 MHz

Divide Ratio = 4

@ 10 Hz Offset −140 dBc/Hz

@ 100 Hz Offset −144 dBc/Hz

@ 1 kHz Offset −154 dBc/Hz

@ 10 kHz Offset −163 dBc/Hz

@ 100 kHz Offset −164 dBc/Hz

>1 MHz Offset −165 dBc/Hz

Distribution Section only; does not

include PLL or external VCO/VCXO

Rev. PrB | Page 8 of 52

Preliminary Technical Data AD9510

Parameter Min Typ Max Unit Test Conditions/Comments

CLK1-TO-LVDS ADDITIVE PHASE NOISE

CLK1 = 622.08 MHz, OUTN = 622.08 MHz

Divide Ratio = 1

@ 10 Hz Offset --- dBc/Hz

@ 100 Hz Offset --- dBc/Hz

@ 1 kHz Offset --- dBc/Hz

@ 10 kHz Offset --- dBc/Hz

@ 100 kHz Offset --- dBc/Hz

>1 MHz Offset --- dBc/Hz

CLK1 = 622.08 MHz, OUTN = 155.52 MHz

Divide Ratio = 4

@ 10 Hz Offset --- dBc/Hz

@ 100 Hz Offset --- dBc/Hz

@ 1 kHz Offset --- dBc/Hz

@ 10 kHz Offset --- dBc/Hz

@ 100 kHz Offset --- dBc/Hz

>1 MHz Offset --- dBc/Hz

CLK1 = 622.08 MHz, OUTN = 38.88 MHz

Divide Ratio = 16

@ 10 Hz Offset --- dBc/Hz

@ 100 Hz Offset --- dBc/Hz

@ 1 kHz Offset --- dBc/Hz

@ 10 kHz Offset --- dBc/Hz

@ 100 kHz Offset --- dBc/Hz

>1 MHz Offset --- dBc/Hz

CLK1 = 491.52 MHz, OUTN = 61.44 MHz

Divide Ratio = 8

@ 10 Hz Offset --- dBc/Hz

@ 100 Hz Offset --- dBc/Hz

@ 1 kHz Offset --- dBc/Hz

@ 10 kHz Offset --- dBc/Hz

@ 100 kHz Offset --- dBc/Hz

> 1 MHz Offset --- dBc/Hz

CLK1 = 491.52 MHz, OUTN = 245.76 MHz

Divide Ratio = 2

@ 10 Hz Offset --- dBc/Hz

@ 100 Hz Offset --- dBc/Hz

@ 1 kHz Offset --- dBc/Hz

@ 10 kHz Offset --- dBc/Hz

@ 100 kHz Offset --- dBc/Hz

>1 MHz Offset --- dBc/Hz

CLK1 = 245.76 MHz, OUTN = 61.44 MHz

Divide Ratio = 4

@ 10 Hz Offset --- dBc/Hz

@ 100 Hz Offset --- dBc/Hz

@ 1 kHz Offset --- dBc/Hz

@ 10 kHz Offset --- dBc/Hz

@ 100 kHz Offset --- dBc/Hz

>1 MHz Offset --- dBc/Hz

Distribution Section only; does not

include PLL or external VCO/VCXO

characterization ongoing

Rev. PrB | Page 9 of 52

AD9510 Preliminary Technical Data

Parameter Min Typ Max Unit Test Conditions/Comments

CLK1-TO-CMOS ADDITIVE PHASE NOISE

CLK1 = 245.76 MHz, OUTN = 245.76 MHz

Divide Ratio = 1

@ 10 Hz Offset −117 dBc/Hz

@ 100 Hz Offset −124 dBc/Hz

@ 1 kHz Offset −131 dBc/Hz

@ 10 kHz Offset −141 dBc/Hz

@ 100 kHz Offset −146 dBc/Hz

@ 1 MHz Offset −150 dBc/Hz

> 10 MHz Offset −156 dBc/Hz

CLK1 = 245.76 MHz, OUTN = 61.44 MHz

Divide Ratio = 4

@ 10 Hz Offset −128 dBc/Hz

@ 100 Hz Offset −136 dBc/Hz

@ 1 kHz Offset −144 dBc/Hz

@ 10 kHz Offset −152 dBc/Hz

@ 100 kHz Offset −158 dBc/Hz

@ 1 MHz Offset −160 dBc/Hz

>10 MHz Offset −162 dBc/Hz

CLK1 = 78.6432 MHz, OUTN = 78.6432 MHz

Divide Ratio = 1

@ 10 Hz Offset −127 dBc/Hz

@ 100 Hz Offset −135 dBc/Hz

@ 1 kHz Offset −142 dBc/Hz

@ 10 kHz Offset −151 dBc/Hz

@ 100 kHz Offset −156 dBc/Hz

@ 1 MHz Offset −158 dBc/Hz

>10 MHz Offset −160 dBc/Hz

CLK1 = 78.6432 MHz, OUTN = 39.3216 MHz

Divide Ratio = 2

@ 10 Hz Offset −134 dBc/Hz

@ 100 Hz Offset −140 dBc/Hz

@ 1 kHz Offset −148 dBc/Hz

@ 10 kHz Offset −156 dBc/Hz

@ 100 kHz Offset −161 dBc/Hz

> 1 MHz Offset −162 dBc/Hz

Distribution Section only; does not

include PLL or external VCO/VCXO

Rev. PrB | Page 10 of 52

Preliminary Technical Data AD9510

CLOCK OUTPUT ADDITIVE TIME JITTER

Table 6.

Parameter Min Typ Max Unit Test Conditions/Comments

LVPECL OUTPUT ADDITIVE TIME JITTER

CLK1 = 622.08 MHz, OUT0:3 = 622.08 MHz 40 fs rms BW = 12 kHz − 20 MHz

Divide Ratio = 1 (OC-12)

CLK1 = 622.08 MHz, OUT0:3 = 155.52 MHz 55 fs rms BW = 12 kHz − 20 MHz

Divide Ratio = 4 (OC-3)

CLK1 = 200 MHz, OUT0:3 = 100 MHz 225 fs rms

Divide Ratio = 2

LVDS OUTPUT ADDITIVE TIME JITTER

CLK1 = 200 MHz, OUT4 = 100 MHz 275 fs rms

CMOS OUTPUT ADDITIVE TIME JITTER

CLK1 = 200 MHz, OUT4 = 100 MHz 275 fs rms

1

Distribution Section only; does not include PLL or external VCO/VCXO.

1

Distribution Section only;

does not include PLL or external VCO/VCXO

Calculated from SNR of ADC method;

FC = 100 MHz with AIN = 170 MHz

Distribution Section only;

does not include PLL or external VCO/VCXO

Calculated from SNR of ADC method;

= 100 MHz with AIN = 170 MHz

F

C

Distribution Section only;

does not include PLL or external VCO/VCXO

Calculated from SNR of ADC method;

= 100 MHz with AIN = 170 MHz

F

C

PLL AND DISTRIBUTION PHASE NOISE AND SPURIOUS

Table 7.

Parameter Min Typ Max Unit Test Conditions/Comments

PHASE NOISE AND SPURIOUS

Setup No.1

245.76 MHz VCXO, F

= 1.2288 MHz; R = 25, N = 200

PFD

245.76 MHz Output Divide by 1

Phase Noise @100 kHz Offset --- dBc/Hz

Spurious --- dBc First and second harmonics of F

61.44 MHz Output Divide by 4

Phase Noise @100 kHz Offset --- dBc/Hz

Spurious --- dBc First and second harmonics of F

Setup No. 2

245.76 MHz VCXO, F

= 30.72 MHz; R = 1, N = 8

PFD

245.76 MHz Output Divide by 1

Phase Noise @100 kHz Offset --- dBc/Hz

Spurious --- dBc First and second harmonics of F

61.44 MHz Output Divide by 4

Phase Noise @100 kHz Offset --- dBc/Hz

Spurious --- dBc First and second harmonics of F

Depends on VCO/VCXO selection.

Characterization ongoing.

Measured at LVPECL clock outputs;

ABP = 6 ns; I

= 5 mA; Ref = 30.72 MHz

CP

Measured at LVPECL clock outputs;

ABP = 6 ns; I

= 5 mA; Ref = 30.72 MHz

CP

PFD

PFD

PFD

PFD

Rev. PrB | Page 11 of 52

AD9510 Preliminary Technical Data

SERIAL CONTROL PORT

Table 8.

Parameter Min Typ Max Unit Test Conditions/Comments

CSB, SCLK (INPUTS)

Input Logic 1 Voltage --- V

Input Logic 0 Voltage --- V

Input Logic 1 Current --- µA

Input Logic 0 Current --- µA

Input Capacitance --- pF

SDIO (WHEN INPUT)

Input Logic 1 Voltage --- V

Input Logic 0 Voltage --- V

Input Logic 1 Current --- µA

Input Logic 0 Current --- µA

Input Capacitance --- pF

SDIO, SDO (OUTPUTS)

Output Logic 1 Voltage --- V

Output Logic 0 Voltage --- V

TIMING

Clock Rate (SCLK, 1/t

Pulse-Width High, t

Pulse-Width Low, t

SDIO and CSB to SCLK Setup, tDS --- ns

SCLK to SDIO Hold, tDH --- ns

SCLK to Valid SDIO and SDO, tDV --- ns

) 25 MHz

SCLK

16 24 ns

PWH

16 24 ns

PWL

CSB and SCLK have 30 kΩ

internal pull-down resistors

FUNCTION PIN

Table 9.

Parameter Min Typ Max Unit Test Conditions/Comments

INPUT CHARACTERISTICS

Logic 1 Voltage --- V

Logic 0 Voltage --- V

Logic 1 Current --- µA

Logic 0 Current --- µA

Capacitance --- pF

RESET TIMING

Pulse-Width Low --- ns

SYNC TIMING

Pulse-Width Low 1.5 Clock cycles

Setup Time --- ps

Hold Time --- ps

Sync single chip; CLK1 or CL2,

whichever is being used for distribution

Sync multichip; Write CLK1 or CLK2,

whichever is being used for distribution

Sync multichip; Write CLK1 or CLK2,

whichever is being used for distribution

Rev. PrB | Page 12 of 52

Preliminary Technical Data AD9510

STATUS PIN

Table 10.

Parameter Min Typ Max Unit Test Conditions/Comments

OUTPUT CHARACTERISTICS

Output Voltage High (VOH) --- mV

Output Voltage Low (VOL) --- mV

MAXIMUM TOGGLE RATE 100 MHz

ANALOG LOCK DETECT

Capacitance 3 pF

POWER

Table 11.

Parameter Min Typ Max Unit Test Conditions/Comments

POWER-UP DEFAULT MODE POWER DISSIPATION 650 --- mW

MAXIMUM POWER DISSIPATION 1050 --- mW

Full Sleep Power-Down --- ---

Power-Down (PDB) --- ---

POWER DELTA

CLK1, CLK2 Power-Down --- --- mW

Divider, DIV 2 − 32 to Bypass --- --- mW

LVPECL Output Power-Down

Safe Power-Down (PD2) 56 --- mW

Total Power-Down (PD3) 58 --- mW PD3 mode; use only with no load resistors connected.

LVDS Output Power-Down 33 46 mW

CMOS Output Power-Down 24 38 mW

Delay Block Bypass --- --- mW

Delay Block Power-Down --- --- mW Versus delay block bypass.

PLL Section Power-Down 40 --- mW Versus PLL in loop with … (conditions)

Applies when PLL mux is set to any divider or counter output,

or PFD up/down pulse. Also applies in analog lock detect mode.

Usually debug mode only. Beware that spurs may couple

to output when this pin is toggling.

On-chip capacitance; used to calculate RC time

constant for analog lock detect readback. Use pull-up resistor.

Power-up default state; does not

include power dissipated in output

load resistors.

All functions enabled, all outputs on

and terminated, maximum clock rates,

and frequencies. Does not include

power dissipated in load resistors.

(Pick these conditions.)

Maximum sleep is entered by setting 0Ah<1:0> = 01b

and 58h<4>= 1b. This powers off the PLL BG and the

distribution BG references. Does not include power

dissipated in terminations.

Set FUNCTION pin for PDB operation by setting

58h<6:5> = 11b. Pull PDB low. Does not include

power dissipated in terminations.

PD2 mode (safe) power-down is required

when load resistors are connected. Delta

does not include dissipation in load resistors.

Versus delay block operation at 10 ns fs

with maximum delay; output clocking at 25 MHz.

Rev. PrB | Page 13 of 52

AD9510 Preliminary Technical Data

C

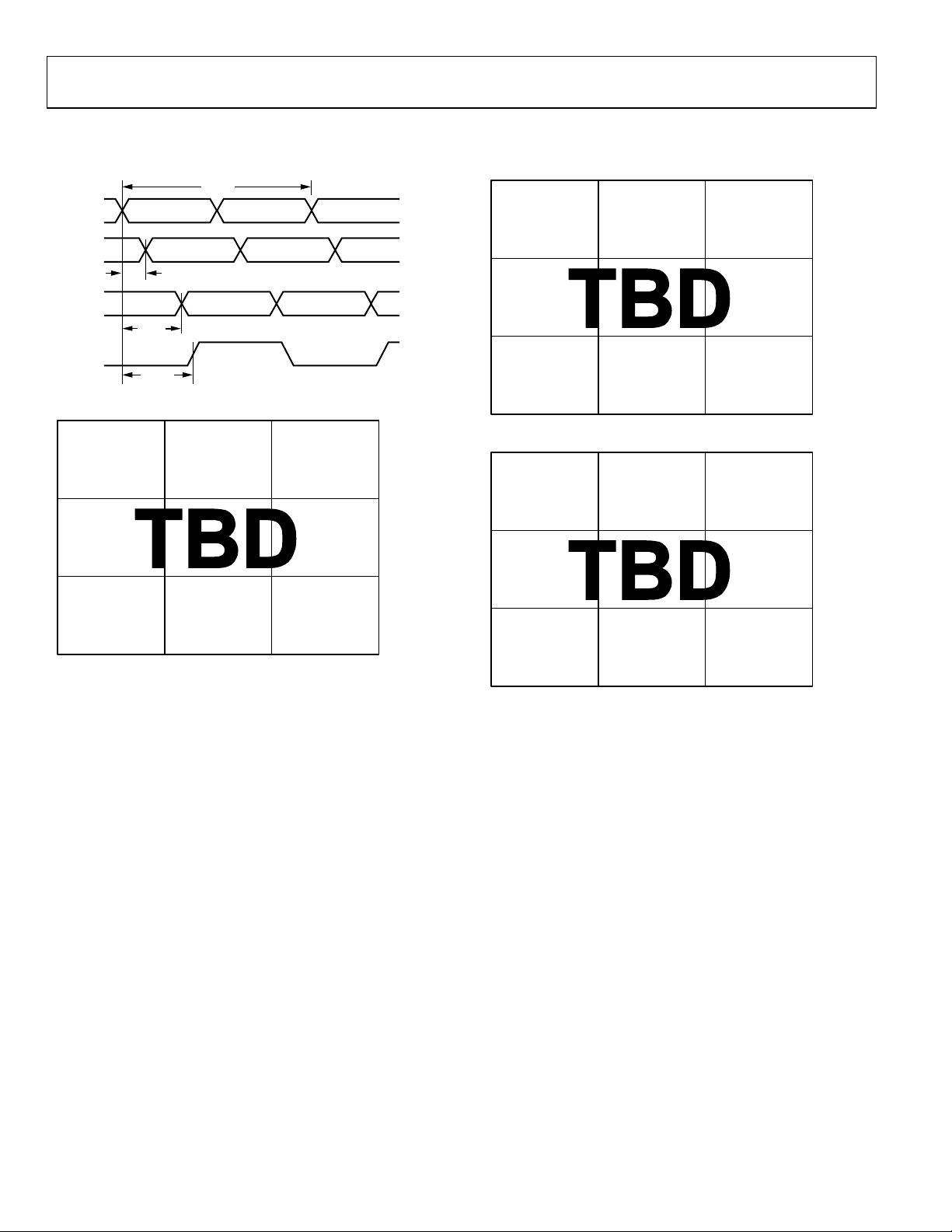

TIMING DIAGRAMS

t

CLK1

LK1

t

PECL

t

LVDS

t

CMOS

Figure 2. CLK1/CLK1B to Clock Output Timing, DIV = 1 Mode

05046-002

Figure 4. LVPECL Fall Time

Figure 3. LVPECL Rise Time

Figure 5. LVDS Timing

Rev. PrB | Page 14 of 52

Preliminary Technical Data AD9510

ABSOLUTE MAXIMUM RATINGS

Table 12.

With

Respect

Parameter or Pin

VS GND −0.3 +3.6 V

VCP GND −0.3 +6 V

VCP V

REFIN, REFINB V

RSET GND V

CPRSET GND V

CLK1, CLK1B, CLK2, CLK2B V

CLK1 CLK1B V

CLK2 CLK2B V

SCLK, SDIO, SDO, CSB GND V

Outputs 0, 1, 2, 3 V

Outputs 4, 5, 6, 7 V

FUNCTION V

STATUS V

Junction Temperature 150 °C

Storage Temperature −65 +150 °C

Lead Temperature (10 sec) 300 °C

to

−0.3 V

S

Min Max Unit

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to

absolute maximum ratings for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS1

Thermal Resistance

64-Lead LFCSP

= 24°C/W

θ

JA

1

Thermal impedance measurements were taken on a 4-layer board in still air,

in accordance with EIA/JESD51-7.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. PrB | Page 15 of 52

AD9510 Preliminary Technical Data

T

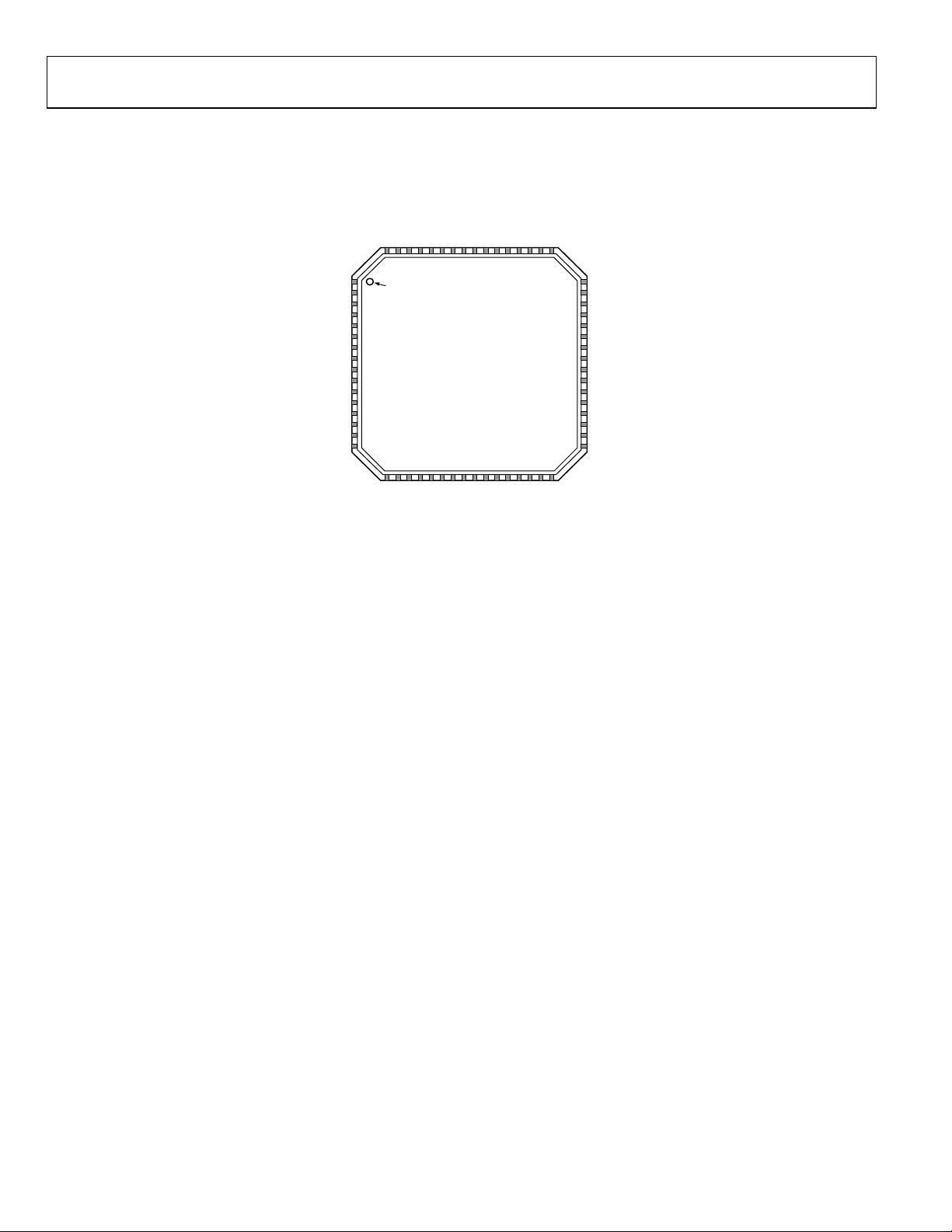

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VS

CPRSE

GND

RSETVSVS

OUT0

OUT0BVSGND

OUT1

OUT1BVSVS

GND

646362616059585756555453525150

GND

49

REFIN

REFINB

GND

VS

VCP

CP

GND

GND

VS

CLK2

CLK2B

GND

VS

CLK1

CLK1B

FUNCTION

PIN 1

1

INDICATOR

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

171819202122232425262728293031

STATUS

SCLK

SDO

SDIO

AD9510

TOP VIEW

(Not to Scale)

VS

CSB

GND

OUT7B

VS

OUT7

GND

OUT3

OUT3B

VS

VS

32

GND

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

VS

OUT4

OUT4B

VS

VS

OUT5

OUT5B

VS

VS

OUT6

OUT6B

VS

VS

OUT2

OUT2B

VS

05046-003

Figure 6. 64-Lead LFCSP Pin Configuration

Note that the exposed paddle on this package is an electrical connection as well as a thermal enhancement. For the device to

function properly, the paddle must be attached to ground, GND.

Rev. PrB | Page 16 of 52

Loading...

Loading...