Analog Devices AD9501SQ, AD9501JQ, AD9501JP, AD9501JN Datasheet

Digitally Programmable

a

FEATURES

Single +5 V Supply

TTL and CMOS Compatible

10 ps Delay Resolution

2.5 ns to 10 ms Full-Scale Range

Maximum Trigger Rate 50 MHz

MIL-STD-883-Compliant Versions Available

APPLICATIONS

Disk Drive Deskewing

Data Communications

Test Equipment

Radar I & Q Matching

GENERAL DESCRIPTION

The AD9501 is a digitally programmable delay generator which

provides programmed time delays of an input pulse. Operating

from a single +5 V supply, the AD9501 is TTL- or CMOScompatible, and is capable of providing accurate timing adjustments with resolutions as low as 10 ps. Its accuracy and

programmability make it ideal for use in data deskewing and

pulse delay applications, as well as clock timing adjustments.

Full-scale delay range is set by the combination of an external

resistor and capacitor, and can range from 2.5 ns to 10 µs for a

Delay Generator

AD9501

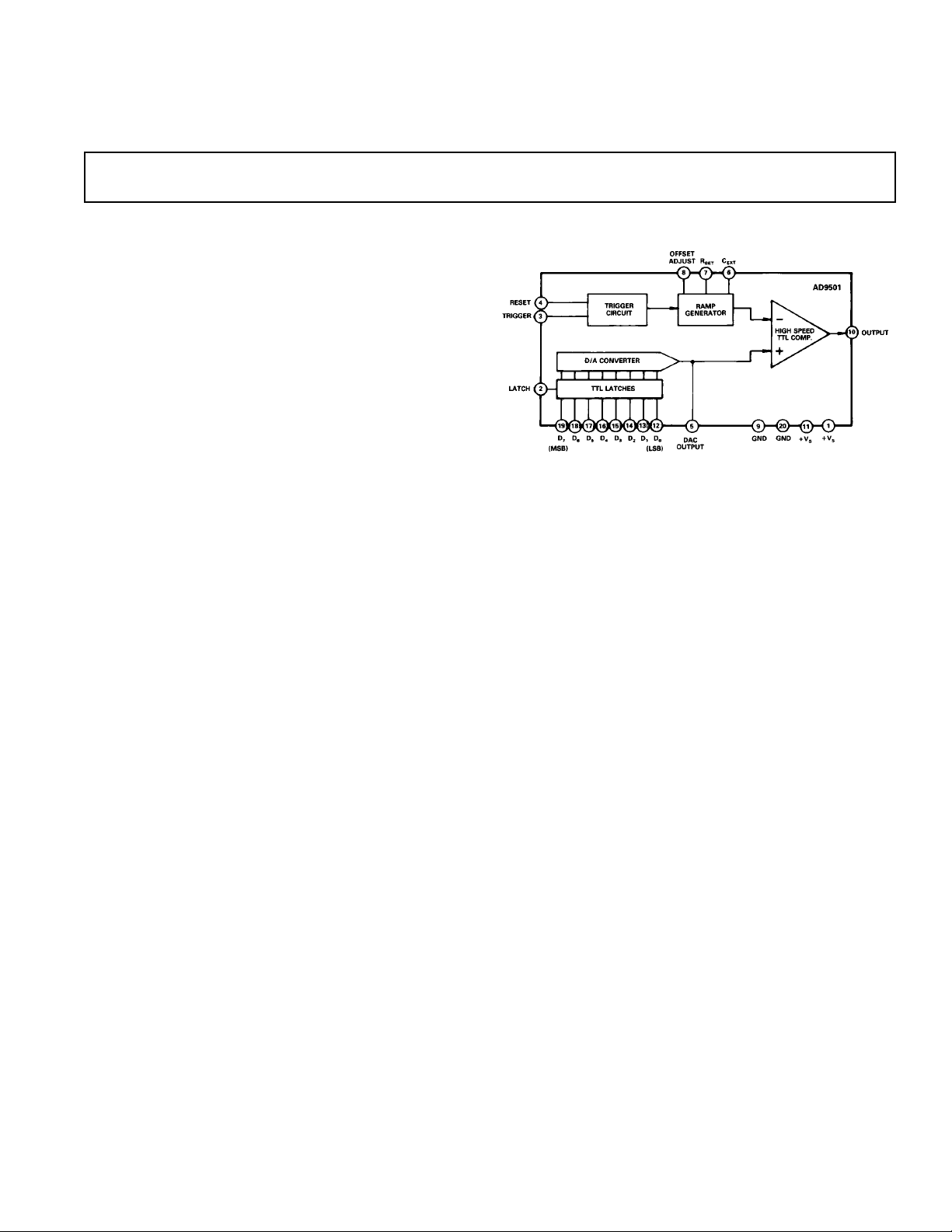

FUNCTIONAL BLOCK DIAGRAM

single AD9501. An eight-bit digital word selects a time delay

within the full-scale range. When triggered by the rising edge of

an input pulse, the output of the AD9501 will be delayed by an

amount equal to the selected time delay (t

propagation delay (t

The AD9501 is available for a commercial temperature range of

0°C to +70°C in a 20-pin plastic DIP, 20-pin ceramic DIP, and

a 20-lead plastic leaded chip carrier (PLCC). Devices fully

compliant to MIL-STD-883 are available in ceramic DIPs.

Refer to the Analog Devices Military Products Databook or current

AD9501/883B data sheet for detailed specifications.

PD

).

) plus an inherent

D

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD9501–SPECIFICA TIONS

ABSOLUTE MAXIMUM RATINGS

Positive Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . +7 V

Digital Input Voltage Range . . . . . . . . . . . . . . . –0.5 V to +V

Trigger/Reset Input Volt. Range . . . . . . . . . . . . –0.5 V to +V

Minimum R

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Ω

SET

Digital Output Current (Sourcing) . . . . . . . . . . . . . . . 10 mA

1

Operating Temperature Range

AD9501JN/JP/JQ . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

S

S

AD9501SQ . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature

2

. . . . . . . . . . . . . . . . . . . . . . . +175°C

Lead Soldering Temperature (10 sec) . . . . . . . . . . . . +300°C

Digital Output Current (Sinking) . . . . . . . . . . . . . . . . 50 mA

ELECTRICAL CHARACTERISTICS

[+VS = +5 V; C

device output connected to Pin 4 RESET input unless otherwise noted]

= Open; R

EXT

= 3090 Ω (Full-Scale Range =100 ns); Pin 8 grounded; and

SET

08C to +708C –558C to +1258C

Test AD9501JN/JP/JQ AD9501SQ

Parameter Temp Level Min Typ Max Min Typ Max Units

RESOLUTION 8 8 Bits

ACCURACY

Differential Nonlinearity +25°C I 0.5 0.5 LSB

Integral Nonlinearity +25°C I 1 1 LSB

Monotonicity +25°C I Guaranteed Guaranteed

DIGITAL INPUTS

Latch Input “1” Voltage Full VI 2.0 2.3 V

Latch Input “0” Voltage Full VI 0.8 0.8 V

Logic “1” Voltage Full VI 2.0 2.0 V

Logic “0” Voltage Full VI 0.8 0.8 V

Logic “1” Current Full VI 60 60 µA

Logic “0” Current Full VI 3 3 µA

Digital Input Capacitance +25°C IV 5.5 5.5 pF

Data Setup Time (t

Data Hold Time (t

Latch Pulse Width (t

3

)

S

4

)

H

) +25°C V 3.5 3.5 ns

L

+25°C V 2.5 2.5 ns

+25°C V 2.5 2.5 ns

Reset/Trigger Pulse Width (tR, tT) +25°CV 2 2 ns

DYNAMIC PERFORMANCE

Maximum Trigger Rate

Minimum Propagation Delay (t

Propagation Delay Tempco

5

PD

7

+25°CIV 1822 1822 MHz

6

)

+25°C I 25 30 25 30 ns

Full V 25 25 ps/°C

Full-Scale Range Tempco Full V 36 36 ps/°C

Delay Uncertainty +25°C V 53 53 ps

Reset Propagation Delay (t

Reset-to-Trigger Holdoff (t

Trigger-to-Reset Holdoff (t

Minimum Output Pulse Width

Output Rise Time

Output Fall Time

DAC Settling Time (t

12

12

LD

Linear Ramp Settling Time (t

8

RD

THO

RHO

)

9

)

10

)

11

+25°C I 14.5 17.5 14.5 17.5 ns

+25°C V 4.5 4.5 ns

+25°C V 19 19 ns

+25°C V 7.5 7.5 ns

+25°C I 2.3 3.5 2.3 3.5 ns

13

)

LRS

+25°C I 1.0 2.0 1.0 2.0 ns

+25°C V 30 30 ns

14

)

+25°C V 20 20 ns

DIGITAL OUTPUT

Logic “1” Voltage (Source 1 mA) Full VI 2.4 2.4 V

Logic “0” Voltage (Sink 4 mA) Full VI 0.24 0.4 0.24 0.5 V

POWER SUPPLY

15

Positive Supply Current (+5.0 V) Full VI 69.5 83 69.5 83 mA

Power Dissipation Full VI 415 415 mW

Power Supply Rejection Ratio

16

Full-Scale Range Sensitivity +25°C I 0.7 2.0 0.7 2.0 ns/V

Minimum Prop Delay Sensitivity +25°C I 0.45 1.7 0.45 1.7 ns/V

–2–

REV. A

AD9501

NOTES

1

Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability

is not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

2

Typical thermal impedances: 20-lead plastic leaded chip carrier θJA= 73°C/W; θJC= 29°C/W. 20-pin ceramic DIP θJA= 65°C/W; θJC= 20°C/W. 20-pin plastic DIP

θJA= 65°C/W; θJC= 26°C/W.

3

Digital data inputs must remain stable for the specified time prior to the positive transition of the LATCH signal.

4

Digital data inputs must remain stable for the specified time after the positive transition of the LATCH signal.

5

Programmed delay (tD) = 0 ns. Maximum self-resetting trigger rate is limited to 6.9 MHz with 100 ns programmed delay. If tD= 0 ns and external RESET signal is

used, maximum trigger rate is 23 MHz.

6

Programmed delay (tD) = 0 ns. In operation, any programmed delays are in addition to the minimum propagation delay (tPD).

7

Programmed delay (tD) = 0 ns. [Minimum propagation delay (tPD)].

8

Measured from 50% transition point of the RESET signal input to the 50% transition point of the falling edge of the output.

9

Minimum time from the falling edge of RESET to the triggering input to insure valid output pulse, using external RESET pulse.

10

Minimum time from triggering event to rising edge of RESET to insure valid output event, using external RESET pulse. Extends to 125 ns when programmed delay

is 100 ns.

11

When self-resetting with a full-scale programmed delay.

12

Measured from +0.4 V to +2.4 V; source = 1 mA; sink = 4 mA.

13

Measured from the data input to the time when the AD9501 becomes 8-bit accurate, after a full-scale change in the program delay data word.

14

Measured from the RESET input to the time when the AD9501 becomes 8-bit accurate, after a full-scale programmed delay.

15

Supply voltage should remain stable within ±5% for normal operation.

16

Measured at +VS = +5.0 V ± 5%; specification shown is for worst case.

Specifications subject to change without notice.

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

II – 100% production tested at +25°C, and sample tested at specified

temperatures.

III – Sample tested only.

IV – Parameter is guaranteed by design and characterization testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C. 100% production

tested at temperature extremes for extended temperature devices;

sample tested at temperature extremes for commercial/industrial

devices.

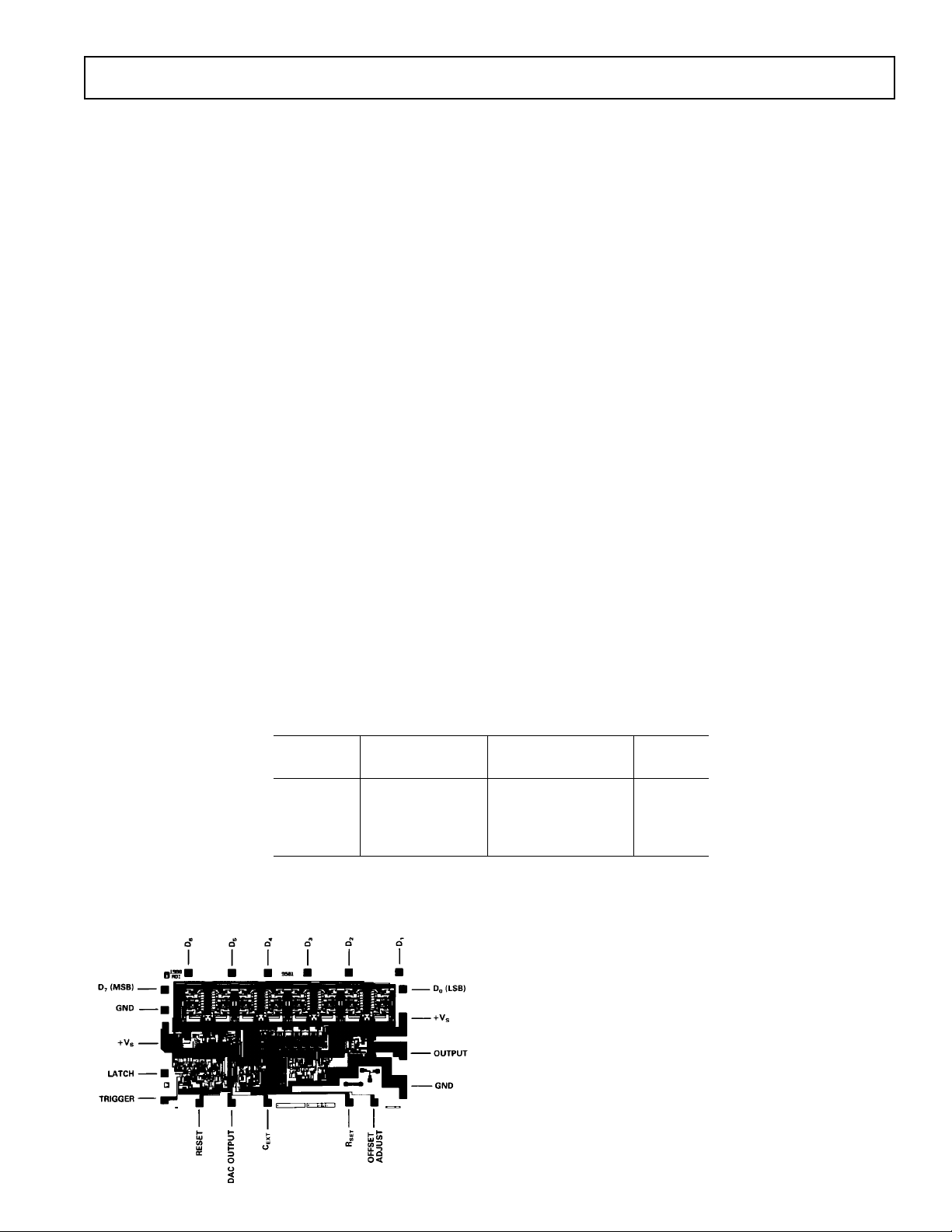

ORDERING GUIDE

Device Temperature Description Option*

AD9501JN 0°C to +70°C 20-Pin Plastic DIP N-20

AD9501JP 0°C to +70°C 20-Lead PLCC P-20A

AD9501JQ 0°C to +70°C 20-Pin Ceramic DIP Q-20

AD9501SQ –55°C to +125°C 20-Pin Ceramic DIP Q-20

*N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip.

DIE LAYOUT AND MECHANICAL INFORMATION

Package

MECHANICAL INFORMATION

Die Dimensions . . . . . . . . . . . . . . . . . . 89 × 153 × 15 (±2) mils

Pad Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 × 4 mils

Metalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Aluminum

Backing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . None

Substrate Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . Ground

Passivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Oxynitride

Die Attach . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Gold Eutectic

Bond Wire . . . . . . . . 1.25 mil, Aluminum; Ultrasonic Bonding

or 1 mil, Gold; Gold Ball Bonding

REV. A

–3–

AD9501

WARNING!

ESD SENSITIVE DEVICE

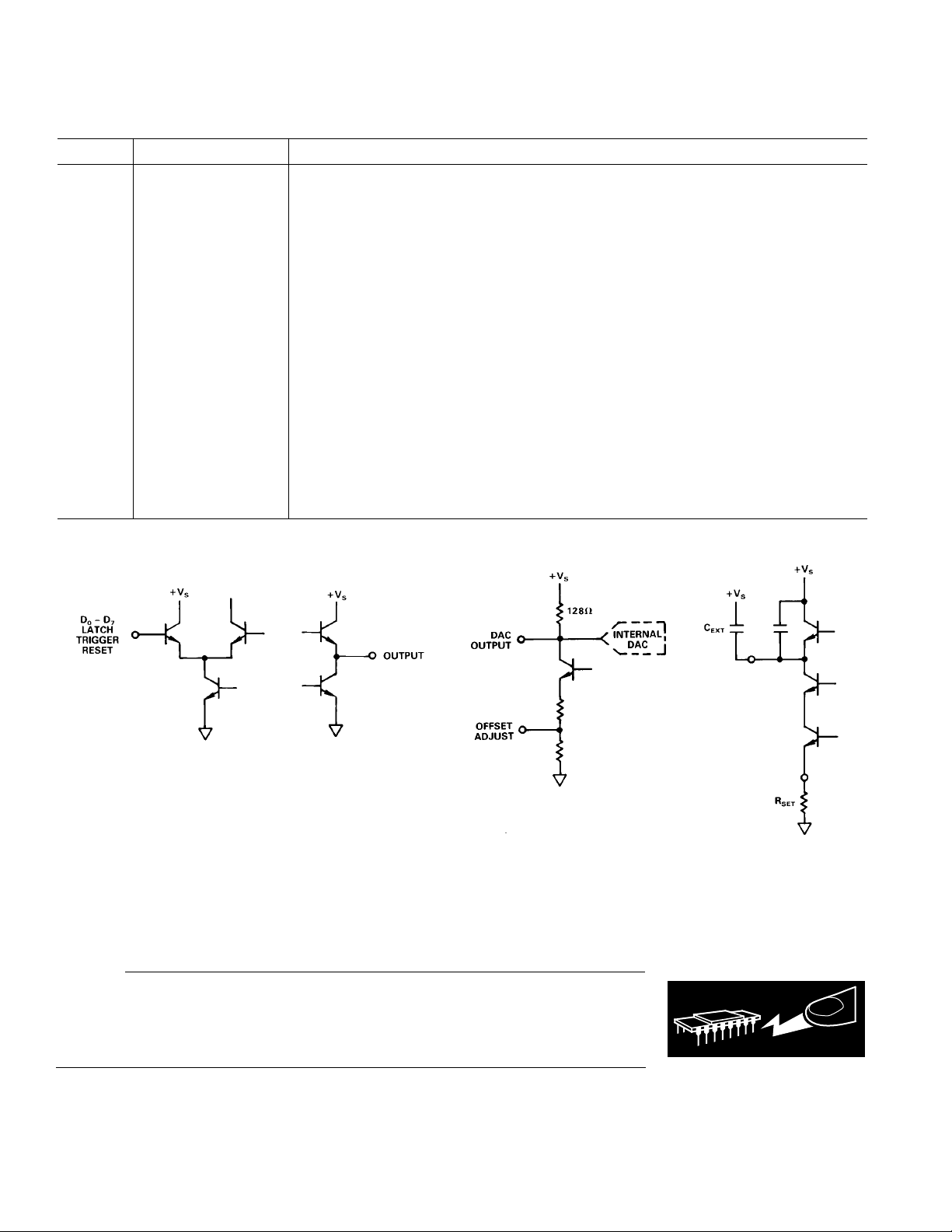

Pin No. Name Function

AD9501 PIN DESCRIPTIONS

1+V

S

2 LATCH TTL/CMOS register control line. Logic HIGH latches input data D

Positive voltage supply; nominally +5 V.

. Register is

0–D7

transparent for logic LOW.

3 TRIGGER TTL/CMOS-compatible input. Rising edge triggers the internal ramp generator, and begins

the delay cycle.

4 RESET TTL/CMOS-compatible input. Logic HIGH resets the ramp voltage and OUTPUT.

5 DAC OUTPUT Output voltage of the internal digital-to-analog converter.

6C

7R

EXT

SET

8 OFFSET ADJUST Normally connected to GROUND. Can be used to adjust minimum propagation delay (t

Optional external capacitor connected to +VS; used with R

to determine full-scale delay range (t

DFS

).

External resistor to ground, used to determine full-scale delay range (t

and 8.5 pF internal capacitor

SET

DFS

).

);

PD

see Theory of Operation text.

9 GROUND Circuit ground return.

10 OUTPUT TTL-compatible delayed output pulse.

11 +V

12-19 D

S

0–D7

Positive voltage supply; nominally +5 V.

TTL/CMOS-compatible inputs, used to set the programmed delay of the AD9501 delayed

output. D

is LSB and D7 is MSB.

0

20 GROUND Circuit ground return.

AD9501 Equivalent Circuits

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9501 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. A

Loading...

Loading...