www.BDTIC.com/ADI

16-Bit, 80/100 MSPS ADC

FEATURES

100 MSPS guaranteed sampling rate (AD9446-100)

83.6 dBFS SNR with 30 MHz input (3.8 V p-p input, 80 MSPS)

82.6 dBFS SNR with 30 MHz input (3.2 V p-p input, 80 MSPS)

89 dBc SFDR with 30 MHz input (3.2 V p-p input, 80 MSPS)

95 dBFS 2-tone SFDR with 9.8 MHz and 10.8 MHz (100 MSPS)

60 fsec rms jitter

Excellent linearity

DNL = ±0.4 LSB typical

INL = ±3.0 LSB typical

2.0 V p-p to 4.0 V p-p differential full-scale input

Buffered analog inputs

LVDS outputs (ANSI-644 compatible) or CMOS outputs

Data format select (offset binary or twos complement)

Output clock available

3.3 V and 5 V supply operation

APPLICATIONS

MRI receivers

Multicarrier, multimode cellular receivers

Antenna array positioning

Power amplifier linearization

Broadband wireless

Radar

Infrared imaging

Communications instrumentation

GENERAL DESCRIPTION

The AD9446 is a 16-bit, monolithic, sampling analog-to-digital

converter (ADC) with an on-chip track-and-hold circuit. It is

optimized for performance, small size, and ease of use. The

product operates up to a 100 MSPS, providing superior SNR for

instrumentation, medical imaging, and radar receivers

employing baseband (<100 MHz) IF frequencies.

The ADC requires 3.3 V and 5.0 V power supplies and a low

v

oltage differential input clock for full performance operation.

No external reference or driver components are required for

many applications. Data outputs are CMOS or LVDS

compatible (ANSI-644 compatible) and include the means to

reduce the overall current needed for short trace distances.

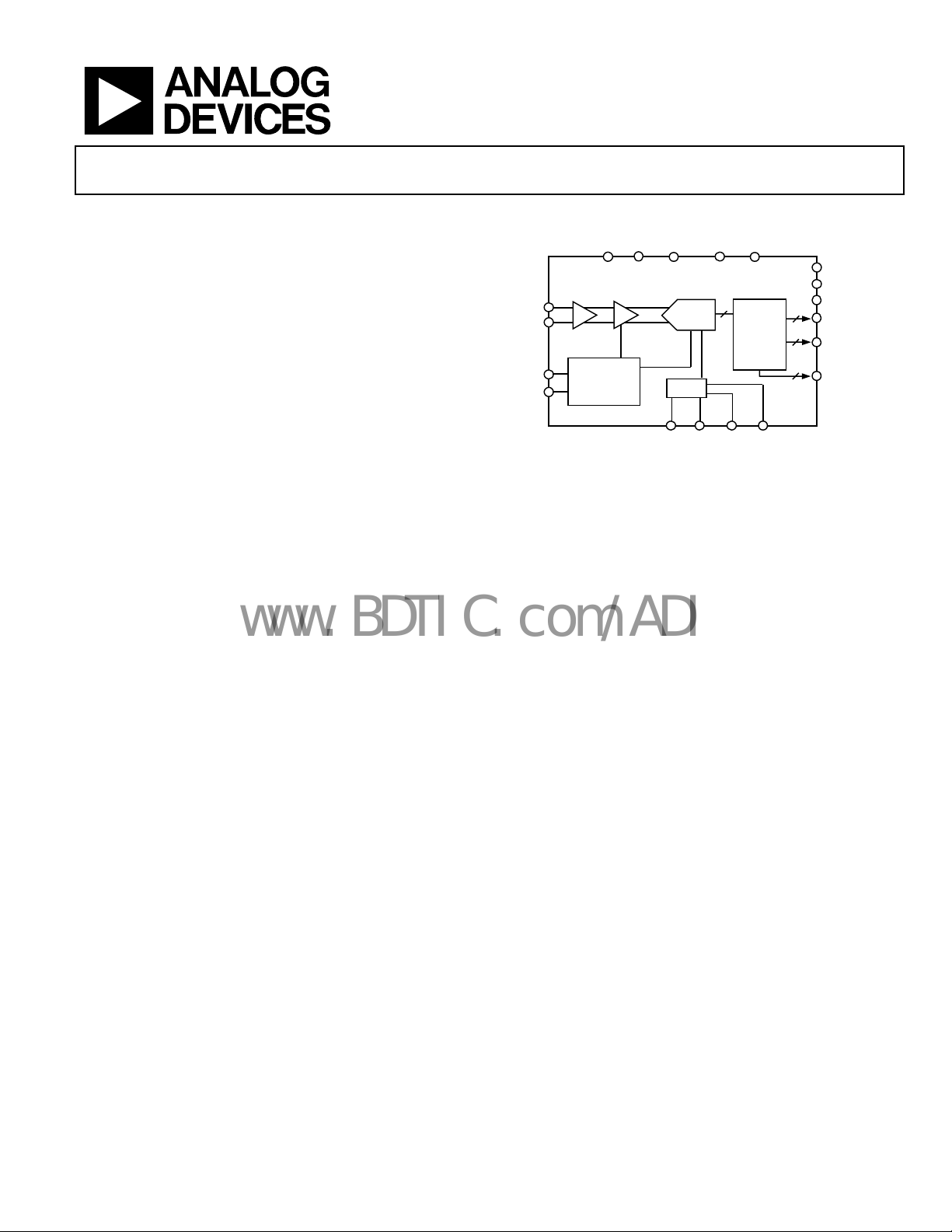

AD9446

FUNCTIONAL BLOCK DIAGRAM

AGND DRGND DRVDD

AVDD1 AVDD2

2

32

2

DFS

DCS MODE

OUTPUT MODE

OR

D15 TO D0

DCO

AD9446

VIN+

VIN–

CLK+

CLK–

BUFFER

CLOCK

AND TIMING

MANAGEMENT

T/H

PIPELINE

VREF

ADC

REF

Figure 1.

16

CMOS

OR

LVDS

OUTPUT

STAGING

REFBSENSE REFT

Optional features allow users to implement various selectable

op

erating conditions, including input range, data format select,

and output data mode.

The AD9446 is available in a Pb-free, 100-lead, surface-mount,

lastic package (100-lead TQFP/EP) specified over the

p

industrial temperature range −40°C to +85°C.

PRODUCT HIGHLIGHTS

1. True 16-bit linearity.

2. H

igh performance: outstanding SNR performance for

baseband IFs in data acquisition, instrumentation,

magnetic resonance imaging, and radar receivers.

ase of use: on-chip reference and high input impedance

3. E

track-and-hold with adjustable analog input range and an

output clock simplifies data capture.

ackaged in a Pb-free, 100-lead TQFP/EP package.

4. P

5. C

lock duty cycle stabilizer (DCS) maintains overall ADC

performance over a wide range of clock pulse widths.

6. O

R (out-of-range) outputs indicate when the signal is

beyond the selected input range.

05490-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

AD9446

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Te r mi n ol o g y .......................................................................................9

Applications....................................................................................... 1

General Description......................................................................... 1

Functional Block Diagram .............................................................. 1

Product Highlights........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

DC Specifications ......................................................................... 3

AC Specifications.......................................................................... 4

Digital Specifications ................................................................... 6

Switching Specifications .............................................................. 6

Timing Diagrams.......................................................................... 7

Absolute Maximum Ratings............................................................ 8

Thermal Resistance ...................................................................... 8

ESD Caution.................................................................................. 8

Pin Configurations and Function Descriptions ......................... 10

Equivalent Circuits......................................................................... 15

Typical Perf or m an c e Chara c t e ristic s ........................................... 16

Theory of Operation ...................................................................... 24

Analog Input and Reference Overview ................................... 24

Clock Input Considerations...................................................... 26

Power Considerations ................................................................ 27

Digital Outputs........................................................................... 27

Timing ......................................................................................... 27

Operational Mode Selection ..................................................... 28

Evaluation Board ............................................................................ 29

Outline Dimensions ....................................................................... 36

Ordering Guide .......................................................................... 36

REVISION HISTORY

10/05—Revision 0: Initial Version

Rev. 0 | Page 2 of 36

AD9446

www.BDTIC.com/ADI

SPECIFICATIONS

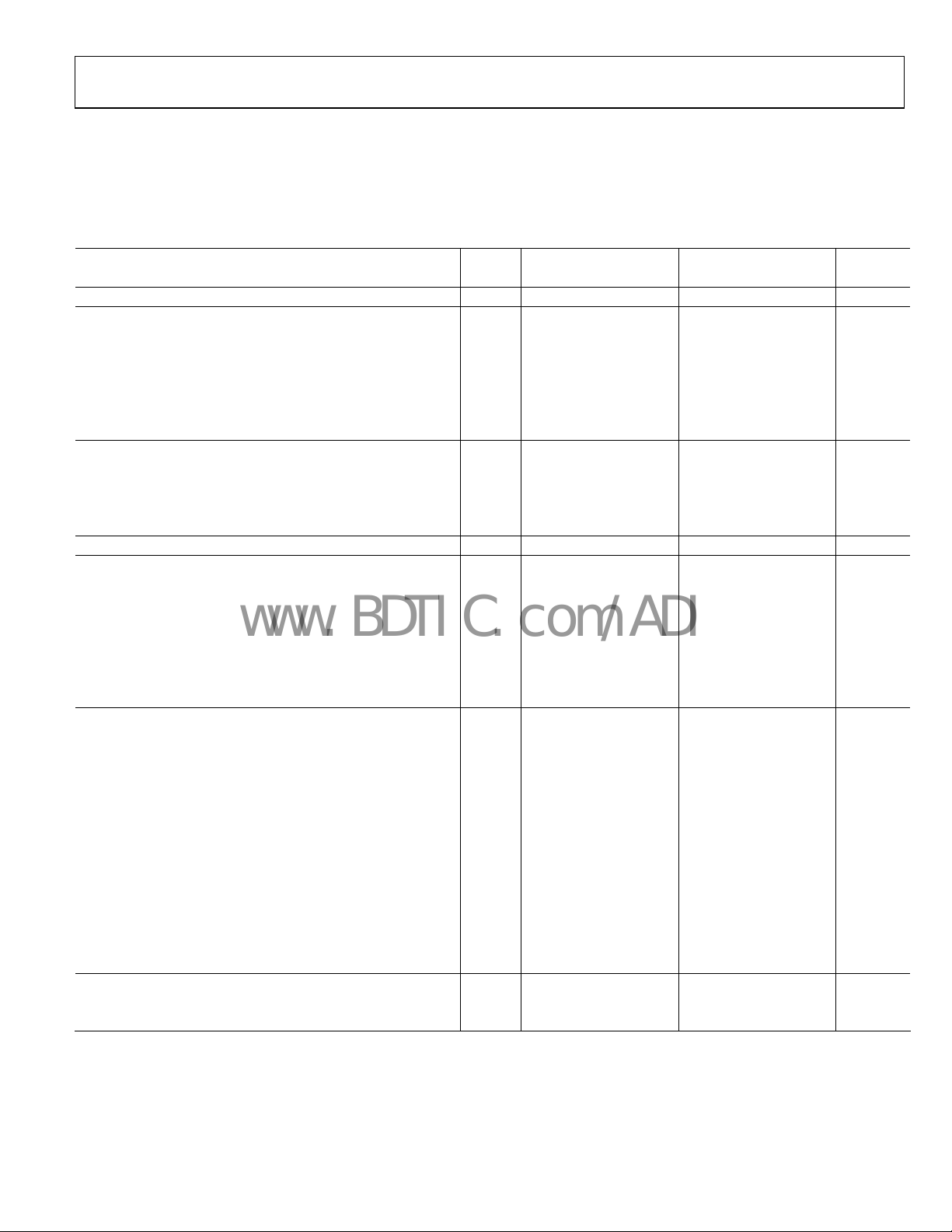

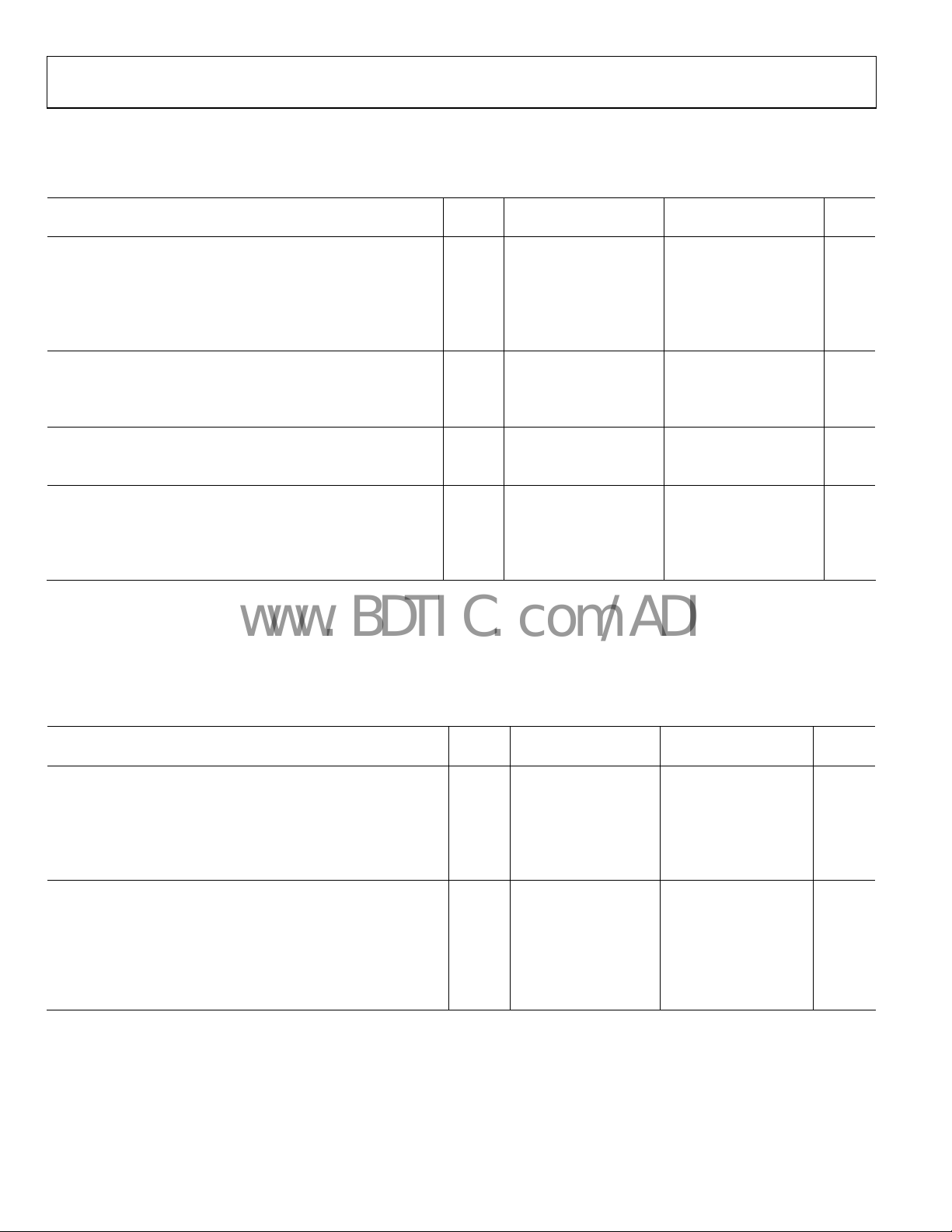

DC SPECIFICATIONS

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, LVDS mode, specified minimum sampling rate, 3.2 V p-p differential input, internal

trimmed reference (1.6 V mode), A

Table 1.

AD9446BSVZ-80 AD9446BSVZ-100

Parameter Te mp Min Typ Max Min Typ Max Unit

RESOLUTION Full 16 16 Bits

ACCURACY

No Missing Codes Full Guaranteed Guaranteed

Offset Error Full −5 ±0.1 +5 −5 ±0.1 +5 mV

Gain Error Full −3 ±0.6 +3 −3 ±0.5 +3 % FSR

25°C −2 ±0.3 +2 −2 ±0.3 +2 % FSR

Differential Nonlinearity (DNL)

Integral Nonlinearity (INL)1 25°C −5 ±3.0 +5 −6 ±3.0 +6 LSB

VOLTAGE REFERENCE

Output Voltage

1

VREF = 1.6 V (3.2 V p-p Analog Input Range) Full 1.6 1.6 V

Load Regulation @ 1.0 mA Full ±2 ±2 mV

Reference Input Current (External 1.6 V Reference) Full µA

INPUT REFERRED NOISE 25°C 1.5 1.9 LSB rms

ANALOG INPUT

Input Span

VREF = 1.6 V Full 3.2 3.2 V p-p

VREF = 1.0 V (External) Full 2.0 2.0 V p-p

Internal Input Common-Mode Voltage Full 3.5 3.5 V

External Input Common-Mode Voltage Full 3.2 3.8 3.2 3.8 V

Input Resistance

Input Capacitance

2

2

POWER SUPPLIES

Supply Voltage

AVDD1 Full 3.14 3.3 3.46 3.14 3.3 3.46 V

AVDD2 Full 4.75 5.0 5.25 4.75 5.0 5.25 V

DRVDD—LVDS Outputs Full 3.0 3.3 3.6 3.0 3.3 3.6 V

DRVDD—CMOS Outputs Full 3.0 3.3 3.6 3.0 3.3 3.6 V

Supply Current

1

I

AVDD

1

I

AVDD2

1

I

—LVDS Outputs Full 68 75 69 75 mA

DRVDD

1

I

—CMOS Outputs Full 14 14 mA

DRVDD

PSRR

Offset Full 1 1 mV/V

Gain Full 0.2 0.2 %/V

POWER CONSUMPTION

LVDS Outputs Full 2.4 2.6 2.6 2.8 W

CMOS Outputs (DC Input) Full 2.2 2.3 W

1

Measured at the maximum clock rate, fIN = 15 MHz, full-scale sine wave, with a 100 Ω differential termination on each pair of output bits for LVDS output mode and

approximately 5 pF loading on each output bit for CMOS output mode.

2

Input capacitance or resistance refers to the effective impedance between one differential input pin and AGND. Refer to Figure 6 for the equivalent analog input structure.

= −1.0 dBFS, DCS on, unless otherwise noted.

IN

1

Full −0.75 ±0.4 +0.75 −0.85 ±0.4 +0.85 LSB

Full 1 1 kΩ

Full 6 6 pF

Full 335 365 368 401 mA

Full 204 234 223 255 mA

Rev. 0 | Page 3 of 36

AD9446

www.BDTIC.com/ADI

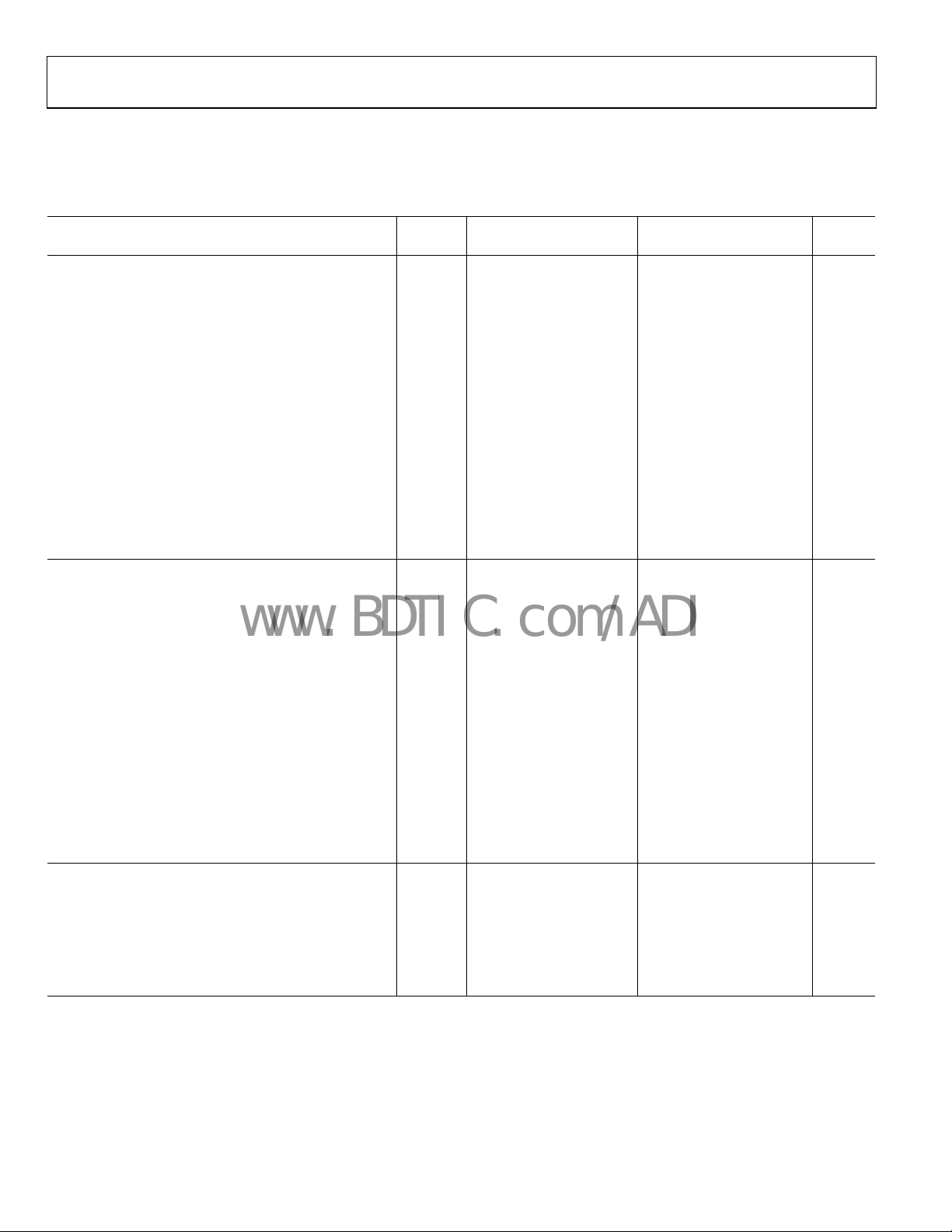

AC SPECIFICATIONS

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, LVDS mode, specified minimum sample rate, 3.2 V p-p differential input, internal

trimmed reference (1.6 V mode), A

Table 2.

AD9446BSVZ-80 AD9446BSVZ-100

Parameter Te m p Min Typ Max Min Typ Max Unit

SIGNAL-TO-NOISE RATIO (SNR)

fIN = 10 MHz 25°C 79.6 81.8 78.4 79.7 dB

fIN = 30 MHz 25°C 80.5 81.6 78.3 79.5 dB

Full 79.2 77.9 dB

fIN = 70 MHz 25°C 79.0 80.6 77.7 79.0 dB

Full 78.2 77.6 dB

fIN = 92 MHz 25°C 80.1 78.9 dB

fIN = 125 MHz 25°C 78.8 78.2 dB

fIN = 170 MHz 25°C 77.1 77.0 dB

fIN = 10 MHz (2 V p-p Input) 25°C 78.3 76.6 dB

fIN = 30 MHz (2 V p-p Input) 25°C 78.3 76.6 dB

fIN = 70 MHz (2 V p-p Input) 25°C 77.6 76.2 dB

fIN = 92 MHz (2 V p-p Input) 25°C 77.5 76 dB

fIN = 125 MHz (2 V p-p Input) 25°C 76.7 75.6 dB

fIN = 170 MHz (2 V p-p Input) 25°C 75.5 75.1 dB

SIGNAL-TO-NOISE AND DISTORTION (SINAD)

fIN = 10 MHz 25°C 77.1 80.5 76.9 78.9 dB

fIN = 30 MHz 25°C 75.9 80.4 75.5 78.6 dB

Full 74.9 71.7 dB

fIN = 70 MHz 25°C 75.5 78.6 73.8 77.7 dB

Full 74.4 69.1 dB

fIN = 92 MHz 25°C 79.2 77.1 dB

fIN = 125 MHz 25°C 74.9 76.9 dB

fIN = 170 MHz 25°C 66.0 70.5 dB

fIN = 10 MHz (2 V p-p Input) 25°C 77.9 76.2 dB

fIN = 30 MHz (2 V p-p Input) 25°C 77.8 76.1 dB

fIN = 70 MHz (2 V p-p Input) 25°C 77.1 75.9 dB

fIN = 92 MHz (2 V p-p Input) 25°C 77.1 75.7 dB

fIN = 125 MHz (2 V p-p Input) 25°C 75.7 75.3 dB

fIN = 170 MHz (2 V p-p Input) 25°C 72.5 73.6 dB

EFFECTIVE NUMBER OF BITS (ENOB)

fIN = 10 MHz 25°C 13.2 13.0 Bits

fIN = 30 MHz 25°C 13.2 12.9 Bits

fIN = 70 MHz 25°C 12.9 12.8 Bits

fIN = 92 MHz 25°C 13.0 12.7 Bits

fIN = 125 MHz 25°C 12.3 12.6 Bits

fIN = 170 MHz 25°C 10.8 11.6 Bits

= −1 dBFS, DCS on, unless otherwise noted.

IN

Rev. 0 | Page 4 of 36

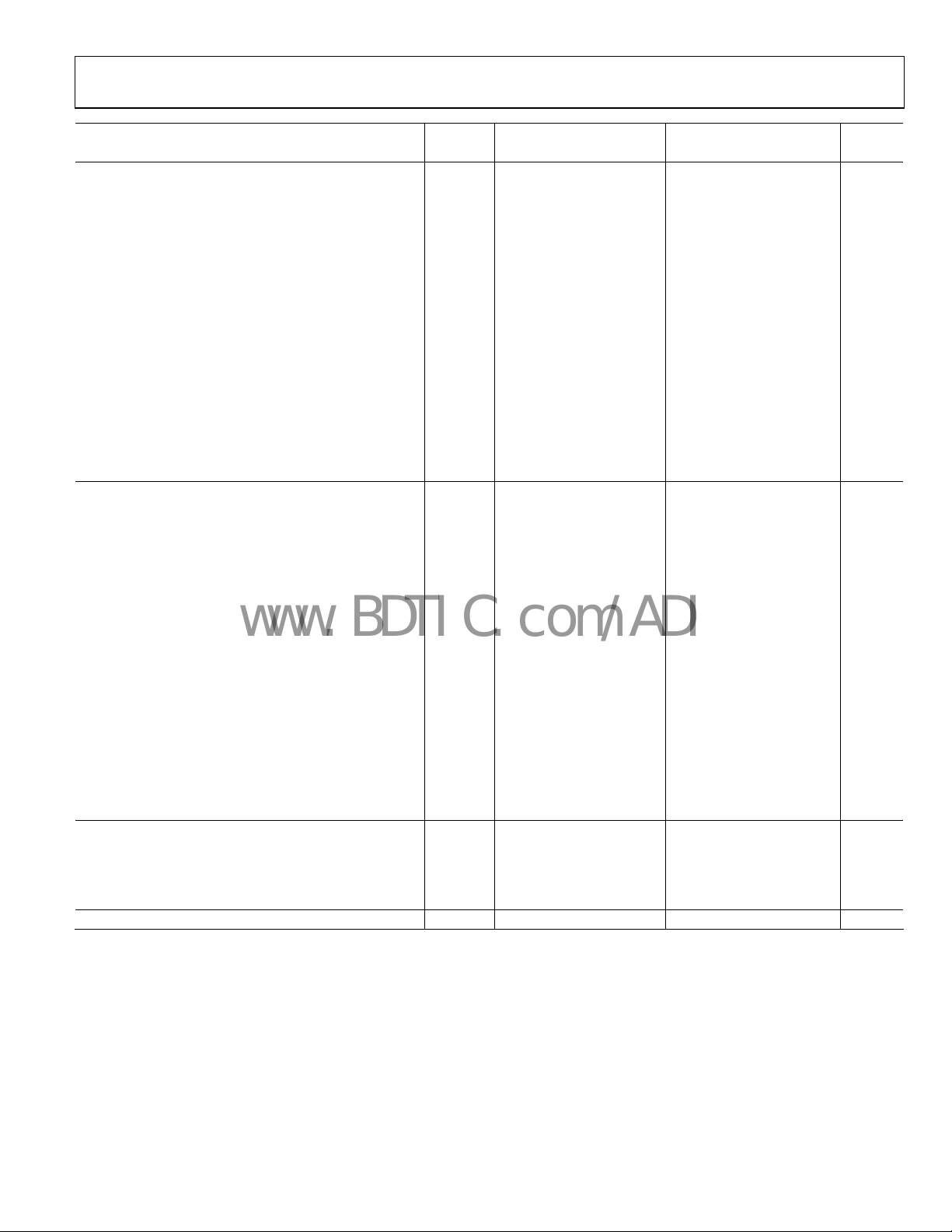

AD9446

www.BDTIC.com/ADI

AD9446BSVZ-80 AD9446BSVZ-100

Parameter Te m p Min Typ Max Min Typ Max Unit

SPURIOUS-FREE DYNAMIC RANGE

(SFDR, Second or Third Harmonic)

fIN = 10 MHz 25°C 82 90 82 92 dBc

fIN = 30 MHz 25°C 82 89 82 89 dBc

Full 80 79 dBc

fIN = 70 MHz 25°C 80 87 81 89 dBc

Full 79 77 dBc

fIN = 92 MHz 25°C 84 84 dBc

fIN = 125 MHz 25°C 80 83 dBc

fIN = 170 MHz 25°C 66 74 dBc

fIN = 10 MHz (2 V p-p Input) 25°C 92 94 dBc

fIN = 30 MHz (2 V p-p Input) 25°C 93 92 dBc

fIN = 70 MHz (2 V p-p Input) 25°C 92 92 dBc

fIN = 92 MHz (2 V p-p Input) 25°C 90 89 dBc

fIN = 125 MHz (2 V p-p Input) 25°C 85 87 dBc

fIN = 170 MHz (2 V p-p Input) 25°C 77 82 dBc

WORST SPUR EXCLUDING SECOND OR

THIRD HARMONICS

fIN = 10 MHz 25°C −98 −89 −96 −91 dBc

fIN = 30 MHz 25°C −97 −89 −97 −89 dBc

Full −89 −87 dBc

fIN = 70 MHz 25°C −98 −90 −96 −90 dBc

Full −89 −88 dBc

fIN = 92 MHz 25°C −98 −95 dBc

fIN = 125 MHz 25°C −96 −96 dBc

fIN = 170 MHz 25°C −95 −92 dBc

fIN = 10 MHz (2 V p-p Input) 25°C −97 −93 dBc

fIN = 30 MHz (2 V p-p Input) 25°C −97 −96 dBc

fIN = 70 MHz (2 V p-p Input) 25°C −94 −94 dBc

fIN = 92 MHz (2 V p-p Input) 25°C −97 −99 dBc

fIN = 125 MHz (2 V p-p Input) 25°C −97 −95 dBc

fIN = 170 MHz (2 V p-p Input) 25°C −93 −95 dBc

TWO-TONE SFDR

fIN = 10.8 MHz @ −7 dBFS,

9.8 MHz @ −7 dBFS

fIN = 70.3 MHz @ −7 dBFS,

69.3 MHz @ −7 dBFS

ANALOG BANDWIDTH Full 325 540 MHz

25°C 96 95 dBFS

25°C 92 92 dBFS

Rev. 0 | Page 5 of 36

AD9446

www.BDTIC.com/ADI

DIGITAL SPECIFICATIONS

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, R

Table 3.

AD9446BSVZ-80 AD9446BSVZ-100

Parameter Te mp Min Typ Max Min Typ Max Unit

CMOS LOGIC INPUTS (DFS, DCS MODE, OUTPUT MODE)

High Level Input Voltage Full 2.0 2.0 V

Low Level Input Voltage Full 0.8 0.8 V

High Level Input Current Full 200 200 µA

Low Level Input Current Full −10

Input Capacitance Full

DIGITAL OUTPUT BITS—CMOS MODE (D0 to D15, OTR)

DRVDD = 3.3 V

High Level Output Voltage Full 3.25

Low Level Output Voltage Full

DIGITAL OUTPUT BITS—LVDS MODE (D0 to D15, OTR)

VOD Differential Output Voltage

2

VOS Output Offset Voltage Full 1.125

CLOCK INPUTS (CLK+, CLK−)

Differential Input Voltage Full 0.2

Common-Mode Voltage Full 1.3 1.5 1.6 1.3 1.5 1.6 V

Input Resistance Full 1.1 1.4 1.7 1.1 1.4 1.7 kΩ

Input Capacitance Full

1

Output voltage levels measured with 5 pF load on each output.

2

LVDS R

TERM

= 100 Ω.

= 3.74 kΩ, unless otherwise noted.

LVD S_ BI AS

1

Full 247

2

+10 −10 +10 µA

0.2 0.2 V

2

545 247 545 mV

1.375 1.125 1.375 V

2 pF

3.25 V

0.2 V

2 pF

SWITCHING SPECIFICATIONS

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, unless otherwise noted.

Table 4.

AD9446BSVZ-80 AD9446BSVZ-100

Parameter Te mp Min Typ Max Min Typ Max Unit

CLOCK INPUT PARAMETERS

Maximum Conversion Rate Full 80 100 MSPS

Minimum Conversion Rate Full 1 1 MSPS

CLK Period Full 12.5 10 ns

CLK Pulse Width High1 (t

CLK Pulse Width Low1 (t

DATA OUTPUT PARAMETERS

Output Propagation Delay—CMOS (tPD)2 (Dx, DCO+) Full 3.35 3.35 ns

Output Propagation Delay—LVDS (tPD)3 (Dx+), (t

Pipeline Delay (Latency) Full 13 13 Cycles

Aperture Delay (tA) Full ns

Aperture Uncertainty (Jitter, tJ) Full 60 60

1

With duty cycle stabilizer (DCS) enabled.

2

Output propagation delay is measured from clock 50% transition to data 50% transition with 5 pF load.

3

LVDS R

= 100 Ω. Measured from the 50% point of the rising edge of CLK+ to the 50% point of the data transition.

TERM

) Full 5.0 4.0 ns

CLKH

) Full 5.0 4.0 ns

CLKL

)3 (DCO+) Full 2.1 3.6 4.8 2.3 3.6 4.8 ns

CPD

fsec

s

rm

Rev. 0 | Page 6 of 36

AD9446

www.BDTIC.com/ADI

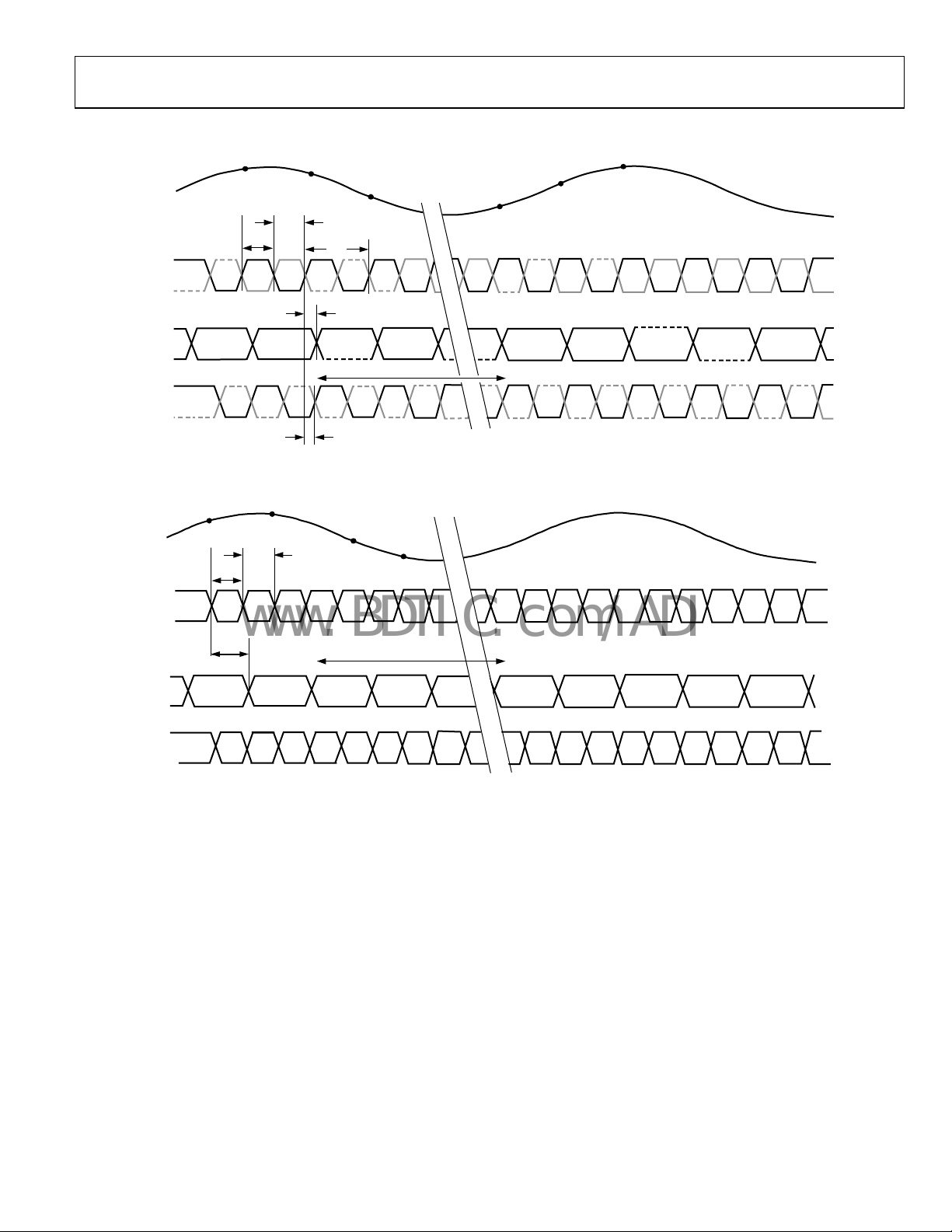

TIMING DIAGRAMS

A

CLK+

CLK–

N–1

IN

t

CLKH

t

CLKL

N

N + 1

1/

f

S

t

PD

DATA OUT

DCO+

DCO–

VIN

CLK–

CLK+

DX

DCO+

DCO–

N–1

t

CLKH

N + 1

05490-002

t

CPD

N – 13

13 CLOCK CYCLES

N–12

N

Figure 2. LVDS Mode Timing Diagram

N

N + 1

t

CLKL

t

PD

N – 13 N – 12 N – 1 N

N + 2

13 CLOCK CYCLES

05490-003

Figure 3. CMOS T

iming Diagram

Rev. 0 | Page 7 of 36

AD9446

www.BDTIC.com/ADI

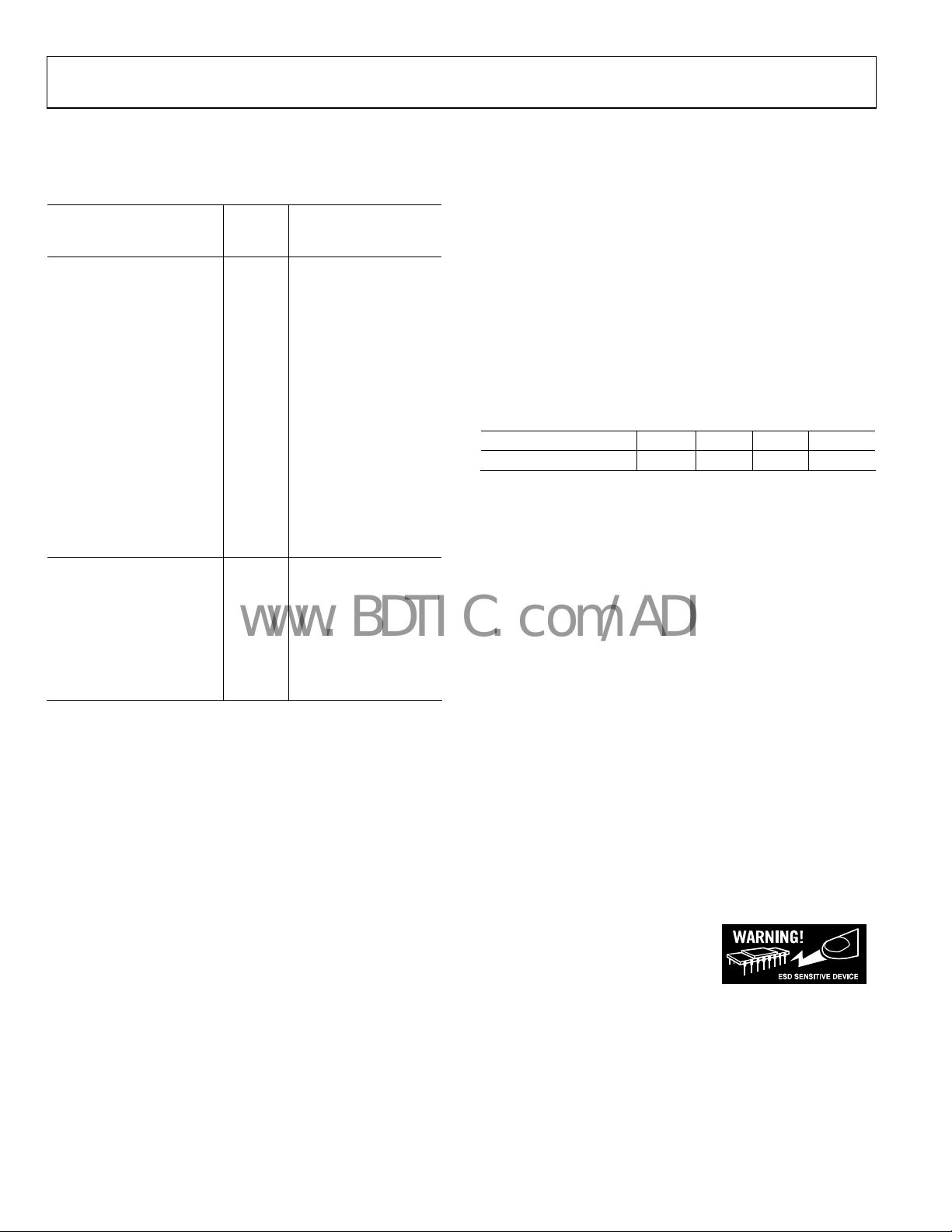

ABSOLUTE MAXIMUM RATINGS

Table 5.

With

t

Respec

Parameter

ELECTRICAL

AVDD1 AGND −0.3 V to +4 V

AVDD2 AGND −0.3 V to +6 V

DRVDD DGND −0.3 V to +4 V

AGND DGND −0.3 V to +0.3 V

AVDD1 DRVDD −4 V to +4 V

AVDD2 DRVDD −4 V to +6 V

AVDD2 AVDD1 −4 V to +6 V

D0± to D15± DGND –0.3 V to DRVDD + 0.3 V

CLK+/CLK− AGND –0.3 V to AVDD1 + 0.3 V

OUTPUT MODE,

DCS MODE, DFS

VIN+, VIN− AGND –0.3 V to AVDD2 + 0.3 V

VREF AGND –0.3 V to AVDD1 + 0.3 V

SENSE AGND –0.3 V to AVDD1 + 0.3 V

REFT, REFB AGND –0.3 V to AVDD1 + 0.3 V

ENVIRONMENTAL

Storage Temperature

Range

Operating Temperature

Range

Lead Temperature

(Soldering 10 sec)

Junction Temperature 150°C

to

AGND –0.3 V to AVDD1 + 0.3 V

–65°C to +125°C

–40°C to +85°C

300°C

Rating

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

The heat sink of the AD9446 package must be soldered to

ground.

Table 6.

Package Type θ

100-lead TQFP/EP 19.8 8.3 2 °C/W

JA

Typical θJA = 19.8°C/W (heat sink soldered) for multilayer

board in still air.

Typical θ

= 8.3°C/W (heat sink soldered) for multilayer board

JB

in still air.

Typical θ

= 2°C/W (junction to exposed heat sink) represents

JC

the thermal resistance through heat sink path.

Airflow increases heat dissipation, effectively reducing θ

more metal directly in contact with the package leads from

metal traces through holes, ground, and power planes reduces

the θ

. It is required that the exposed heat sink be soldered to

JA

the ground plane.

θ

JB

θ

JC

Unit

. Also,

JA

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 8 of 36

AD9446

www.BDTIC.com/ADI

TERMINOLOGY

Analog Bandwidth (Full Power Bandwidth)

The analog input frequency at which the spectral power of the

undamental frequency (as determined by the FFT analysis) is

f

reduced by 3 dB.

Minimum Conversion Rate

The clock rate at which the SNR of the lowest analog signal

frequency drops by no more than 3 dB below the guaranteed

limit.

Aperture Delay (t

The delay between the 50% point of the rising edge of the clock

nd the instant at which the analog input is sampled.

a

Aperture Uncertainty (Jitter, t

The sample-to-sample variation in aperture delay.

Clock Pulse Width and Duty Cycle

Pulse width high is the minimum amount of time that the

lock pulse should be left in the Logic 1 state to achieve rated

c

performance. Pulse width low is the minimum time the clock

pulse should be left in the low state. At a given clock rate, these

specifications define an acceptable clock duty cycle.

Differential Nonlinearity (DNL, No Missing Codes)

An ideal ADC exhibits code transitions that are exactly 1 LSB

part. DNL is the deviation from this ideal value. Guaranteed

a

no missing codes to 16-bit resolution indicates that all 65,536

codes must be present over all operating ranges.

Effective Number of Bits (ENOB)

The effective number of bits for a sine wave input at a given

put frequency can be calculated directly from its measured

in

SINAD using the following formula:

ENOB

Gain Error

The first code transition should occur at an analog value of

½ LSB above negative full scale. The last transition should occur

at an analog value of 1½ LSB below the positive full scale. Gain

error is the deviation of the actual difference between first and

last code transitions and the ideal difference between first and

last code transitions.

Integral Nonlinearity (INL)

The deviation of each individual code from a line drawn from

negative full scale through positive full scale. The point used as

negative full scale occurs ½ LSB before the first code transition.

Positive full scale is defined as a level 1½ LSB beyond the last

code transition. The deviation is measured from the middle of

each particular code to the true straight line.

Maximum Conversion Rate

The clock rate at which parametric testing is performed.

)

A

)

J

()

SINAD

=

1.76−

6.02

Offset Error

The major carry transition should occur for an analog value of

½ LSB below VIN+ = VIN−. Offset error is defined as the

deviation of the actual transition from that point.

Out-of-Range Recovery Time

The time it takes for the ADC to reacquire the analog input

after a transition from 10% above positive full scale to 10%

above negative full scale, or from 10% below negative full scale

to 10% below positive full scale.

Output Propagation Delay (tPD)

The delay between the clock rising edge and the time when all

bits are within valid logic levels.

Power-Supply Rejection Ratio

The change in full scale from the value with the supply at the

minimum limit to the value with the supply at the maximum

limit.

Signal-to-Noise and Distortion (SINAD)

The ratio of the rms input signal amplitude to the rms value of

the sum of all other spectral components below the Nyquist

frequency, including harmonics but excluding dc.

Signal-to-Noise Ratio (SNR)

The ratio of the rms input signal amplitude to the rms value of

the sum of all other spectral components below the Nyquist

frequency, excluding the first six harmonics and dc.

Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the

peak spurious spectral component. The peak spurious component

may be a harmonic. SFDR can be reported in dBc (that is, degrades

as signal level is lowered) or dBFS (always related back to converter

full scale).

Tem p er at u re Dr i ft

The temperature drift for offset error and gain error specifies

the maximum change from the initial (25°C) value to the value

at T

or T

MIN

Total Harmonic Distortion (THD)

The ratio of the rms input signal amplitude to the rms value of

the sum of the first six harmonic components.

Two -Tone SFDR

The ratio of the rms value of either input tone to the rms value

of the peak spurious component. The peak spurious component

may or may not be an IMD product.

MAX

.

Rev. 0 | Page 9 of 36

AD9446

www.BDTIC.com/ADI

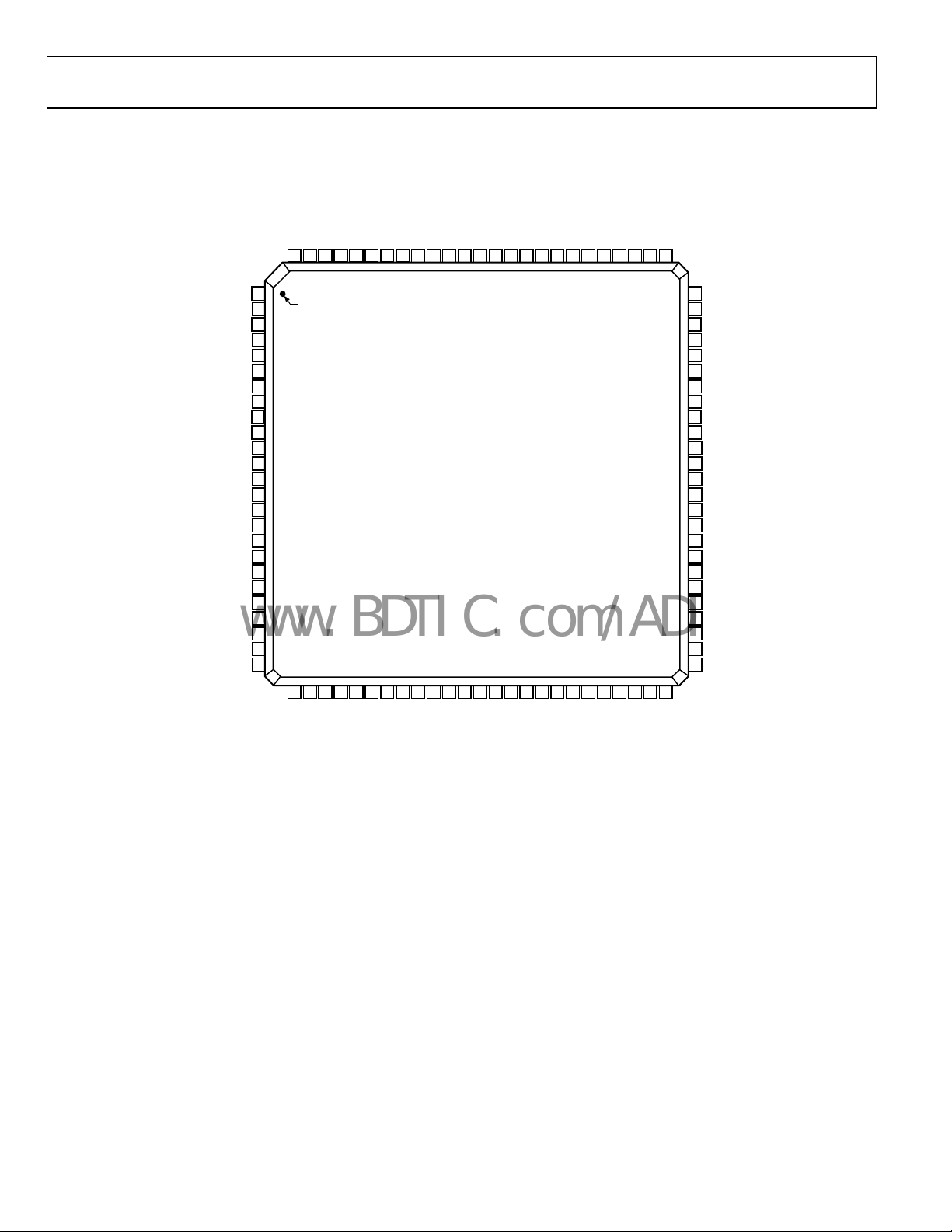

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

AGND99AGND98AGND97AVDD196AVDD195AVDD194AVDD193AVDD192AVDD191AGND90OR+89OR–88DRVDD87DRGND86D15+ (MSB)85D15–84D14+83D14–82D13+81D13–80D12+79D12–78D11+77D11–76DRVDD

100

DNC

DFS

AVDD1

SENSE

VREF

AGND

REFT

REFB

AVDD2

AVDD2

AVDD2

AVDD2

AVDD2

AVDD2

AVDD1

AVDD1

AVDD1

AGND

VIN+

VIN–

AGND

AVDD2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

DCS MODE

OUTPUT MODE

LVDS_BIAS

DNC = DO NOT CONNECT

PIN 1

AD9446

LVDS MODE

TOP VIEW

(Not to Scale)

26

AVDD227AVDD228AVDD229AVDD230AVDD231AVDD232AVDD133AVDD134AVDD135AVDD236AVDD137AVDD238AVDD1

39

40

AGND

41

CLK+

42

CLK–

AGND

Figure 4. 100-Lead TQFP/EP Pin Configuration in LVDS Mode

43

AVDD144AVDD145AVDD1

46

47

AGND

48

DRVDD

DRGND

75

DRGND

74

D10+

73

D10–

72

D9+

71

D9–

70

D8+

69

D8–

68

DCO+

67

DCO–

66

D7+

65

D7–

64

DRVDD

63

DRGND

62

D6+

61

D6–

60

D5+

59

D5–

58

D4+

57

D4–

56

D3+

55

D3–

54

D2+

53

D2–

52

D1+

51

D1–

49

50

D0+

D0– (LSB)

05490-004

Rev. 0 | Page 10 of 36

AD9446

www.BDTIC.com/ADI

Table 7. Pin Function Descriptions—100-Lead TQFP/EP in LVDS Mode

Pin No. Mnemonic Description

1 DCS MODE

2 DNC Do Not Connect. These pins should float.

3

4 DFS

5 LVDS_BIAS Set Pin for LVDS Output Current. Place 3.7 kΩ resistor terminated to DRGND.

6, 18 to 20, 32 to 34, 36, 38,

43 to 45, 92 to 97

7 SENSE

8 VREF

9, 21, 24, 39, 42, 46, 91, 98,

99, 100, Exposed Heat Sink

10 REFT

11 REFB

12 to 17, 25 to 31, 35, 37 AVDD2 5.0 V Analog Supply (±5%).

22 VIN+ Analog Input—True.

23 VIN− Analog Input—Complement.

40 CLK+ Clock Input—True.

41 CLK− Clock Input—Complement.

47, 63, 75, 87, DRGND Digital Output Ground.

48, 64, 76, 88 DRVDD 3.3 V Digital Output Supply (3.0 V to 3.6 V).

49 D0− (LSB) D0 Complement Output Bit (LVDS Levels).

50 D0+ D0 True Output Bit.

51 D1− D1 Complement Output Bit.

52 D1+ D1 True Output Bit.

53 D2− D2 Complement Output Bit.

54 D2+ D2 True Output Bit.

55 D3− D3 Complement Output Bit.

56 D3+ D3 True Output Bit.

57 D4− D4 Complement Output Bit.

58 D4+ D4 True Output Bit.

59 D5− D5 Complement Output Bit.

60 D5+ D5 True Output Bit.

61 D6− D6 Complement Output Bit.

62 D6+ D6 True Output Bit.

65 D7− D7 Complement Output Bit.

66 D7+ D7 True Output Bit.

67 DCO− Data Clock Output—Complement.

68 DCO+ Data Clock Output—True.

69 D8− D8 Complement Output Bit.

70 D8+ D8 True Output Bit.

71 D9− D9 Complement Output Bit.

72 D9+ D9 True Output Bit.

73 D10− D10 Complement Output Bit.

74 D10+ D10 True Output Bit.

77 D11− D11 Complement Output Bit.

78 D11+ D11 True Output Bit.

OUTPUT

MODE

AVDD1 3.3 V (±5%) Analog Supply.

AGND

Clock Duty Cycle Stabilizer (DCS) Control Pin. CMOS compatible. DCS = low (AGND) to enable

ecommended); DCS = high (AVDD1) to disable DCS.

DCS (r

CMOS-Compatible Output Logic Mode Control Pin. OUTPUT MODE = 0 for CMOS mode;

OUTPUT MODE

Data Format Select Pin. CMOS control pin that det

high (AVDD1) for twos complement; DFS = low (ground) for offset binary format.

Reference Mode Selection. Connect to AGND for internal 1.6 V reference (3.2 V p-p analog

ange); connect to AVDD1 for external reference.

input r

1.6 V Reference I/O. Function dependent on SENSE and ex

Decouple to ground with 0.1 µF and 10 µF capacitors.

Analog Ground. The exposed heat sink on the bottom of the package must be connected to

AG

ND.

Differential Reference Output. Decoupled to ground with 0.1 µF

with 0.1 µF and 10 µF capacitors.

Differential Reference Output. Decoupled to ground with a 0.1 µ

(Pin 10) with 0.1 µF and 10 µF capacitors.

= 1 (AVDD1) for LVDS outputs.

ermines the format of the output data. DFS =

ternal programming resistors.

capacitor and to REFB (Pin 11)

F capacitor and to REFT

Rev. 0 | Page 11 of 36