Page 1

A

HDMI™ Display Interface

FEATURES

Internal HDCP keys

HDMI interface

Supports high bandwidth digital content protection

RGB to YCbCr 2-way color conversion

1.8 V/3.3 V power supply

100-lead Pb-free LQFP

RGB and YCbCr output formats

Digital video interface

HDMI 1.1, DVI 1.0

150 MHz HDMI receiver

Supports high bandwidth digital content protection

(HDCP 1.1)

Digital audio interface

HDMI 1.1-compatible audio interface

S/PDIF (IEC90658-compatible) digital audio output

Multichannel I

APPLICATIONS

Advanced TVs

HDTVs

Projectors

LCD monitors

GENERAL DESCRIPTION

2

S audio output (up to 8 channels)

SCL

SDA

Rx0+

Rx0–

Rx1+

Rx1–

Rx2+

Rx2–

RxC+

RxC–

RTERM

DDCSD

DDCSCL

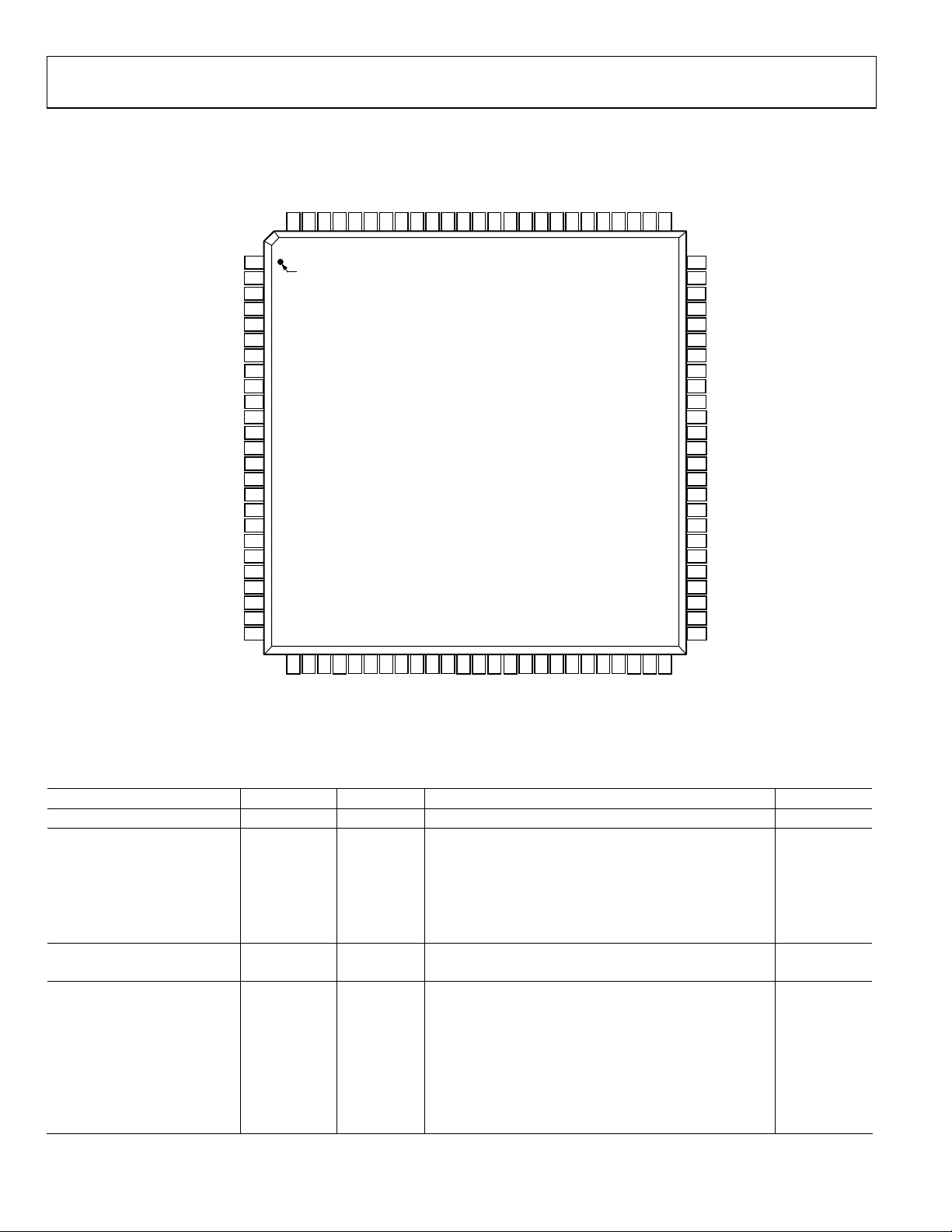

AD9381

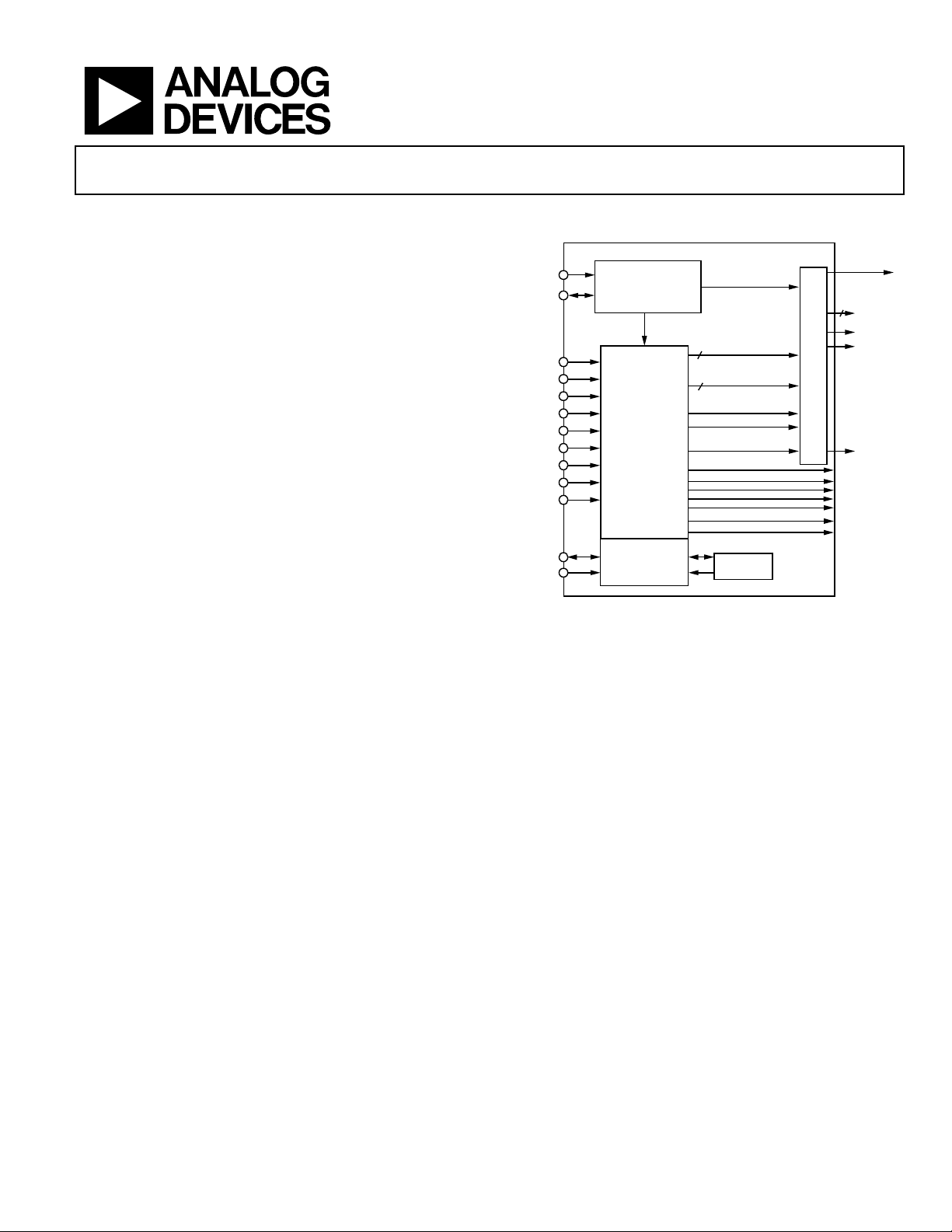

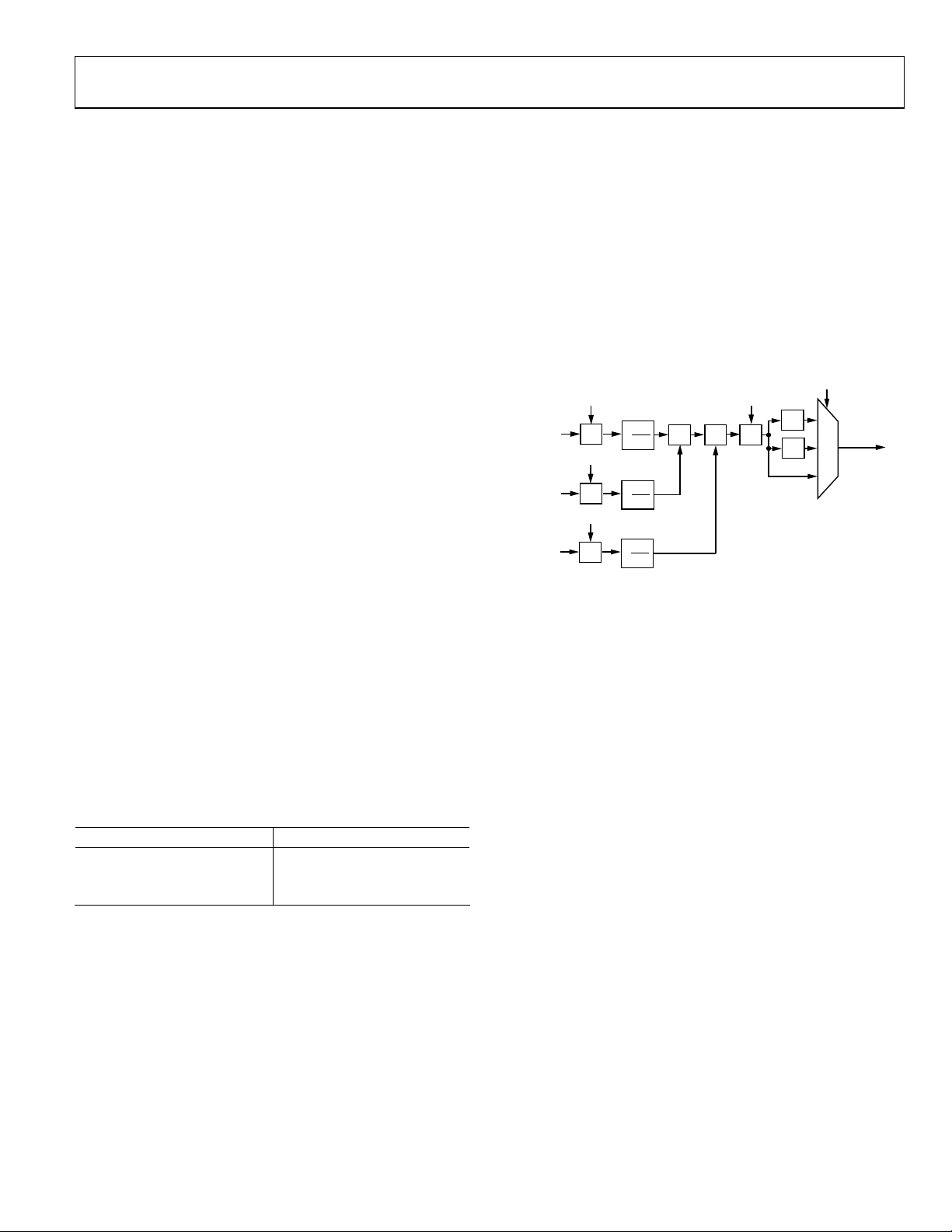

FUNCTIONAL BLOCK DIAGRAM

SERIAL REGISTER

AND

POWER MANAGEMENT

R/G/B 8 × 3

OR YCbCr

DATACK

HDMI RECEIVER

HDCP

2

HSYNC

VSYNC

DE

HDCP KEYS

Figure 1.

RGB ↔YCbCr

AD9381

R/G/B 8 × 3

YCbCr (4:2:2

OR 4:4:4)

2

COLORSPACE CONVERTER

S/PDIF

8-CHANNEL

2

I

S

MCLK

LRCLK

DATACK

HSOUT

VSOUT

DE

05689-001

The AD9381 offers a high definition multimedia interface

(HDMI) receiver integrated on a single chip. Also included is

support for high bandwidth digital content protection (HDCP)

via an internal key storage.

The AD9381 contains an HDMI 1.0-compatible receiver and

supports all HDTV formats (up to 1080p) and display

resolutions up to SXGA (1280×1024 @ 75 Hz). The receiver

features an intrapair skew tolerance of up to one full clock cycle.

With the inclusion of HDCP, displays may now receive

encrypted video content. The AD9381 allows for authentication

of a video receiver, decryption of encoded data at the receiver,

and renewability of that authentication during transmission as

specified by the HDCP 1.1 protocol.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Fabricated in an advanced CMOS process, the AD9381 is

provided in a space-saving, 100-lead, surface-mount, Pb-free

plastic LQFP and is specified over the 0°C to 70°C temperature

range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

Page 2

AD9381

TABLE OF CONTENTS

Features.............................................................................................. 1

4:4:4 to 4:2:2 Filter...................................................................... 11

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Specifications..................................................................................... 3

Electrical Characteristics ............................................................. 3

Digital Interface Electrical Characteristics ............................... 3

Absolute Maximum Ratings............................................................ 5

Explanation of Test Levels ........................................................... 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Design Guide..................................................................................... 9

General Description..................................................................... 9

Digital Inputs ................................................................................ 9

Serial Control Port ....................................................................... 9

Output Signal Handling............................................................... 9

Audio PLL Setup......................................................................... 12

Audio Board Level Muting........................................................ 13

Output Data Formats................................................................. 13

2-Wire Serial Register Map........................................................... 14

2-Wire Serial Control Register DetailS........................................ 26

Chip Identification..................................................................... 26

BT656 Generation...................................................................... 28

Macrovision................................................................................. 29

Color Space Conversion............................................................ 30

2-Wire Serial Control Port............................................................ 37

Data Transfer via Serial Interface............................................. 37

Serial Interface Read/Write Examples..................................... 38

PCB Layout Recommendations.................................................... 39

Power Supply Bypassing............................................................ 39

Outputs (Both Data and Clocks).............................................. 39

Timing.............................................................................................. 10

VSYNC Filter and Odd/Even Fields ........................................ 10

HDMI Receiver........................................................................... 10

DE Generator.............................................................................. 10

REVISION HISTORY

10/05—Revision 0: Initial Version

Digital Inputs .............................................................................. 39

Color Space Converter (CSC) Common Settings...................... 40

Outline Dimensions....................................................................... 42

Ordering Guide .......................................................................... 42

Rev. 0 | Page 2 of 44

Page 3

AD9381

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VDD, VD = 3.3 V, DVDD = PVDD = 1.8 V, ADC clock = maximum.

Table 1.

AD9381KSTZ-100 AD9381KSTZ-150

Parameter Temp Test Level Min Typ Max Min Typ Max Unit

DIGITAL INPUTS (5 V Tolerant)

Input Voltage, High (VIH) Full VI 2.6 2.6 V

Input Voltage, Low (VIL) Full VI 0.8 0.8 V

Input Current, High (IIH) Full V −82 −82 μA

Input Current, Low (IIL) Full V 82 82 μA

Input Capacitance 25°C V 3 3 pF

DIGITAL OUTPUTS

Output Voltage, High (VOH) Full VI VDD − 0.1 VDD − 0.1 V

Output Voltage, Low (VOL) Full VI 0.4 0.4 V

Duty Cycle, DATACK Full V 45 50 55 45 50 55 %

Output Coding Binary Binary

THERMAL CHARACTERISTICS

θJA-Junction-to-Ambient V 35 35 °C/W

DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS

VDD = VD = 3.3 V, DVDD = PVDD = 1.8 V, ADC clock = maximum.

Table 2.

AD9381KSTZ-100

Parameter Test Level Conditions Min Typ Max Min Typ Max Unit

RESOLUTION 8 8 Bit

DC DIGITAL I/O Specifications

High-Level Input Voltage, (VIH) VI 2.5 2.5 V

Low-Level Input Voltage, ( VIL) VI 0.8 0.8 V

High-Level Output Voltage, (VOH) VI VDD − 0.1 V

Low-Level Output Voltage, (VOL) VI VDD − 0.1 0.1 0.1 V

DC SPECIFICATIONS

Output High Level IV Output drive = high 36 36 mA

I

, (V

OHD

= VOH) IV Output drive = low 24 24 mA

OUT

Output Low Level IV Output drive = high 12 12 mA

I

, (V

OLD

= VOL) IV Output drive = low 8 8 mA

OUT

DATACK High Level IV Output drive = high 40 40 mA

V

, (V

OHC

= VOH) IV Output drive = low 20 20 mA

OUT

DATACK Low Level IV Output drive = high 30 30 mA

V

, (V

OLC

Differential Input Voltage, Single-

= VOL) IV Output drive = low 15 15 mA

OUT

IV 75 700 75 700 mV

Ended Amplitude

POWER SUPPLY

VD Supply Voltage IV 3.15 3.3 3.47 3.15 3.3 3.47 V

VDD Supply Voltage IV 1.7 3.3 347 1.7 3.3 347 V

DVDD Supply Voltage IV 1.7 1.8 1.9 1.7 1.8 1.9 V

PVDD Supply Voltage IV 1.7 1.8 1.9 1.7 1.8 1.9 V

IVD Supply Current (Typical Pattern)1 V 80 100 80 110 mA

I

Supply Current (Typical

VDD

Pattern)

2

V 40 100

AD9381KSTZ-150

3

55 1753 mA

Rev. 0 | Page 3 of 44

Page 4

AD9381

AD9381KSTZ-100

Parameter Test Level Conditions Min Typ Max Min Typ Max Unit

I

Supply Current (Typical

DVDD

Pattern)

I

PVDD

Pattern)

1, 4

Supply Current (Typical

1

V 88 110 110 145 mA

V 26 35 30 40 mA

Power-Down Supply Current (IPD) VI 130 130 mA

AC SPECIFICATIONS

Intrapair (+ to −) Differential Input

DPS

)

Skew (T

Channel to Channel Differential

Input Skew (T

CCS

)

Low-to-High Transition Time for

Data and Controls (D

LHT

)

IV

Low-to-High Transition Time for

DATACK (D

LHT

)

IV

High-to-Low Transition Time for

Data and Controls (D

HLT

)

IV

High-to-Low Transition Time for

DATACK (D

HLT

)

IV

Clock to Data Skew5 (T

Duty Cycle, DATACK

DATACK Frequency (F

1

The typical pattern contains a gray scale area, output drive = high. Worst-case pattern is alternating black and white pixels.

2

The typical pattern contains a gray scale area, output drive = high.

3

Specified current and power values with a worst-case pattern (on/off).

4

DATACK load = 10 pF, data load = 5 pF.

5

Drive strength = high.

) IV –0.5 +2.0 –0.5 +2.0 ns

SKEW

5

) VI 20 150 MHz

CIP

IV 360 ps

IV 6

IV

IV

IV

IV

Output drive = high;

= 10 pF

C

L

Output drive = low;

= 5 pF

C

L

Output drive = high;

C

= 10 pF

L

Output drive = low;

= 5 pF

C

L

Output drive = high;

= 10 pF

C

L

Output drive = low;

C

= 5 pF

L

Output drive = high;

= 10 pF

C

L

Output drive = low;

C

= 5 pF

L

900 ps

1300 ps

650 ps

1200 ps

850 ps

1250 ps

800 ps

1200 ps

IV 45 50 55 %

AD9381KSTZ-150

Clock

Period

Rev. 0 | Page 4 of 44

Page 5

AD9381

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

VD 3.6 V

VDD 3.6 V

DVDD 1.98 V

PVDD 1.98 V

Analog Inputs VD to 0.0 V

Digital Inputs 5 V to 0.0 V

Digital Output Current 20 mA

Operating Temperature Range −25°C to +85°C

Storage Temperature Range −65°C to +150°C

Maximum Junction Temperature 150°C

Maximum Case Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

EXPLANATION OF TEST LEVELS

Table 4.

Level Test

I 100% production tested.

II

III Sample tested only.

IV

V Parameter is a typical value only.

VI

100% production tested at 25°C and sample tested at

specified temperatures.

Parameter is guaranteed by design and

characterization testing.

100% production tested at 25°C; guaranteed by design

and characterization testing.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 5 of 44

Page 6

AD9381

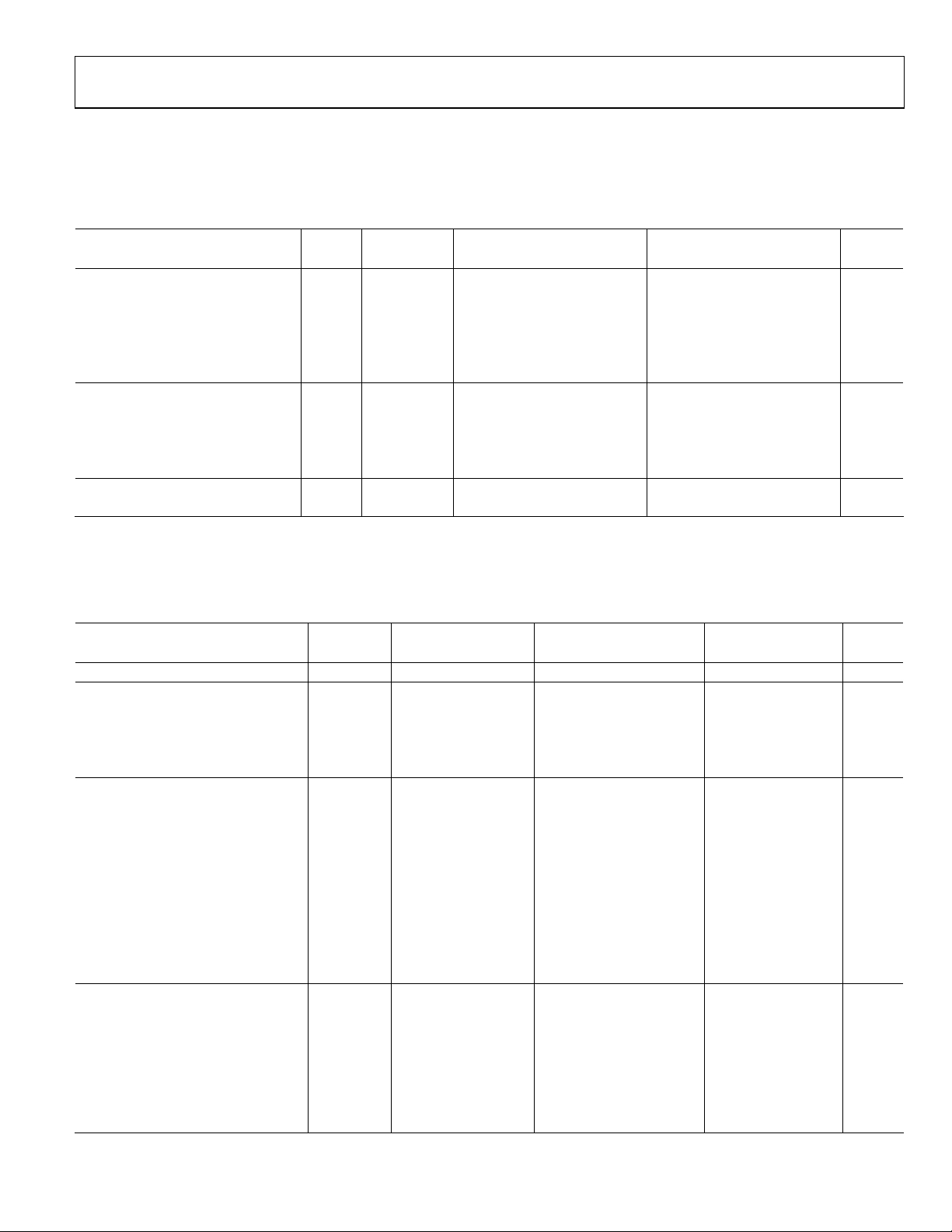

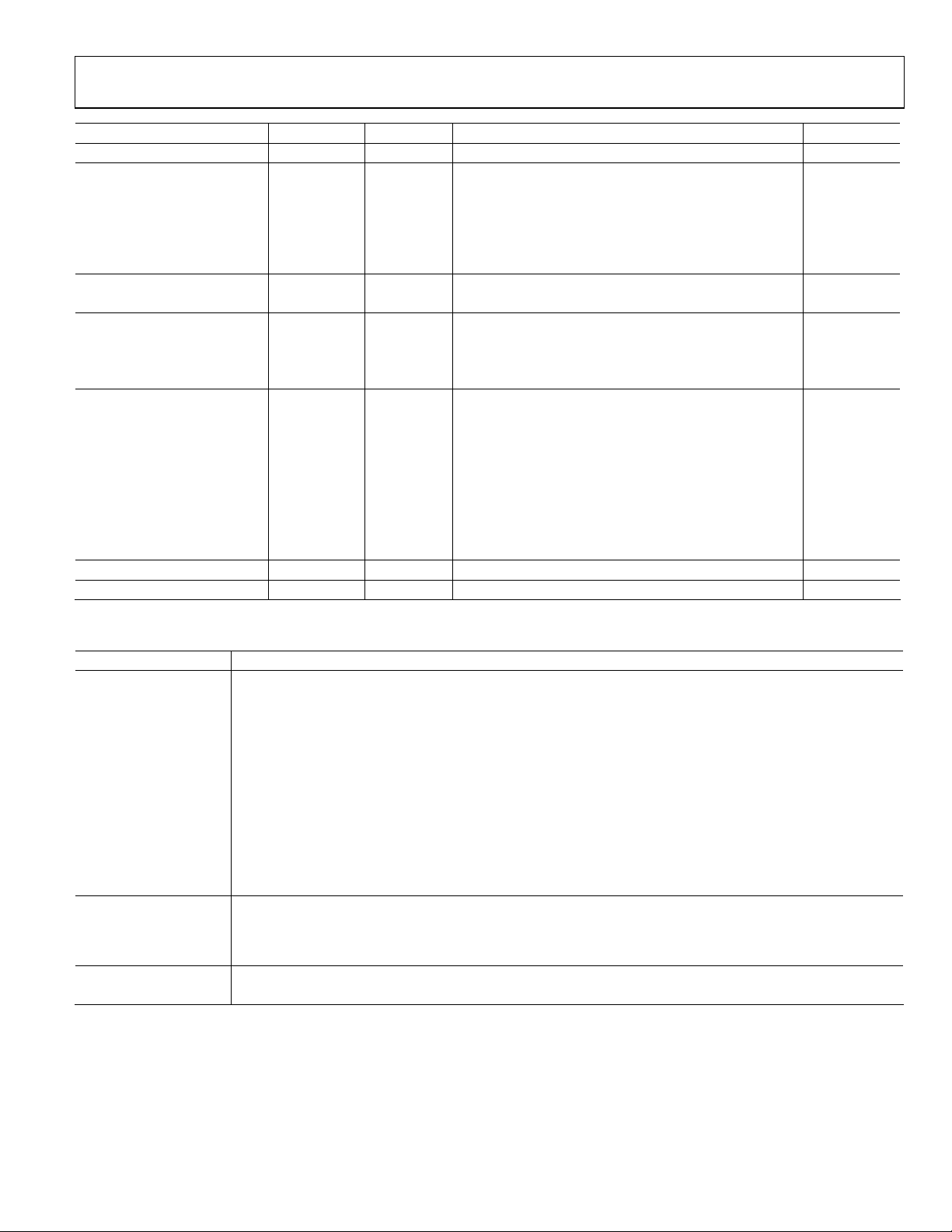

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

GND

GREEN 7

GREEN 6

GREEN 5

GREEN 4

GREEN 3

GREEN 2

GREEN 1

GREEN 0

V

DD

GND

BLUE 7

BLUE 6

BLUE 5

BLUE 4

BLUE 3

BLUE 2

BLUE 1

BLUE 0

MCLKIN

MCLKOUT

SCLK

LRCLK

I2S3

I2S2

VDDRED 0

RED 1

RED 2

RED 3

RED 4

RED 5

RED 6

RED 7

GND

VDDDATACKDEHSOUT

99

98

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

PIN 1

95

93

97

96

92

94

898887

91

90

AD9381

TOP VIEW

(Not to Scale)

SOGOUT

VSOUT

86

85

O/E FIELD

SDA

SCL

84

82

83

PWRDN

81

VDNC

80

79

GNDNCV

787776

D

75

GND

74

NC

73

NC

72

V

D

71

NC

70

NC

69

GND

68

NC

67

V

D

66

NC

65

GND

64

GND

63

GND

62

GND

61

GND

60

GND

59

PV

DD

58

GND

57

FILT

56

PV

DD

55

GND

54

PV

DD

53

GND

52

PU1

51

PU2

NC = NO CONNECT

27

26

28

S1

S0

2

2

I

I

S/PDIF

29

GND

30

DV

31

33

34

32

D

DD

DD

V

GND

Rx0–

DV

35

Rx0+

36

GND

37

38

39

42

44

GND

45

43

V

RxC–

RxC+

40

41

GND

Rx1–

Rx2–

Rx1+

Rx2+

48

49

47

GND

DV

50

DD

DDCSCL

DDCSDA

05689-002

46

D

RTERM

Figure 2. Pin Configuration

Table 5. Complete Pinout List

Pin Type Pin No. Mnemonic Function Value

INPUTS 81 PWRDN Power-Down Control 3.3 V CMOS

DIGITAL VIDEO DATA INPUTS 35 Rx0+ Digital Input Channel 0 True TMDS

34 Rx0− Digital Input Channel 0 Complement TMDS

38 Rx1+ Digital Input Channel 1 True TMDS

37 Rx1− Digital Input Channel 1 Complement TMDS

41 Rx2+ Digital Input Channel 2 True TMDS

40 Rx2− Digital Input Channel 2 Complement TMDS

DIGITAL VIDEO CLOCK INPUTS 43 RxC+ Digital Data Clock True TMDS

44 RxC− Digital Data Clock Complement TMDS

OUTPUTS 92 to 99 RED [7:0] Outputs of Red Converter, Bit 7 is MSB VDD

2 to 9 GREEN [7:0] Outputs of Green Converter, Bit 7 is MSB VDD

12 to 19 BLUE [7:0] Outputs of Blue Converter, Bit 7 is MSB VDD

89 DATACK Data Output Clock VDD

87 HSOUT HSYNC Output Clock (Phase-Aligned with DATACK) VDD

85 VSOUT VSYNC Output Clock (Phase-Aligned with DATACK) VDD

86 SOGOUT SOG Slicer Output VDD

84 O/E FIELD Odd/Even Field Output VDD

Rev. 0 | Page 6 of 44

Page 7

AD9381

Pin Type Pin No. Mnemonic Function Value

REFERENCES 57 FILT Connection for External Filter Components for Audio PLL PVDD

POWER SUPPLY

100, 90, 10 VDD Output Power Supply 1.8 V to 3.3 V

59, 56, 54 PVDD PLL Power Supply 1.8 V

48, 32, 30 DVDD Digital Logic Power Supply 1.8 V

GND Ground 0 V

CONTROL 83 SDA Serial Port Data I/O 3.3 V CMOS

82 SCL Serial Port Data Clock 3.3 V CMOS

HDCP 49 DDCSCL HDCP Slave Serial Port Data Clock 3.3 V CMOS

50 DDCSDA HDCP Slave Serial Port Data I/O 3.3 V CMOS

51 PU2 This should be pulled up to 3.3 V through a 10 kΩ resistor 3.3 V CMOS

52 PU1 This should be pulled up to 3.3 V through a 10 kΩ resistor 3.3 V CMOS

AUDIO DATA OUTPUTS 28 S/PDIF S/PDIF Digital Audio Output VDD

27 I2S0 I2S Audio (Channel 1, Channel 2) VDD

26 I2S1 I2S Audio (Channels 3, Channel 4) VDD

25 I2S2 I2S Audio (Channels 5, Channel 6) VDD

24 I2S3 I2S Audio (Channels 7, Channel 8) VDD

20 MCLKIN External Reference Audio Clock In VDD

21 MCLKOUT Audio Master Clock Output VDD

22 SCLK Audio Serial Clock Output VDD

23 LRCLK Data Output Clock for Left and Right Audio Channels VDD

DATA ENABLE 88 DE Data Enable 3.3 V CMOS

RTERM 46 RTERM Sets Internal Termination Resistance 500 Ω

80, 76, 72, 67,

45, 33

Table 6. Pin Function Descriptions

Mnemonic Description

INPUTS

Rx0+ Digital Input Channel 0 True.

Rx0− Digital Input Channel 0 Complement.

Rx1+ Digital Input Channel 1 True.

Rx1− Digital Input Channel 1 Complement.

Rx2+ Digital Input Channel 2 True.

Rx2− Digital Input Channel 2 Complement.

These six pins receive three pairs of transition minimized differential signaling (TMDS) pixel data (at 10× the pixel

rate) from a digital graphics transmitter.

RxC+ Digital Data Clock True.

RxC− Digital Data Clock Complement.

This clock pair receives a TMDS clock at 1× pixel data rate.

FILT External Filter Connection.

PWRDN Power-Down Control/Three-State Control.

For proper operation, the audio clock generator PLL requires an external filter. Connect the filter shown in

Figure 8 to this pin. For optimal performance, minimize noise and parasitics on this node. For more information

see the

PCB Layout Recommendations section .

The function of this pin is programmable via Register 0x26 [2:1].

Analog Power Supply and DVI Terminators 3.3 V

V

D

Rev. 0 | Page 7 of 44

Page 8

AD9381

Mnemonic Description

OUTPUTS

HSOUT Horizontal Sync Output.

A reconstructed and phase-aligned version of the HSYNC input. Both the polarity and duration of this output can

be programmed via serial bus registers. By maintaining alignment with DATACK and Data, data timing with

respect to horizontal sync can always be determined.

VSOUT Vertical Sync Output.

The separated VSYNC from a composite signal or a direct pass through of the VSYNC signal. The polarity of this

output can be controlled via the serial bus bit (Register 0x24[6]).

O/E FIELD

SERIAL PORT

SDA Serial Port Data I/O for Programming AD9381 Registers—I2C Address is 0x98.

SCL Serial Port Data Clock for Programming AD9381 Registers.

DDCSDA Serial Port Data I/O for HDCP Communications to Transmitter—I2C Address is 0x74 or 0x76.

DDCSCL Serial Port Data Clock for HDCP Communications to Transmitter.

PU2 This should be pulled up to 3.3 V through a 10 kΩ resistor.

PU1 This should be pulled up to 3.3 V through a 10 kΩ resistor.

DATA OUTPUTS

Red [7:0] Data Output, Red Channel.

Green [7:0] Data Output, Green Channel.

Blue [7:0] Data Output, Blue Channel.

DATA CLOCK OUTPUT

DATACK Data Clock Output.

POWER SUPPLY

1

VD (3.3 V) Analog Power Supply.

VDD (1.8 V to 3.3 V)

PVDD (1.8 V) Clock Generator Power Supply.

DVDD (1.8 V) Digital Input Power Supply.

GND Ground.

1

The supplies should be sequenced such that VD and VDD are never less than 300 mV below DVDD. At no time should DVDD be more than 300 mV greater than VD or V

Odd/Even Field Bit for Interlaced Video. This output identifies whether the current field (in an interlaced signal) is

odd or even. The polarity of this signal is programmable via Register 0x24[4].

The main data outputs. Bit 7 is the MSB. The delay from pixel sampling time to output is fixed, but will be

different if the color space converter is used. When the sampling time is changed by adjusting the phase register,

the output timing is shifted as well. The DATACK and HSOUT outputs are also moved, so the timing relationship

among the signals is maintained.

This is the main clock output signal used to strobe the output data and HSOUT into external logic. Four possible

output clocks can be selected with Register 0x25[7:6]. These are related to the pixel clock (1/2× pixel clock, 1×

pixel clock, 2× frequency pixel clock, and a 90° phase shifted pixel clock). They are produced either by the

internal PLL clock generator or EXTCLK and are synchronous with the pixel sampling clock. The polarity of

DATACK can also be inverted via Register 0x24[0]. The sampling time of the internal pixel clock can be changed

by adjusting the phase register. When this is changed, the pixel-related DATACK timing is shifted as well. The

DATA, DATACK, and HSOUT outputs are all moved, so the timing relationship among the signals is maintained.

These pins supply power to the ADCs and terminators. They should be as quiet and filtered as possible.

Digital Output Power Supply.

A large number of output pins (up to 27) switching at high speed (up to 150 MHz) generates many power supply

transients (noise). These supply pins are identified separately from the V

pins so special care can be taken to

D

minimize output noise transferred into the sensitive analog circuitry. If the AD9381 is interfacing with lower

voltage logic, V

may be connected to a lower supply voltage (as low as 1.8 V) for compatibility.

DD

The most sensitive portion of the AD9381 is the clock generation circuitry. These pins provide power to the clock

PLL and help the user design for optimal performance. The designer should provide quiet, noise-free power to

these pins.

This supplies power to the digital logic.

The ground return for all circuitry on chip. It is recommended that the AD9381 be assembled on a single solid

ground plane, with careful attention to ground current paths.

DD.

Rev. 0 | Page 8 of 44

Page 9

AD9381

DESIGN GUIDE

GENERAL DESCRIPTION

The AD9381 is a fully integrated solution for receiving DVI/

HDMI signals and is capable of decoding HDCP-encrypted

signals through connections to an internal EEPROM. The

circuit is ideal for providing an interface for HDTV monitors

or as the front end to high performance video scan converters.

SERIAL CONTROL PORT

The serial control port is designed for 3.3 V logic. However, it is

tolerant of 5 V logic signals.

OUTPUT SIGNAL HANDLING

The digital outputs operate from 1.8 V to 3.3 V (VDD).

Implemented in a high performance CMOS process, the

interface can capture signals with pixel rates of up to 150 MHz.

The AD9381 includes all necessary circuitry for decoding

TMDS signaling including those encrypted with HDCP. The

output data formatting includes a color space converter (CSC),

which accommodates any input color space and can output any

color space. All controls are programmable via a 2-wire serial

interface. Full integration of these sensitive mixed signal

functions makes system design straight-forward and less

sensitive to the physical and electrical environment.

DIGITAL INPUTS

The digital control inputs (I2C) on the AD9381 operate to 3.3 V

CMOS levels. In addition, all digital inputs, except the TMDS

(HDMI/DVI) inputs, are 5 V tolerant (applying 5 V to them

does not cause damage). The TMDS input pairs (Rx0+/Rx0−,

Rx1+/Rx1−, Rx2+/Rx2−, and RxC+/RxC−) must maintain a

100 Ω differential impedance (through proper PCB layout)

from the connector to the input where they are internally

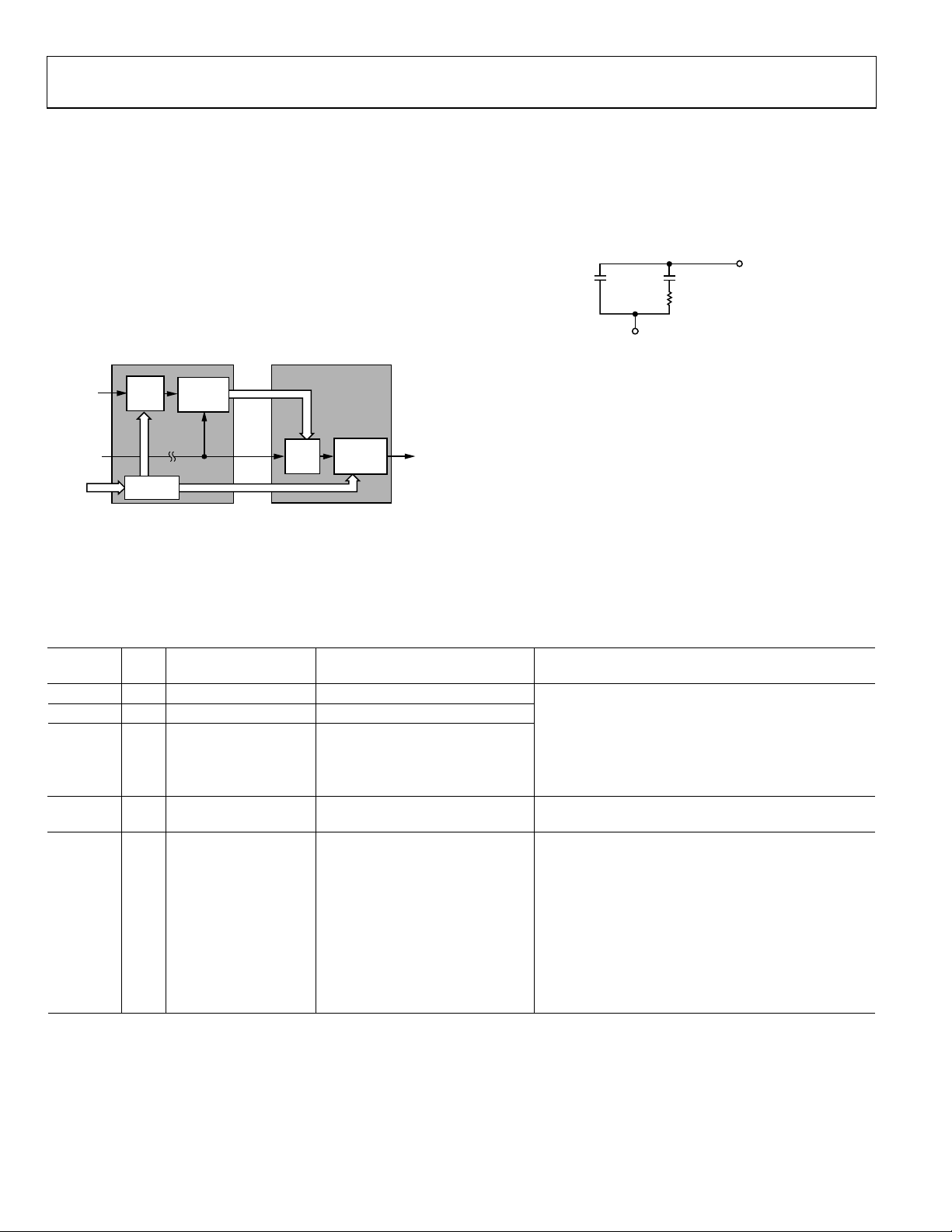

Power Management

The AD9381 uses the activity detect circuits, the active interface

bits in the serial bus, the active interface override bits, the

power-down bit, and the power-down pin to determine the

correct power state. There are four power states: full-power,

seek mode, auto power-down, and power-down.

Tabl e 7 summarizes how the AD9381 determines which power

mode to use and which circuitry is powered on/off in each of

these modes. The power-down command has priority and then

the automatic circuitry. The power-down pin (Pin 81—polarity

set by Register 0x26[3]) can drive the chip into four powerdown options. Bit 2 and Bit1 of Register 0x26 control these four

options. Bit 0 controls whether the chip is powered down or the

outputs are placed in high impedance mode (with the exception

of SOG). Bit 7 to Bit 4 of Register 0x26 control whether the

outputs, SOG, Sony Philips digital interface (S/PDIF ) or InterIC sound bus (I

or not. See the

2

S or IIS) outputs are in high impedance mode

2-Wire Serial Control Register Detail section for

more details.

terminated (50 Ω to 3.3 V). If additional ESD protection is

desired, use of a California Micro Devices (CMD) CM1213

(among others) series low capacitance ESD protection offers

8 kV of protection to the HDMI TMDS lines.

Table 7. Power-Down Mode Descriptions

Mode Power-Down

Full Power 1 1 X Everything

Seek Mode 1 0 0 Everything

Seek Mode 1 0 1 Serial bus, sync activity detect, SOG, band gap reference

Power-Down 0 X Serial bus, sync activity detect, SOG, band gap reference

1

Power-down is controlled via Bit 0 in Serial Bus Register 0x26.

2

Sync detect is determined by OR’ing Bits 7 to Bit 2 in Serial Bus Register 0x15.

3

Auto power-down is controlled via Bit 7 in Serial Bus Register 0x27.

1

Inputs

Sync Detect

2

Auto PD Enable

3

Power-On or Comments

Rev. 0 | Page 9 of 44

Page 10

AD9381

K

T

T

TIMING

The output data clock signal is created so that its rising edge

always occurs between data transitions and can be used to latch

the output data externally.

Figure 3 shows the timing operation of the AD9381.

t

PER

t

DCYCLE

DATAC

t

SKEW

DATA

HSOUT

05689-003

Figure 3. Output Timing

VSYNC FILTER AND ODD/EVEN FIELDS

The VSYNC filter eliminates spurious VSYNCs, maintains a

consistent timing relationship between the VSYNC and HSYNC

output signals, and generates the odd/even field output.

The filter works by examining the placement of VSYNC

with respect to HSYNC and, if necessary, slightly shifting

it in time at the VSOUT output. The goal is to keep the

VSYNC and HSYNC leading edges from switching at the

same time, eliminating confusion as to when the first line

of a frame occurs. Enabling the VSYNC filter is done with

Register 0x21[5]. Use of the VSYNC filter is recommended for

all cases, including interlaced video, and is required when using

the HSYNC per VSYNC counter.

illustrate even/odd field determination in two situations.

SYNC SEPARATOR THRESHOLD

FIELD 1 FIELD 0

QUADRAN

VSOUT

O/E FIELD

23 21431

HSIN

VSIN

Figure 4 and Figure 5

FIELD 1 FIELD 0

4

EVEN FIELD

Figure 4.

05689-004

SYNC SEPARATOR THRESHOLD

FIELD 1 FIELD 0

QUADRAN

HSIN

VSIN

VSYOUT

O/E FIELD

FIELD 1 FIELD 0

23 214431

ODD FIELD

Figure 5. VSYNC Filter—Odd/Even

HDMI RECEIVER

The HDMI receiver section of the AD9381 allows the reception

of a digital video stream, which is backward compatible with

DVI and able to accommodate not only video of various formats (RGB, YCrCb 4:4:4, 4:2:2), but also up to eight channels of

audio. Infoframes are transmitted carrying information about

the video format, audio clocks, and many other items necessary

for a monitor to use fully the information stream available.

The earlier digital visual interface (DVI) format was restricted

to an RGB 24-bit color space only. Embedded in this data

stream were HSYNCs, VSYNCs, and display enable (DE)

signals, but no audio information. The HDMI specification

allows transmission of all the DVI capabilities, but adds several

YCrCb formats that make the inclusion of a programmable

color space converter (CSC) a very desirable feature. With this,

the scaler following the AD9381 can specify that it always

wishes to receive a particular format—for instance, 4:2:2

YCrCb—regardless of the transmitted mode. If RGB is sent, the

CSC can easily convert that to 4:2:2 YCrCb while relieving the

scaler of this task.

In addition, the HDMI specification supports the transmission

of up to eight channels of S/PDIF or I

2

S audio. The audio

information is packetized and transmitted during the video

blanking periods along with specific information about the

clock frequency. Part of this audio information (audio

Infoframe) tells the user how many channels of audio are being

transmitted, where they should be placed, information

regarding the source (make, model), and other data.

DE GENERATOR

The AD9381 has an onboard generator for DE, for start of

active video (SAV) and for end of active video (EAV), all of

which is necessary for describing the complete data stream for a

BT656-compatible output. In addition to this particular output,

it is possible to generate the DE for cases in which a scaler is not

used. This signal alerts the following circuitry as to which are

displayable video pixels.

05689-005

Rev. 0 | Page 10 of 44

Page 11

AD9381

G

4:4:4 TO 4:2:2 FILTER

The AD9381 contains a filter that allows it to convert a signal

from YCrCb 4:4:4 to YCrCb 4:2:2 while maintaining the

maximum accuracy and fidelity of the original signal.

Input Color Space to Output Color Space

The AD9381 can accept a wide variety of input formats and

either retain that format or convert to another. Input formats

supported are:

• 4:4:4 YCrCb 8-bit

• 4:2:2 YCrCb 8-bit, 10-bit, and 12-bit

• RGB 8-bit

Output modes supported are:

• 4:4:4 YCrCb 8-bit

• 4:2:2 YCrCb 8-bit, 10-bit, and 12-bit

• Dual 4:2:2 YCrCb 8-bit

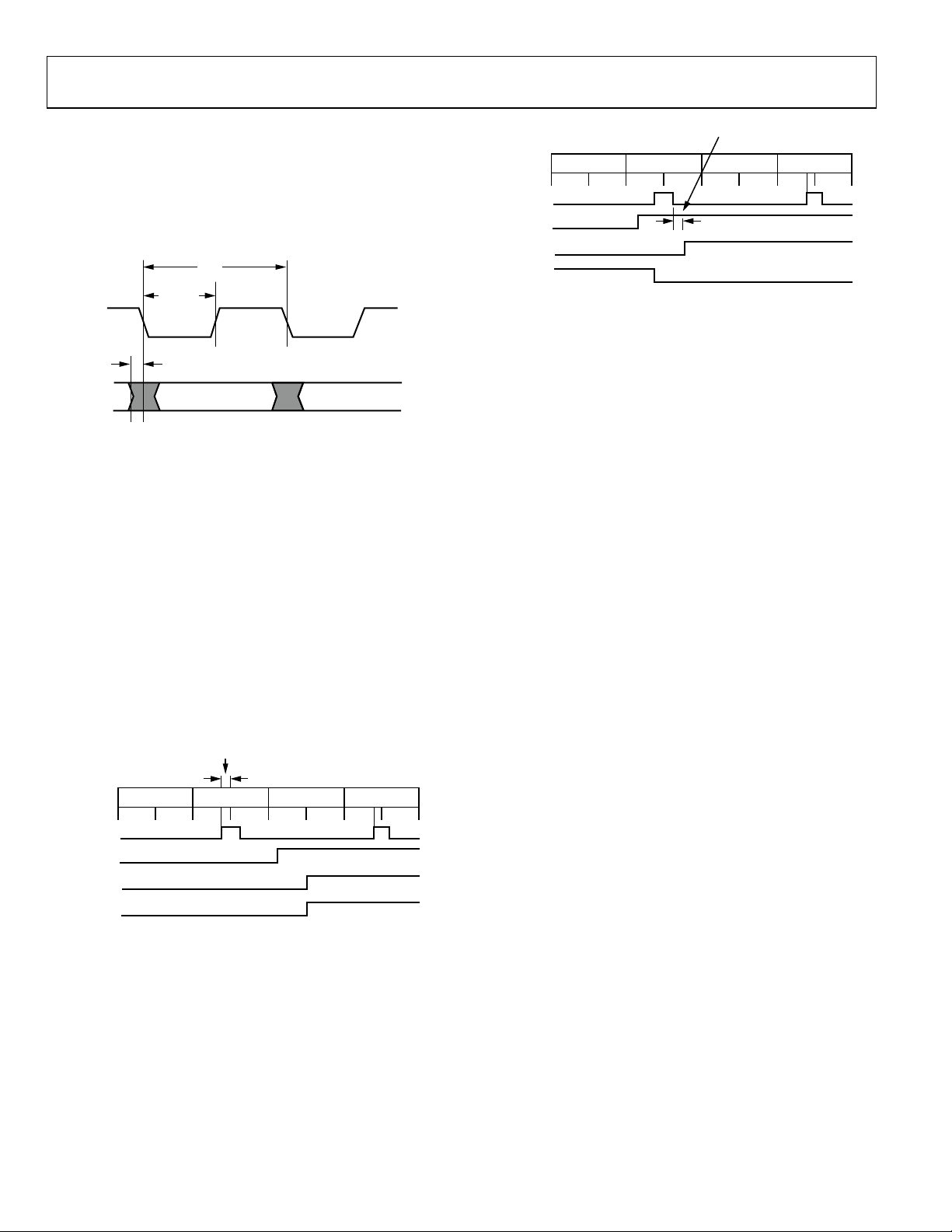

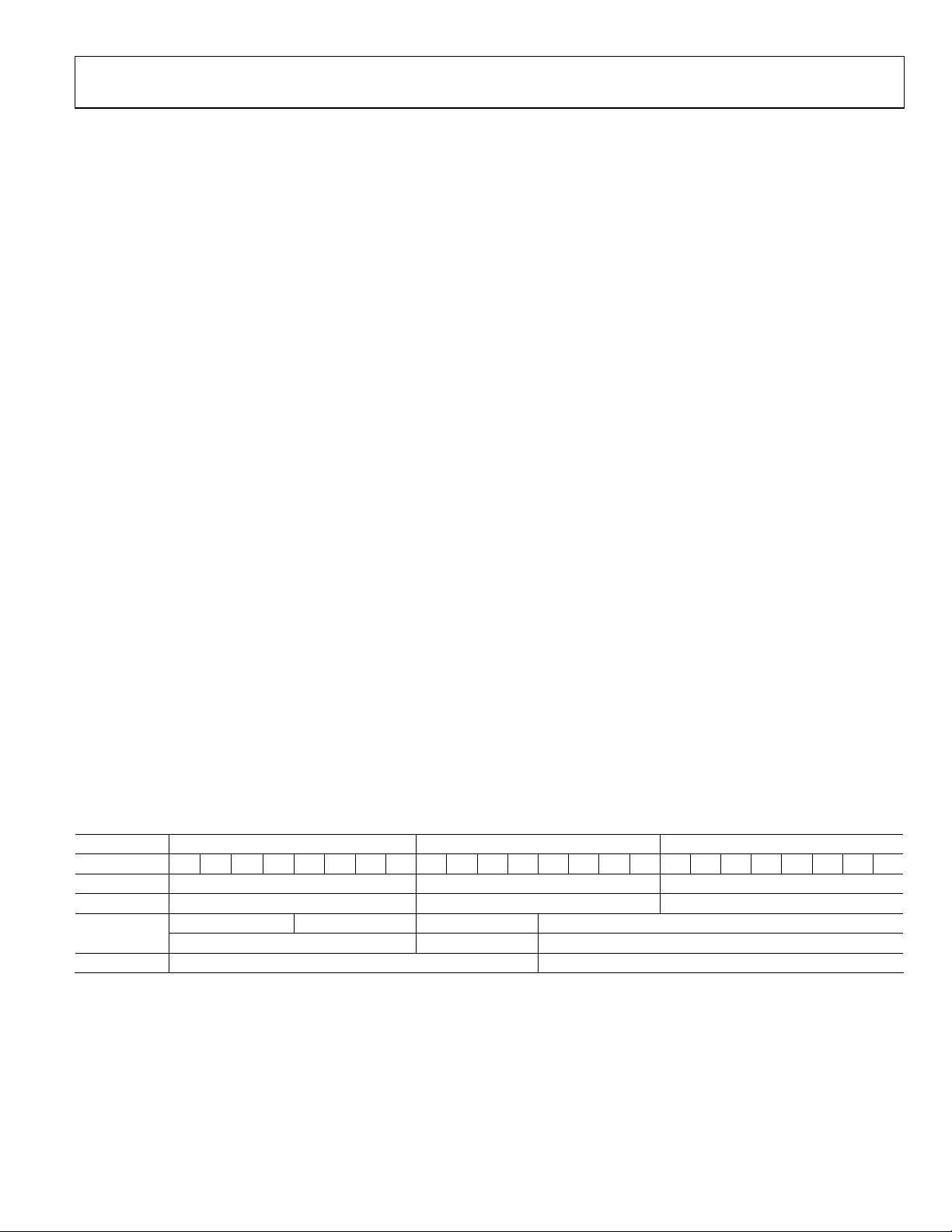

Color Space Conversion (CSC) Matrix

The CSC matrix in the AD9381 consists of three identical

processing channels. In each channel, three input values are

multiplied by three separate coefficients. Also included are an

offset value for each row of the matrix and a scaling multiple for

all values. Each value has a 13-bit, twos complement resolution

to ensure the signal integrity is maintained. The CSC is

designed to run at speeds up to 150 MHz supporting resolutions up to 1080p at 60 Hz. With any-to-any color space

support, formats such as RGB, YUV, YCbCr, and others are

supported by the CSC.

The main inputs, R

inputs from each channel. These inputs are based on the input

format detailed in

CSC inputs is shown in

Table 8. CSC Port Mapping

Input Channel CSC Input Channel

R/CR RIN

Gr/Y GIN

B/CB BIN

, GIN, and BIN come from the 8- to 12-bit

IN

Tabl e 7 . The mapping of these inputs to the

Tabl e 8.

One of the three channels is represented in

processing channel, the three inputs are multiplied by three

separate coefficients marked a1, a2, and a3. These coefficients

are divided by 4096 to obtain nominal values ranging from

–0.9998 to +0.9998. The variable labeled a4 is used as an offset

control. The CSC_Mode setting is the same for all three

processing channels. This multiplies all coefficients and offsets

by a factor of 2

CSC_Mode

.

The functional diagram for a single channel of the CSC, as

shown in

Figure 6, is repeated for the remaining G and B

channels. The coefficients for these channels are b1, b2, b3, b4,

c1, c2, c3, and c4.

a1[12:0]

[11:0]

R

IN

[11:0]

IN

B

[11:0]

IN

×

a2[12:0]

×

a3[12:0]

×

1

×

4096

1

×

4096

1

×

4096

+

+

Figure 6. Single CSC Channel

A programming example and register settings for several

common conversions are listed in the

(CSC) Common Settings

section.

For a detailed functional description and more programming

examples, please refer to the application note AN-795, AD9800

Color Space Converter User's Guide.

Figure 6. In each

CSC_Mode[1:0]

a4[12:0]

×4

+

2

R

×2

OUT

1

0

Color Space Converter

[11:0]

05689-006

Rev. 0 | Page 11 of 44

Page 12

AD9381

8

AUDIO PLL SETUP

Data contained in the audio infoframes, among other registers,

define for the AD9381 HDMI receiver not only the type of

audio, but the sampling frequency (f

contains information about the N and CTS values used to

recreate the clock. With this information it is possible to

regenerate the audio sampling frequency. The audio clock is

regenerated by dividing the 20-bit CTS value into the TMDS

clock, then multiplying by the 20-bit N value. This yields a

multiple of the f

256 × f

. It is possible for this to be specified up to 1024 × fs.

s

f

128 ×

S

VIDEO

CLOCK

N

1

N AND CTS VALUES ARE TRANSMITTED USING THE

AUDIO CLOCK REGENERATION PACKET. VIDEO

CLOCK IS TRANSMITTED ON TMDS CLOCK CHANNEL.

(sampling frequency) of either 128 × fs or

s

DIVIDE

BY

REGISTER

CYCLE

N

TIME

COUNTER

N

Figure 7. N and CTS for Audio Clock

). The audio infoframe also

S

SINK DEVICESOURCE DEVICE

1

CTS

TMDS

CLOCK

1

N

DIVIDE

BY

CTS

MULTIPLY

BY

128 ×

N

f

S

05689-007

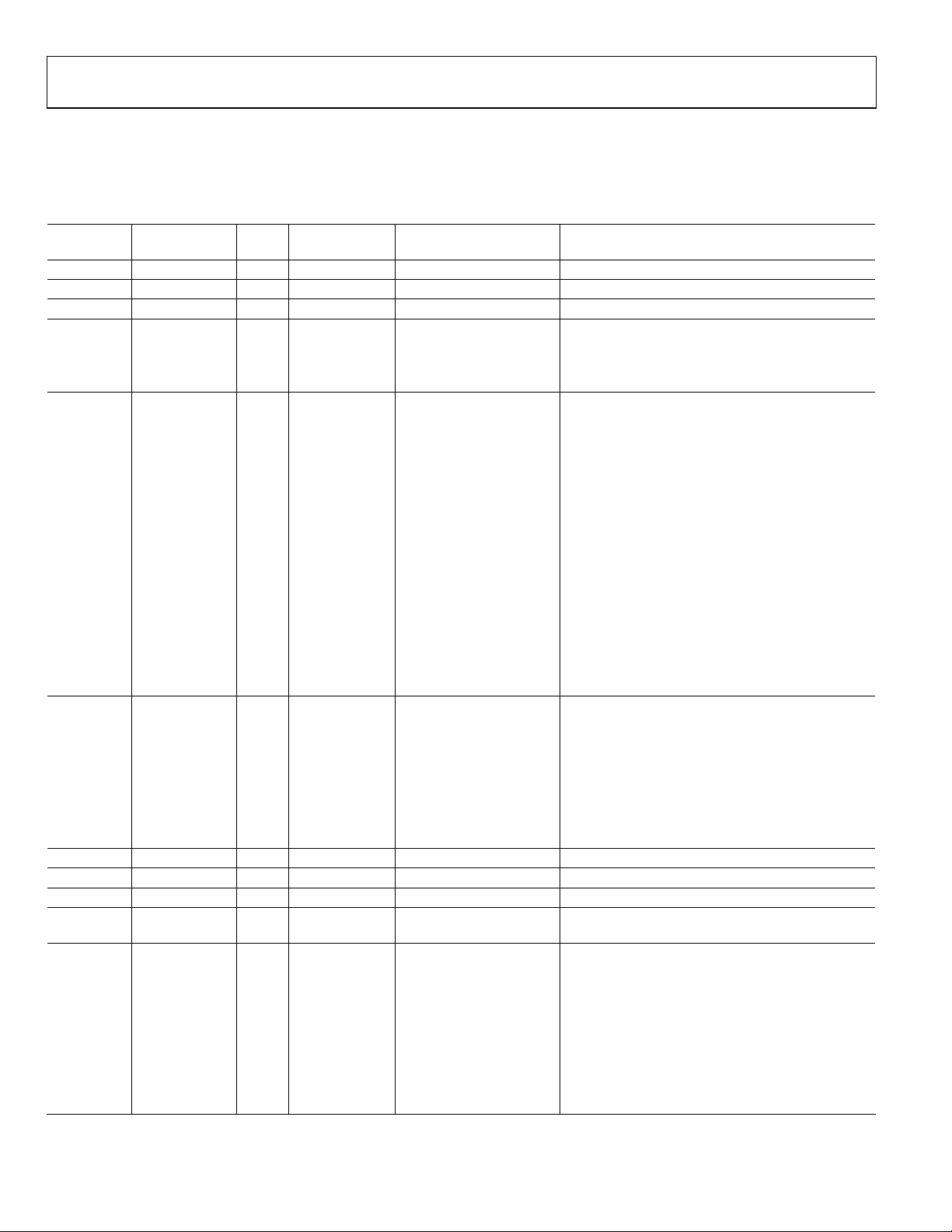

In order to provide the most flexibility in configuring the audio

sampling clock, an additional PLL is employed. The PLL

characteristics are determined by the loop filter design, the PLL

charge pump current, and the VCO range setting. The loop

filter design is shown in

C

nF

Figure 8.

1.5kΩ

C

Z

80nF

R

Z

P

FILT

Figure 8. PLL Loop Filter Detail

PV

D

05689-010

To fully support all audio modes for all video resolutions up to

1080p, it is necessary to adjust certain audio-related registers

from their power-on default values.

Table 9 describes these

registers and gives their recommended settings.

Table 9. AD9398 Audio Register Settings

Register Bits Recommended

Function Comments

Setting

0x01 7:0 0x00 PLL Divisor (MSBs)

0x02 7:4 0x40 PLL Divisor (Lab’s)

0x03

7:6 01 VCO Range

5:3 010 Charge Pump Current

2 1 PLL Enable

0x34 4 0 Audio Frequency Mode Override

0x58

7 1 PLL Enable

6:4 011 MCLK PLL Divisor

3 0 N/CTS Disable The N and CTS values should always be enabled.

2:0 0** MCLK Sampling Frequency 000 = 128 × f

The analog video PLL is also used for the audio clock

circuit when in HDMI mode. This is done automatically.

In HDMI mode, this bit enables a lower frequency to be

used for audio MCLK generation.

Allows the chip to determine the low frequency mode

of the audio PLL.

This enables the analog PLL to be used for audio MCLK

generation.

When the analog PLL is enabled for MCLK generation,

another frequency divider is provided. These bits set

the divisor to 4.

S

001 = 256 × f

010 = 384 × f

011 = 512 × f

S

S

S

Rev. 0 | Page 12 of 44

Page 13

AD9381

AUDIO BOARD LEVEL MUTING

The audio can be muted through the infoframes or locally

via the serial bus registers. This can be controlled with

Register R0x57, Bits [7:4].

AVI Infoframes

The HDMI TMDS transmission contains Infoframes with

specific information for the monitor such as:

• Audio information

• 2 to 8 channels of audio identified

• Audio coding

• Audio sampling frequency

• Speaker placement

• N and CTS values (for reconstruction of the audio)

• Muting

• Source information

• CD

• SACD

• DVD

• Video information

• Video ID code (per CEA861B)

• Color space

• Aspect ratio

• Horizontal and vertical bar information

• MPEG frame information (I, B, or P frame)

• Vendor (transmitter source) name and product model

This information is the fundamental difference between DVI

and HDMI transmissions and is located in read-only registers

R0x5A to R0xEE. In addition to this information, registers are

provided to indicate that new information has been received.

Registers with addresses ending in 0xX7 or 0xXF beginning at

R0x87 contain the new data flags (NDF) information. All of

these registers contain the same information and all are reset

once any of them are read. Although there is no external

interrupt signal, it is easy for the user to read any of these

registers and see if there is new information to be processed.

OUTPUT DATA FORMATS

The AD9398 supports 4:4:4, 4:2:2, double data-rate (DDR),

and BT656 output formats. Register 0x25[3:0] controls the

output mode. These modes and the pin mapping are shown

in

Tabl e 1 0.

.

Table 10.

Port Red Green Blue

Bit 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

4:4:4 Red/Cr [7:0] Green/Y [7:0] Blue/Cb [7:0]

4:2:2 CbCr [7:0] Y [7:0]

4:4:4 DDR

4:2:2 to 12 CbCr [11:0] Y [11:0]

1

Arrows in the table indicate clock edge. Rising edge of clock = ↑, falling edge = ↓.

DDR ↑ 1 G [3:0] DDR ↑ B [7:4] DDR ↑ B [3:0] DDR 4:2:2 ↑ CbCr [11:0]

DDR

↓ R [7:0] DDR ↓ G [7:4] DDR 4:2:2 ↓ Y,Y [11:0]

DDR 4:2:2

↑ CbCr ↓ Y, Y

Rev. 0 | Page 13 of 44

Page 14

AD9381

2-WIRE SERIAL REGISTER MAP

The AD9381 is initialized and controlled by a set of registers that determines the operating modes. An external controller is employed to

write and read the control registers through the 2-wire serial interface port.

Table 11. Control Register Map

Hex

Address

0x00 Read [7:0] 00000000 Chip Revision Chip revision ID. Revision is read [7:4]. [3:0].

0x01 Read/Write [7:0] 01101001 PLL Divider MSB PLL feedback divider value MSB.

0x02 Read/Write [7:4] 1101**** PLL Divider PLL feedback divider value.

0x03 Read/Write [7:6] 01****** VCO Range VCO range.

[5:3] **001*** Charge Pump Charge pump current control for PLL.

[2] *****0** PLL Enable

0x11 Read/Write [7] 0******* HSYNC Source 0 = HSYNC.

1 = SOG.

[6] *0****** HSYNC Source Override 0 = auto HSYNC source.

1 = manual HSYNC source.

[5] **0***** VSYNC Source 0 = VSYNC.

1 = VSYNC from SOG.

[4] ***0**** VSYNC Source Override 0 = auto HSYNC source.

1 = manual HSYNC source.

[3] ****0*** Channel Select 0 = Channel 0.

1 = Channel 1.

[2] *****0** Channel Select Override 0 = autochannel select.

1 = manual channel select.

[1] ******0* Interface Select 0 = analog interface.

1 = digital interface.

[0] *******0 Interface Override 0 = auto-interface select.

1 = manual interface select.

0x12 Read/Write [7] 1******* Input HSYNC Polarity 0 = active low.

1 = active high.

[6] *0****** HSYNC Polarity Override 0 = auto HSYNC polarity.

1 = manual HSYNC polarity.

[5] **1***** Input VSYNC Polarity 0 = active low.

1 = active high.

[4] ***0**** VSYNC Polarity Override 0 = auto VSYNC polarity.

1 = manual VSYNC polarity.

0x17 Read [3:0] ****0000 HSYNCs Per VSYNC MSB MSB of HSYNCs per VSYNC.

0x18 Read [7:0] 00000000 HSYNCs Per VSYNC HSYNCs per VSYNC count.

0x22 Read/Write [7:0] 4 VSYNC Duration VSYNC duration.

0x23 Read/Write [7:0] 32 HSYNC Duration

0x24 Read/Write [7] 1******* HSYNC Output Polarity Output HSYNC polarity.

0 = active low out.

1 = active high out.

[6] *1****** VSYNC Output Polarity Output VSYNC polarity.

0 = active low out.

1 = active high out.

[5] **1***** DE Output Polarity Output DE polarity.

0 = active low out.

1 = active high out.

Read/Write

or Read Only Bits Default Value Register Name

Description

This bit enables a lower frequency to be used for

audio MCLK generation

HSYNC duration. Sets the duration of the output

HSYNC in pixel clocks.

Rev. 0 | Page 14 of 44

Page 15

AD9381

Hex

Address

[4] ***1**** Field Output Polarity Output field polarity.

0 = active low out.

1 = active high out.

[0] *******0 Output CLK Invert 0 = don’t invert clock out.

1 = invert clock out.

0x25 Read/Write [7:6] 01****** Output CLK Select

00 = ½× CLK.

01 = 1× CLK.

10 = 2× CLK.

11 = 90° phase 1× CLK.

[5:4] **11**** Output Drive Strength Sets the drive strength of the outputs.

00 = lowest, 11 = highest.

[3:2] ****00** Output Mode Selects the data output mapping.

00 = 4:4:4 mode (normal).

01 = 4:2:2 + DDR 4:2:2 on blue.

10 = DDR 4:4:4 + DDR 4:2:2 on blue.

11 = 12-bit 4:2:2 (HDMI option only).

[1] ******1* Primary Output Enable Enables primary output.

[0] *******0

0x26 Read/Write [7] 0******* Output Three-State Three-state the outputs.

[5] **0***** SPDIF Three-State Three-state the S/PDIF output.

[4] ***0**** I2S Three-State Three-state the I2S output and the MCLK out.

[3] ****1*** Power-Down Pin Polarity Sets polarity of power-down pin.

0 = active low.

1 = active high.

[2:1] *****00*

00 = power-down.

01 = power-down and three-state SOG.

10 = three-state outputs only.

11 = three-state outputs and SOG.

[0] *******0 Power-Down 0 = normal.

1 = power-down.

0x27 Read/Write [7] 1*******

1 = enable auto low power state.

[6] *0****** HDCP A0

0 = use internally generated MCLK.

1 = use external MCLK input.

[5] **0***** MCLK External Enable

[4] ***0**** BT656 EN

[3] ****0*** Force DE Generation

Read/Write

or Read Only Bits Default Value Register Name

Secondary Output

Enable

Power-Down Pin

Func tion

Auto Power-Down

Enable

Description

Selects which clock to use on output pin. 1× CLK is

divided down from TMDS clock input when pixel

repetition is in use.

Enables secondary output (DDR 4:2:2 in Output

Mode 1 and Mode 2).

Selects the function of the power-down pin.

0 = disable auto low power state.

2

Sets the LSB of the address of the HDCP I

Set to 1 only for a second receiver in a dual-link

configuration.

If an external MCLK is used, it must be locked to the

video clock according to the CTS and N available in

the I2C. Any mismatch between the internal MCLK

and the input MCLK results in dropped or repeated

audio samples.

Enables EAV/SAV codes to be inserted into the

video output data.

Allows use of the internal DE generator in DVI

mode.

C.

Rev. 0 | Page 15 of 44

Page 16

AD9381

Hex

Address

[2:0] *****000 Interlace Offset

0x28 Read/Write [7:2] 011000** VS Delay

[1:0] ******01 HS Delay MSB MSB, Register 0x29.

0x29 Read/Write [7:0] 00000100 HS Delay

0x2A Read/Write [3:0] ****0101 Line Width MSB MSB, Register 0x2B.

0x2B Read/Write [7:0] 00000000 Line Width Sets the width of the active video line in pixels.

0x2C Read/Write [3:0] ****0010 Screen Height MSB MSB, Register 0x2D.

0x2D Read/Write [7:0] 11010000 Screen Height Sets the height of the active screen in lines.

0x2E Read/Write [7] 0******* Ctrl EN Allows Ctrl [3:0] to be output on the I2S data pins.

00 = I2S mode.

[6:5] *00***** I2S Out Mode 01 = right-justified.

10 = left-justified.

11 = raw IEC60958 mode.

[4:0] ***11000 I2S Bit Width Sets the desired bit width for right-justified mode.

0x2F Read [6] *0****** TMDS Sync Detect Detects a TMDS DE.

[5] **0***** TMDS Active Detects a TMDS clock.

[4] ***0**** AV Mute

[3] ****0*** HDCP Keys Read Returns 1 when read of EEPROM keys is successful.

[2:0] *****000 HDMI Quality Returns quality number based on DE edges.

0x30 Read [6] *0****** HDMI Content Encrypted

[5] **0***** DVI HSYNC Polarity Returns DVI HSYNC polarity.

[4] ***0**** DVI VSYNC Polarity Returns DVI VSYNC polarity.

[3:0] ****0000 HDMI Pixel Repetition

0x31 Read/Write [7:4] 1001**** MV Pulse Max

[3:0] ****0110 MV Pulse Min

0x32 Read/Write [7] 0******* MV Oversample En

[6] *0****** MV Pal En

[5:0] **001101 MV Line Count Start Sets the start line for Macrovision detection.

0x33 Read/Write [7] 1******* MV Detect Mode 0 = standard definition.

1 = progressive scan mode.

[6] *0****** MV Settings Override

1 = use I2C values for these settings.

[5:0] **010101 MV Line Count End Sets the end line for Macrovision detection.

0x34 Read/Write [7:6] 10****** MV Pulse Limit Set

[5] **0***** Low Freq Mode

Read/Write

or Read Only Bits Default Value Register Name

Description

Sets the difference (in HSYNCs) in field length

between Field 0 and Field 1.

Sets the delay (in lines) from the VSYNC leading

edge to the start of active video.

Sets the delay (in pixels) from the HSYNC leading

edge to the start of active video.

Gives the status of AV mute based on general

control packets.

This bit is high when HDCP decryption is in use

(content is protected). The signal goes low when

HDCP is not being used. Customers can use this bit

to allow copying of the content. The bit should be

sampled at regular intervals because it can change

on a frame-by-frame basis.

Returns current HDMI pixel repetition amount.

0 = 1×, 1 = 2×, ... .The clock and data outputs

automatically de-repeat by this value.

Sets the maximum pseudo sync pulse width for

Macrovision® detection.

Sets the minimum pseudo sync pulse width for

Macrovision detection.

Tells the Macrovision detection engine whether we

are oversampling or not.

Tells the Macrovision detection engine to enter PAL

mode.

0 = use hard-coded settings for line counts and

pulse widths.

Sets the number of pulses required in the last 3

lines (SD mode only).

Sets audio PLL to low frequency mode. Low

frequency mode should only be set for pixel clocks

<80 MHz.

Rev. 0 | Page 16 of 44

Page 17

AD9381

Hex

Address

[4] ***0**** Low Freq Override

[3] ****0*** Up Conversion Mode 0 = repeat Cr and Cb values.

1 = interpolate Cr and Cb values.

[2] *****0** CrCb Filter Enable Enables the FIR filter for 4:2:2 CrCb output.

[1] ******0* CSC_Enable

0x35 Read/Write [6:5] *01* **** CSC_Mode 00 = ±1.0, −4096 to 4095.

01 = ±2.0, −8192 to 8190.

1× = ±4.0, −16384 to 16380.

[4:0] ***01100 CSC_Coeff_A1 MSB MSB, Register 0x36.

0x36 Read/Write [7:0] 01010010 CSC_Coeff_A1 LSB

G

B

0x37 Read/Write [4:0] ***01000 CSC_Coeff_A2 MSB MSB, Register 0x38.

0x38 Read/Write [7:0] 00000000 CSC_Coeff_A2 LSB CSC coefficient for equation:

G

B

0x39 Read/Write [4:0] ***00000 CSC_Coeff_A3 MSB MSB, Register 0x3A.

0x3A Read/Write [7:0] 00000000 CSC_Coeff_A3 LSB CSC coefficient for equation:

G

B

0x3B Read/Write [4:0] ***11001 CSC_Coeff_A4 MSB MSB, Register 0x3C.

0x3C Read/Write [7:0] 11010111 CSC_Coeff_A4 LSB CSC coefficient for equation:

B

0x3D Read/Write [4:0] ***11100 CSC_Coeff_B1 MSB MSB, Register 0x3E.

0x3E Read/Write [7:0] 01010100 CSC_Coeff_B1 LSB CSC coefficient for equation:

R

B

0x3F Read/Write [4:0] ***01000 CSC_Coeff_B2 MSB MSB, Register 0x40.

0x40 Read/Write [7:0] 00000000 CSC_Coeff_B2 CSC coefficient for equation:

R

B

0x41 Read/Write [4:0] ***11110 CSC_Coeff_B3 MSB MSB, Register 0x42.

0x42 Read/Write [7:0] 10001001 CSC_Coeff_B3 LSB

R

G

B

Read/Write

or Read Only Bits Default Value Register Name

Description

Allows the previous bit to be used to set low

frequency mode rather than the internal autodetect.

Enables the color space converter (CSC). The

default settings for the CSC provide HDT-to-RGB

conversion.

Sets the fixed-point position of the CSC

coefficients, including the A4, B4, and C4 offsets.

Color space converter (CSC) coefficient for

equation:

R

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

R

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

R

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

R

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

G

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

G

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

G

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

Color space converter (CSC) coefficient for

equation:

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

Rev. 0 | Page 17 of 44

Page 18

AD9381

Hex

Address

0x43 Read/Write [4:0] ***00010 CSC_Coeff_B4 MSB MSB, Register 0x44.

0x44 Read/Write [7:0] 10010010 CSC_Coeff_B4 LSB CSC coefficient for equation:

R

B

0x45 Read/Write [4:0] ***00000 CSC_Coeff_C1 MSB MSB, Register 0x46.

0x46 Read/Write [7:0] 00000000 CSC_Coeff_C1 LSB CSC coefficient for equation:

R

G

0x47 Read/Write [4:0] ***01000 CSC_Coeff_C2 MSB MSB, Register 0x48.

0x48 Read/Write [7:0] 00000000 CSC_Coeff_C2 LSB CSC coefficient for equation:

R

G

0x49 Read/Write [4:0] ***01110 CSC_Coeff_C3 MSB MSB, Register 0x4A.

0x4A Read/Write [7:0] 10000111 CSC_Coeff_C3 LSB CSC coefficient for equation:

R

G

0x4B Read/Write [4:0] ***11000 CSC_Coeff_C4 MSB MSB, Register 0x4C.

0x4C Read/Write [7:0] 10111101 CSC_Coeff_C4 LSB CSC coefficient for equation:

R

G

0x50 Read/Write [7:0] 00100000 Test Must be written to 0x20 for proper operation.

0x56 Read/Write [7:0] 00001111 Test

0x57 Read/Write [7] 0******* A/V Mute Override A1 overrides the AV mute value with Bit 6.

[6] *0****** AV Mute Value Sets AV mute value if override is enabled.

[3] ****0*** Disable Video Mute Disables mute of video during AV mute.

[2] *****0** Disable Audio Mute Disables mute of audio during AV mute.

0x58 Read/Write [7] MCLK PLL Enable MCLK PLL enable—uses analog PLL.

[6:4] MCLK PLL_N

[3] N_CTS_Disable

[2:0] MCLK FS_N

0x59 Read/Write [6] MDA/MCL PU This disables the MDA/MCL pull-ups.

[5] CLK Term O/R

[4] Manual CLK Term Clock termination: 0 = normal, 1 = disconnected.

[2] FIFO Reset UF

[1] FIFO Reset OF

[0] MDA/MCL Three-State This bit three-states the MDA/MCL lines.

Read/Write

or Read Only Bits Default Value Register Name

Description

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

G

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

B

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

B

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

B

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

= (A1 × RIN) + (A2 × GIN) + (A3 × BIN) + A4

OUT

= (B1 × RIN) + (B2 × GIN) + (B3 × BIN) + B4

OUT

B

= (C1 × RIN) + (C2 × GIN) + (C3 × BIN) + C4

OUT

Must be written to default of 0x0F for proper

operation.

MCLK PLL N [2:0]—this controls the division of the

MCLK out of the PLL: 0 = /1, 1 = /2, 2 = /3, 3 = /4,

etc.

Prevents the N/CTS packet on the link from writing

to the N and CTS registers.

Controls the multiple of 128 Fs, used for MCLK out .

0 = 128 f

, 1 = 256 fS, 2 = 384, 7 = 1024 fS.

S

Clock termination power-down override: 0 = auto,

1 = manual.

This bit resets the audio FIFO if underflow is

detected.

This bit resets the audio FIFO if overflow is

detected.

Rev. 0 | Page 18 of 44

Page 19

AD9381

Hex

Address

0x5A Read [6:0] Packet Detected

0x5B Read [3] HDMI Mode 0 = DVI, 1 = HDMI.

0x5E Read [7:6] Channel Status Mode = 00. All others are reserved.

[5:3] When Bit 1 = 0 (Linear PCM).

000 = 2 audio channels without pre-emphasis.

010 = reserved.

011 = reserved.

2 0 = software for which copyright is asserted.

1 = software for which no copyright is asserted.

1

1 = audio sample word used for other purposes.

0 0 = consumer use of channel status block.

0x5F Read [7:0]

0x60 Read [7:4] Channel Number

[3:0] Source Number

0x61 Read [5:4] Clock Accuracy Clock accuracy.

[3:0] Sampling Frequency 0011 =32 kHz

Read/Write

or Read Only Bits Default Value Register Name

Audio Channel Status

Channel Status Category

Code

Description

These 7 bits are updated if any specific packet has

been received since last reset or loss of clock

detect. Normal is 0x00.

Bit Data Packet Detected

0 AVI infoframe.

1 Audio infoframe.

2 SPD infoframe.

3 MPEG source infoframe.

4 ACP packets.

5 ISRC1 packets.

6 ISRC2 packets.

001 = 2 audio channels with 50/15 μs preemphasis.

0 = audio sample word represents linear PCM

samples.

00 = Level II.

01 = Level III.

10 = Level I.

11 = reserved.

0000 = 44.1 kHz

1000 = 88.2 kHz.

1100 = 176.4 kHz.

0010 = 48 kHz.

1010 = 96 kHz.

1110 = 192 kHz.

Rev. 0 | Page 19 of 44

Page 20

AD9381

Hex

Address

0x62 Read [3:0] Word Length

0x7B Read [7:0] CTS [19:12]

0x7C Read [7:0] CTS [11:4]

0x7D Read [7:4] CTS [3:0]

Read [3:0] N [19:16]

0x7E Read [7:0] N [15:8]

0x7F Read [7:0] N [7:0]

0x80 Read [7:0] AVI Infoframe Version

0x81 Read [6:5] Y [1:0] Indicates RGB, 4:2:2 or 4:4:4.

00 = RGB.

01 = YCbCr 4:2:2.

10 = YCbCr 4:4:4.

4 Active Format Active format information present.

Information Status 0 = no data.

1 = active format information valid.

[3:2] Bar Information B [1:0].

00 = no bar information.

01 =horizontal bar information valid.

10 = vertical bar information valid.

11 = horizontal and vertical bar information valid.

[1:0] Scan Information S [1:0].

00 = no information.

01 = overscanned (television).

10 = underscanned (computer).

0x82 Read [7:6] Colorimetry C [1:0].

00 = no data.

01 = SMPTE 170M, ITU601.

10 = ITU709.

[5:4] Picture Aspect Ratio M [1:0].

00 = no data.

01 = 4:3.

10 = 16:9.

Read/Write

or Read Only Bits Default Value Register Name

AVI Infoframe

Description

Word length.

0000 not specified.

0100 = 16 bits.

0011 = 17 bits.

0010 = 18 bits.

0001 = 19 bits.

0101 = 20 bits.

1000 not specified.

1100 = 20 bits.

1011 = 21 bits.

1010 = 22 bits.

1001 = 23 bits.

1101 = 24 bits.

Cycle time stamp—this 20-bit value is used with

the N value to regenerate an audio clock. For

remaining bits, see Register 0x7C and Register

0x7D.

20-bit N used with CTS to regenerate the audio

clock. For remaining bits, see Register 0x7E and

Register 0x7F.

Rev. 0 | Page 20 of 44

Page 21

AD9381

Hex

Address

[3:0]

1000 = same as picture aspect ratio.

1001 = 4:3 (center).

1010 = 16:9 (center).

1011 = 14:9 (center).

0x83 Read [1:0]

00 = no known nonuniform scaling.

01 = picture has been scaled horizontally.

10 = picture has been scaled vertically.

0x84 Read [6:0] Video Identification Code

0x85 Read [3:0] Pixel Repeat

0000 = no repetition (pixel sent once).

0001 = pixel sent twice (repeated once).

0010 = pixel sent 3 times.

1001 = pixel sent 10 times.

0xA—0xF reserved.

0x86 Read [7:0] Active Line Start LSB

0x87 Read [6:0] New Data Flags

0x88 Read [7:0] Active Line Start MSB Active line start MSB (see Register 0x86).

0x89 Read [7:0] Active Line End LSB

0x8A Read [7:0] Active Line End MSB Active line end MSB. See Register 0x89.

0x8B Read [7:0] Active Pixel Start LSB

0x8C Read [7:0] Active Pixel Start MSB Active pixel start MSB. See Register 0x8B.

0x8D Read [7:0] Active Pixel End LSB

0x8E Read [7:0] Active Pixel End MSB Active pixel end MSB. See Register 0x8D.

0x8F Read [6:0] New Data Flags New data flags (see 0x87).

Read/Write

or Read Only Bits Default Value Register Name

Active Format Aspect

Ratio

Nonuniform Picture

Scaling

Description

R [3:0].

SC [1:0].

11 = picture has been scaled horizontally and

vertically.

VIC [6:0] video identification code—refer to CEA

EDID short video descriptors.

PR [3:0]—This specifies how many times a pixel has

been repeated.

This represents the line number of the end of the

top horizontal bar. If 0, there is no horizontal bar.

Combines with Register 0x88 for a 16-bit value.

New data flags. These 8 bits are updated if any

specific data changes. Normal (no NDFs) is 0x00.

When any NDF register is read, all bits reset to 0x00.

All NDF registers contain the same data.

Bit Data Packet Changed

0 AVI infoframe.

1 Audio infoframe.

2 SPD infoframe.

3 MPEG source infoframe.

4 ACP packets.

5 ISRC1 packets.

6 ISRC2 packets.

This represents the line number of the beginning of

a lower horizontal bar. If greater than the number

of active video lines, there is no lower horizontal

bar. Combines with Register 0x8A for a 16-bit value.

This represents the last pixel in a vertical pillar bar

at the left side of the picture. If 0, there is no left

bar. Combines with Register 0x8C for a 16-bit value.

This represents the first horizontal pixel in a vertical

pillar-bar at the right side of the picture. If greater

than the maximum number of horizontal pixels,

there is no vertical bar. Combines with Register

0x8E for a16-bit value.

Rev. 0 | Page 21 of 44

Page 22

AD9381

Hex

Address

0x90 Read [7:0] Audio Infoframe Version

0x91 Read [7:4] Audio Coding Type CT [3:0]. Audio coding type.

[2:0] Audio Coding Count CC [2:0]. Audio channel count.

000 = refer to stream header.

001 = 2 channels.

010 = 3 channels.

111 = 8 channels.

0x92 Read [4:2] Sampling Frequency SF [2:0]. Sampling frequency.

000 = refer to stream header.

001 = 32 kHz.

010 = 44.1 kHz (CD).

011 = 48 kHz.

100 = 88.2 kHz.

101 = 96 kHz.

110 = 176.4 kHz.

111 = 192 kHz.

[1:0] Sample Size SS [1:0]. Sample size.

00 = refer to stream header.

01 = 16-bit.

10 = 20-bit.

11 = 24-bit.

0x93 Read [7:0] Max Bit Rate

0x94 Read [7:0] Speaker Mapping

0x95 Read 7 Down-Mix DM_INH—down-mix inhibit.

0 = permitted or no information.

1 = prohibited.

[6:3] Level Shift

0000 = 0 dB attenuation.

0001 = 1 dB attenuation.

…..

1111 = 15 dB attenuation.

0x96 Read [7:0] Reserved.

0x97 Read [6:0] New Data Flags New data flags (see 0x87).

Read/Write

or Read Only Bits Default Value Register Name

Description

0x00 = refer to stream header.

0x01 = IEC60958 PCM.

0x02 = AC3.

0x03 = MPEG1 (Layer 1 and Layer 2).

0x04 = MP3 (MPEG1 Layer 3).

0x05 = MPEG2 (multichannel).

0x06 = AAC.

0x07 = DTS.

0x08 = ATRAC.

Max bit rate (compressed audio only).The value of

this field multiplied by 8 kHz represents the

maximum bit rate.

CA [7:0]. Speaker mapping or placement for up to 8

channels. See

LSV [3:0]—level shift values with attenuation

information.

Tab le 33.

Rev. 0 | Page 22 of 44

Page 23

AD9381

Hex

Address

0x98 Read [7:0]

0x99 Read [7:0]

0x9A Read [7:0] VN2 VN2.

0x9B Read [7:0] VN3 VN3.

0x9C Read [7:0] VN4 VN4.

0x9D Read [7:0] VN5 VN5.

0x9E Read [7:0] VN6 VN6.

0x9F Read [6:0] New Data Flags New data flags (see 0x87).

0xA0 Read [7:0] VN7 VN7.

0xA1 Read [7:0] VN8 VN8.

0xA2 Read [7:0]

0xA3 Read [7:0] PD2 PD2.

0xA4 Read [7:0] PD3 PD3.

0xA5 Read [7:0] PD4 PD4.

0xA6 Read [7:0] PD5 PD5.

0xA7 Read [7:0] New Data Flags New data flags (see 0x87).

0xA8 Read [6:0] PD6 PD6.

0xA9 Read [7:0] PD7 PD7.

0xAA Read [7:0] PD8 PD8.

0xAB Read [7:0] PD9 PD9.

0xAC Read [7:0] PD10 PD10.

0xAD Read [7:0] PD11 PD11.

0xAE Read [7:0] PD12 PD12.

0xAF Read [6:0] New Data Flags New data flags (see 0x87).

0xB0 Read [7:0] PD13 PD13.

0xB1 Read [7:0] PD14 PD14.

0xB2 Read [7:0] PD15 PD15.

0xB3 Read [7:0] PD16 PD16.

0xB4 Read [7:0] Source Device This is a code that classifies the source device.

Information Code 0x00 = unknown.

0x01 = digital STB.

0x02 = DVD.

0x03 = D-VHS.

0x04 = HDD video.

0x05 = DVC.

0x06 = DSC.

0x07 = video CD.

0x08 = game.

0x09 = PC general.

0xB7 Read [6:0] New Data Flags New data flags (see 0x87).

Read/Write

or Read Only Bits Default Value Register Name

Source Product Description (SPD) Infoframe

Source Product

Description (SPD)

Infoframe Version

Vendor Name

Character 1

Product Description

Character 1

Description

Vendor name character 1 (VN1) 7-bit ASCII code.

The first character in 8 that is the name of the

company that appears on the product.

Product Description Character 1 (PD1) 7-bit ASCII

code. The first character of 16 that contains the

model number and a short description.

Rev. 0 | Page 23 of 44

Page 24

AD9381

Hex

Address

0xB8 Read [7:0]

0xB9 Read [7:0] MB(0)

0xBA Read [7:0] MB[1] MB [1].

0xBB Read [7:0] MB[2] MB [2].

0xBC Read [7:0] MB [3] (upper byte).

4 Field Repeat FR—New field or repeated field.

0 = New field or picture.

1 = Repeated field.

0xBD Read [1:0] MPEG Frame

00 = unknown.

01 = I picture.

10 = B picture.

11 = P picture.

0xBE Read [7:0] Reserved.

0xBF Read [6:0] New Data Flags New data flags (see 0x87).

0xC0 Read [7:0]

0x00 = generic audio.

0x01 = IEC 60958-identified audio.

0x02 = DVD-audio.

0x03 = reserved for super audio CD (SACD).

0x04 = 0xFF reserved.

0xC1 Read [7:0] ACP Packet Byte 0 ACP Packet Byte 0 (ACP_PB0).

0xC2 Read [7:0] ACP_PB1 ACP_PB1.

0xC3 Read [7:0] ACP_PB2 ACP_PB2.

0xC4 Read [7:0] ACP_PB3 ACP_PB3.

0xC5 Rea [7:0] ACP_PB4 ACP_PB4.

0xC6 Read [7:0] ACP_PB5 ACP_PB5.

0xC7 Read [6:0] NDF New data flags (see 0x87).

0xC8 7 ISRC1 Continued

Read 6 ISRC1 Valid 0 = ISRC1 status bits and PBs not valid.

1 = ISRC1 status bits and PBs valid.

001 = starting position.

[2:0] ISRC1 Status 010 = intermediate position.

100 = final position.

0xC9 Read [7:0] ISRC1 Packet Byte 0 ISRC1 Packet Byte 0 (ISRC1_PB0).

0xCA Read [7:0] ISRC1_PB1 ISRC1_PB1.

0xCB Read [7:0] ISRC1_PB2 ISRC1_PB2.

0xCC Read [7:0] ISRC1_PB3 ISRC1_PB3.

0xCD Read [7:0] ISRC1_PB4 ISRC1_PB4.

0xCE Read [7:0] ISRC1_PB5 ISRC1_PB5.

0xCF Read [6:0] NDF New data flags (see 0x87).

0xD0 Read [7:0] ISRC1_PB6 ISRC1_PB6.

0xD1 Read [7:0] ISRC1_PB7 ISRC1_PB7.

Read/Write

or Read Only Bits Default Value Register Name

MPEG Source Infoframe

MPEG Source Infoframe

Version

Audio Content

Protection Packet (ACP)

Type

Description

MB [0] (Lower byte of MPEG bit rate: Hz). The lower

8 bits of 32 bits (4 bytes) that specify the MPEG bit

rate in Hz.

MF [1:0] This identifies whether frame is an I, B, or P

picture.

Audio content protection packet (ACP) type.

International standard recording code (ISRC1)

continued. This indicates an ISRC2 packet is being

transmitted.

Rev. 0 | Page 24 of 44

Page 25

AD9381

Hex

Address

0xD2 Read [7:0] ISRC1_PB8 ISRC1_PB8.

0xD3 Read [7:0] ISRC1_PB9 ISRC1_PB9.

0xD4 Read [7:0] ISRC1_PB10 ISRC1_PB10.

0xD5 Read [7:0] ISRC1_PB11 ISRC1_PB11.

0xD6 Read [7:0] ISRC1_PB12 ISRC1_PB12.

0xD7 Read [6:0] NDF New data flags (see 0x87).

0xD8 Read [7:0] ISRC1_PB13 ISRC1_PB13.

0xD9 Read [7:0] ISRC1_PB14 ISRC1_PB14.

0xDA Read [7:0] ISRC1_PB15 ISRC1_PB15.

0xDB Read [7:0] ISRC1_PB16 ISRC1_PB16.

0xDC Read [7:0] ISRC2 Packet Byte 0

0xDD Read [7:0] ISRC2_PB1 ISRC2_PB1.

0xDE Read [7:0] ISRC2_PB2 ISRC2_PB2.

0xDF Read [6:0] New Data Flags New data flags (see 0x87).

0xE0 Read [7:0] ISRC2_PB3 ISRC2_PB3.

0xE1 Read [7:0] ISRC2_PB4 ISRC2_PB4.

0xE2 Read [7:0] ISRC2_PB5 ISRC2_PB5.

0xE3 Read [7:0] ISRC2_PB6 ISRC2_PB6.

0xE4 Read [7:0] ISRC2_PB7 ISRC2_PB7.

0xE5 Read [7:0] ISRC2_PB8 ISRC2_PB8.

0xE6 Read [7:0] ISRC2_PB9 ISRC2_PB9.

0xE7 Read [6:0] New Data Flags New data flags (see 0x87).

0xE8 Read [7:0] ISRC2_PB10 ISRC2_PB10.

0xE9 Read [7:0] ISRC2_PB11 ISRC2_PB11.

0xEA Read [7:0] ISRC2_PB12 ISRC2_PB12.

0xEB Read [7:0] ISRC2_PB13 ISRC2_PB13.

0xEC Read [7:0] ISRC2_PB14 ISRC2_PB14.

0xED Read [7:0] ISRC2_PB15 ISRC2_PB15.

0xEE Read [7:0] ISRC2_PB16 ISRC2_PB16.

Read/Write

or Read Only Bits Default Value Register Name

Description

ISRC2 Packet Byte 0 (ISRC2_PB0). This is transmitted

only when the ISRC_ continue bit (Register 0xC8,

Bit 7) is set to 1.

Rev. 0 | Page 25 of 44

Page 26

AD9381

2-WIRE SERIAL CONTROL REGISTER DETAILS

CHIP IDENTIFICATION

0x00—Bits[7:0] Chip Revision

An 8-bit value that reflects the current chip revision.

0x11—Bit[7] HSYNC Source

0 = HSYNC, 1 = SOG. The power-up default is 0. These

selections are ignored if Register 0x11, Bit 6 = 0.

0x11—Bit[6] HSYNC Source Override

0 = auto HSYNC source, 1 = manual HSYNC source. Manual

HSYNC source is defined in Register 0x11, Bit 7. The power-up

default is 0.

0x11—Bit[5] VSYNC Source

0 = VSYNC, 1 = VSYNC from SOG. The power-up default is 0.

These selections are ignored if Register 0x11, Bit 4 = 0.

0x11—Bit[4] VSYNC Source Override

0 = auto VSYNC source, 1 = manual VSYNC source. Manual

VSYNC source is defined in Register 0x11, Bit 5. The power-up

default is 0.

0x11—Bit[3] Channel Select

0 = Channel 0, 1 = Channel 1. The power-up default is 0. These

selections are ignored if Register 0x11, Bit 2 = 0.

0x11—Bit[2] Channel Select Override

0 = auto channel select, 1 = manual channel select. Manual

channel select is defined in Register 0x11, Bit 3. The power-up

default is 0.

0x11—Bit[1] Interface Select

0 = analog interface, 1 = digital interface. The power-up default

is 0. These selections are ignored if Register 0x11, Bit 0 = 0.

0x11—Bit[0] Interface Select Override

0 = auto interface select, 1 = manual interface select. Manual

interface select is defined in Register 0x11, Bit 1. The power-up

default is 0.

0x12—Bit[7] Input HSYNC Polarity

0 = active low, 1 = active high. The power-up default is 1. These

selections are ignored if Register 10x2, Bit 6 = 0.

0x12—Bit[6] HSYNC Polarity Override

0 = auto HSYNC polarity, 1 = manual HSYNC polarity. Manual

HSYNC polarity is defined in Register 0x11, Bit 7. The powerup default is 0.

0x12—Bit[5] Input VSYNC Polarity

0 = active low, 1 = active high. The power-up default is 1. These

selections are ignored if Register 0x11, Bit 4 = 0.

0x12—Bit[4] VSYNC Polarity Override

0 = auto VSYNC polarity, 1 = manual VSYNC polarity. Manual

VSYNC polarity is defined in Register 0x11, Bit 5. The powerup default is 0.

0x17—Bits[3:0] HSYNCs per VSYNC MSBs

The 4 MSBs of the 12-bit counter that reports the number of

HSYNCs/VSYNC on the active input. This is useful in

determining the mode and an aid in setting the PLL divide

ratio.

0x18—Bits[7:0] HSYNCs per VSYNC LSBs

The 8 LSBs of the 12-bit counter that reports the number of

HSYNCs/VSYNC on the active input.

0x21—Bit[5] VSYNC Filter Enable

The purpose of the VSYNC filter is to guarantee the position of

the VSYNC edge with respect to the HSYNC edge and to

generate a field signal. The filter works by examining the

placement of VSYNC and regenerating a correctly placed

VSYNC one line later. The VSYNC is first checked to see

whether it occurs in the Field 0 position or the Field 1 position.

This is done by checking the leading edge position against the

sync separator threshold and the HSYNC position. The HSYNC

width is divided into four quadrants with Quadrant 1 starting at

the HSYNC leading edge plus a sync separator threshold. If the

VSYNC leading edge occurs in Quadrant 1 or Quadrant 4, the

field is set to 0 and the output VSYNC is placed coincident with

the HSYNC leading edge. If the VSYNC leading edge occurs in

Quadrant 2 or Quadrant 3, the field is set to 1 and the output

VSYNC leading edge is placed in the center of the line. In this

way, the VSYNC filter creates a predictable relative position

between HSYNC and VSYNC edges at the output.

If the VSYNC occurs near the HSYNC edge, this guarantees

that the VSYNC edge follows the HSYNC edge. This performs

filtering also in that it requires a minimum of 64 lines between

VSYNCs. The VSYNC filter cleans up extraneous pulses that

might occur on the VSYNC. This should be enabled whenever

the HSYNC/VSYNC count is used. Setting this bit to 0 disables

the VSYNC filter. Setting this bit to 1 enables the VSYNC filter.

Power-up default is 0.

0x21—Bit[4] VSYNC Duration Enable

This enables the VSYNC duration block that is designed to be

used with the VSYNC filter. Setting the bit to 0 leaves the

VSYNC output duration unchanged; setting the bit to 1 sets the

VSYNC output duration based on Register 0x22. The power-up

default is 0.

Rev. 0 | Page 26 of 44

Page 27

AD9381

0x22—Bits[7:0] VSYNC Duration

This is used to set the output duration of the VSYNC, and is

designed to be used with the VSYNC filter. This is valid only if

Register 0x21, Bit 4 is set to 1. Power-up default is 4.

0x23—Bits[7:0]HSYNC Duration

An 8-bit register that sets the duration of the HSYNC output

pulse. The leading edge of the HSYNC output is triggered by

the internally generated, phase-adjusted PLL feedback clock.

The AD9381 then counts a number of pixel clocks equal to the

value in this register. This triggers the trailing edge of the

HSYNC output, which is also phase-adjusted. The power-up

default is 32.

0x24—Bit[7] HSYNC Output Polarity

This bit sets the polarity of the HSYNC output. Setting this bit

to 0 sets the HSYNC output to active low. Setting this bit to 1

sets the HSYNC output to active high. Power-up default setting

is 1.

0x24—Bit[6] VSYNC Output Polarity

This bit sets the polarity of the VSYNC output (both DVI and

analog). Setting this bit to 0 sets the VSYNC output to active

low. Setting this bit to 1 sets the VSYNC output to active high.

Power-up default is 1.

0x24—Bit[5] Display Enable Output Polarity

This bit sets the polarity of the display enable (DE) for both

DVI and analog. 0 = DE output polarity is negative. 1 = DE

output polarity is positive.

The power-up default is 1.

0x24—Bit[4] Field Output Polarity

This bit sets the polarity (both DVI and analog) of the field

output signal on Pin 21. 0 = active low out. 1 = active high out.

The power-up default is 1.

0x24—Bit[0] Output Clock Invert

This bit allows inversion of the output clock as specified by

Register 0x25, Bits 7 to 6. 0 = noninverted clock. 1 =inverted

clock .The power-up default setting is 0.

0x25—Bits[7:6] Output Clock Select

These bits select the clock output on the DATACLK pin. They

include 1/2× clock, a 2× clock, a 90° phase shifted clock or the

normal pixel clock. The power-up default setting is 01.

Table 12. Output Clock Select

Select Result

00 ½× pixel clock

01 1× pixel clock

10 2× pixel clock

11 90° phase 1× pixel clock

0x25—Bits[5:4] Output Drive Strength

These two bits select the drive strength for all the high speed

digital outputs (except VSOUT, A0 and O/E field). Higher drive

strength results in faster rise/fall times and in general makes it

easier to capture data. Lower drive strength results in slower

rise/fall times and helps to reduce EMI and digitally generated

power supply noise. The power-up default setting is 11.

Table 13. Output Drive Strength

Output Drive Result

00 Low output drive strength

01 Medium low output drive strength

10 Medium high output drive strength

11 High output drive strength

0x25—Bits[3:2] Output Mode

These bits choose between four options for the output mode,

one of which is exclusive to an HDMI input. 4:4:4 mode is

standard RGB; 4:2:2 mode is YCrCb, which reduces the number

of active output pins from 24 to 16; 4:4:4 is double data rate

(DDR) output mode; and the data is RGB mode that changes on

every clock edge. The power-up default setting is 00.