4 × 1 Wideband

a

FEATURES

34 MHz Full Power Bandwidth

60.1 dB Gain Flatness to 8 MHz

72 dB Crosstalk Rejection @ 10 MHz

0.038/0.01% Differential Phase/Gain

Cascadable for Switch Matrices

MIL-STD-883 Compliant Versions Available

APPLICATIONS

Video Routing

Medical Imaging

Electro Optics

ECM Systems

Radar Systems

Data Acquisition

GENERAL DESCRIPTION

The AD9300 is a monolithic high speed video signal multiplexer

usable in a wide variety of applications.

Its four channels of video input signals can be randomly

switched at megahertz rates to the single output. In addition,

multiple devices can be configured in either parallel or cascade

arrangements to form switch matrices. This flexibility in using

the AD9300 is possible because the output of the device is in a

high-impedance state when the chip is not enabled; when the

chip is enabled, the unit acts as a buffer with a high input impedance and low output impedance.

An advanced bipolar process provides fast, wideband switching

capabilities while maintaining crosstalk rejection of 72 dB at

10 MHz. Full power bandwidth is a minimum 27 MHz. The

device can be operated from ±10 V to ±15 V power supplies.

Video Multiplexer

AD9300

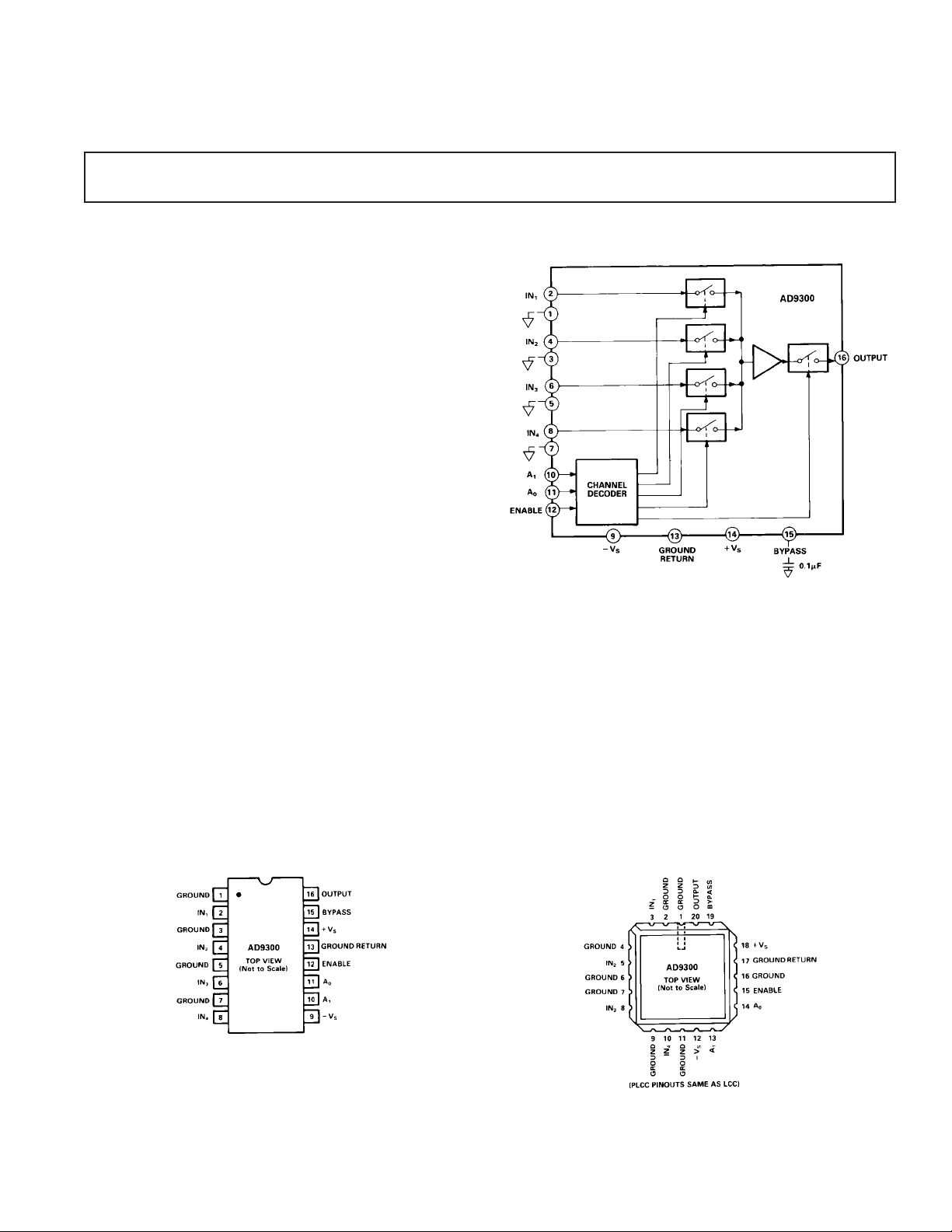

FUNCTIONAL BLOCK DIAGRAM

(Based on Cerdip)

The AD9300K is available in a 16-pin ceramic DIP and a

20-pin PLCC and is designed to operate over the commercial

temperature range of 0°C to +70°C. The AD9300TQ is a

hermetic 16-pin ceramic DIP for military temperature range

(–55°C to +125°C) applications. This part is also available processed to MIL-STD-883. The AD9300 is available in a 20-pin

LCC as the model AD9300TE, which operates over a temperature range of –55°C to +125°C.

The AD9300 Video Multiplexer is available in versions compliant with MIL-STD-883. Refer to the Analog Devices Military

Products Databook or current AD9300/883B data sheet for detailed specifications.

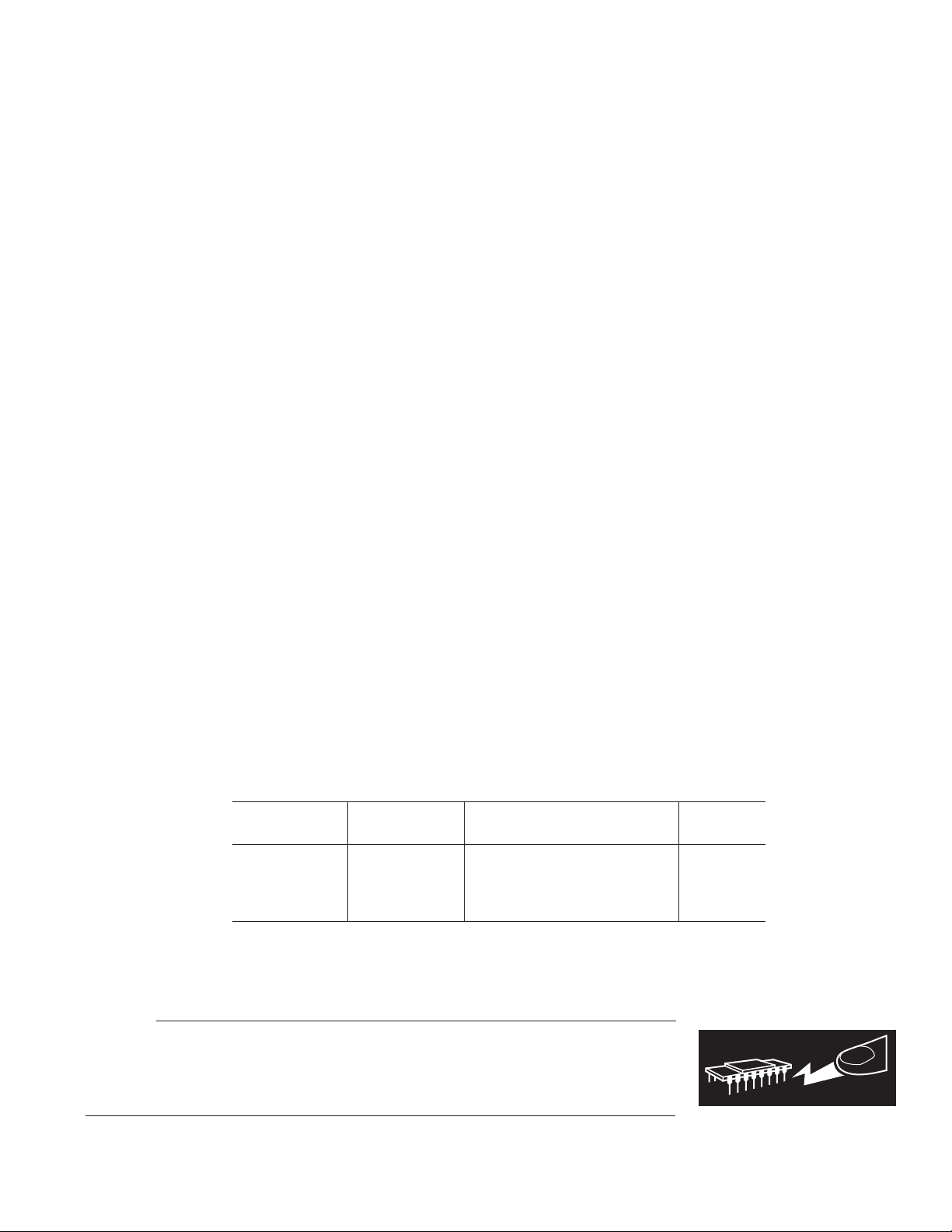

PIN DESIGNATIONS

DIP

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

LCC and PLCC

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1996

AD9300–SPECIFICA TIONS

ELECTRICAL CHARACTERISTICS

(6VS = 612 V 6 5%; CL = 10 pF; RL = 2 kV, unless otherwise noted)

COMMERCIAL

08C to +708C

Test AD9300KQ/KP

Parameter (Conditions) Temp Level Min Typ Max Units

INPUT CHARACTERISTICS

Input Offset Voltage +25°CI 3 10 mV

Input Offset Voltage Full VI 14 mV

Input Offset Voltage Drift

2

Full V 75 µV/°C

Input Bias Current +25°C I 15 37 µA

Input Bias Current Full VI 55 µA

Input Resistance +25°C V 3.0 MΩ

Input Capacitance +25°CV 2 pF

Input Noise Voltage (dc to 8 MHz) +25°CV 16 µV rms

TRANSFER CHARACTERISTICS

Voltage Gain

Voltage Gain

DC Linearity

Gain Tolerance (V

3

3

4

= ±1 V)

IN

+25°C I 0.990 0.994 V/V

Full VI 0.985 V/V

+25°C V 0.01 %

dc to 5 MHz +25°C I 0.05 0.1 dB

5 MHz to 8 MHz +25°C I 0.1 0.3 dB

Small-Signal Bandwidth +25°C V 350 MHz

(V

= 100 mV p-p)

IN

Full Power Bandwidth

(V

= 2 V p-p)

IN

5

+25°C I 27 34 MHz

Output Swing Full VI ±2V

Output Current (Sinking @ = +25°C) +25°CV 5 mA

Output Resistance +25°C IV, V 9 15 Ω

DYNAMIC CHARACTERISTICS

Slew Rate

6

+25°C I 170 215 V/µs

Settling Time (to 0.1% on ±2 V Output) +25°C IV 70 100 ns

Overshoot

To T-Step

To Pulse

Differential Phase

Differential Gain

Crosstalk Rejection

Three Channels

One Channel

SWITCHING CHARACTERISTICS

AX Input to Channel HIGH Time

A

Input to Channel LOW Time14 (t

X

Enable to Channel ON Time

Enable to Channel OFF Time

Switching Transient

7

8

9

9

10

11

12

13

(t

HIGH

) +25°C I 35 45 ns

LOW

15

(tON) +25°C I 35 45 ns

16

(t

) +25°C I 35 45 ns

17

OFF

+25°C V <0.1 %

+25°C V <10 %

+25°C IV 0.03 0.1 °

+25°C IV 0.01 0.1 %

+25°CIV 68 72 dB

+25°CIV 70 76 dB

) +25°C I 40 50 ns

+25°CV 60 mV

DIGITAL INPUTS

Logic “1” Voltage Full VI 2 V

Logic “0” Voltage Full VI 0.8 V

Logic “1” Current Full VI 5 µA

Logic “0” Current Full VI 1 µA

POWER SUPPLY

Positive Supply Current (+12 V) +25°C I 13 16 mA

Positive Supply Current (+12 V) Full VI 13 16 mA

Negative Supply Current (–12 V) +25°C I 12.5 15 mA

Negative Supply Current (–12 V) Full VI 12.5 16 mA

Power Supply Rejection Ratio Full VI 67 75 dB

(±V

= ±12 V ± 5%)

S

Power Dissipation (±12 V)

l8

+25°C V 306 mW

–2–

REV. A

AD9300

NOTES

11

Permanent damage may occur if any one absolute maximum rating is exceeded. Functional operation is not implied, and device reliability may be impaired by

exposure to higher-than-recommended voltages for extended periods of time.

12

Measured at extremes of temperature range.

13

Measured as slope of V

14

Measured as worst deviation from endpoint fit with VIN = ±1 V.

15

Full Power Bandwidth (FPBW) based on Slew Rate (SR). FPBW = SR/2 π V

16

Measured between 20% and 80% transition points of ±1 V output.

17

T-Step = Sin2 × Step, when Step between 0 V and +700 mV points has 10% to 90% risetime = 125 ns.

18

Measured with a pulse input having slew rate >250 V/µs.

19

Measured at output between 0.28 V dc and 1.0 V dc with VIN = 284 mV p-p at 3.58 MHz and 4.43 MHz.

10

This specification is critically dependent on circuit layout. Value shown is measured with selected channel grounded and 10 MHz 2 V p-p signal applied to remaining

three channels. If selected channel is grounded through 75 Ω, value is approximately 6 dB higher.

11

This specification is critically dependent on circuit layout. Value shown is measured with selected channel grounded and 10 MHz 2 V p-p signal applied to one other

channel. If selected channel is grounded through 75 Ω, value is approximately 6 dB higher. Minimum specification in ( ) applies to DIPs.

12

Consult system timing diagram.

13

Measured from address change to 90% point of –2 V to +2 V output LOW-to-HIGH transition.

14

Measured from address change to 90% point of +2 V to –2 V output HIGH-to-LOW transition.

15

Measured from 50% transition point of ENABLE input to 90% transition of 0 V to –2 V and 0 V to +2 V output.

16

Measured from 50% transition point of ENABLE input to 10% transition of +2 V to 0 V and –2 V to 0 V output.

17

Measured while switching between two grounded channels.

18

Maximum power dissipation is a package-dependent parameter related to the following typical thermal impedances:

16-Pin Ceramic θJA = 87°C/W; θJC = 25°C/W

20-Pin LCC θJA = 74°C/W; θJC = 10°C/W

20-Pin PLCC θJA = 71°C/W; θ

Specifications subject to change without notice.

versus VIN with VIN = ±1 V.

OUT

= 26°C/W

JC

PEAK

ABSOLUTE MAXIMUM RATINGS

l

Supply Voltages (±VS) . . . . . . . . . . . . . . . . . . . . . . . . . . ±16 V

Analog Input Voltage Each Input

(IN

thru IN4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±3.5 V

1

Differential Voltage Between Any Two

Inputs (IN

Digital Input Voltages (A

thru IN4) . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 V

1

, A1, ENABLE) . . .–0.5 V to +5.5 V

0

Output Current

Sinking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.0 mA

Sourcing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.0 mA

Operating Temperature Range

AD9300KQ/KP . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . +175°C

Lead Soldering (10 sec) . . . . . . . . . . . . . . . . . . . . . . . +300°C

ORDERlNG GUlDE

Temperature Package

Device Range Description Option

AD9300KQ 0°C to +70°C 16-Pin Cerdip, Commercial Q-16

AD9300TE/883B

AD9300TQ/883B

AD9300KP 0°C to +70°C 20-Pin PLCC, Commercial P-20A

NOTES

1

E = Ceramic Leadless Chip Carrier; P = Plastic Leaded Chip Carrier; Q = Cerdip.

2

For specifications, refer to Analog Devices Military Products Databook .

2

–55°C to +125°C 20-Pin LCC, Military Temperature E-20A

2

–55°C to +125°C 16-Pin Cerdip, Military Temperature Q-16

EXPLANATION OF TEST LEVELS

Test Level I – 100% production tested.

Test Level II – 100% production tested at +25°C, and

sample tested at specified temperatures.

Test Level III – Sample tested only.

Test Level IV – Parameter is guaranteed by design and

characterization testing.

Test Level V – Parameter is a typical value only.

Test Level VI – All devices are 100% production tested at

+25°C. 100% production tested at tempera-

ture extremes for military temperature de-

vices; sample tested at temperature extremes

for commercial/industrial devices.

1

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9300 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. A

–3–

WARNING!

ESD SENSITIVE DEVICE

Loading...

Loading...