Dual Channel 8-Bit

REV. F

©1999-2011 Analog Devices, Inc. All rights reserved.

781/461-3113

a

FEATURES

Complete Dual Matching ADC

Low Power Dissipation: 225 mW (+3 V Supply)

Single Supply: 2.7 V to 5.5 V

Differential Nonlinearity Error: 0.1 LSB

On-Chip Analog Input Buffers

On-Chip Reference

Signal-to-Noise Ratio: 49.2 dB

Over Seven Effective Bits

Spurious-Free Dynamic Range: –65 dB

No Missing Codes Guaranteed

28-Lead SSOP

PRODUCT DESCRIPTION

The AD9281 is a complete dual channel, 28 MSPS, 8-bit

CMOS ADC. The AD9281 is optimized specifically for applications where close matching between two ADCs is required (e.g.,

I/Q channels in communications applications). The 28 MHz

sampling rate and wide input bandwidth will cover both narrowband and spread-spectrum channels. The AD9281 integrates

two 8-bit, 28 MSPS ADCs, two input buffer amplifiers, an internal

voltage reference and multiplexed digital output buffers.

Each ADC incorporates a simultaneous sampling sample-andhold amplifier at its input. The analog inputs are buffered; no

external input buffer op amp will be required in most applications. The ADCs are implemented using a multistage pipeline

architecture that offers accurate performance and guarantees no

missing codes. The outputs of the ADCs are ported to a multiplexed digital output buffer.

The AD9281 is manufactured on an advanced low cost CMOS

process, operates from a single supply from 2.7 V to 5.5 V, and

consumes 225 mW of power (on 3 V supply). The AD9281

input structure accepts either single-ended or differential signals,

providing excellent dynamic performance up to and beyond

14 MHz Nyquist input frequencies.

Resolution CMOS ADC

AD9281

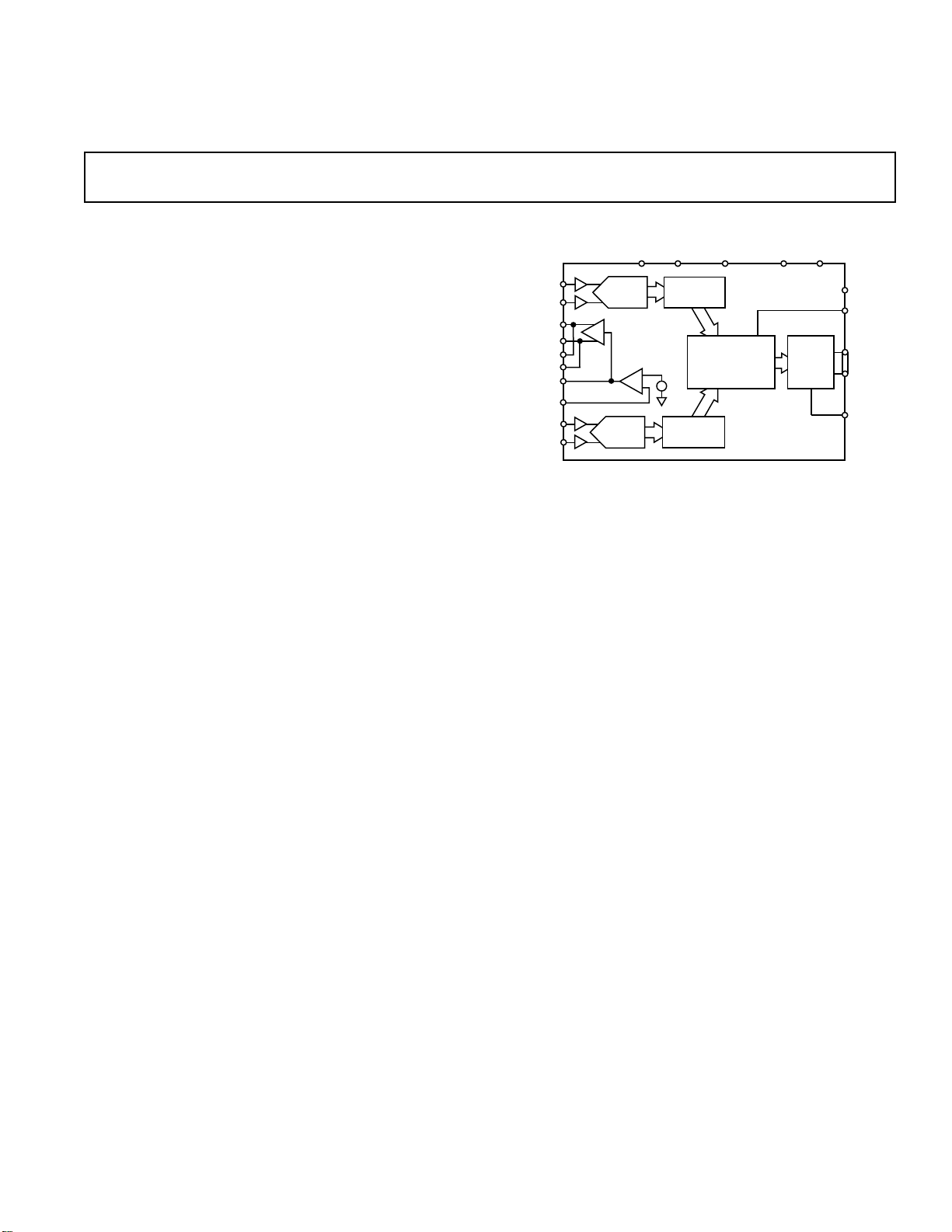

FUNCTIONAL BLOCK DIAGRAM

IINA

IINB

IREFB

IREFT

QREFB

QREFT

VREF

REFSENSE

QINB

QINA

AVDD AVSS

"I" ADC

REFERENCE

BUFFER

"Q" ADC

CLOCK

I

REGISTER

ASYNCHRONOUS

MULTIPLEXER

1V

Q

REGISTER

PRODUCT HIGHLIGHTS

1. Dual 8-Bit, 28 MSPS ADC

A pair of high performance 28 MSPS ADCs that are optimized for spurious free dynamic performance are provided for

encoding of I and Q or diversity channel information.

2. Low Power

Complete CMOS Dual ADC function consumes a low

225 mW on a single supply (on 3 V supply). The AD9281

operates on supply voltages from 2.7 V to 5.5 V.

3. On-Chip Voltage Reference

The AD9281 includes an on-chip compensated bandgap

voltage reference pin programmable for 1 V or 2 V.

4. On-chip analog input buffers eliminate the need for external

op amps in most applications.

5. Single 8-Bit Digital Output Bus

The AD9281 ADC outputs are interleaved onto a single

output bus saving board space and digital pin count.

6. Small Package

The AD9281 offers the complete integrated function in a

compact 28-lead SSOP package.

7. Product Family

The AD9281 dual ADC is pin compatible with a dual 10-bit

ADC (AD9201).

DVDD DVSS

AD9281

THREE-

STATE

OUTPUT

BUFFER

SLEEP

SELECT

DATA

8 BITS

CHIP

SELECT

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax:

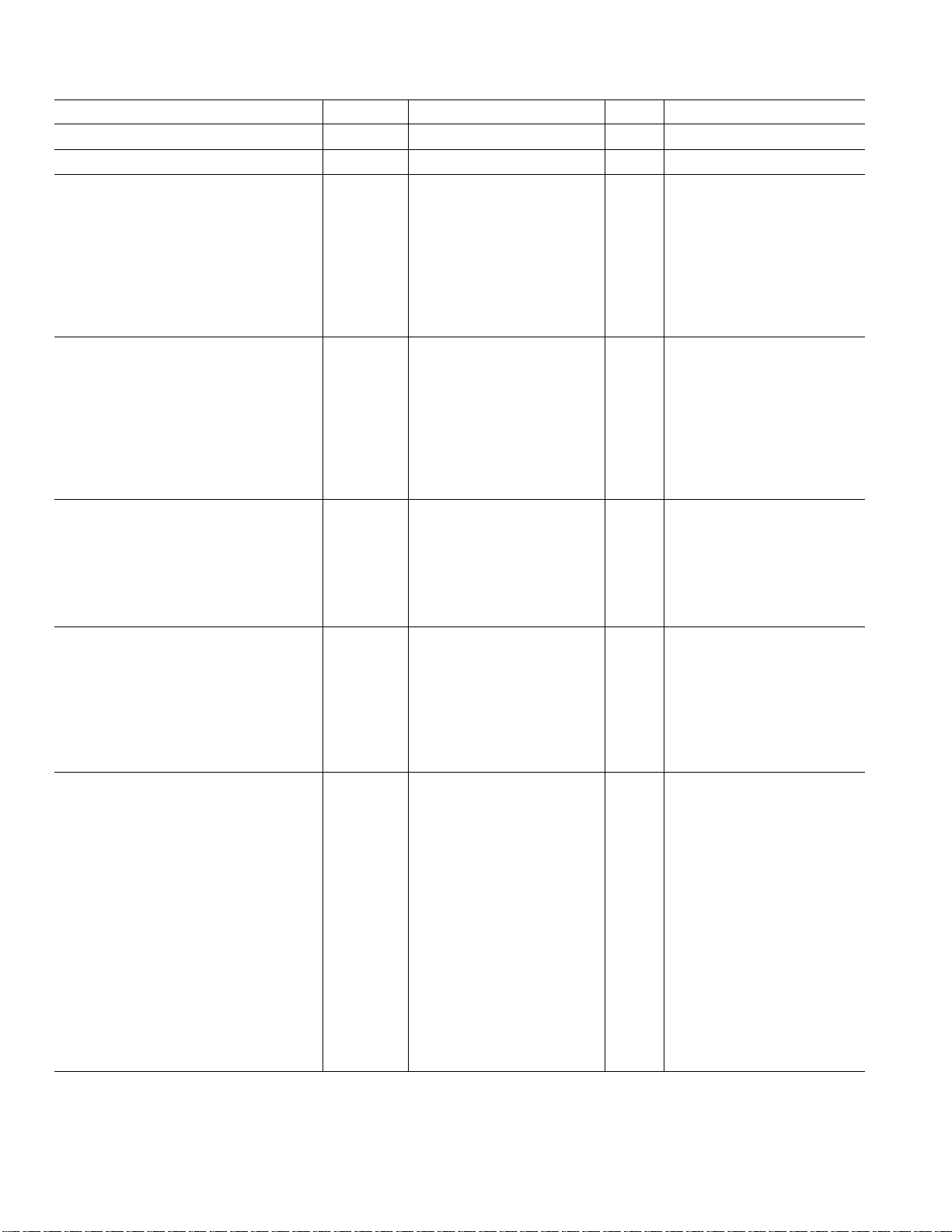

AD9281–SPECIFICATIONS

REV. F

(AVDD = +3 V, DVDD = +3 V, F

unless otherwise noted)

= 28 MSPS, VREF = 2 V, INB = 0.5 V, T

SAMPLE

MIN

to T

Parameter Symbol Min Typ Max Units Condition

RESOLUTION 8 Bits

CONVERSION RATE F

S

28 MHz (32 MHz at +25°C)

DC ACCURACY

Differential Nonlinearity DNL ± 0.1 LSB REFT = 1.0 V, REFB = 0.0 V

Integral Nonlinearity INL ± 0.25 LSB

Differential Nonlinearity (SE)

Integral Nonlinearity (SE)

Zero-Scale Error, Offset Error E

Full-Scale Error, Gain Error E

1

1

DNL ±0.2 ± 1.0 LSB REFT = 1.0 V, REFB = 0.0 V

INL ± 0.3 ± 1.5 LSB

ZS

FS

± 1 ± 3.2 % FS

± 1.2 ± 5.4 % FS

Gain Match ± 0.2 LSB

Offset Match ± 1.2 LSB

ANALOG INPUT

Input Voltage Range AIN –0.5 AVDD/2 V

Input Capacitance C

Aperture Delay t

Aperture Uncertainty (Jitter) t

IN

AP

AJ

2pF

4ns

2ps

Aperture Delay Match 2 ps

Input Bandwidth (–3 dB) BW

Small Signal (–20 dB) 240 MHz

Full Power (0 dB) 245 MHz

INTERNAL REFERENCE

Output Voltage (1 V Mode) VREF 1 V REFSENSE = VREF

Output Voltage Tolerance (1 V Mode) ± 10 mV

Output Voltage (2 V Mode) VREF 2 V REFSENSE = GND

Output Voltage Tolerance (2 V Mode) ± 15 mV

Load Regulation (1 V Mode) VREF ±10 ± 35 mV 1 mA Load Current

Load Regulation (2 V Mode) ± 15 mV 1 mA Load Current

POWER SUPPLY

Operating Voltage AVDD 2.7 3 5.5 V

DVDD 2.7 3 5.5 V

Supply Current I

Power Consumption P

AVDD

I

DVDD

D

75 mA

0.1 mA

225 260 mW

Power-Down 16 mW STBY = AVDD, Clock Low

Power Supply Rejection PSR 0.15 0.75 % FS

DYNAMIC PERFORMANCE

2

Signal-to-Noise and Distortion SINAD

f = 3.58 MHz 46.4 49.1 dB

f = 14 MHz 48 dB

Signal-to-Noise SNR

f = 3.58 MHz 47.8 49.2 dB

f = 14 MHz 48.5 dB

Total Harmonic Distortion THD

f = 3.58 MHz –67.5 –49.5 dB

f = 14 MHz –60 dB

Spurious Free Dynamic Range SFDR

f = 3.58 MHz 49.6 65 dB

f = 14 MHz 56 dB

Two-Tone Intermodulation Distortion

3

IMD –58 dB f = 44.9 MHz and 45.52 MHz

Differential Phase DP 0.2 Degree NTSC 40 IRE Mod Ramp

Differential Gain DG 0.08 % F

= 14.3 MHz

S

Crosstalk Rejection –62 dB

MAX

–2–

Parameter Symbol Min Typ Max Units Condition

REV. F

DYNAMIC PERFORMANCE (SE)

1

Signal-to-Noise and Distortion SINAD

f = 3.58 MHz 47.2 dB

Signal-to-Noise SNR

f = 3.58 MHz 48 dB

Total Harmonic Distortion THD

f = 3.58 MHz –55 dB

Spurious Free Dynamic Range SFDR

f = 3.58 MHz –58 dB

DIGITAL INPUTS

High Input Voltage V

Low Input Voltage V

DC Leakage Current I

Input Capacitance C

IH

IL

IN

IN

2.4 V

0.3 V

± 6 µA

2pF

LOGIC OUTPUT (with DVDD = 3 V)

High Level Output Voltage

(I

= 50 µA) V

OH

OH

2.88 V

Low Level Output Voltage

(IOL = 1.5 mA) V

OL

0.095 V

LOGIC OUTPUT (with DVDD = 5 V)

High Level Output Voltage

(I

= 50 µA) V

OH

OH

4.5 V

Low Level Output Voltage

(I

= 1.5 mA) V

OL

Data Valid Delay t

MUX Select Delay t

Data Enable Delay t

OL

OD

MD

ED

0.4 V

11 ns

7ns

13 ns CL = 20 pF. Output Level to

90% of Final Value

Data High-Z Delay t

DHZ

13 ns

CLOCKING

Clock Pulsewidth High t

Clock Pulsewidth Low t

CH

CL

16.9 ns

16.9 ns

Pipeline Latency 3.0 Cycles

NOTES

1

SE is single ended input, REFT = 1.5 V, REFB = –0.5 V.

2

AIN differential 2 V p-p, REFT = 1.5 V, REFB = –0.5 V.

3

IMD referred to larger of two input signals.

Specifications subject to change without notice.

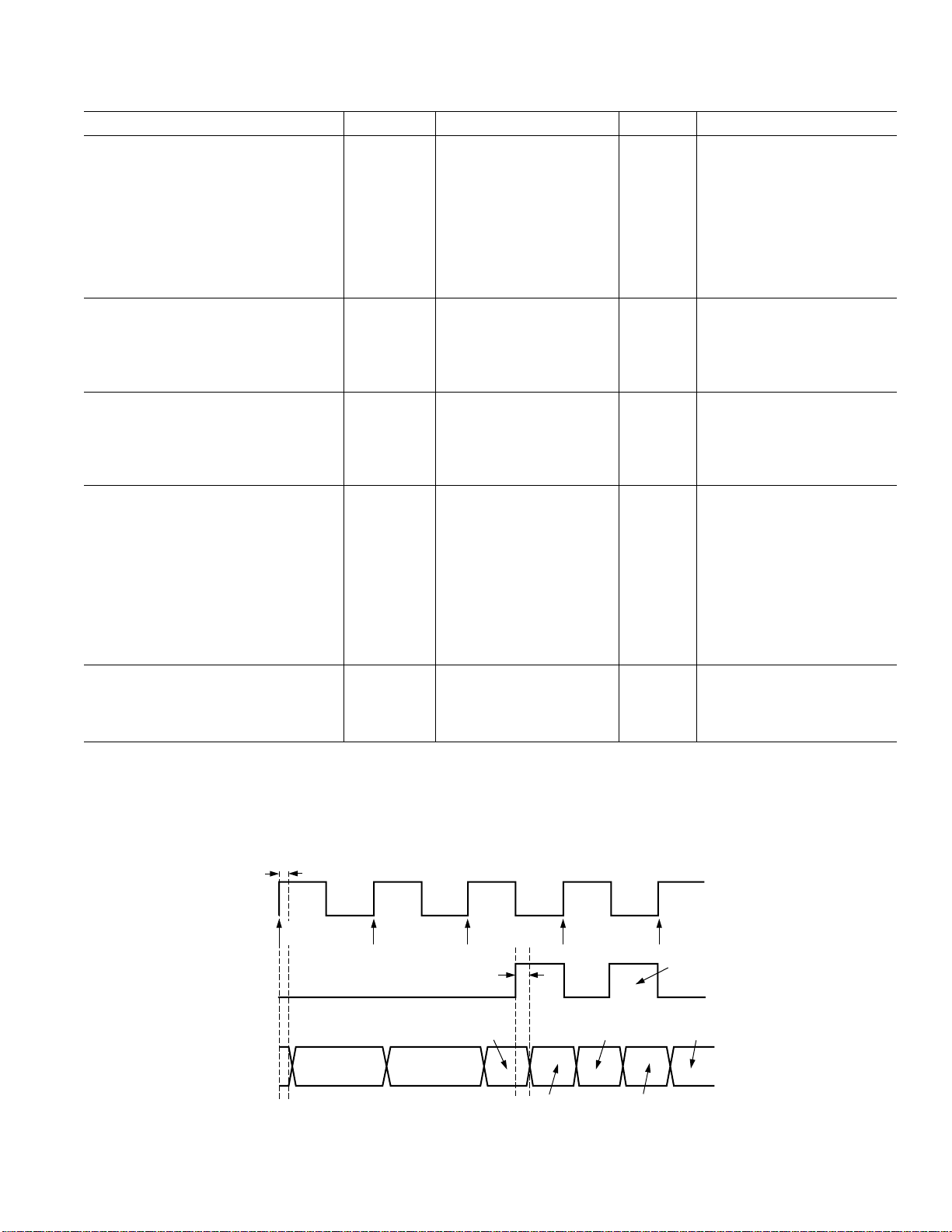

AD9281

CLOCK

INPUT

SELECT

INPUT

DATA

OUTPUT

t

OD

ADC SAMPLE

#1

SAMPLE #1-3

Q CHANNEL

ADC SAMPLE#2ADC SAMPLE

Q CHANNEL

OUTPUT ENABLED

OUTPUT

#3

t

MD

SAMPLE #1-1

Q CHANNEL

OUTPUT

SAMPLE #1-2

Q CHANNEL

OUTPUT

Figure 1. ADC Timing

–3–

ADC SAMPLE

#4

SAMPLE #1-1

I CHANNEL

OUTPUT

SAMPLE #1

Q CHANNEL

OUTPUT

SAMPLE #1

I CHANNEL

OUTPUT

ADC SAMPLE

#5

I CHANNEL

OUTPUT ENABLED

SAMPLE #2

Q CHANNEL

OUTPUT

AD9281

REV. F

DNC

DNC

DNC

DNC

Do not connect

Do not connect

ABSOLUTE MAXIMUM RATINGS*

With

Respect

Parameter to Min Max Units

AVDD AVSS –0.3 +6.5 V

DVDD DVSS –0.3 +6.5 V

AVSS DVSS –0.3 +0.3 V

AVDD DVDD –6.5 +6.5 V

CLK AVSS –0.3 AVDD + 0.3 V

Digital Outputs DVSS –0.3 DVDD + 0.3 V

AINA, AINB AVSS –1.0 AVDD + 0.3 V

VREF AVSS –0.3 AVDD + 0.3 V

REFSENSE AVSS –0.3 AVDD + 0.3 V

REFT, REFB AVSS –0.3 AVDD + 0.3 V

Junction Temperature +150 °C

Storage Temperature –65 +150 °C

Lead Temperature

10 sec +300 °C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum ratings

for extended periods may effect device reliability.

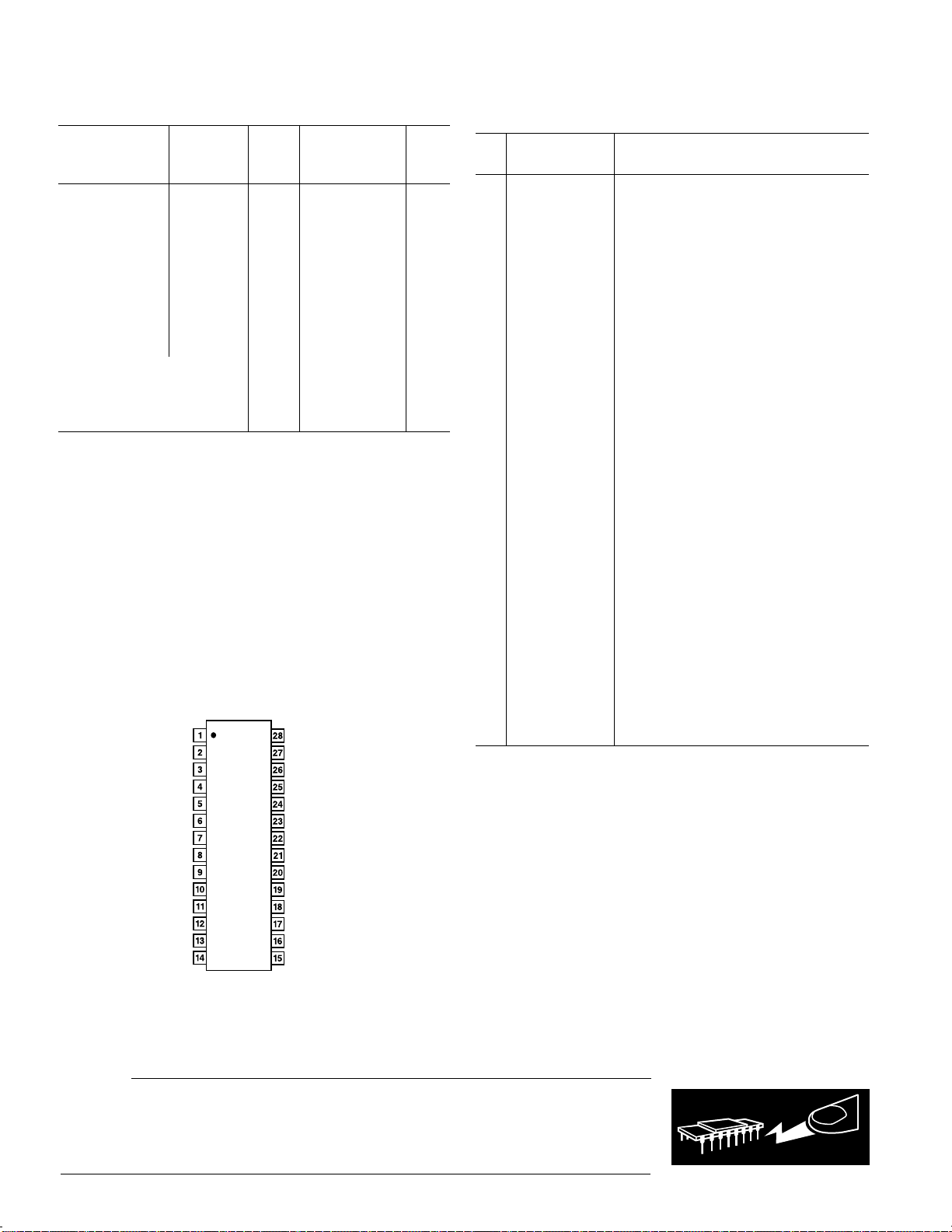

PIN CONFIGURATION

DVSS

DVDD

(LSB) D0

(MSB) D7

SELECT

CLOCK

AD9281

D1

TOP VIEW

(Not to Scale)

D2

D3

D4

D5

D6

NC = NO CONNECT

CHIP-SELECT

INA-Q

INB-Q

REFT-Q

REFB-Q

AVDD

VREF

REFSENSE

AVSS

REFB-I

REFT-I

INB-I

INA-I

SLEEP

PIN FUNCTION DESCRIPTIONS

P

in

No. Name Description

1 DVSS Digital Ground

2 DVDD Digital Supply

3

4

5 D0 Bit 0 (LSB)

6 D1 Bit 1

7 D2 Bit 2

8 D3 Bit 3

9 D4 Bit 4

10 D5 Bit 5

11 D6 Bit 6

12 D7 Bit 7 (MSB)

13 SELECT Hi I Channel Out, Lo Q Channel Out

14 CLOCK Clock

15 SLEEP Hi Power Down, Lo Normal Operation

16 INA-I I Channel, A Input

17 INB-I I Channel, B Input

18 REFT-I Top Reference Decoupling, I Channel

19 REFB-I Bottom Reference Decoupling, I Channel

20 AVSS Analog Ground

21 REFSENSE Reference Select

22 VREF Internal Reference Output

23 AVDD Analog Supply

24 REFB-Q Bottom Reference Decoupling, Q Channel

25 REFT-Q Top Reference Decoupling, Q Channel

26 INB-Q Q Channel B Input

27 INA-Q Q Channel A Input

28 CHIP-SELECT Hi-High Impedance, Lo-Normal Operation

DEFINITIONS OF SPECIFICATIONS

INTEGRAL NONLINEARITY (INL)

Integral nonlinearity refers to the deviation of each individual

code from a line drawn from “zero” through “full scale.” The

point used as “zero” occurs 1/2 LSB before the first code transition. “Full scale” is defined as a level 1 1/2 LSBs beyond the last

code transition. The deviation is measured from the center of

each particular code to the true straight line.

DIFFERENTIAL NONLINEARITY (DNL, NO MISSING

CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. It is often

specified in terms of the resolution for which no missing codes

(NMC) are guaranteed.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9281 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–4–

AVDD

REV. F

DRVDD

AVDD

AVDD

AVDD

AD9281

AVDD

AVSS

DRVSS

DRVSS

AVSS

AVSS

AVSS

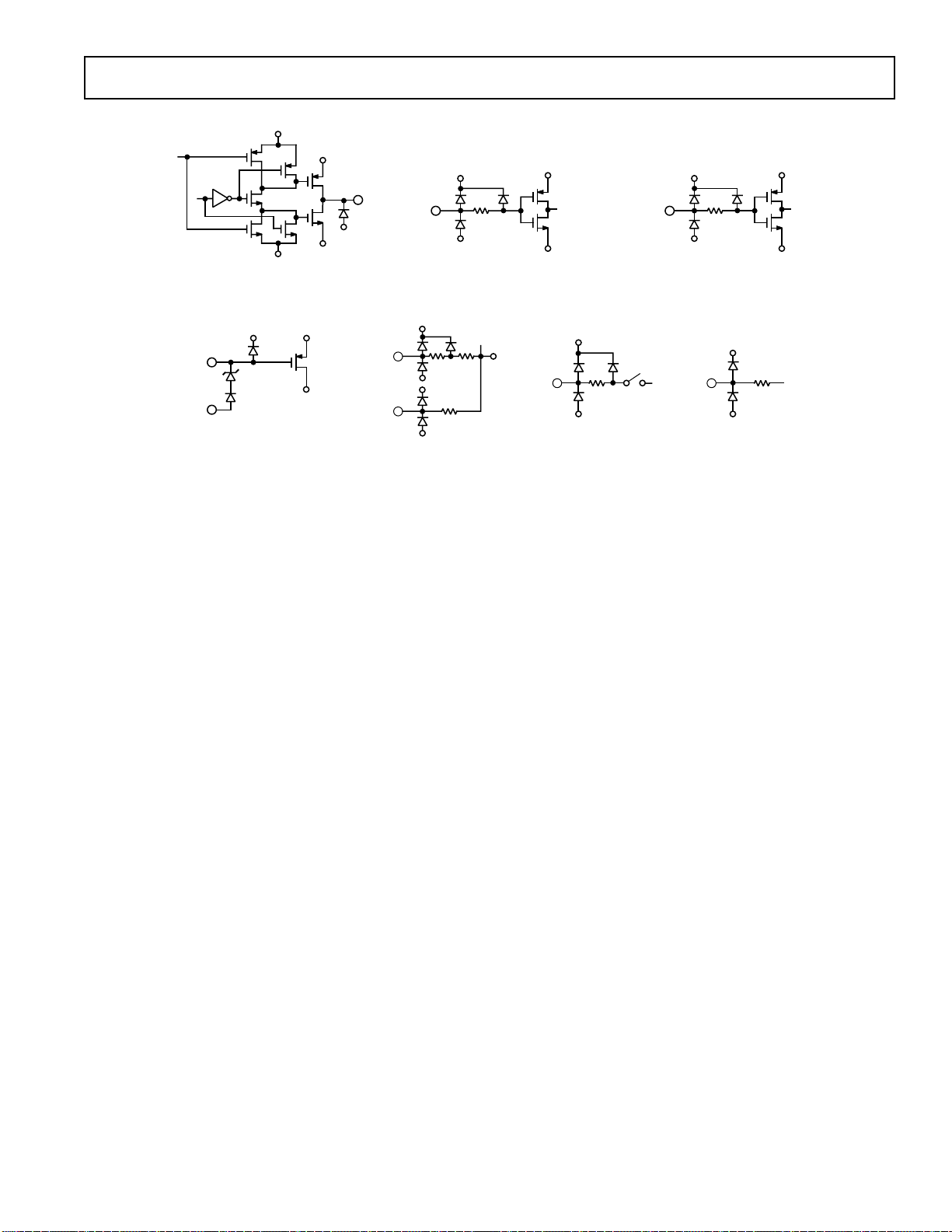

a. D0–D9 b. Three-State Standby c. CLK

AVDD

AVDD

AVSS

AVSS

AVDD

AVSS

AVDD

AVSS

AVSS

AVDD

IN

AVDD

REFBS

AVSS

REFBF

d. INA, INB e. Reference f. REFSENSE g. VREF

Figure 2. Equivalent Circuits

OFFSET ERROR

The first transition should occur at a level 1 LSB above “zero.”

Offset is defined as the deviation of the actual first code transi-

scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference

between the first and last code transitions.

tion from that point.

GAIN MATCH

OFFSET MATCH

The change in gain error between I and Q channels.

The change in offset error between I and Q channels.

PIPELINE DELAY (LATENCY)

EFFECTIVE NUMBER OF BITS (ENOB)

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula,

N = (SINAD – 1.76)/6.02

It is possible to get a measure of performance expressed as N,

the effective number of bits.

The number of clock cycles between conversion initiation and

the associated output data being made available. New output

data is provided every rising clock edge.

MUX SELECT DELAY

The delay between the change in SELECT pin data level and

valid data on output pins.

Thus, effective number of bits for a device for sine wave inputs

at a given input frequency can be calculated directly from its

measured SINAD.

POWER SUPPLY REJECTION

The specification shows the maximum change in full scale from

the value with the supply at the minimum limit to the value

TOTAL HARMONIC DISTORTION (THD)

with the supply at its maximum limit.

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and

is expressed as a percentage or in decibels.

APERTURE JITTER

Aperture jitter is the variation in aperture delay for successive

samples and is manifested as noise on the input to the A/D.

SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the measured input signal

to the rms sum of all other spectral components below the

Nyquist frequency, excluding the first six harmonics and dc.

The value for SNR is expressed in decibels.

APERTURE DELAY

Aperture delay is a measure of the Sample-and-Hold Amplifier

(SHA) performance and is measured from the rising edge of the

clock input to when the input signal is held for conversion.

AVSS

SPURIOUS FREE DYNAMIC RANGE (SFDR)

The difference in dB between the rms amplitude of the input

signal and the peak spurious signal.

GAIN ERROR

The first code transition should occur for an analog value 1 LSB

above nominal negative full scale. The last transition should

occur for an analog value 1 LSB below the nominal positive full

–5–

SIGNAL-TO-NOISE AND DISTORTION (S/N+D, SINAD)

RATIO

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below

the Nyquist frequency, including harmonics but excluding dc.

The value for S/N+D is expressed in decibels.

Loading...

Loading...