Octal LNA/VGA/AAF/12-Bit ADC

A

A

FEATURES

8 channels of LNA, VGA, AAF, ADC, and I/Q demodulator

Low noise preamplifier (LNA)

Input-referred noise: 0.75 nV/√Hz typical at 5 MHz

(gain = 21.3 dB)

SPI-programmable gain: 15.6 dB/17.9 dB/21.3 dB

Single-ended input: V

550 mV p-p/367 mV p-p

Dual-mode active input impedance matching

Bandwidth (BW) > 100 MHz

Full-scale (FS) output: 4.4 V p-p differential

Variable gain amplifier (VGA)

Attenuator range: −42 dB to 0 dB

Postamp gain: 21 dB/24 dB/27 dB/30 dB

Linear-in-dB gain control

Antialiasing filter (AAF)

Programmable second-order LPF from 8 MHz to 18 MHz

Programmable HPF

Analog-to-digital converter (ADC)

12 bits at 10 MSPS to 80 MSPS

SNR: 70 dB

SFDR: 75 dB

Serial LVDS (ANSI-644, IEEE 1596.3 reduced range link)

Data and frame clock outputs

CW mode I/Q demodulator

Individual programmable phase rotation

Output dynamic range per channel >160 dBFS/√Hz

Low power: 195 mW per channel at 12 bits/40 MSPS (TGC),

94 mW per channel for CW Doppler

Flexible power-down modes

Overload recovery in <10 ns

Fast recovery from low power standby mode: <2 μs

100-lead TQFP_EP

maximum = 733 mV p-p/

IN

and CW I/Q Demodulator

AD9276

APPLICATIONS

Medical imaging/ultrasound

Automotive radar

PRODUCT HIGHLIGHTS

1. Small Footprint.

Eight channels are contained in a small, space-saving

package. Full TGC path, ADC, and I/Q demodulator

contained within a 100-lead, 16 mm × 16 mm TQFP.

2. Low Power.

In TGC mode, low power of 195 mW per channel

at 40 MSPS. In CW mode, ultralow power of 94 mW

per channel.

3. Integrated High Dynamic Range I/Q Demodulator with

Phase Rotation.

4. Ease of Use.

A data clock output (DCO±) operates up to 480 MHz

and supports double data rate (DDR) operation.

5. User Flexibility.

Serial port interface (SPI) control offers a wide range of

flexible features to meet specific system requirements.

6. Integrated Second-Order Antialiasing Filter.

This filter is placed before the ADC and is programmable

from 8 MHz to 18 MHz.

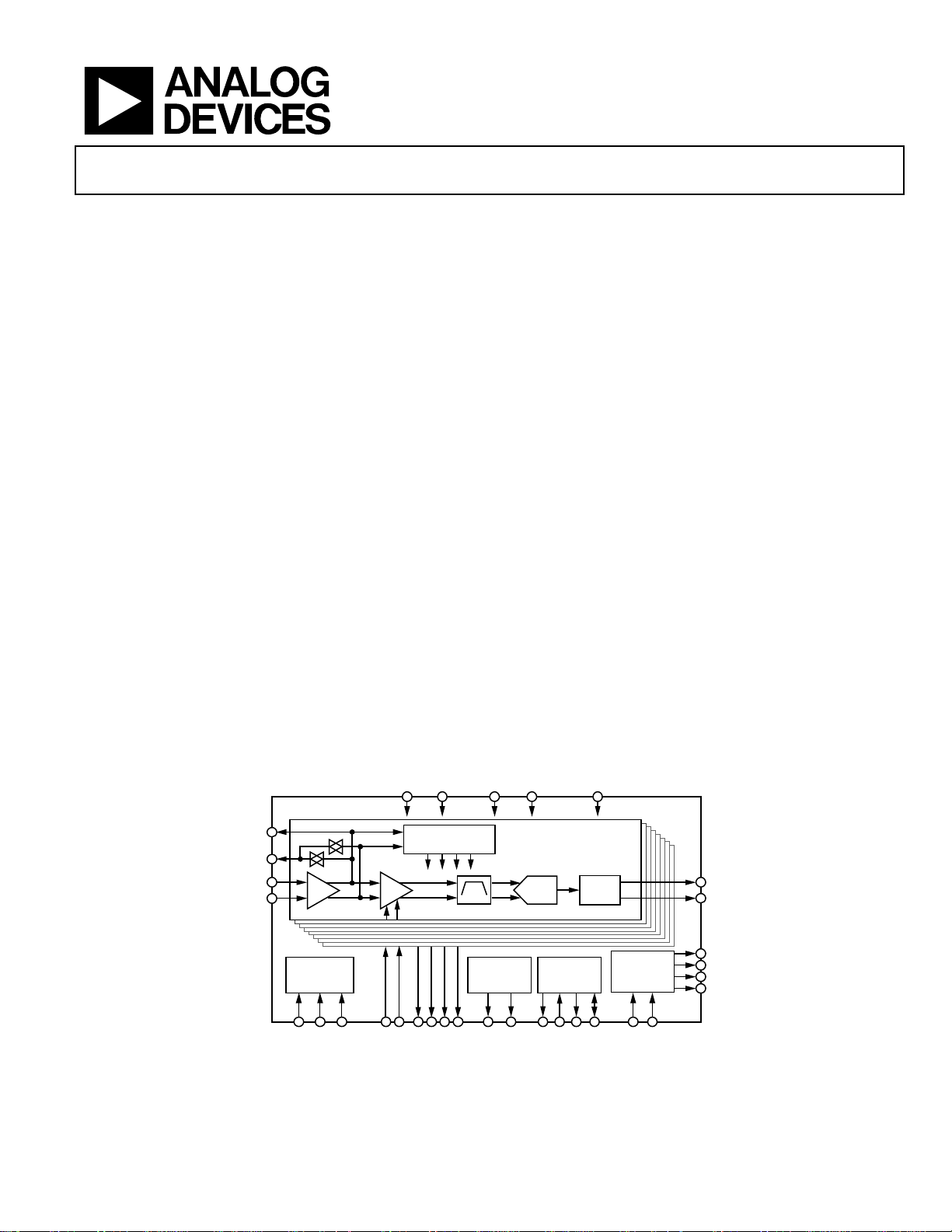

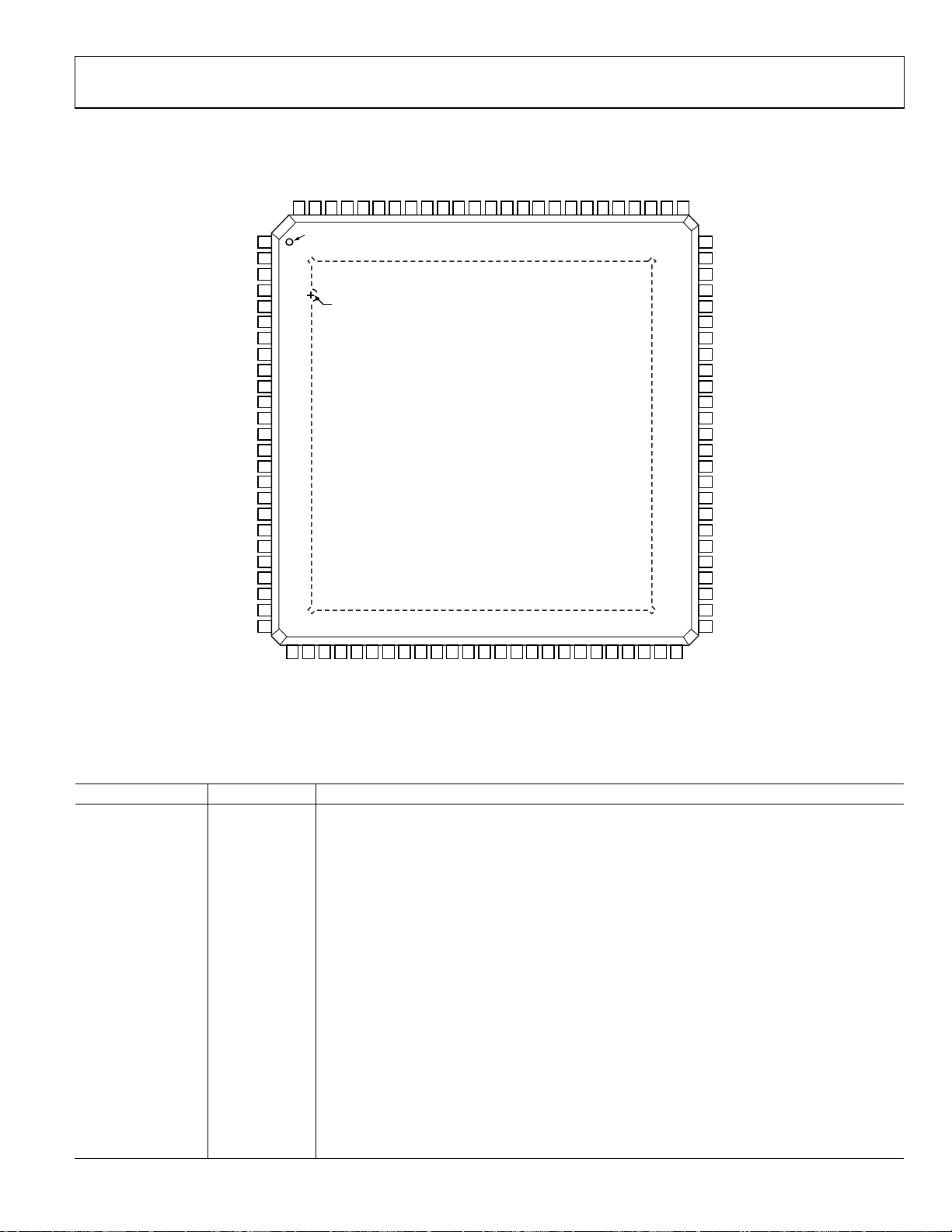

FUNCTIONAL BLOCK DIAGRAM

VDD2

VDD1

LO-A TO LO-H

LOSW-A TO LOSW-H

LI-A TO LI-H

LG-A TO LG-H

LO

GENERATIO N

4LO+

RESET

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

VGALNA

4LO–

GAIN+

I/Q

DEMODULATO R

CWI–

CWI+

CWQ–

GAIN–

AAF

REFERENCE

VREF

CWQ+

Figure 1.

STBYPDWN

12-BIT

ADC

RBIAS

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

DRVDD

8 CHANNELS

SERIAL

LVDS

SERIAL

PORT

INTERFACE

CSB

SCLK

GPO[0:3]

MULTIPLIER

SDIO

DATA

RATE

CLK+

DOUTA+ TO DO UTH+

DOUTA– TO DOUT H–

FCO+

FCO–

DCO+

DCO–

CLK–

08180-001

AD9276

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Product Highlights ........................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

General Description ......................................................................... 3

Specifications ..................................................................................... 4

AC Specifications .......................................................................... 4

Digital Specifications ................................................................... 7

Switching Specifications .............................................................. 8

ADC Timing Diagrams ............................................................... 9

Absolute Maximum Ratings .......................................................... 10

Thermal Impedance ................................................................... 10

ESD Caution ................................................................................ 10

Pin Configuration and Function Descriptions ........................... 11

Typical Performance Characteristics ........................................... 14

TGC Mode ................................................................................... 14

CW Doppler Mode ..................................................................... 17

Equivalent Circuits ......................................................................... 19

Theory of Operation ...................................................................... 21

Ultrasound .................................................................................. 21

Channel Overview ..................................................................... 22

Input Overdrive .......................................................................... 25

CW Doppler Operation ............................................................. 25

TGC Operation ........................................................................... 29

ADC ............................................................................................. 33

Clock Input Considerations ...................................................... 33

Digital Outputs and Timing ..................................................... 35

Serial Port Interface (SPI) .............................................................. 39

Hardware Interface ..................................................................... 40

Memory Map .................................................................................. 41

Reading the Memory Map Table .............................................. 41

Reserved Locations .................................................................... 41

Default Values ............................................................................. 41

Logic Levels ................................................................................. 41

Applications Information .............................................................. 45

Power and Ground Recommendations ................................... 45

Exposed Paddle Thermal Heat Slug Recommendations ...... 45

Outline Dimensions ....................................................................... 46

Ordering Guide .......................................................................... 46

REVISION HISTORY

7/09—Revision 0: Initial Version

Rev. 0 | Page 2 of 48

AD9276

GENERAL DESCRIPTION

The AD9276 is designed for low cost, low power, small size,

and ease of use. It contains eight channels of a variable gain

amplifier (VGA) with a low noise preamplifier (LNA); an antialiasing filter (AAF); a 12-bit, 10 MSPS to 80 MSPS analog-todigital converter (ADC); and an I/Q demodulator with

programmable phase rotation.

Each channel features a variable gain range of 42 dB, a fully

differential signal path, an active input preamplifier termination,

a maximum gain of up to 52 dB, and an ADC with a conversion

rate of up to 80 MSPS. The channel is optimized for dynamic

performance and low power in applications where a small

package size is critical.

The LNA has a single-ended-to-differential gain that is selectable

through the SPI. The LNA input noise is typically 0.75 nV/√Hz

at a gain of 21.3 dB, and the combined input-referred noise of

the entire channel is 0.85 nV/√Hz at maximum gain. Assuming

a 15 MHz noise bandwidth (NBW) and a 21.3 dB LNA gain, the

input SNR is roughly 92 dB. In CW Doppler mode, each LNA

output drives an I/Q demodulator. Each demodulator has independently programmable phase rotation through the SPI with

16 phase settings.

The AD9276 requires a LVPECL-/CMOS-/LVDS-compatible

sample rate clock for full performance operation. No external

reference or driver components are required for many applications.

The ADC automatically multiplies the sample rate clock for

the appropriate LVDS serial data rate. A data clock (DCO±) for

capturing data on the output and a frame clock (FCO±) trigger

for signaling a new output byte are provided.

Powering down individual channels is supported to increase

battery life for portable applications. A standby mode option

allows quick power-up for power cycling. In CW Doppler operation, the VGA, AAF, and ADC are powered down. The power of

the TGC path scales with selectable ADC speed power modes.

The ADC contains several features designed to maximize flexibility

and minimize system cost, such as a programmable clock, data

alignment, and programmable digital test pattern generation. The

digital test patterns include built-in fixed patterns, built-in pseudorandom patterns, and custom user-defined test patterns entered

via the serial port interface.

Fabricated in an advanced CMOS process, the AD9276 is

available in a 16 mm × 16 mm, RoHS compliant, 100-lead

TQFP. It is specified over the industrial temperature range

of −40°C to +85°C.

Rev. 0 | Page 3 of 48

AD9276

SPECIFICATIONS

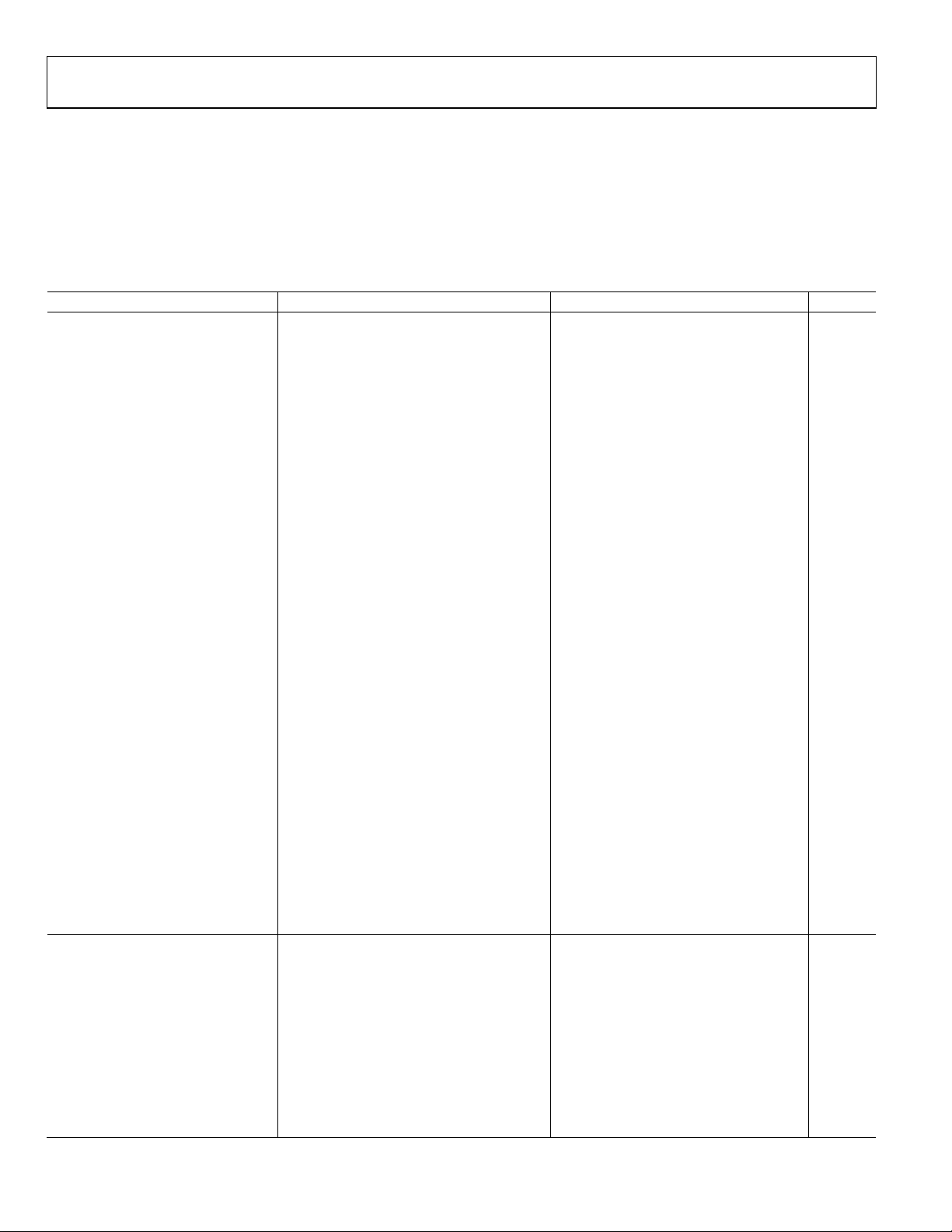

AC SPECIFICATIONS

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference, fIN = 5 MHz, RS = 50 Ω, LNA gain = 21.3 dB, LNA bias = high,

PGA gain = 27 dB, GAIN− = 0.8 V, AAF LPF cutoff = f

Mode I = f

= 40 MSPS, Mode II = f

SAMPLE

= 65 MSPS, Mode III = f

SAMPLE

otherwise noted.

/3 (Mode I/Mode II), f

SAMPLE

SAMPLE

/4.5 (Mode III), HPF cutoff = LPF cutoff/20.7 (default),

SAMPLE

= 80 MSPS, full temperature, ANSI-644 LVDS mode, unless

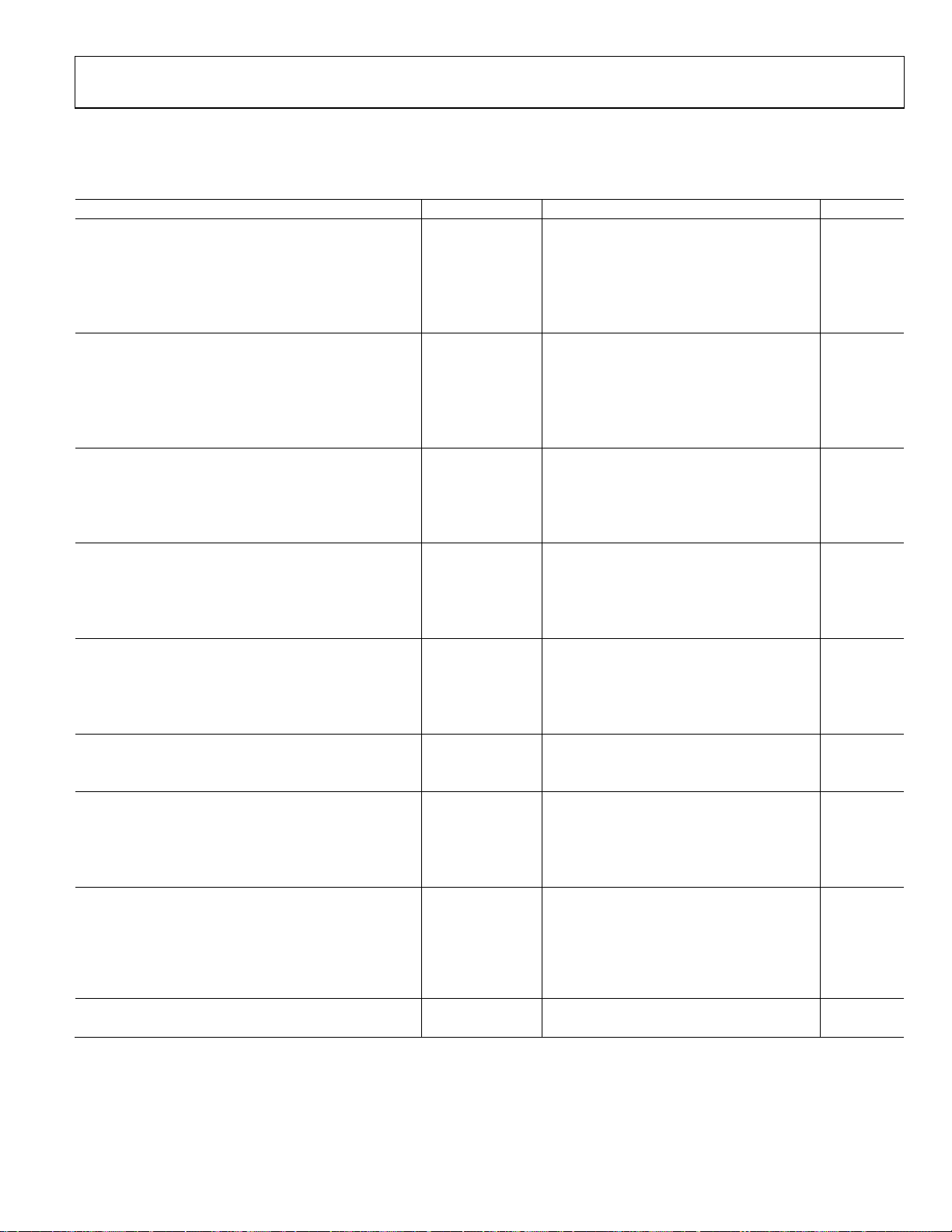

Table 1.

1

Parameter

Test Conditions/Comments Min Typ Max Unit

LNA CHARACTERISTICS

Gain Single-ended input to differential output 15.6/17.9/21.3 dB

Single-ended input to single-ended output 9.6/11.9/15.3 dB

Input Voltage Range

(Single-Ended)

LNA output limited to 4.4 V p-p differential

output

LNA gain = 15.6 dB 733 mV p-p

LNA gain = 17.9 dB 550 mV p-p

LNA gain = 21.3 dB 367 mV p-p

Input Common Mode (LI-x, LG-x) 1.0 V

Output Common Mode (LO-x) 1.5 V

Output Common Mode (LOSW-x) Switch off High-Z Ω

Switch on 1.5 V

Input Resistance (LI-x) RFB = 250 Ω 50 Ω

R

R

= 500 Ω 100 Ω

FB

= ∞ 15 kΩ

FB

Input Capacitance (LI-x) 22 pF

−3 dB Bandwidth 100 MHz

Input Noise Voltage RS = 0 Ω, RFB = ∞

LNA gain = 15.6 dB 0.98 nV/√Hz

LNA gain = 17.9 dB 0.86 nV/√Hz

LNA gain = 21.3 dB 0.75 nV/√Hz

Input Noise Current RFB = ∞ 1 pA/√Hz

1 dB Input Compression Point GAIN+ = 0 V

LNA gain = 15.6 dB 1.0 V p-p

LNA gain = 17.9 dB 0.8 V p-p

LNA gain = 21.3 dB 0.5 V p-p

Noise Figure RS = 50 Ω

Active Termination Matched LNA gain = 15.6 dB, RFB = 200 Ω 4.8 dB

LNA gain = 17.9 dB, RFB = 250 Ω 4.1 dB

LNA gain = 21.3 dB, RFB = 350 Ω 3.2 dB

Unterminated LNA gain = 15.6 dB, RFB = ∞ 3.4 dB

LNA gain = 17.9 dB, RFB = ∞ 2.8 dB

LNA gain = 21.3 dB, RFB = ∞ 2.3 dB

FULL-CHANNEL (TGC)

CHARACTERISTICS

AAF Low-Pass Cutoff

In Range −3 dB, programmable 8 18 MHz

In Range AAF Bandwidth

±10 %

Tol er an ce

Group Delay Variation f = 1 MHz to 18 MHz, GAIN+ = 0 V to 1.6 V ±0.5 ns

Input-Referred Noise Voltage GAIN+ = 1.6 V, RFB = ∞

LNA gain = 15.6 dB 1.26 nV/√Hz

LNA gain = 17.9 dB 1.04 nV/√Hz

LNA gain = 21.3 dB 0.85 nV/√Hz

Rev. 0 | Page 4 of 48

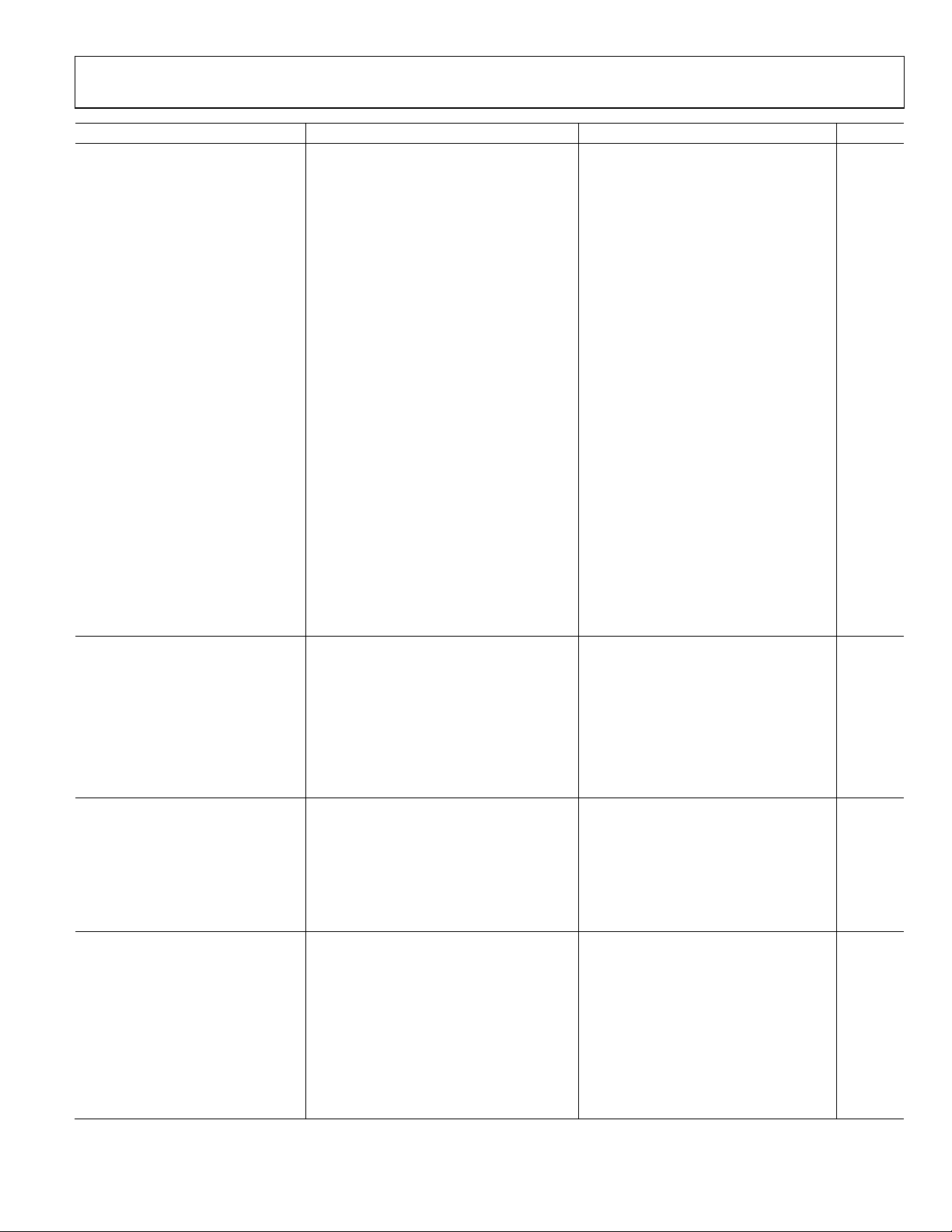

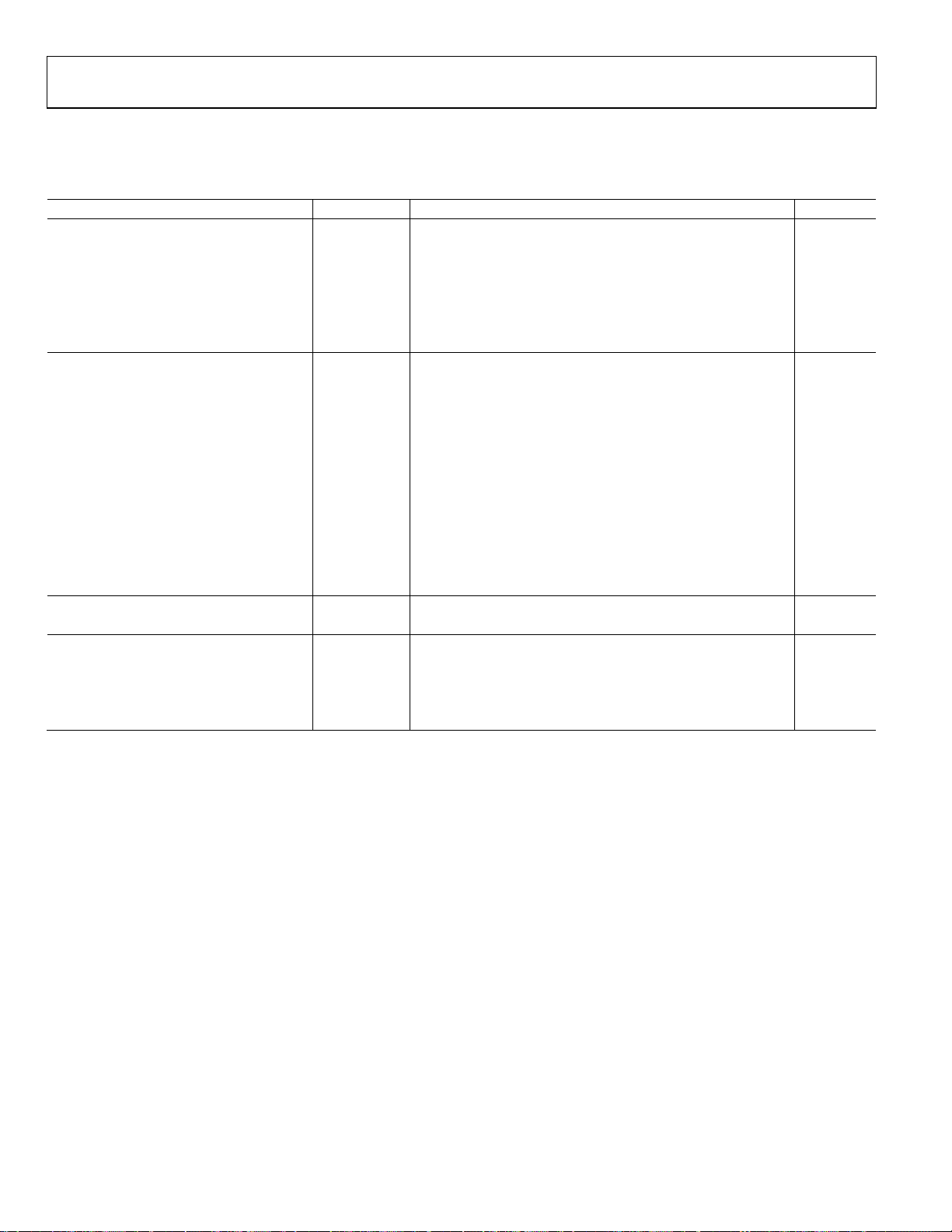

AD9276

Parameter

1

Test Conditions/Comments Min Typ Max Unit

Noise Figure GAIN+ = 1.6 V, RS = 50 Ω

Active Termination Matched

LNA gain = 15.6 dB, R

= 200 Ω 8.0/7.7/7.6 dB

FB

Mode I/Mode II/Mode III

LNA gain = 17.9 dB, RFB = 250 Ω 6.6/6.2/6.1 dB

LNA gain = 21.3 dB, RFB = 350 Ω 4.7/4.5/4.4 dB

Unterminated LNA gain = 15.6 dB, RFB = ∞ 4.7 dB

LNA gain = 17.9 dB, RFB = ∞ 3.7 dB

LNA gain = 21.3 dB, RFB = ∞ 2.8 dB

Correlated Noise Ratio No signal, correlated/uncorrelated −30 dB

Output Offset −35 +35 LSB

f

Signal-to-Noise Ratio (SNR)

= 5 MHz at −10 dBFS, GAIN+ = 0 V 65/64/63 dBFS

IN

Mode I/Mode II/Mode III

f

Harmonic Distortion

= 5 MHz at −1 dBFS, GAIN+ = 1.6 V 57/56/54.5 dBFS

IN

Mode I/Mode II/Mode III

Second Harmonic fIN = 5 MHz at −10 dBFS, GAIN+ = 0 V −62/−58/−55 dBc

f

= 5 MHz at −1 dBFS, GAIN+ = 1.6 V −60/−61/−58 dBc

IN

Third Harmonic fIN = 5 MHz at −10 dBFS, GAIN+ = 0 V −71/−60/−60 dBc

f

Two-Tone Intermodulation (IMD3)

= 5 MHz at −1 dBFS, GAIN+ = 1.6 V −57/−55/−56 dBc

IN

= 5.015 MHz, f

f

RF1

A

RF1

= 0 dB, A

= −20 dB, GAIN+ = 1.6 V,

RF2

IMD3 relative to A

= 5.020 MHz,

RF2

RF2

−55 dBc

Channel-to-Channel Crosstalk fIN = 5 MHz at −1 dBFS −70 dB

Overrange condition

Channel-to-Channel Delay

Full TGC p ath, f

2

−65 dB

= 5 MHz, GAIN+ = 0 V to 1.6 V 0.3 Degrees

IN

Variation

PGA Gain Differential input to differential output 21/24/27/30 dB

GAIN ACCURACY 25°C

Gain Law Conformance Error

0 < GAIN+ < 0.16 V 1.5 dB

Mode I/Mode II/Mode III

0.16 V < GAIN+ < 1.44 V

1.44 V < GAIN+ < 1.6 V

−1.5/−1.5/

−1.6

−1.5/−1.5/

−1.6

−2.5

+1.5/+1.5/

+1.6

+1.5/+1.5/

+1.6

dB

dB

Linear Gain Error GAIN+ = 0.8 V, normalized for ideal AAF loss −1.5 +1.5 dB

Channel-to-Channel Matching 0.16 V < GAIN+ < 1.44 V 0.1 dB

GAIN CONTROL INTERFACE

Normal Operating Range 0 1.6 V

Gain Range GAIN+ = 0 V to 1.6 V −42 0 dB

Scale Factor 28.5 dB/V

Response Time 42 dB change 750 ns

GAIN+ Impedance Single-ended 10 MΩ

GAIN− Impedance Single-ended 70 kΩ

CW DOPPLER MODE

LO Frequency fLO = f

/4 1 10 MHz

4LO

Phase Increment Per channel 22.5 Degrees

Output DC Bias (Single-Ended) CWI+, CWI−, CWQ+, CWQ− 1.5 V

Maximum Output Swing

Per CWI+, CWI−, CWQ+, CWQ−, per channel

±1.25 mA

enabled

Transconductance (Differential) Demodulated I

, each I or Q output

OUT/VIN

LNA gain = 15.6 dB 1.8 mA/V

LNA gain = 17.9 dB 2.4 mA/V

LNA gain = 21.3 dB 3.5 mA/V

Rev. 0 | Page 5 of 48

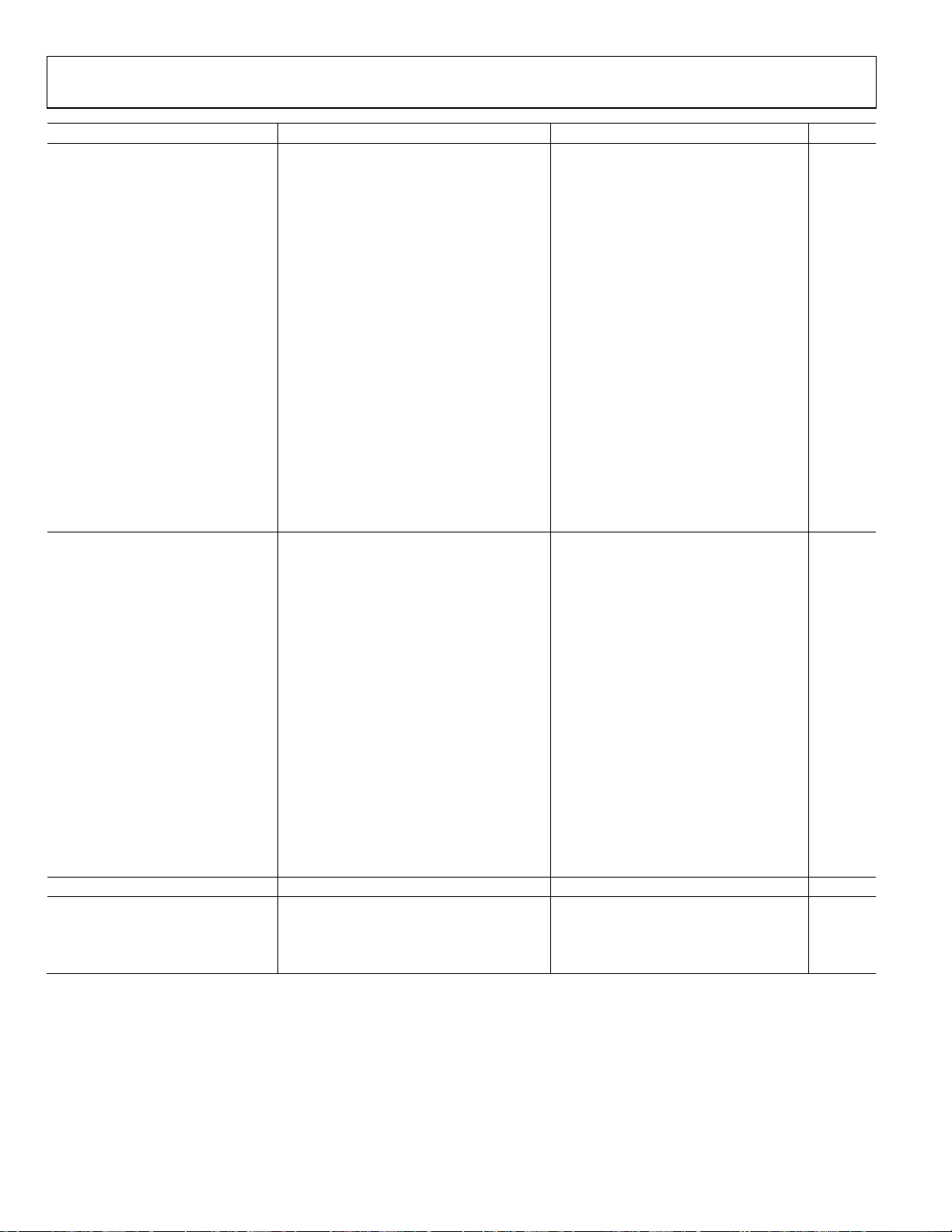

AD9276

Parameter

1

Test Conditions/Comments Min Typ Max Unit

Input-Referred Noise Voltage RS = 0 Ω, RFB = ∞

LNA gain = 15.6 dB 1.5 nV/√Hz

LNA gain = 17.9 dB 1.4 nV/√Hz

LNA gain = 21.3 dB 1.3 nV/√Hz

Noise Figure RS = 50 Ω, RFB = ∞

LNA gain = 15.6 dB 5.7 dB

LNA gain = 17.9 dB 5.3 dB

LNA gain = 21.3 dB 4.8 dB

Input-Referred Dynamic Range RS = 0 Ω, RFB = ∞

LNA gain = 15.6 dB 164 dBFS/√Hz

LNA gain = 17.9 dB 162 dBFS/√Hz

LNA gain = 21.3 dB 160 dBFS/√Hz

Output-Referred SNR

−3 dBFS input, f

= 2.5 MHz, f

RF

= 10 MHz,

4LO

155 dBc/√Hz

1 kHz offset

Two-Tone Intermodulation (IMD3)

= 5.015 MHz, f

f

RF1

f

= 20 MHz, A

4LO

RF1

IMD3 relative to A

= 5.020 MHz,

RF2

= 0 dB, A

RF2

RF2

= −20 dB,

−58 dB

Quadrature Phase Error I to Q, all phases, 1 σ 0.15 Degrees

I/Q Amplitude Imbalance I to Q, all phases, 1 σ 0.015 dB

Channel-to-Channel Matching Phase I to I, Q to Q, 1 σ 0.5 Degrees

Amplitude I to I, Q to Q, 1 σ 0.25 dB

POWER SUPPLY

Mode I/Mode II/Mode III

AVDD1 1.7 1.8 1.9 V

AVDD2 2.7 3.0 3.6 V

DRVDD 1.7 1.8 1.9 V

I

TGC mode 190/263/317 mA

AVDD1

CW Doppler mode 15 mA

I

TGC mode, no signal 365 mA

AVDD2

CW Doppler mode per channel enabled,

30 mA

no signal

I

49/51/52 mA

DRVDD

Total Power Dissipation

(Including Output Drivers)

TGC mode, no signal

CW Doppler mode with eight channels

1560/1690/

1780

1800/1940/

2050

750 mW

mW

enabled, no signal

Power-Down Dissipation 5 mW

Standby Power Dissipation 175/200/210 mW

Power Supply Rejection Ratio

1.6 mV/V

(PSRR)

ADC RESOLUTION 12 Bits

ADC REFERENCE

Output Voltage Error VREF = 1 V ±20 mV

Load Regulation at 1.0 mA VREF = 1 V 2 mV

Input Resistance 6 kΩ

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and information about how these tests were

completed.

2

The overrange condition is specified as being 6 dB more than the full-scale input range.

Rev. 0 | Page 6 of 48

AD9276

DIGITAL SPECIFICATIONS

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference, fIN = 5 MHz, full temperature, unless otherwise noted.

Table 2.

1

Parameter

Temperature Min Typ Max Unit

CLOCK INPUTS (CLK+, CLK−)

Logic Compliance CMOS/LVDS/LVPECL

Differential Input Voltage

2

Full 250 mV p-p

Input Common-Mode Voltage Full 1.2 V

Input Resistance (Differential) 25°C 20 kΩ

Input Capacitance 25°C 1.5 pF

CW 4LO INPUTS (4LO+, 4LO−)

Logic Compliance CMOS/LVDS/LVPECL

2

Differential Input Voltage

Full 250 mV p-p

Input Common-Mode Voltage Full 1.2 V

Input Resistance (Differential) 25°C 20 kΩ

Input Capacitance 25°C 1.5 pF

LOGIC INPUTS (PDWN, STBY, SCLK, RESET)

Logic 1 Voltage Full 1.2 3.6 V

Logic 0 Voltage Full 0.3 V

Input Resistance 25°C 30 kΩ

Input Capacitance 25°C 0.5 pF

LOGIC INPUT (CSB)

Logic 1 Voltage Full 1.2 3.6 V

Logic 0 Voltage Full 0.3 V

Input Resistance 25°C 70 kΩ

Input Capacitance 25°C 0.5 pF

LOGIC INPUT (SDIO)

Logic 1 Voltage Full 1.2 DRVDD + 0.3 V

Logic 0 Voltage Full 0 0.3 V

Input Resistance 25°C 30 kΩ

Input Capacitance 25°C 2 pF

LOGIC OUTPUT (SDIO)

3

Logic 1 Voltage (IOH = 800 A) Full 1.79 V

Logic 0 Voltage (IOL = 50 A) Full 0.05 V

DIGITAL OUTPUTS (DOUTx+, DOUTx−), (ANSI-644)

1

Logic Compliance LVDS

Differential Output Voltage (VOD) Full 247 454 mV

Output Offset Voltage (VOS) Full 1.125 1.375 V

Output Coding (Default) Offset binary

DIGITAL OUTPUTS (DOUTx+, DOUTx−),

(LOW POWER, REDUCED SIGNAL OPTION)

1

Logic Compliance LVDS

Differential Output Voltage (VOD) Full 150 250 mV

Output Offset Voltage (VOS) Full 1.10 1.30 V

Output Coding (Default) Offset binary

LOGIC OUTPUTS (GPO0, GPO1, GPO2, GPO3)

Logic 0 Voltage (IOL = 50 A) Full 0.05 V

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and information about how these tests were

completed.

2

Specified for LVDS and LVPECL only.

3

Specified for 13 SDIO pins sharing the same connection.

Rev. 0 | Page 7 of 48

AD9276

SWITCHING SPECIFICATIONS

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference, fIN = 5 MHz, full temperature, unless otherwise noted.

Table 3.

1

Parameter

CLOCK

2

Temperature Min Typ Max Unit

Clock Rate

40 MSPS (Mode I) Full 10 40 MHz

65 MSPS (Mode II) Full 10 65 MHz

80 MSPS (Mode III) Full 10 80 MHz

Clock Pulse Width High (tEH) Full 6.25 ns

Clock Pulse Width Low (tEL) Full 6.25 ns

OUTPUT PARAMETERS

Propagation Delay (tPD) Full (t

2, 3

/2) + 1.5 (t

SAMPLE

/2) + 2.3 (t

SAMPLE

/2) + 3.1 ns

SAMPLE

Rise Time (tR) (20% to 80%) Full 300 ps

Fall Time (tF) (20% to 80%) Full 300 ps

FCO Propagation Delay (t

DCO Propagation Delay (t

DCO to Data Delay (t

DCO to FCO Delay (t

Data-to-Data Skew (t

) Full (t

FCO

4

)

Full t

CPD

4

)

Full (t

DATA

4

)

Full (t

FRAME

DATA-MAX

− t

) Full ±100 ±350 ps

DATA-MIN

/2) + 1.5 (t

SAMPLE

/24) − 300 (t

SAMPLE

/24) − 300 (t

SAMPLE

/2) + 2.3 (t

SAMPLE

+ (t

FCO

SAMPLE

/24) (t

SAMPLE

/24) (t

SAMPLE

/2) + 3.1 ns

SAMPLE

/24) ns

/24) + 300 ps

SAMPLE

/24) + 300 ps

SAMPLE

Wake-Up Time (Standby), GAIN+ = 0.5 V 25°C 2 µs

Wake-Up Time (Power-Down) 25°C 1 ms

Pipeline Latency Full 8

Clock

cycles

APERTURE

Aperture Uncertainty (Jitter) 25°C <1 ps rms

LO GENERATION

4LO Frequency Full 4 40 MHz

LO Divider RESET Setup Time

LO Divider RESET Hold Time

5

5

Full 5 ns

Full 5 ns

LO Divider RESET High Pulse Width Full 20 ns

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and information about how these tests were

completed.

2

Can be adjusted via the SPI.

3

Measurements were made using a part soldered to FR-4 material.

4

t

/24 is based on the number of bits divided by 2 because the delays are based on half duty cycles.

SAMPLE

5

RESET edge to rising 4LO edge.

Rev. 0 | Page 8 of 48

AD9276

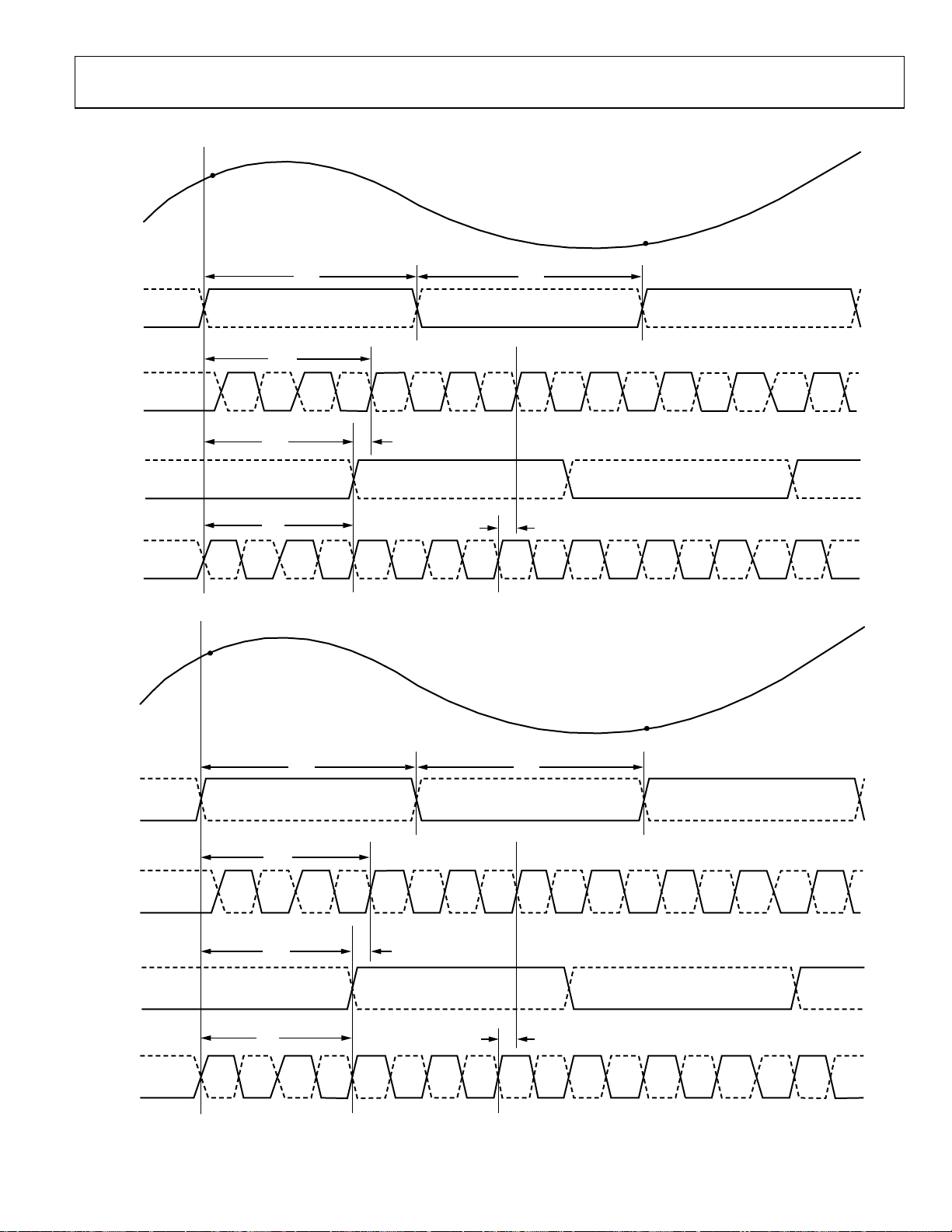

ADC TIMING DIAGRAMS

N – 1

AIN

N

CLK–

CLK+

DCO–

DCO+

FCO–

FCO+

DOUTx–

DOUTx+

AIN

N – 1

t

EH

t

CPD

t

FCO

t

PD

t

FRAME

MSB

D10

N – 8

N – 8D9N – 8D8N – 8D7N – 8D6N – 8D5N – 8D4N – 8D3N – 8D2N – 8D1N – 8D0N – 8

t

EL

t

DATA

D10

MSB

N – 7

N – 7

08180-002

Figure 2. 12-Bit Data Serial Stream (Default)

N

CLK–

CLK+

DCO–

DCO+

FCO–

FCO+

DOUTx–

DOUTx+

t

EH

t

CPD

t

FCO

t

PD

t

FRAME

LSB

N – 8D0N – 8D1N – 8D2N – 8D3N – 8D4N – 8D5N – 8D6N – 8D7N – 8D8N – 8D9N – 8

t

EL

t

DATA

D10

N – 8

LSB

N – 7

D0

N – 7

08180-003

Figure 3. 12-Bit Data Serial Stream, LSB First

Rev. 0 | Page 9 of 48

AD9276

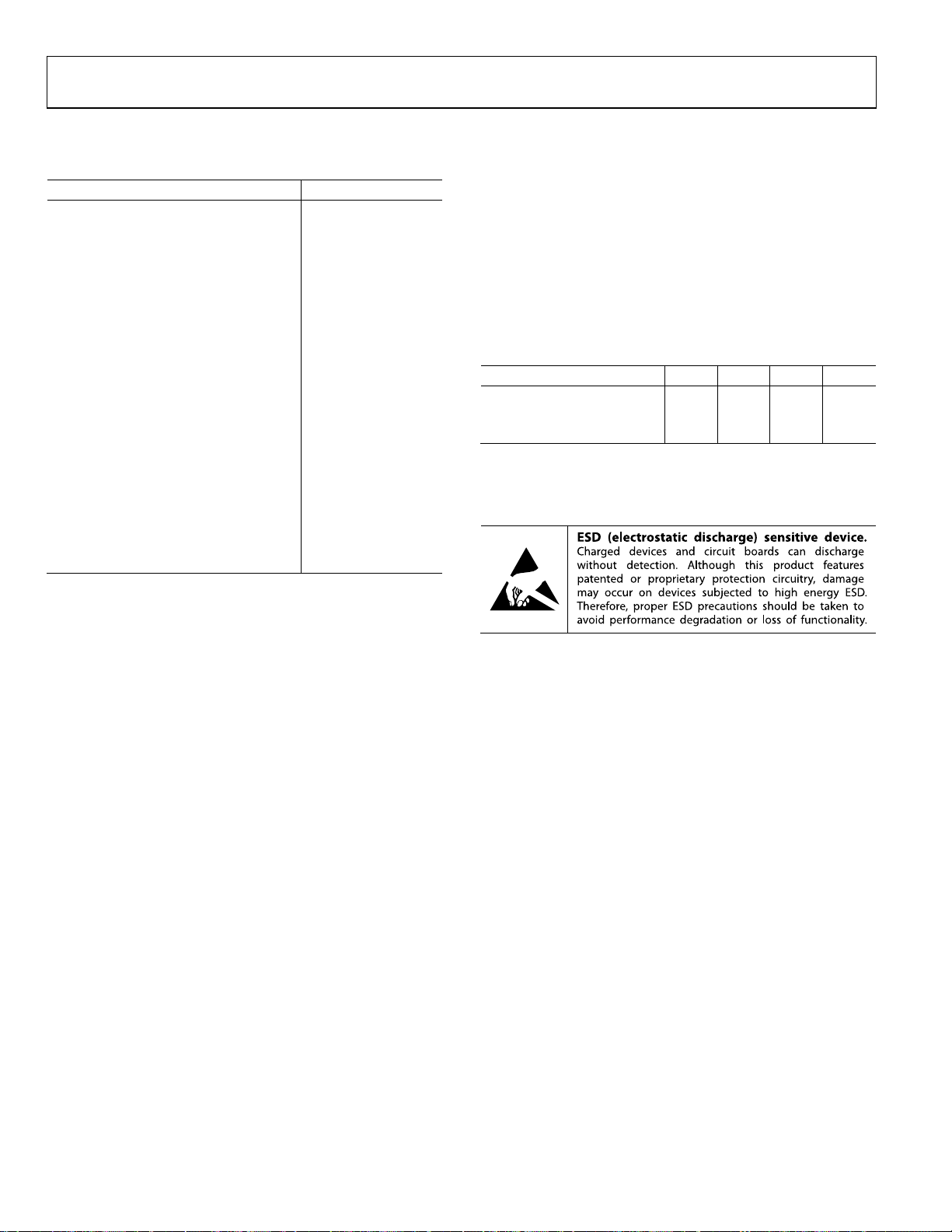

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

AVDD1 to GND −0.3 V to +2.0 V

AVDD2 to GND −0.3 V to +3.9 V

DRVDD to GND −0.3 V to +2.0 V

GND to GND −0.3 V to +0.3 V

AVDD2 to AVDD1 −2.0 V to +3.9 V

AVDD1 to DRVDD −2.0 V to +2.0 V

AVDD2 to DRVDD −2.0 V to +3.9 V

Digital Outputs (DOUTx+, DOUTx−,

DCO+, DCO−, FCO+, FCO−) to GND

CLK+, CLK−, SDIO to GND −0.3 V to +2.0 V

LI-x, LO-x, LOSW-x to GND −0.3 V to +3.9 V

CWI−, CWI+, CWQ−, CWQ+ to GND −0.3 V to +3.9 V

PDWN, STBY, SCLK, CSB to GND −0.3 V to +2.0 V

GAIN+, GAIN−, RESET, 4LO+, 4LO−,

GPO0, GPO1, GPO2, GPO3 to GND

RBIAS, VREF to GND −0.3 V to +2.0 V

Operating Temperature Range (Ambient) −40°C to +85°C

Storage Temperature Range (Ambient) −65°C to +150°C

Maximum Junction Temperature 150°C

Lead Temperature (Soldering, 10 sec) 300°C

−0.3 V to +2.0 V

−0.3 V to +3.9 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL IMPEDANCE

Table 5.

Airflow Velocity (m/s) θ

0.0 20.3 °C/W

1.0 14.4 7.6 4.7 °C/W

2.5 12.9 °C/W

1

θ

for a 4-layer PCB with solid ground plane (simulated). Exposed pad

JA

soldered to PCB.

1

θJB θJC Unit

JA

ESD CAUTION

Rev. 0 | Page 10 of 48

AD9276

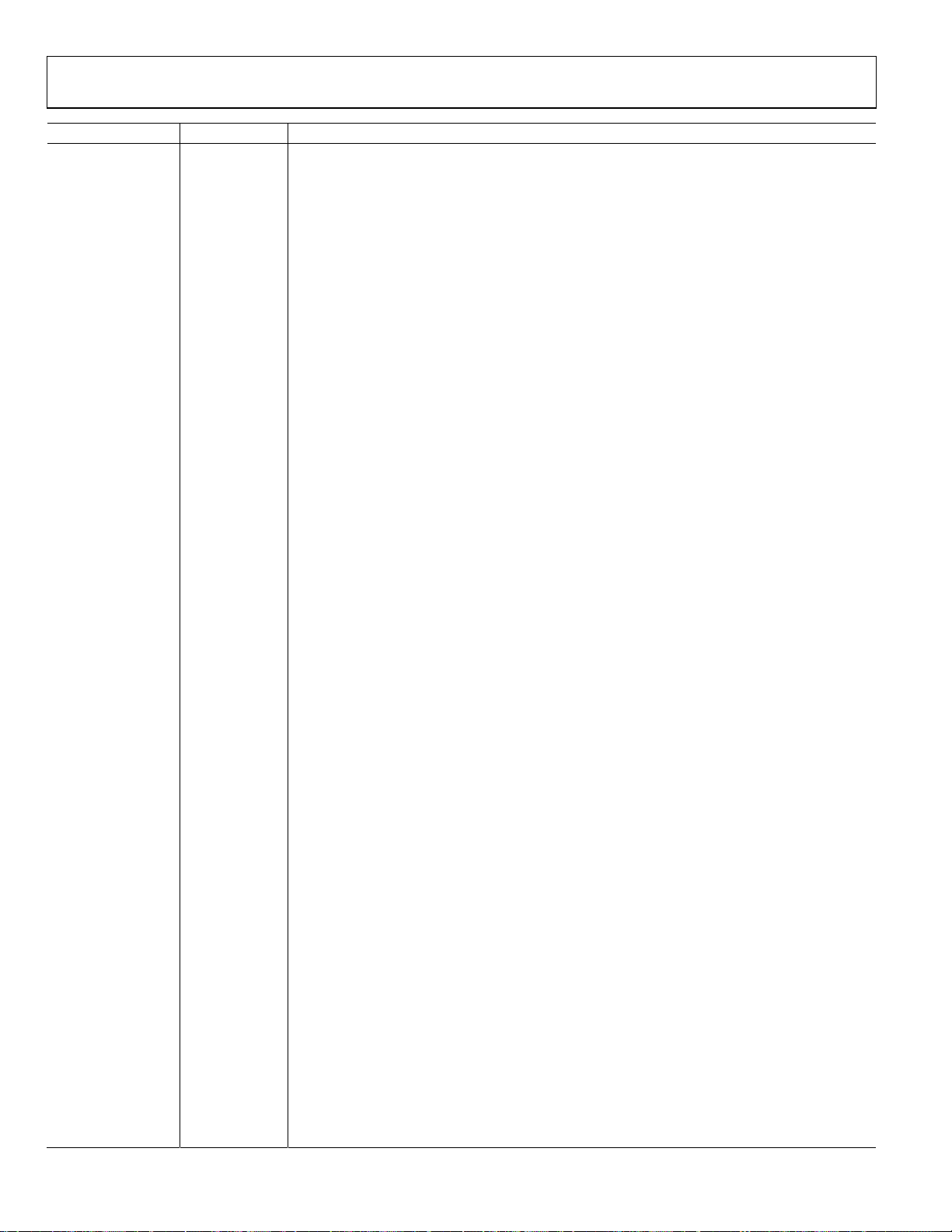

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

LOSW-DLO-D

GPO0

GPO1

GPO2

GPO3

RESET

4LO–

4LO+

AVDD2

AVDD2

GAIN–

GAIN+

VREF

RBIAS

AVDD2

AD9276

TOP VIEW

(Not to Scale)

76

LI-D

75

LG-D

74

AVDD2

73

AVDD1

72

LO-C

71

LOSW-C

70

LI-C

69

LG-C

68

AVDD2

67

AVDD1

66

LO-B

65

64

LOSW-B

63

LI-B

LG-B

62

AVDD2

61

AVDD1

60

59

LO-A

58

LOSW-A

57

LI-A

LG-A

56

AVDD2

55

54

AVDD1

53

CSB

52

SDIO

51

SCLK

LI-E

LG-E

AVDD2

AVDD1

LO-F

LOSW-F

LI-F

LG-F

AVDD2

AVDD1

LO-G

LOSW-G

LI-G

LG-G

AVDD2

AVDD1

LO-H

LOSW-H

LI-H

LG-H

AVDD2

AVDD1

CLK–

CLK+

AVDD1

CWI+

CWQ–

CWQ+

GND

GND

GND

LO-E

LOSW-E

9998979695949392919089888786858483828180797877

100

PIN 1

1

INDICATOR

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

EXPOSED PADDLE, PIN 0

(BOTTOM OF PACKAGE)

CWI–

2627282930313233343536373839404142434445464748

FCO–

DRVDD

DOUTH–

DOUTH+

DOUTG –

NOTES

1. THE EXPOSED PAD SHOULD BE TIED TO A QUIET ANALOG GROUND.

DOUTF+

DOUTG+

DOUTF–

DCO–

DOUTE–

DOUTE+

FCO+

DCO+

DOUTD–

DOUTD+

DOUTC–

DOUTC+

DOUTA+

DOUTB+

DRVDD

DOUTA–

DOUTB–

50

49

STBY

PDWN

AVDD1

Figure 4. Pin Configuration

Table 6. Pin Function Descriptions

Pin No. Name Description

0, 96, 97, 98 GND Ground. Exposed paddle should be tied to a quiet analog ground.

1 LI-E LNA Analog Input for Channel E.

2 LG-E LNA Ground for Channel E.

3, 9, 15, 21, 55, 61,

AVDD2 3.0 V Analog Supply.

67, 73, 85, 86, 91

4, 10, 16, 22, 25, 50,

AVDD1 1.8 V Analog Supply.

54, 60, 66, 72

5 LO-F LNA Analog Inverted Output for Channel F.

6 LOSW-F LNA Analog Switched Output for Channel F.

7 LI-F LNA Analog Input for Channel F.

8 LG-F LNA Ground for Channel F.

11 LO-G LNA Analog Inverted Output for Channel G.

12 LOSW-G LNA Analog Switched Output for Channel G.

13 LI-G LNA Analog Input for Channel G.

14 LG-G LNA Ground for Channel G.

17 LO-H LNA Analog Inverted Output for Channel H.

18 LOSW-H LNA Analog Switched Output for Channel H.

19 LI-H LNA Analog Input for Channel H.

20 LG-H LNA Ground for Channel H.

Rev. 0 | Page 11 of 48

08180-004

AD9276

Pin No. Name Description

23 CLK− Clock Input Complement.

24 CLK+ Clock Input True.

26, 47 DRVDD 1.8 V Digital Output Driver Supply.

27 DOUTH− ADC H Digital Output Complement.

28 DOUTH+ ADC H Digital Output True.

29 DOUTG− ADC G Digital Output Complement.

30 DOUTG+ ADC G Digital Output True.

31 DOUTF− ADC F Digital Output Complement.

32 DOUTF+ ADC F Digital Output True.

33 DOUTE− ADC E Digital Output Complement.

34 DOUTE+ ADC E Digital Output True.

35 DCO− Digital Clock Output Complement.

36 DCO+ Digital Clock Output True.

37 FCO− Digital Frame Clock Output Complement.

38 FCO+ Digital Frame Clock Output True.

39 DOUTD− ADC D Digital Output Complement.

40 DOUTD+ ADC D Digital Output True.

41 DOUTC− ADC C Digital Output Complement.

42 DOUTC+ ADC C Digital Output True.

43 DOUTB− ADC B Digital Output Complement.

44 DOUTB+ ADC B Digital Output True.

45 DOUTA− ADC A Digital Output Complement.

46 DOUTA+ ADC A Digital Output True.

48 STBY Standby Power-Down.

49 PDWN Full Power-Down.

51 SCLK Serial Clock.

52 SDIO Serial Data Input/Output.

53 CSB Chip Select Bar.

56 LG-A LNA Ground for Channel A.

57 LI-A LNA Analog Input for Channel A.

58 LOSW-A LNA Analog Switched Output for Channel A.

59 LO-A LNA Analog Inverted Output for Channel A.

62 LG-B LNA Ground for Channel B.

63 LI-B LNA Analog Input for Channel B.

64 LOSW-B LNA Analog Switched Output for Channel B.

65 LO-B LNA Analog Inverted Output for Channel B.

68 LG-C LNA Ground for Channel C.

69 LI-C LNA Analog Input for Channel C.

70 LOSW-C LNA Analog Switched Output for Channel C.

71 LO-C LNA Analog Inverted Output for Channel C.

74 LG-D LNA Ground for Channel D.

75 LI-D LNA Analog Input for Channel D.

76 LOSW-D LNA Analog Switched Output for Channel D.

77 LO-D LNA Analog Inverted Output for Channel D.

78 GPO0 General-Purpose Open-Drain Output 0.

79 GPO1 General-Purpose Open-Drain Output 1.

80 GPO2 General-Purpose Open-Drain Output 2.

81 GPO3 General-Purpose Open-Drain Output 3.

82 RESET Reset for Synchronizing 4LO Divide-by-4 Counter.

83 4LO− CW Doppler 4LO Input Complement.

84 4LO+ CW Doppler 4LO Input True.

87 GAIN− Gain Control Voltage Input Complement.

88 GAIN+ Gain Control Voltage Input True.

Rev. 0 | Page 12 of 48

AD9276

Pin No. Name Description

89 RBIAS External Resistor to Set the Internal ADC Core Bias Current.

90 VREF Voltage Reference Input/Output.

92 CWI− CW Doppler I Output Complement.

93 CWI+ CW Doppler I Output True.

94 CWQ− CW Doppler Q Output Complement.

95 CWQ+ CW Doppler Q Output True.

99 LO-E LNA Analog Inverted Output for Channel E.

100 LOSW-E LNA Analog Switched Output for Channel E.

Rev. 0 | Page 13 of 48

AD9276

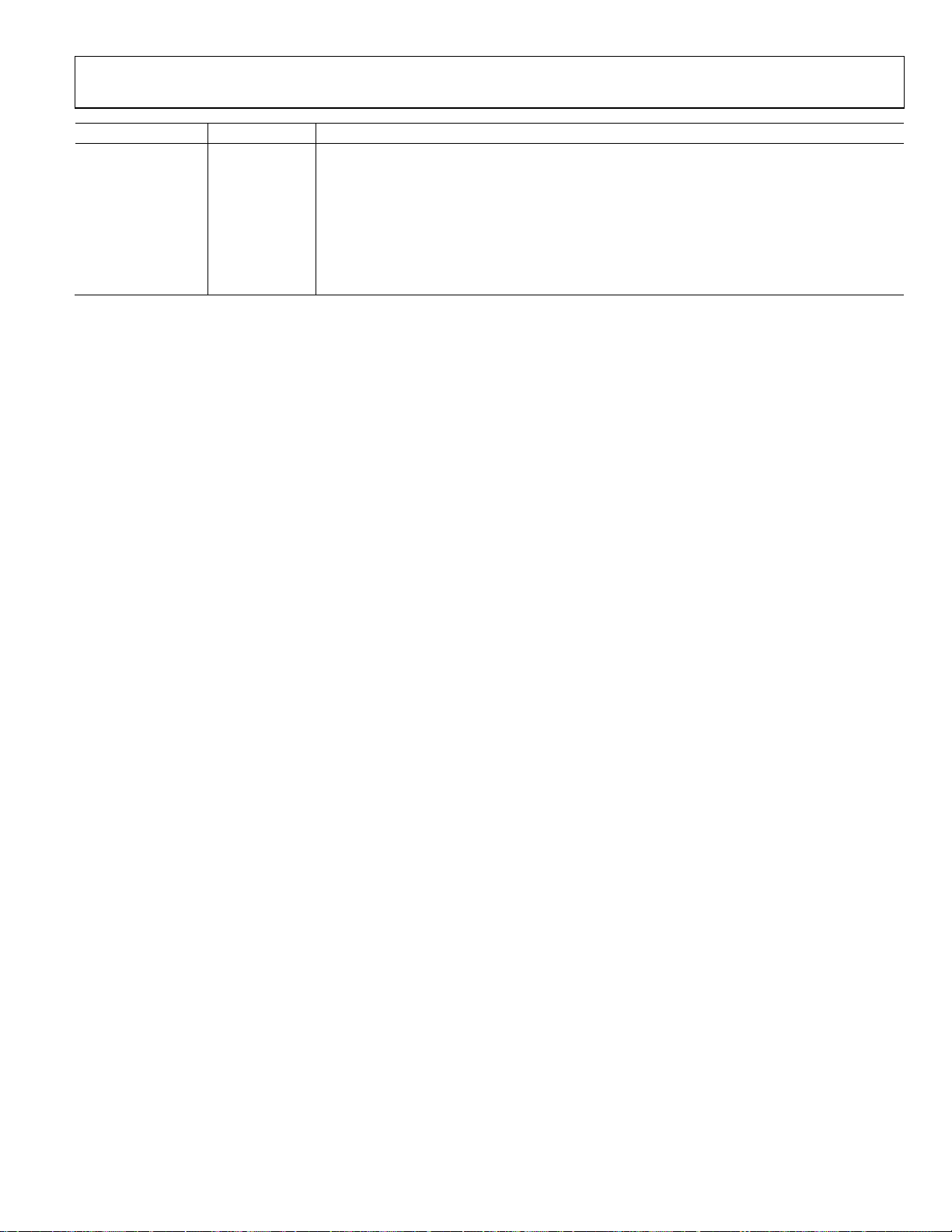

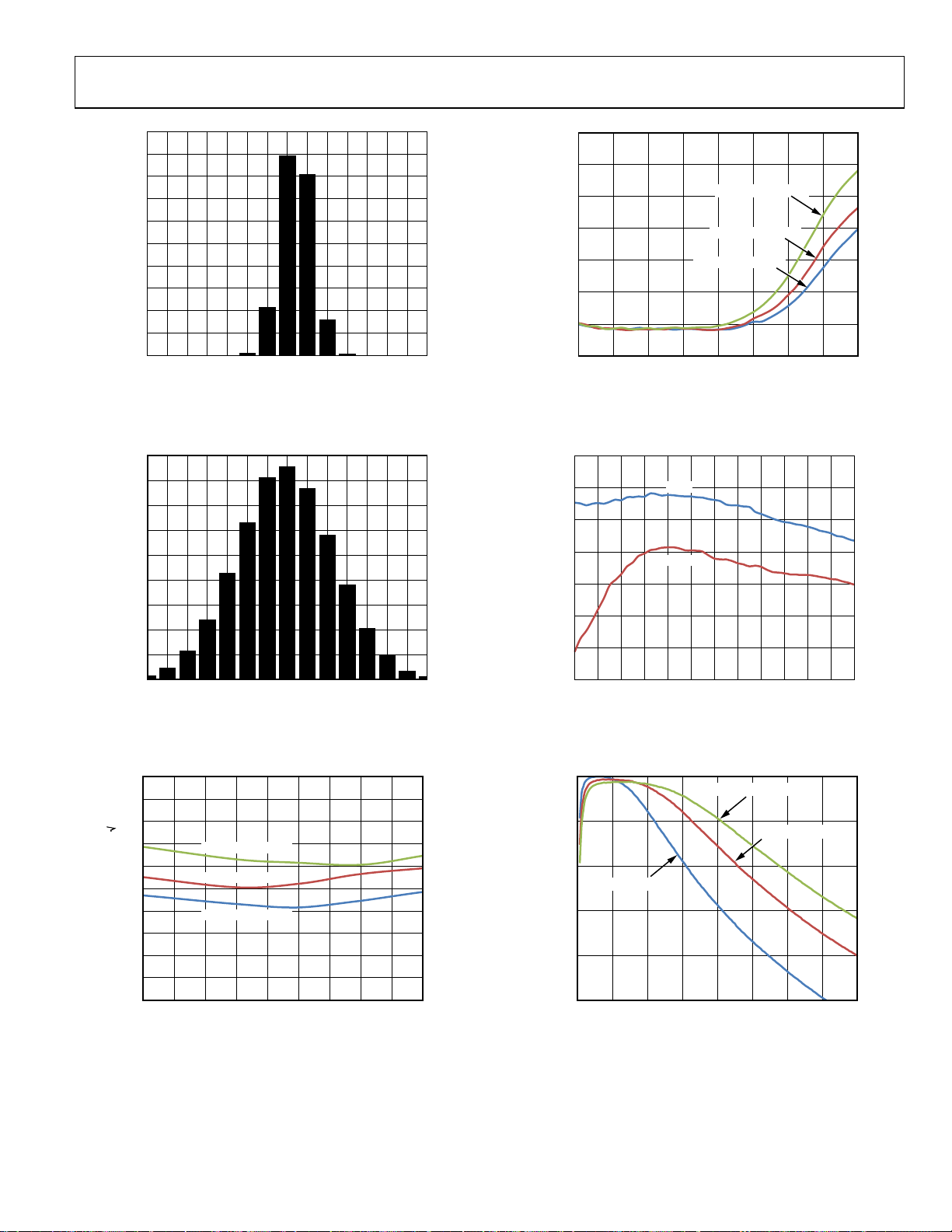

TYPICAL PERFORMANCE CHARACTERISTICS

TGC MODE

f

= 40 MSPS, fIN = 5 MHz, RS = 50 Ω, LNA gain = 21.3 dB, LNA bias = high, PGA gain = 27 dB, AAF LPF cutoff = f

SAMPLE

HPF cutoff = LPF cutoff/20.7 (default).

2.0

1.5

1.0

0.5

0

–0.5

GAIN ERROR (dB)

–1.0

–1.5

–2.0

0 0.2 0.4 0. 6 0. 8 1.0

–40°C

+25°C

+85°C

GAIN+ (V)

Figure 5. Gain Error vs. GAIN+ at Three Temperatures

1.2 1.4 1.6

08180-005

25

20

15

10

PERCENTAGE OF UNITS (%)

5

0

–1.0

–0.9

–0.8

–0.7

–0.6

–0.5

–0.4

–0.3

–0.2

GAIN ERROR (dB)

Figure 8. Gain Error Histogram, GAIN+ = 1.44 V

0

0.1

0.2

0.3

–0.1

0.4

SAMPLE

0.5

0.6

/3,

0.7

0.8

0.9

1.0

08180-008

25

20

15

10

PERCENTAGE OF UNITS (%)

5

0

–1.0

–0.9

–0.8

–0.7

–0.6

–0.5

–0.4

0

–0.3

–0.2

–0.1

GAIN ERROR (d B)

Figure 6. Gain Error Histogram, GAIN+ = 0.16 V

14

12

10

8

6

4

PERCENTAGE OF UNITS (%)

2

25

20

15

10

PERCENTAGE O F UNITS (%)

5

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

08180-006

–1.25 –1.00 –0.75

–0.50 –0.25 0

CHANNEL-TO-CHANNEL GAIN MATCHI NG (dB)

0.25 0.50 0.75 1.00 1. 25

08180-009

Figure 9. Gain Match Histogram, GAIN+ = 0.3 V

25

20

15

10

PERCENTAGE OF UNITS (%)

5

0

–1.0

–0.9

–0.8

–0.7

–0.6

–0.5

–0.4

0

–0.3

GAIN ERROR (dB)

0.1

–0.2

–0.1

0.2

Figure 7. Gain Error Histogram, GAIN+ = 0.8 V

0

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

08180-007

–1.25 –1.00 –0.75

–0.50 –0.25 0

CHANNEL-TO-CHANNEL GAIN MATCHI NG (dB)

0.25 0.50 0.75 1.00 1. 25

08180-010

Figure 10. Gain Match Histogram, GAIN+ = 1.3 V

Rev. 0 | Page 14 of 48

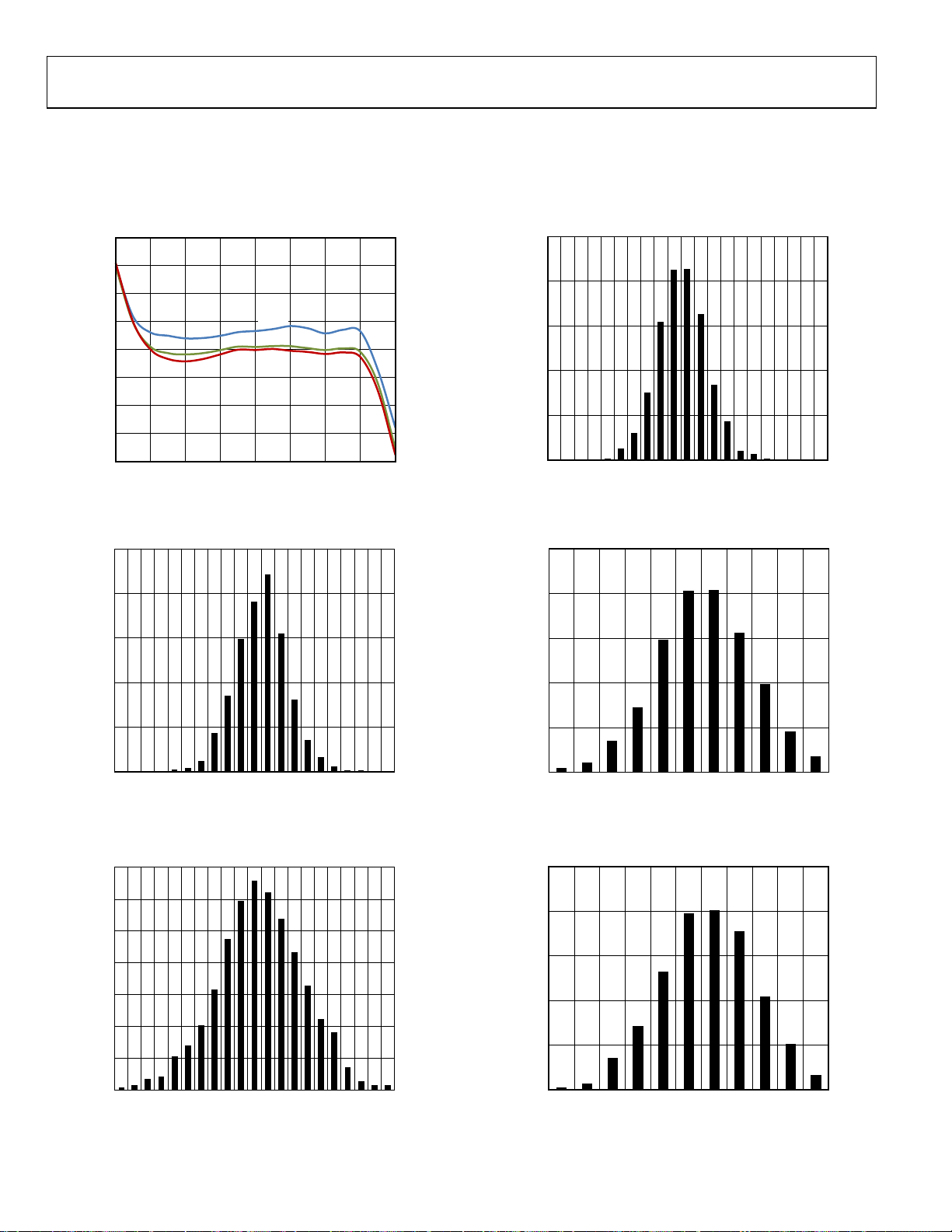

AD9276

–

A

500k

450k

400k

350k

300k

250k

200k

NUMBER OF HIT S

150k

100k

50k

0

–7 –6 –5 –4

–3–2–101234567

CODES

Figure 11. Output-Referred Noise Histogram, GAIN+ = 0.0 V

08180-011

126

–128

–130

–132

–134

–136

OUTPUT-REF ERRED NOISE ( dBFS/Hz)

–138

–140

0 0.2 0.4 0.6 0.8

LNA GAIN = 21.3dB

LNA GAIN = 17.9dB

LNA GAIN = 15.6dB

1.0 1.2 1.4 1.6

GAIN+ (V)

Figure 14. Short-Circuit, Output-Referred Noise vs. GAIN+

08180-014

180k

160k

140k

120k

100k

80k

60k

NUMBER OF HIT S

40k

20k

0

–7 –6 –5 –4

–3–2–101234567

CODES

Figure 12. Output-Referred Noise Histogram, GAIN+ = 1.6 V

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

INPUT-REFERRE D NOISE (n V/ Hz)

0.2

0

12345678910

LNA GAIN = 15.6dB

LNA GAIN = 17.9dB

LNA GAIN = 21.3dB

FREQUENCY (MHz)

Figure 13. Short-Circuit, Input-Referred Noise vs. Frequency,

PGA Gain = 30 dB, GAIN+ = 1.6 V

64

62

60

58

D(dBFS)

56

SNR/SIN

54

52

50

08180-012

0.4 0.5 0.6 0.7 0.8 0. 9 1.0 1.1 1.2 1.3 1.4 1.5 1.6

SNR

SINAD

GAIN+ (V)

08180-015

Figure 15. SNR/SINAD vs. GAIN+, AIN = −1.0 dBFS

0

–5

–10

MODE I – 40MS PS

–15

AMPLITUDE ( dBFS)

–20

–25

0 5 10 15 20 25 30 35 40

08180-013

MODE III – 80MSPS

FREQUENCY (MHz )

MODE II – 65MSPS

08180-016

Figure 16. Antialiasing Filter (AAF) Pass-Band Response,

LPF Cutoff = f

/3 (Mode I and Mode II), f

SAMPLE

/4.5 (Mode III)

SAMPLE

Rev. 0 | Page 15 of 48

Loading...

Loading...